Diego da Silva de Medeiros

Tecnólogo em Sistemas de Telecomunicações pelo Instituto Federal de Santa Catarina e Mestre em Engenharia Elétrica pela Universidade Federal de Santa Catarina. É desde agosto de 2011 Professor da Área de Telecomunicações do Instituto Federal de Santa Catarina, Campus São José.

- Contato

- Telefone: +55 48 3381-2855

- E-mail: diegomedeiros@ifsc.edu.br

- ÍNDICE

Currículo

Link para o Lattes: http://lattes.cnpq.br/5102150000360627

Dígitro Tecnologia LTDA

- Janeiro de 2007 a junho de 2008: Suporte técnico em centrais de grande porte

- Junho a outubro de 2008: desenvolvimento de plataforma para acompanhamento de rotinas de testes

Associação Beneficente da Indústria Carbonífera de Santa Catarina - SATC

- Agosto a dezembro de 2009: Professor na disciplina de Sistemas Lineares no curso de Engenharia Elétrica.

Instituto Federal de Santa Catarina - IFSC

Formação acadêmica

- 2009 - 2013

- Mestrado em Engenharia Elétrica

- Universidade Federal de Santa Catarina - UFSC

- Grupo de Pesquisa em Comunicações - GPqCom

- Título: Cancelamento de sinais interferentes usando arranjo de microfones: aplicação em aparelhos auditivos

- Orientador: Leonardo Silva Resende

- 2005 - 2008

- Graduação em Sistemas de Telecomunicações

- Instituto Federal de Santa Catarina - IFSC - Campus São José

- Título: Transmissão de Seqüências de Imagens Através da Rede Celular GSM/EDGE

- Orientadores: Marcos Moecke e Mario de Noronha Neto

Cursos realizados

- Janeiro de 2008 - NGC Nível I para credenciados técnicos - Dígitro - Certificado

- Setembro de 2013 - Tecnologia FPGA Altera. Macnica DHW, Florianópolis/SC. (Incluir certificado)

- Semestre 2014-1 - Programa Avançado de Matemática - PAM. UFSC, Florianópolis/SC.

- H-CÁLCULO I - 108h - Certificado

- Semestre 2017-2 - Transmissão Digital, Redes SFN, BTS, Headend e Ajustes e Parâmetros dos Transmissores Digitais - Hitachi - 5h - Certificado

Viagens de estudo

- 29/11/2010 a 01/12/2010 - Acompanhamento de alunos na III Jornada da produção científica da educação profissional e tecnológica da região sul, no IF-PR, Câmpus Foz do Iguaçu.

- 18/11/2013 a 22/11/2013 - Acompanhamento de alunos em visitas técnicas aos estabelecimentos:

- 25/04/2017 - Acompanhamento de alunos de primeira fase do Curso Técnico Integrado em Telecomunicações ao Museu do Expedicionário, em Curitiba/PR, como atividade do Projeto Integrador do primeiro ano do curso.

Orientações

TCCs do CST em Sistemas de Telecomunicações

- 2011-1 - Natan Martins Jory - Reconhecimento de moedas via processamento de imagens

- 2011-2 - Antônio Manoel dos Santos Neto - Estudo e Desenvolvimento de um Aplicativo para Monitoramento de Vídeo Proveniente de DVR

- 2013-1 - Thayse Christine da Silva - Detecção de Tumores em mamografia

- 2013-1 - Sant'Clear Ali Costa - Fretum: Sistema WEB de armazenamento de arquivos

- 2013-2 - Ana Paula Rosa Negri - Detecção de crises epilépticas baseada em sinais de eletroencefalograma utilizando a transformada Wavelet

- 2014-2 - Kelly Hilleshein - Reconhecimento de Moedas por Discriminação de Texturas

- 2014-2 - Patrícia Alves Machado - Detecção de problemas em filmes antigos via processamento de imagens digitais

- 2016-2 - Vinicius Antonio Hames - Interface para captura e processamento de imagens em FPGA

- 2017-1 - Mathias Silva - Sistema de alerta de placas de sinalização para motoristas via processamento de imagens

Participação em bancas

TCCs do CST em Sistemas de Telecomunicações

- 2010-2 - Juliana Camilo Inácio - Implementação de um Rádio Definido por Software usando MATLAB e um Par Transmissor/Receptor FM

- 2011-1 - Natan Martins Jory - Reconhecimento de moedas via processamento de imagens

- 2011-1 - Mattia Vismara - Análise e aperfeiçoamento de um sistema didático de transmissão SDR utilizando o MATLAB e um par transmissor/receptor FM

- 2011-2 - Ivon Eduardo Esser Rosa - Projeto de Equalizador Paramétrico Avançado para Aplicações em MP3

- 2011-2 - Glaucio Bertelli Peres - Sistema de análise de sinais: Módulo de interface VGA em FPGA

- 2011-2 - Antônio Manoel dos Santos Neto - Estudo e Desenvolvimento de um Aplicativo para Monitoramento de Vídeo Proveniente de DVR

- 2011-2 - Jânio Anselmo - Identificações de Impressões Digitais em Tempo Real

- 2012-1 - André Lucas Schlichting - Implementações em VHDL de um filtro FIR para controle ativo de ruído

- 2013-1 - Thayse Christine da Silva - Detecção de Tumores em mamografia

- 2013-1 - Sant'Clear Ali Costa - Fretum: Sistema WEB de armazenamento de arquivos

- 2013-2 - Ana Paula Rosa Negri - Detecção de crises epilépticas baseada em sinais de eletroencefalograma utilizando a transformada Wavelet

- 2013-2 - Christiane Fernandes Dias e Silva - Análise de um Cenário Corporativo para Aplicação do Uso de Femtocélulas

- 2014-1 - Bruno Mauri da silva - Controle de áudio baseado na normalização Loudness

- 2014-2 - Anderson Felisbino - Sensoriamento espectral em redes de rádio cognitivo

- 2014-2 - Kelly Hilleshein - Reconhecimento de Moedas por Discriminação de Texturas

- 2014-2 - Rafael da Silva Pereira - AVASS - Ambiente Virtual de Aprendizagem de Sinais e Sistemas - Módulos Estendidos

- 2014-2 - Patrícia Alves Machado - Detecção de problemas em filmes antigos via processamento de imagens digitais

- 2015-1 - Aliny Anselmo - Detecção automática de crises epilépticas em sinais de eletroencefalograma

- 2015-2 - Aline da Silva Damasio - Lixo eletrônico: Uma análise sobre a quantidade e as ações de descarte declaradas pelos sujeitos do Instituto Federal de Educação, Ciência e Tecnologia de Santa Catarina - Campus São José, nos últimos cinco anos. Trabalho do curso de Licenciatura em Ciências da Natureza - Habilitação em Química.

- 2016-1 - Bruna Amante - Sistema Ubíquo para Apoio na Vacinação de Crianças de 0 a 10 Anos de Idade

- 2016-1 - Kamila Rose da Silva - Estudo de Circuitos Aritméticos e Implementação em Dispositivos Lógicos Programáveis

- 2016-2 - Danilo Bedaque - Análise de desempenho de enlaces ponto a ponto da tecnologia Lora

- 2017-1 - Karoline da Rocha - Detecção de vértebras em imagens médicas - estudo de caso Pixeon

- 2017-2 - Vinicius Bandeira - Redução de sensores de EEG e detecção de movimento motor através de RNA

- 2017-2 - Ernani Rodrigues de São Thiago - Reconhecimento de voz utilizando extração de coeficientes Mel-Cepstrais e RNA

Publicações

Mestrado

- Redução de interferências em aparelhos auditivos com um beamformer multi-split GSC e microfones direcionais: Artigo apresentado no XXXIV Simpósio Brasileiro de Telecomunicações e Processamento de Sinais (SBrT 2016), de 30 de agosto a 2 de setembro de 2016, em Santarém/PA. (Certificado de participação)

Graduação

- Jogo “Cinco em Linha” na Internet: Programação de Sockets e implementação de um algoritmo com baixo processamento: Pôster apresentado na I Jornada da Produção Científica da Educação Profissional e Tecnológica da Região Sul, de 8 a 10 de agosto de 2007, em São José/SC.

- Transmissão de sequências de imagens através da rede celular GSM/EDGE: Artigo apresentado na II Jornada da Produção Científica da Educação Profissional e Tecnológica da Região Sul, 27 a 29 de agosto de 2008, em Pelotas/RS.

- Transmissão de sequências de imagens através da rede celular GSM/EDGE: Pôster apresentado na Semana Nacional de Ciência e Tecnologia, nos dias 21 a 23 de outubro de 2008, em Florianópolis/SC.

Alunos

2013:

- Ana Paula Rosa Negri - Identificação de Crises Epilépticas Baseado em Sinais de Eletroencefalograma Utilizando Reconhecimento de Padrões: Pôster apresentado na Semana Nacional de Ciência e Tecnologia do IFSC Campus São José, nos dias 23 a 25 de outubro de 2013, em São José/SC.

2014:

- Thayse Christine Silva - Detecção automática de tumores em mamografias utilizando técnicas de processamento digital de imagem: Artigo apresentado no XXIV Congresso Brasileiro de Engenharia Biomédica, de 13 a 17 de outubro de 2014, em Uberlândia/MG.

- Ana Paula Rosa Negri - Identificação de crises epilépticas baseada em sinais de eletroencefalograma utilizando a transformada Wavelet: Artigo apresentado no V Simpósio de Processamento de Sinais da UNICAMP, nos dias 15 a 17 de setembro de 2014, em Campinas/SP.

- Stephany Guimarães - MATLAB: Software de Estudos Matemáticos: Pôster apresentado na 2ª Mostra Científico-Cultural do IFSC Campus São José, nos dias 14 a 16 de outubro de 2014, em São José/SC.

- Davi Goulart - Arduíno e robótica: Robô seguidor de linha: Pôster apresentado na 2ª Mostra Científico-Cultural do IFSC Campus São José, nos dias 14 a 16 de outubro de 2014, em São José/SC.

- Patricia Alves Machado - Restauração de filmes antigos via processamento de imagens digitais: Pôster apresentado na 2ª Mostra Científico-Cultural do IFSC Campus São José, nos dias 14 a 16 de outubro de 2014, em São José/SC.

2016:

- Vitor Hugo de Oliveira Vargas - Oficina de robótica: Pôster apresentado na 3ª Mostra Científico-Cultural do IFSC Campus São José, nos dias 18 a 21 de outubro de 2016, em São José/SC.

Projetos

- 2013

-

- Edital: Chamada interna simplificada para projetos de curta duração Nº 3/2013 Campus São José

- Função: Coordenador

- Bolsista: Ana Paula Rosa Negri

- Execução: 15 de agosto a 15 de dezembro de 2013

- Produção: Identificação de Crises Epilépticas Baseado em Sinais de Eletroencefalograma Utilizando Reconhecimento de Padrões - Pôster.

-

- 2014

-

- Edital: Chamada pública MEC/SETEC/CNPq Nº 94/2013

- Função: Coordenador

- Professor consultor: Marcos Moecke

- Bolsista externo (DTI-A): Edgard Ubaldo Guillen Salas (Lattes)

- Empresa parceira: CataMoeda Pesquisa e Desenvolvimento de Máquinas S/A

- Execução: Janeiro de 2014 a dezembro de 2015

-

-

- Edital: Chamada pública Nº 20/2014 PRPPGI Campus São José

- Função: Coordenador

- Bolsista: Davi Goulart Soares

- Execução: Maio a setembro de 2014

- Produção: Arduíno e robótica: Robô seguidor de linha - Pôster.

-

-

- Edital: Edital de curta duração Nº 1/2014 Campus São José

- Função: Coordenador

- Bolsista: Patricia Alves Machado

- Execução: Abril a junho de 2014

- Produção: Restauração de filmes antigos via processamento de imagens digitais - Pôster.

-

-

- Edital: Edital de curta duração Nº 1/2014 Campus São José

- Coordenador: Jeremias Stein Rodrigues

- Função: Professor ministrante

- Bolsista: Stephany Padilha Guimarães

- Execução: Abril a junho de 2014

- Produção: MATLAB: Software de Estudos Matemáticos - Pôster.

-

- 2015

- Título: Oficina de construção de robôs

- Edital: Edital para projetos didático-pedagógicos Nº 13/2015 PRPPGI Campus São José

- Função: Coordenador

- Professor palestrante: Fernando Bruinjé Cosentino

- Bolsista: Vitor Hugo de Oliveira Vargas

- Execução: Maio a novembro de 2015

- Produção: Oficina de robótica - Pôster.

- 2017

-

- Edital: Programa de apoio ao desenvolvimento de projetos de ensino, pesquisa e extensão no campus São José - Chamada Nº 04/2017 Campus São José

- Função: Membro

- Bolsista: Natália Adriana Miranda

- Execução: Junho a dezembro de 2017

- Produção: Incluir

-

Projetos Integradores Extracurriculares

- Projeto Integrador do primeiro ano do Curso Técnico Integrado de Telecomunicações

- 2017-1 - 1ª fase

- 2017-2 - 1ª e 2ª fases

Ideias de projetos

Ações de extensão

Disciplinas lecionadas

Curso Técnico Integrado de Telecomunicações

- ICO60801 - Introdução à Computação, nos semestres:

- 2011-1

- 2011-2

- 2012-1

- 2013-1

- 2016-2 - Reestruturação da disciplina (Página)

- 2017-1

- 2017-2

- 2018-1

- ANC60805 - Análise de Circuitos, no semestre:

- 2016-1

| Material preparado - Clicar no "+" para expandir | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Informações da disciplina

Planejamento

Diário de aula

AulasApresentação da disciplina

Circuitos R, L e C em corrente contínuaO capacitorNesta aula é vista a construção, finalidade básica e funcionamento do capacitor. Além disso, é introduzido o conceito de capacitância. A associação de capacitores e a realização do cálculo da capacitância equivalente é apresentada. Por fim, é feita a análise do funcionamento do capacitor na carga e descarga. A apostila de base está disponível no (Link). Para melhor entender o conceito de taxa de variação, ver applet (Link)

Resolver os exercícios nas últimas páginas da apostila O indutorOs princípios básicos de funcionamento do indutor é estudado, com base nos experimentos de Faraday e Lenz. A indutância, associação série e paralelo e os processos de carga e descarga serão vistos. A aula foi baseada principalmente no material no quadro, porém, a apostila dos outros semestres pode ser usada (Link)

Resolver os exercícios nas últimas páginas da apostila Regime permanente em corrente contínuaOs componentes estudados são trabalhados juntos num circuito em regime permanente em corrente contínua. Neste caso:

Resolver os exercícios disponíveis em (Link) Circuitos R, L e C em regime permanente em corrente alternadaSinais senoidaisAula de revisão sobre as características dos sinais senoidais, usando como base a apostila disponível no (Link). Discussões:

FasoresUma forma de trabalhar com sinais senoidais usando números complexos. Facilita os cálculos de circuitos de corrente alternada. A apostila da aula está disponível em (Link).

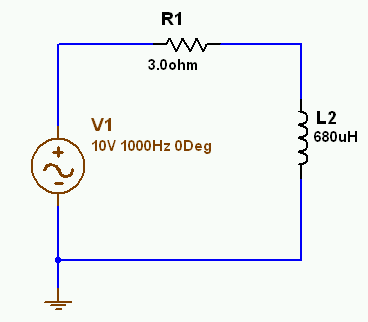

Resolver os exercícios nas últimas páginas da apostila Observação: os exercícios sobre o sinal senoidal e fasores serão cobrados num segundo momento, pois a próxima matéria não faz uso dessas ferramentas. Assim, os exercícios ainda devem ser resolvidos, mas a sua correção ficará para depois. Componentes em corrente alternadaNesta aula, o comportamento dos componentes em corrente alternada é estudado. É introduzido o conceito de reatância indutiva e capacitiva, bem como os atrasos de fase entre tensão e corrente causado pela presença desses componentes no circuito. A resposta em frequência dos componentes é apresentada através de slides. Circuitos em corrente alternadaImpedânciaA impedância é uma grandeza que indica o quanto um elemento consegue "impedir" a passagem de corrente. Ela faz com que a análise de circuitos em CA seja semelhante à análise de circuitos em CC. Circuitos série em CAPara um circuito série, a impedância equivalente vista pela fonte é calculada a partir da equação: Assim, as leis de Ohm e de Kirchhoff podem ser usadas da mesma forma que era usada em CC. Circuitos paralelo em CAPara um circuito paralelo, a impedância equivalente vista pela fonte é calculada a partir da equação: Assim, as leis de Ohm e de Kirchhoff podem ser usadas da mesma forma que era usada em CC. Uso da calculadora Casio fx-82msVer vídeo disponível no Link ExercíciosA lista de exercícios pode ser acessada em (Link). Uma lista complementar pode ser acessada em (Link). Laboratório - Circuitos em CAOs exercícios podem ser desenvolvidos em laboratório. Nesta aula, vamos usar simuladores para observar o comportamento dos circuitos em CA. Vamos usar os simuladores Multisim, na versão de demonstração de 2001 (para instalar em casa, baixar programa do Link), e o Partsim, ferramenta Web acessível em Link. Como exemplo, vamos desenvolver o circuito abaixo:

O laboratório consistirá em 3 partes:

Análise de Malhas

Análise de Nós

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

- Estudo dirigido de Python para alunos de primeira fase do ensino médio - Aula extra-oficial

Curso Técnico Subsequente de Telecomunicações

- 2010-1: Finalização das disciplinas do professor Willi Gonçalez Osaka, substituto que pediu exoneração

- 2010-2:

- 2011-1:

- 2011-2:

- 2013-1:

- Introdução à Computação, formado pelas disciplinas SOP12501 - Sistemas Operacionais e MAN12501 - Manutenção de Computadores

- 2013-2:

Curso Superior de Tecnologia em Sistemas de Telecomunicações

- CMS20706 - Comunicações Móveis e sem Fio II, nos semestres:

- 2010-2

- 2011-1

- 2011-2

- 2012-1

- 2012-2

- CDI20705 - Comunicação Digital, nos semestres:

- 2012-1

- 2012-2

- PSD20706 - Processamento de Sinais Digitais, nos semestres:

- 2012-1

- 2012-2

- 2013-1

- 2013-2

- 2014-1

- 2014-2

- 2016-1

- 2016-2

- 2017-2

Informações da disciplina

- Professor: Diego da Silva de Medeiros

- Plano de Ensino 2017-2

| Atividades previstas - Clicar no "+" para expandir | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Planos de ensino anteriores - Clicar no "+" para expandir | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Diário de aula

| 2017-2 - Clicar no "+" para expandir | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 2016-2 - Clicar no "+" para expandir | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 2016-1 - Clicar no "+" para expandir | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 2014-2 - Clicar no "+" para expandir | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 2014-1 - Clicar no "+" para expandir | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 2013-2 - Clicar no "+" para expandir | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Aulas

Apresentação da disciplina

- Roteiro:

- Apresentação do professor;

- Apresentação da Área de Processamento de Sinais (Slides)

- Apresentação da disciplina (Planos de ensino);

- Grupo da disciplina: IFSCTelePSD

- Atividade (Trabalho 1)

- Pesquisar um artigo da área de Processamento de Sinais no site IEEEXplore e fazer um pequeno resumo sobre o artigo. Como dica, dar preferências a artigos entre 1960 e 1970, pois estes deverão ser de mais fácil compreensão que artigos mais recentes ou muito antigos.

Tutorial de Matlab

Tutorial Linux.m Tutorial Windows.m Versão em PDF do tutorial

Sinais em tempo discreto

Referência: Capítulo 3 do Livro do Lathi, pg. 224.

Introdução à Sinais em Tempo Discreto

- Esta aula é a introdução da disciplina.

- Um sinal discreto é uma abstração de um sinal amostrado, que por sua vez é obtido a partir da multiplicação de um sinal contínuo por um trem de impulsos. A amostragem de sinais é assunto de outra disciplina (Sinais e Sistemas e Comunicação Digital).

- Uma das medidas do tamanho de um sinal é a energia e a potência.

- Energia do sinal:

- Potência do sinal:

- Desta forma, sinais podem ser divididos em sinais de energia ou de potência

- Sinais de energia são sinais que tem energia finita, que desta forma tem potência zero.

- Sinais de potência são sinais que tem potência finita, que desta forma tem energia infinita.

- Alguns sinais não são nem de energia nem de potência

- É comum na área de processamento de sinais a realização de operações com sinais. Algumas dessas operações utilizadas em sinais discretos são:

- Deslocamento - Atraso ou avanço de um sinal no tempo.

- Reversão no tempo - Espelhamento no sinal a partir do eixo da ordenada (y)

- Alteração na taxa de amostragem

- Decimação - Redução da frequência de amostragem do sinal

- Interpolação - Aumento da frequência de amostragem do sinal

- Códigos Matlab desenvolvidos

* Simulação.m * u.m * s.m

- Exercícios (Lathi)

* Exemplo 3.1, pg. 226 * Exemplo 3.2, pg. 227 * Exercício E3.1, ppg. 226 * Exercícios E3.2, E3.3, E3.4 e E3.5, pg. 230

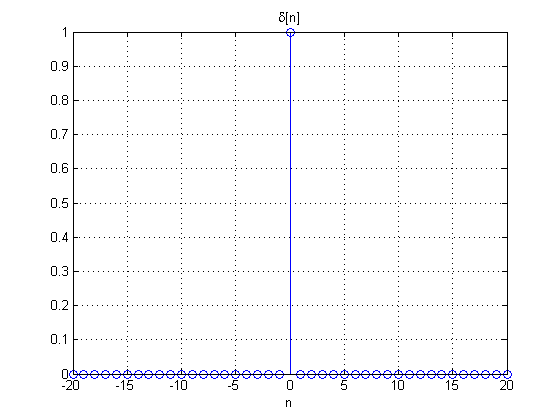

Funções Úteis

- Alguns sinais úteis na área de processamento de sinais digitais (Seção 3.3, pg. 230, do Lathi).

- Impulso unitário, também conhecido como Delta de Kronecker, é a versão discreta da Função Impulso, também conhecida como Delta de Dirac:

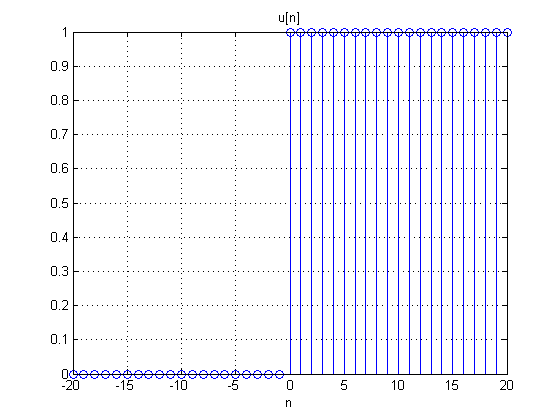

- Degrau unitário, versão discreta da Função Degrau. Muito utilizada para a limitação de sinais em um intervalo de tempo.

- Uma Função Exponencial discreta é descrita na forma , onde é o argumento da função e é inteiro. É possível escrever a função exponencial de uma outra forma, tendo em vista que a base e o argumento são constantes:

- A análise de funções exponenciais discretas é realizada baseada no valor de ou de . Iniciemos nossa análise considerando que , e por consequência , é real.

- Se , , de forma que é uma função crescente;

- Se , encontra-se entre 0 e 1, de forma que é uma função decrescente;

- Se , , de forma que é uma função constante igual a 1.

- A análise de funções exponenciais discretas é realizada baseada no valor de ou de . Iniciemos nossa análise considerando que , e por consequência , é real.

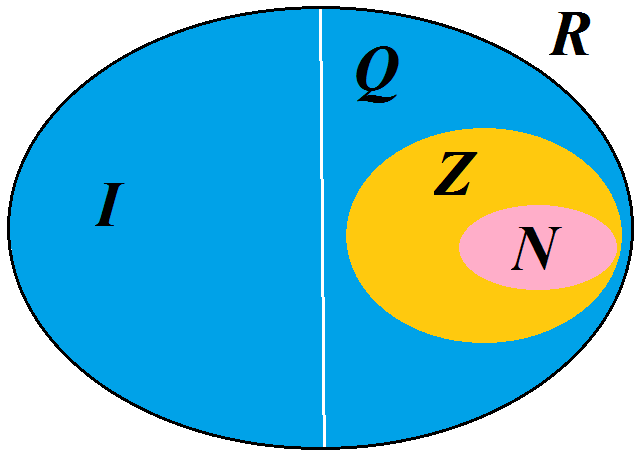

- Se é complexo, ele pode ser escrito na forma , e . Desta forma, também será complexo, ou . A análise é feita então em função de e .

- Se , a exponencial é puramente real, possuindo os três casos acima descritos;

- Se , e , sendo então uma função oscilatória complexa de módulo igual a 1 e frequência de oscilação igual a ;

- Se , e , sendo então uma função oscilatória complexa com módulo crescente e frequência de oscilação igual a

- Se , e , sendo então uma função oscilatória complexa com módulo decrescente e frequência de oscilação igual a

- Se é complexo, ele pode ser escrito na forma , e . Desta forma, também será complexo, ou . A análise é feita então em função de e .

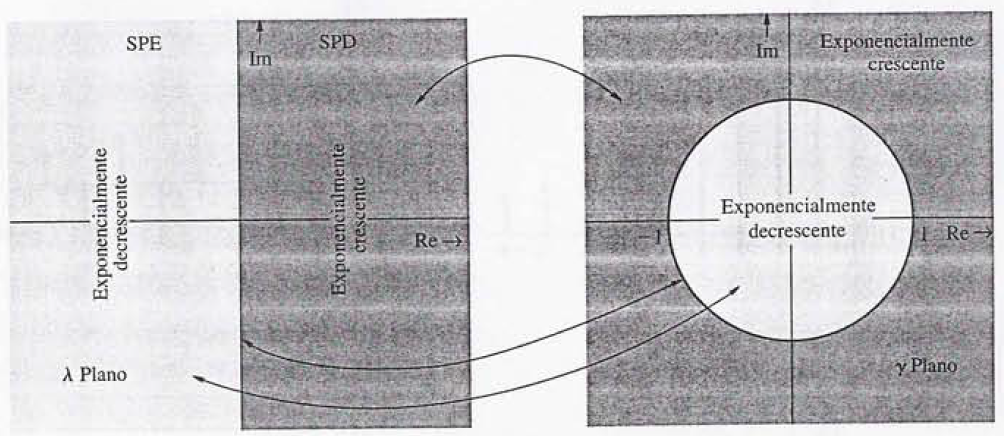

- A análise acima pode ser exportada para um gráfico, como pode ser visto na figura ao lado. Neste caso, o mapeamento de em transforma o Semi Plano Esquerdo (SPE), região onde a exponencial é decrescente, num círculo de raio unitário. O eixo das ordenadas, onde a exponencial possui módulo constante se transforma na borda do círculo. Por fim, o Semi Plano Direito (SPD), onde a exponencial é crescente, se transforma na região fora do círculo unitário.

- Códigos Matlab desenvolvidos

* Simulação.m * u.m * d.m * Comandos usados na aula

- Exercícios (Lathi)

* Exemplo 3.3, pg. 232 * Exercícios E3.6 e E3.7, pg. 234 * Exemplos de computador: * C3.1 para o sinal , mostrando o sinal no intervalo de 0 a 10 * C3.2 para o sinal , mostrando o sinal no intervalo de 0 a 33

Laboratório - Sinais digitais

- Laboratório 1 - Som

- Ler o arquivo de áudio abaixo

- Realizar operações de deslocamento, reversão no tempo, reversão de amplitude, mexer na frequência de amostragem, etc

* Codigo.m * Audio.mp3

- Laboratório 2 - Imagem

- Fazer partes 1 a 3 do laboratório acessível em Link

- Laboratório 3 - Interpolação de uma imagem

- Ler o arquivo de imagem abaixo

- Aumentar a resolução da imagem, através da interpolação

* Imagem.jpg * Codigo.m - Aula do dia 23/08/2016

Avaliação - Interpolação

Terminar o processo de interpolação iniciado em aula. Já foi feito o processo para linhas, fazer para colunas e diagonais.

* Codigo.m - Completo

Sistemas em tempo discreto

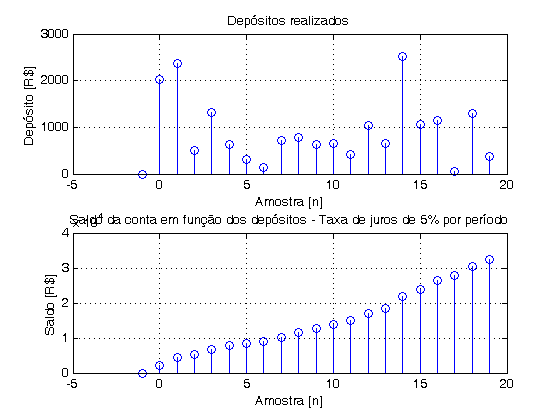

- Ao pensar em Sistemas de Tempo Discreto, normalmente vem à mente aplicações como áudio digital, imagem digital, etc. O termo discreto porém, é maior do que isso, e inclui todo sistema que é não contínuo. O exemplo abaixo, exemplo 3.4 do Lathi, aborda esta questão.

- Uma pessoa faz regularmente um depósito em um banco a um intervalo . O banco paga um certo juro na conta bancária durante o período e envia periodicamente uma correspondência com o saldo ao depositante. As variáveis envolvidas no problema são:

- = depósito feito no instante

- = saldo na conta no instante , calculado imediatamente após o recebimento do depósito

- = taxa de juros

- O saldo é a soma de:

- Saldo anterior

- Juros obtidos em durante o período

- Depósito

- A equação que relaciona a saída (saldo) com a entrada (depósito) é:

- , onde

- Ou, substituindo por

- , onde

- Uma pessoa faz regularmente um depósito em um banco a um intervalo . O banco paga um certo juro na conta bancária durante o período e envia periodicamente uma correspondência com o saldo ao depositante. As variáveis envolvidas no problema são:

- As equações anteriores, chamadas de equações diferença, relacionam a entrada e a saída de um sistema, ou de uma forma mais completa, relacionam as amostras atual e anteriores da entrada com as amostras atual e anteriores da saída. Uma versão genérica da equação diferença é:

- , com

- ou

- As equações anteriores estão na forma do operador de avanço. Substituindo por , a equação fica na forma do operador de atraso:

- , com

- Para que um sistema descrito pelas equações diferença acima descritas seja causal, é necessário que sua saída não dependa de valores futuros de sua entrada. Na forma do operador de avanço, a saída mais avançada no tempo é , e a entrada mais avançada no tempo é . Assim, para que um sistema seja causal, é necessário que

- Uma forma simples e rápida de resolver o sistema a partir da sua equação diferença é a solução recursiva (ou interativa). O método é calculado passo a passo, utilizando as condições iniciais e os valores do sinal de entrada.

Ver exemplo 3.8 do Lathi, pg. 247

- Uma forma diferente de representar o sistema é através da Notação Operacional. Nela, a equação diferença do sistema fica similar à uma equação diferencial, e um tratamento semelhante pode ser utilizado para sua resolução. Para a notação operacional, utiliza-se o operador para representar um avanço de amostras.

- Exemplo:

- Equação diferença de primeira ordem:

- Equação diferença de segunda ordem:

- Desta forma, uma equação diferença genérica em notação operacional é

- ou simplesmente

- onde

- Códigos Matlab desenvolvidos

* Simulação.m - Solução do exemplo 3.8

- Exercícios (Lathi)

* Exercício 3.4-1 e 3.4-2 pg. 295 * Exemplo 3.8, pg. 247 * Exercício E3.10, pg. 249 * Exemplo de computador C3.3 para o sinal do exercício E3.10 * Descrever todas as equações diferença dos exercícios anteriores com Notação Operacional

Solução de Sistemas e Resposta de Entrada Nula

- Saída de um sistema possui componentes referentes à entrada do sistema e componentes referentes às condições iniciais

- Referentes às condições iniciais: Resposta de entrada nula

- Referentes à entrada: Resposta de estado nulo

- A resposta de entrada nula de um sistema é a solução da sua equação diferença, assumindo que não há sinais de entrada (solução homogênea).

- ou

- ou ainda

- A solução do problema é então (assumindo raízes distintas):

- onde os 's são as constantes do problema, obtidas através das condições iniciais

- Para raízes repetidas:

- e a resposta de entrada nula será:

- Para raízes complexas, expressamos as raízes na forma polar:

- e

- E a resposta de entrada nula será

- Para um sistema real

- e

- E então:

- Nomenclatura:

- = polinônio característico do sistema

- = equação característica do sistema

- = raízes características, valores característicos ou autovalores do sistema

- = modos característicos ou modos naturais do sistema

- = resposta de entrada nula do sistema, que é a combinação linear dos modos característicos

- Exercícios (Lathi)

* Exemplo 3.10, pg. 252 * Exercícios E3.11, E3.12 e E3.13, pg. 255 * Exercício de computador C3.4 para os sistemas dos outros exercícios

Resposta ao Impulso e Resposta de Estado Nulo

- Uma solução importante na análise de sistemas é a resposta do sistema à um impulso unitário. A resposta ao impulso de um sistema é a solução da sua equação diferença, considerando que há, na entrada do sistema, uma função impulso .

- Ou:

- Neste caso, considera-se todas as condições iniciais nulas:

- O método iterativo (ou recursivo) pode ser utilizado para a resolução do sistema, mas este é pouco prático para respostas longas. Por isso, há a solução fechada, dada pela equação:

- onde é a combinação linear dos modos característicos e e são obtidos da equação diferença do sistema.

Ver exemplo 3.12, pg. 258

- A resposta de estado nulo é a resposta do sistema à sua entrada, considerando suas condições iniciais zero. A solução da resposta de estado nulo é dada pelo somatório de convolução:

- onde é a entrada do sistema e é sua resposta ao impulso. Embora pareça um pouco diferente, o somatório de convolução é a mesma operação realizada em tempo contínuo, a integral de convolução.

- As propriedades do somatório de convolução são:

- Comutativa

- Distributiva

- Associativa

- Propriedade do deslocamento

- Se ,

- Convolução com um impulso

- Propriedade da largura

- Se tem elementos (amostras) e tem elementos, tem elementos.

- Causalidade

- para

- para , tal que para

- E a convolução causal é:

Ver exemplo 3.13, pg. 262

- Em geral, o cálculo da convolução propriamente dito não é muito realizado. Isso se deve à existência de tabelas com a convolução dos sinais mais comuns. Um exemplo pode ser visto na Tabela 3.1 do livro do Lathi, pg. 263.

- Mais importante que a resolução dos cálculos, seja pela equação ou pela tabela, é o entendimento do que é realizado com os sinais durante a operação. A convolução de dois sinais e inicia com a reversão no tempo de um dos sinais (por exemplo, ). Para encontrar o valor de saída para um dado instante , é deslocado de amostras, e uma multiplicação ponto a ponto é executada entre os sinais e . O processo de convolução consiste então no deslocamento de por toda a extensão de . Este fato pode ser visto em [1] e [2].

- Exercícios (Lathi)

* Exemplo 3.11, pg. 256 * Exemplo 3.12, pg. 258 * Exercício E3.14, pg. 259 * Exercício 3.7-4, pg. 298 * Exemplo 3.13, pg. 262 * Exercício E3.15, pg. 263 * Exemplo 3.14, pg. 264 * Exemplo de computador C3.6 * Criar uma função no Matlab para realizar a convolução entre dois sinais causais

Laboratório - Reposta ao impulso

- Parte 1 - Em sala

- Criar respostas ao impulso com poucos multipercursos:

d = zeros(30000,1); d(1) = 1; d(15000) = 1;

- Ler um arquivo de áudio e realizar a convolução entre ele e a resposta ao impulso criada

- Observar o comportamento

- Parte 2 - Entregar

Construir uma simulação no Matlab que lê um dos arquivos de áudio e cria um efeito de que a voz foi falada à 45° do ouvinte (estéreo).

| Comentários - Clicar no "+" para expandir |

|---|

|

Observa-se que o efeito de 45° de ângulo de incidência é difícil de ser implementado com os conceitos abordados em aula. A alteração para 90° permite um certo nível de sucesso. Para a implementação do ângulo de 45° seria necessário usar o método das imagens de Allen e Berkley (ver artigo). |

Resposta Total e Estabilidade

- A Resposta total de um sistema é definida como:

- Resposta Total = Resposta de entrada nula + Resposta de estado nulo

- Resposta Total =

- A estabilidade de um sistema é dividida entre estabilidade externa (BIBO - Bounded-input/boundded-output) e interna (assintótica).

- Um sistema é BIBO estável se a sua resposta ao impulso for absolutamente somável:

- A estabilidade interna de um sistema é caracterizada da seguinte forma:

- Raízes simples ou repetidas dentro do círculo unitário: assintoticamente estável

- Raízes simples sobre o círculo unitário: marginalmente estável

- Raízes repetidas sobre o círculo unitário: assintoticamente instável

- Raízes simples ou repetidas fora do círculo unitário: assintoticamente instável

- As estabilidades interna e externa são relacionadas da seguinte forma:

- Raízes dentro do círculo são absolutamente somáveis, por isso sistemas assintoticamente estáveis são BIBO estáveis.

- Raízes sobre ou fora do círculo não são absolutamente somáveis, por isso sistemas marginalmente estáveis ou assintoticamente instáveis são BIBO instáveis.

- Exercícios (Lathi)

* Exemplo 3.22, pg. 285 * Exercício 3.10-2, pg. 303

Avaliação 1 - Sinais e sistemas de tempo discreto

- Os conteúdos referentes à primeira parte da disciplina (capítulo 3 do Lathi) serão avaliados através de uma prova.

Para 2016-2, a prova será aplicada no formato de um trabalho, com prazo para entrega em 30/09/2016.

| Resultados - Clicar no "+" para expandir |

|---|

|

|

Transformada Z

Referência: Capítulo 5 do Livro do Lathi, pg. 442.

Definição da Transformada Z Direta e Inversa

- A Transformada Z Direta é calculada como a seguir:

- A forma mais direta de resolução se dá considerando que os termos a serem somados são elementos de uma PG (progressão geométrica). Uma PG é definida como uma sucessão de termos:

- onde, ou , sendo denominado razão da sucessão de termos.

- A planilha a seguir foi feita para ajudar o entendimento das PGs, confirmando a equivalências das duas equações acima Link.

- Para a soma de termos de uma PG ( finito):

- Para a soma de infinitos termos de uma PG:

- Para mais informações sobre PGs, ver Link.

- A Transformada Z inversa é definida como:

- Em geral este cálculo não é realizado, dada a existência de tabelas (ver tabela 5.1 do Lathi ou esta seção da Wikipédia). O que é necessário para a resolução dos problemas é adequar o sinal no domínio Z à algum par específico da tabela.

- Exercícios (Lathi)

* Exemplo 5.1, pg. 444 * Exemplo 5.2, pg. 446 * Exercício E5.1, pg. 448 * Selecionar alguns itens do exercício 5.1-2, pg. 516 * Exercício 5.1-4, pg. 517

* Exemplo 5.3, pg. 448 * Exercício E5.2, pg. 451 * Exercício 5.1-5, pg. 517

- Resoluções realizadas no semestre 2013-1

- Solução exemplo 5.3.b

- Solução exemplo 5.3.c

Propriedades da Transformada Z

- Algumas propriedades podem ser utilizadas para facilitar o cálculo da transformada Z. Exemplos de tabelas são a Tabela 5.2, pg. 459 do Lathi e esta seção da Wikipédia.

- Nesta aula, as propriedades serão derivadas.

- Exercícios (Lathi)

* Exemplo 5.4, pg. 456 * Exercício 5.2-3, 5.2-7 e 5.2-9, pg. 518

Solução de sistemas usando a Transformada Z

- A Transformada é utilizada principalmente na solução de sistemas Lineares Discretos Invariantes no Tempo (LDIT). O método é sintetizado a seguir:

- A equação diferenças é convertida para o domínio utilizando a propriedade do deslocamento à direita da Transformada Z:

- A equação algébrica no domínio é trabalhada de forma a isolar .

- Com o isolado, a equação algébrica é convertida de volta para o domínio através da Transformada Z Inversa, encontrando então a resposta total do sistema, .

- Com esta abordagem, é possível também encontrar a resposta total com as componentes de entrada nula e de estado nulo em separado. Para isso, as componentes referentes ao sinal de entrada e às condições iniciais devem ser mantidas separadas durante o trabalho algébrico.

- Uma outra utilização da Transformada Z diz respeito à Função de transferência de um sistema. A Função de Transferência é utilizada para encontrar a a resposta de estado nulo do sistema, ou mesmo a resposta total, quando o sistema não possui condições iniciais (resposta de entrada nula igual à zero):

- então:

- Dada a equação diferenças genérica:

- ou, em notação operacional:

- ou simplesmente:

- onde:

- A Função de Transferência do sistema é:

- A estabilidade do sistema pode ser obtida a partir da sua Função de Transferência. Como a Função de Transferência é uma descrição externa do sistema, pois relaciona saída e entrada, a estabilidade BIBO (externa) é encontrada. Assim, se todos os polos de estiverem dentro do círculo unitário, o sistema será BIBO estável.

- Se e não possuírem fatores comuns, o denominador de será idêntico à , e:

- sistema assintoticamente estável: Polos de , repetidos ou simples, dentro do círculo unitário

- sistema assintoticamente instável:

- (i) Ao menos um polo de fora do círculo unitário;

- (ii) Polos de repetidos sobre o círculo unitário

- sistema marginalmente estável: Nenhum polo de fora do círculo unitário e pelo menos um polo simples sobre o círculo unitário.

- Exercícios (Lathi)

* Exemplo 5.5, pg. 461 * Exercício E5.10, pg. 462 * Exercício E5.11, pg. 463 * Exercício E5.12, pg. 464 * Exercícios 5.3-2, 5.3-3, 5.3-5, 5.3-6, 5.3-7, 5.3-8, 5.3-10, pg. 519

* Exemplo 5.6, pg. 466 * Exercício 5.3-18, pg. 519 * Exercícios 5.3-19, 5.3-20, 5.3-21, 5.3-23, pg. 520

- Resoluções realizadas no semestre 2014-1

- Solução exercício E5.10

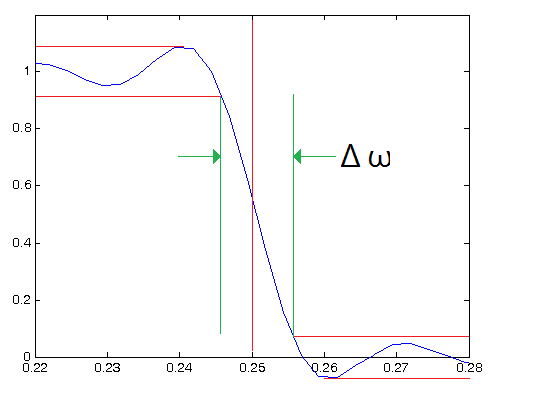

Resposta em Frequência de Sistemas em Tempo Discreto

- A Resposta em Frequência de um sistema de Tempo Discreto é encontrada a partir da sua Função de Transferência, substituindo por . Assim, a frequência é indicada por . Usando a seta direcional para representar a relação entrada saída:

- E, fazendo :

- onde é a Resposta em Frequência do sistema, que expressa na forma polar:

- Para uma entrada senoidal, considerando que é a parte real de :

- e para uma senoide defasada de :

Ver Exemplo 5.10 do Lathi, pg. 476

- Como pode ser visto no exemplo anterior, a Resposta em Frequência de Sistemas de Tempo Discreto é Periódica com período . Isto se deve à não unicidade de ondas senoidais no domínio de tempo contínuo:

- , para inteiro

- Isto pode ser confirmado pelo seguinte Código MATLAB.

- A Resposta em Frequência do sistema também pode ser determinada pela posição dos seus polos e zeros. Para uma Função de Transferência genérica:

- encontrando as raízes de ambos os polinômios, a Forma Fatorada da Função de Transferência é encontrada:

- Para encontrar a Resposta em Frequência do sistema, fazemos . Como , variar significa percorrer o círculo unitário. Desta forma, a resposta do sistema para uma determinada frequência é encontrada a partir da linha que une os polos e zeros ao ponto de ângulo sobre o círculo unitário. Ou:

- ou

- onde e são os módulos e e são os ângulos da linha que une o zero e o polo ao ponto de ângulo sobre o círculo unitário.

- Desta forma, as seguintes conclusões podem ser tomadas

- Como a magnitude de é diretamente proporcional ao produto das distâncias dos zeros à , incluir um zero próximo de um determinado ângulo do círculo unitário reduz a resposta de magnitude para esta frequência angular. Para suprimir totalmente uma determinada frequência, um zero neste ângulo do círculo unitário pode ser inserido.

- Como a magnitude de é inversamente proporcional ao produto das distâncias dos zeros à , incluir um polo próximo de um determinado ângulo do círculo unitário aumenta a resposta de magnitude para esta frequência angular. Não se deve esquecer que um polo sobre o círculo unitário resulta num sistema BIBO instável.

- Para um filtro ideal, o número de polos e zeros necessários é muito grande (infinito).

- Este comportamento pode ser visto na ferramenta do MATLAB Fdatool.

- Exercícios (Lathi)

* Exemplo 5.10, pg. 476 * Exercício E5.18, pg. 479 * Exercícios 5.5-1, 5.5-2, 5.5-4, pg. 521 * Exercícios 5.5-5, pg. 522

* Exercício 5.6-1, pg. 522

Laboratório de Transformada Z

- Este laboratório tem o objetivo de auxiliar o entendimento dos conceitos que envolvem a utilização da Transformada Z na análise e solução de sistemas LDIT. Mais precisamente, a Função de Transferência será explorada, de forma a visualizar a resposta em frequência a partir da posição dos polos e zeros do sistema.

- Pré laboratório

- Estudar o help do matlab das funções:

- polar() - Plot em coordenadas polares

- poly() - Encontra os coeficientes de um polinômio com base em suas raízes

- roots() - Encontra as raízes de um polinômio com base em seus coeficientes

- freqz() - Retorna a resposta em frequência de um sistema com base na sua equação diferença

- Laboratório

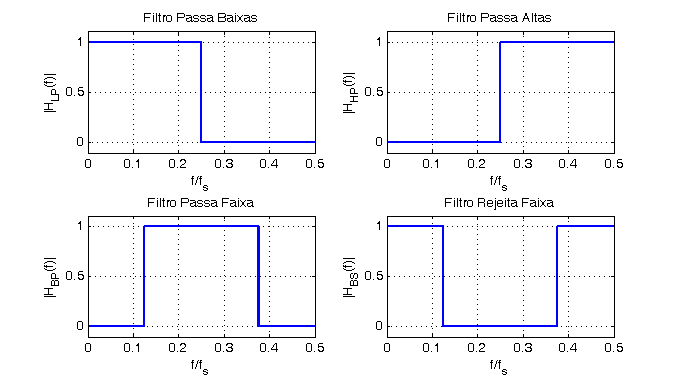

- Definir os seguintes sistemas com o mínimo de polos e zeros:

- Filtro passa-baixas

- Filtro passa-altas

- Filtro passa-faixa

- Filtro rejeita-faixa

- Plotar os polos (x) e os zeros (o) no círculo unitário usando a função polar()

- Calcular a resposta em frequência do filtro criado utilizando a função freqz()

- Observar a definição da frequência de amostragem nos parâmetros.

- Plotar a resposta de magnitude e de fase dos filtros

- Aumentar o número de polos e zeros dos filtros e observar o comportamento

Avaliação 2 - Transformada Z

- Os conteúdos referentes à segunda parte da disciplina (capítulo 5 do Lathi) serão avaliados através de uma prova.

| Resultados - Clicar no "+" para expandir |

|---|

|

|

Análise de Fourier de Sinais em Tempo Discreto

Referência: Capítulo 9 do Livro do Lathi, pg. 738.

Série de Fourier de Tempo Discreto

- Periodicidade de uma senoide discreta

- Uma senoide discreta é periódica com período inteiro se . Esta equação é verdadeira quando , com inteiro. Assim, a senoide será periódica se:

- um número racional (representado pela divisão de dois números inteiros)

- O Período Fundamental da senoide será então:

- sendo a Frequência Fundamental da senoide e o menor inteiro que faz um número inteiro.

- O Período Fundamental da senoide será então:

- Definição da Série de Fourier de Tempo Discreto

- A Série de Fourier de Tempo Discreto é constituída pela soma de exponenciais complexas e discretas, com frequências múltiplas da frequência fundamental:

- Mas como:

- A Série de Fourier de Tempo Discreto é finita, com termos.

- Mas como:

- A Série de Fourier de Tempo Discreto é definida por:

- onde é o coeficiente associado à frequência angular , definido por:

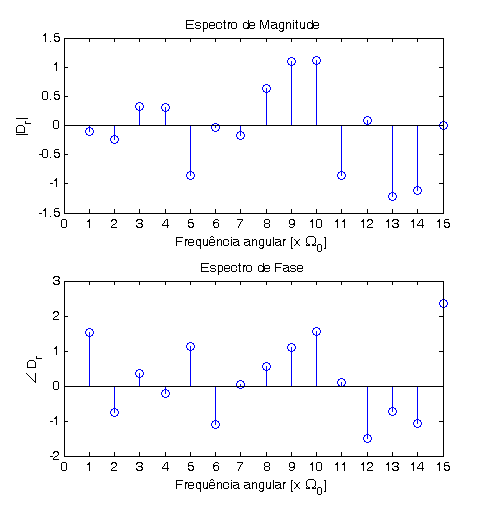

- Espectro de Fourier de um Sinal Discreto

- A Série de Fourier tem componentes:

- onde as frequências de cada componente. Considerando que é em geral complexo, na forma

- Pode-se então fazer um gráfico relacionando o módulo e a fase de com a frequência do termo. Este é o Espectro de Fourier do sinal.

- Códigos Matlab desenvolvidos

* Periodicidade_senoide.m * Espectro_Fourier.m -- Simples * ExemploC9_2.m * Espectro_Fourier_3D.m * Espectro_Fourier_3D_onda_quadrada.m

- Exercícios (Lathi)

* Exemplo 9.2, pg. 745 * Exercício E9.2, pg. 744 * Exercício 9.1-1, 9.1-4, 9.1-5 e 9.1-6, pg. 783

Transformada de Fourier de Tempo Discreto

- As Séries de Fourier de Tempo Discreto permitem descrever sinais discretos periódicos através da soma de exponenciais complexas. Quando o sinal é aperiódico a utilização da série é inviabilizada. A extensão da análise de Fourier para sinais discretos aperiódicos é feita da mesma forma que no mundo contínuo, formando um sinal aperiódico a partir de um sinal periódico com período infinito.

- Sendo assim, o par de Transformadas de Fourier é definido como:

- Transformada Direta

- Transformada Inversa

- Informações relevantes

-

- Espectro é uma função contínua de

- Espectro é uma função periódica de :

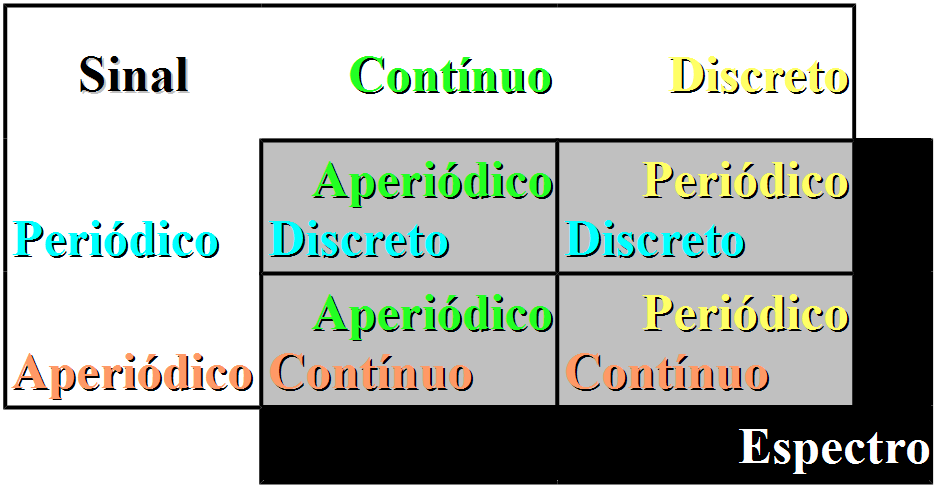

- Espectro Periódico X Amostrado

- Sinal periódico:

- Séries de Fourier

- Espectro discreto (harmônicas)

- Sinal aperiódico:

- Espectro contínuo

- Sinal discreto (amostrado)

- Espectro periódico (repetido a cada Hz ou )

- Sinal contínuo

- Espectro aperiódico

- Exercícios (Lathi)

* Exemplo 9.3, pg. 752 * Exemplo 9.4, pg. 753 * Exemplo 9.5, pg. 754 * Exemplo 9.6, pg. 756 * Exercício E9.4 e E9.5, pg. 756

Laboratório de Transformada de Fourier

- Criação de sinais digitais no Matlab.

- Funções do Matlab apresentadas:

linspace() - função utilizada para criar vetores em intervalos lineares fft() - função que calcula a transformada de Fourier fftshift() - função auxiliar no trabalho com a transformada de Fourier

| Código executado em sala |

|---|

clear all; close all

% Amostragem

fs = 5000;

ts = 1/fs;

% Numero de amostras do seno

N = 10000;

% Criando o vetor de tempo

n = 0:N-1;

t = linspace(0,(N-1)*ts,100000);

% Criando o vetor de frequencia

f = linspace(-fs/2,fs/2,N);

% Parametros dos senos - cada elemento do vetor

% irá criar um seno diferente, e todos serao somados

A = [1 0.5 0.25 0.5];

fo = [50 200 450 900]; % Hz

% Iniciando o sinal

sinal = zeros(size(n));

sinal_plot = zeros(size(t));

for ii = 1:length(A)

% Gerando o sinal senoidal

sinal = sinal + A(ii) * sin(2*pi*fo(ii)*n*ts);

sinal_plot = sinal_plot + A(ii) * sin(2*pi*fo(ii)*t);

end

% Exibindo o sinal no tempo

figure

stem(n*ts,sinal,'Marker','none')

hold on

plot(t,sinal_plot,'k')

xlabel('Tempo [s]')

ylabel('Sinal')

% Tirando a transformada de fourier

espectro = (2/N)*fft(sinal);

% Exibindo o sinal na frequencia

figure

plot(f,fftshift(abs(espectro)))

% Tocando o sinal na caixa de som

sound(sinal,fs)

%% Receber tecla do usuário

%

% Tecla digitada está armazenada na variável "x", como um texto

x = input('Digite uma tecla > ','s');

display(['A tecla digitada foi: ' x])

%% Juntando os dois códigos

%

% Usar CTRL+c para interomper

while true

x = input('Digite uma tecla > ','s');

display(['A tecla digitada foi: ' x])

end

%% Controlando a execução do laço

%

% Usar a tecla "q" para sair do laço

% Iniciando o "x"

x = ' ';

while x ~= 's'

x = input('Digite uma tecla > ','s');

display(['A tecla digitada foi: ' x])

end

%% Estrutura de teste

%

mynumber = input('Enter a number: ');

switch mynumber

case 1

disp(' Digitou 1');

case 2

disp(' Digitou 2');

case 3

disp(' Digitou 3');

case 4

disp(' Digitou 4');

case 5

disp(' Digitou 5');

case 6

disp(' Digitou 6');

case 7

disp(' Digitou 7');

case 8

disp(' Digitou 8');

case 9

disp(' Digitou 9');

otherwise

disp(' Other value');

end

|

Avaliação 3 - Trabalho sobre Transformada de Fourier

| Atividades dos semestres anteriores - Clicar no "+" para expandir |

|---|

Laboratório de Processamento Digital de Imagens

Este laboratório é uma apresentação da Área de Processamento Digital de Imagens. É baseado em alguns materiais de alunos do professor Manuel Menezes de Oliveira Neto (página), da UFRGS. (Colorização)

Filtros Digitais

Referência: Capítulo 4, 5 e 6 do Livro do Shenoi.

Introdução aos Filtros Digitais

- As respostas clássicas de filtros analógicos também se aplicam aos filtros digitais:

- Os filtros digitais são sistemas descritos por equações diferenças, que na sua forma genérica é:

- A Função de Transferência dos filtros digitais é encontrada via Transformada Z:

- Fazendo , obtemos a Resposta em Frequência do filtro:

- Nota-se que é um número complexo, que pode então ser descrito na forma polar:

- onde é o módulo da resposta em frequência (Resposta de Magnitude) e é a fase da resposta em frequência (Resposta de Fase).

- O processo de filtragem de um sinal por um filtro digital é descrito através da operação de convolução. "Filtrar" um sinal significa realizar a convolução da resposta ao impulso do filtro com o sinal em questão:

- Que no domínio da frequência é:

- ou:

- Ou seja, o espectro de magnitude do sinal filtrado é o produto do espectro de magnitude do sinal original pela resposta de magnitude do filtro, enquanto que o espectro de fase do sinal filtrado é a soma do espectro de fase do sinal original pela resposta de fase do filtro.

Filtros FIR e IIR

- Os filtros FIR e IIR serão apresentados através dos dois seguintes exemplos:

- Exemplos

- , tendo como condições iniciais e , e sinal de entrada

- O resultado deste exemplo é

- , com sinal de entrada

- O resultado deste exemplo é

- É visível que há diferenças nos resultados dos exemplos. No primeiro exemplo, o sinal de saída inicia em e se estende até o infinito, dado que não há nenhuma limitação no tempo na equação. Já no segundo exemplo, o sinal de saída é limitado a existir apenas nos instantes e . Sendo assim, temos no primeiro exemplo um sinal de duração infinita e no segundo um sinal de duração finita. Como o sinal de entrada dos sistemas é um impulso (), os sinais em questão são as respostas ao impulso dos respectivos sistemas.

- Sendo assim, os filtros são classificados numa das duas formas:

- Filtros com Resposta ao Impulso Finita (FIR - Finite Impulse Response)

- Filtros com Resposta ao Impulso Infinita (IIR - Infinite Impulse Response)

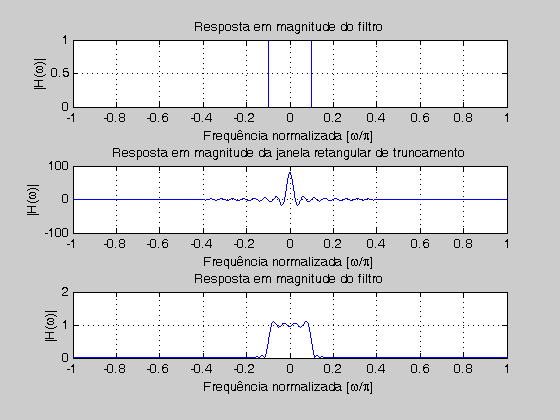

Filtros FIR janelados

- A resposta de magnitude ideal de um filtro passa baixas pode ser descrita através da seguinte equação:

- Ao calcular a transformada inversa de Fourier da resposta em questão, o seguinte sinal é obtido:

- ou de outra forma:

- Para outros filtros:

- Filtro passa altas:

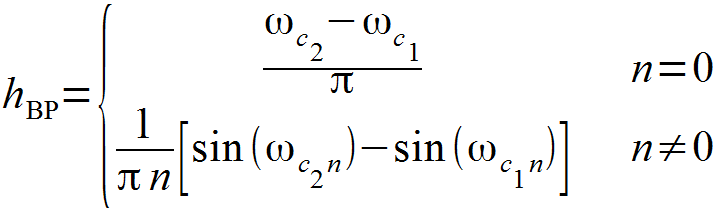

- Filtro passa faixa:

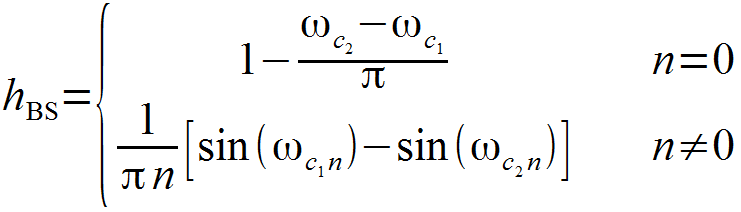

- Filtro rejeita faixa:

- Observação: Todas essas equações consideram o uso de uma frequência de amostragem . Caso uma outra frequência de amostragem seja utilizada, cuidar com as seguintes situações:

- A distância entre as amostras não serão de uma unidade. Assim, sempre que o termo aparecer, este deve ser substituído por . Com isso, a distância entre as amostras irá depender da frequência de amostragem utilizada.

- No filtro rejeita faixa, o termo em da subtração deve ser substituído pela frequência de amostragem, ficando a equação

- Estas são as respostas ao impulso dos filtros ideais. Uma questão importante destas respostas é que elas são ilimitadas no tempo, ou seja, possuem duração infinita. Para que estas repostas sejam realizáveis através de filtros FIR, é necessário limitar o número de amostras da resposta ao impulso :

- ou seja, amostras fora do intervalo são descartadas.

- Um filtro passa baixas truncado não possui mais a resposta em frequência ideal, já que para obter aquela resposta seriam necessárias infinitas amostras. Considerando que o truncamento pode ser representado pela multiplicação da resposta ao impulso original por uma janela retangular:

- a resposta em frequência do filtro truncado será a convolução da resposta em frequência ideal do fitro pela transformada de fourier da janela retangular utilizada no truncamento da resposta. Ou:

- onde é a transformada de Fourier da janela retangular:

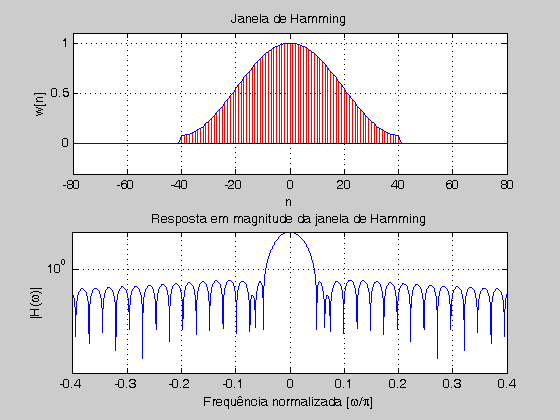

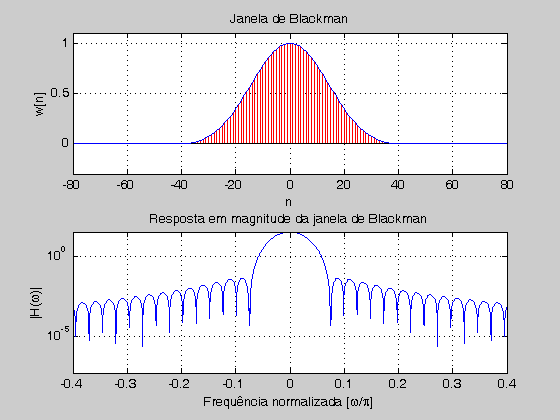

- A janela retangular não é a única opção de truncamento disponível. A seguir, as principais janelas serão apresentadas:

- Bartlett (triangular):

- Hann:

- Hamming:

- Blackman:

- Os impactos do uso destas e muitas outras janelas podem ser vistos no Matlab, na ferramenta fdatool. Para mais informações, ver Link.

- Códigos Matlab desenvolvidos

* Simulação.m * u.m * d.m

A janela Kaiser

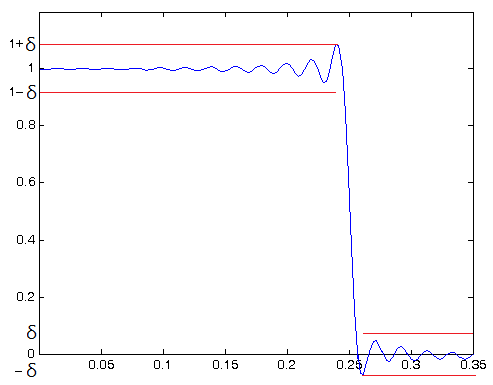

- Nas janelas anteriores não há um controle sobre a resposta em frequência dos filtros. Visando obter tal controle, a janela de Kaiser foi desenvolvida.

- Na janela de Kaiser, o parâmetro é utilizado para indicar a máxima flutuação da resposta nas bandas de rejeição e passagem, assim como o parâmetro indica a taxa de transição entre as duas bandas. Desta forma têm-se um controle total sobre a resposta em frequência do filtro.

- Para encontrar a resposta ao impulso da Janela de Kaiser, deve-se seguir os passos:

- Número de amostras da resposta ao impulso

- Janela de Kaiser:

- onde:

- Função de Bessel de ordem zero modificada (para fazer no Matlab, ver função besseli)

Laboratório de Filtros Digitais

Avaliação 4 - Filtros Digitais

| Semestres anteriores - Clicar no "+" para expandir |

|---|

|

Avaliações de Recuperação

| Avaliações semestres anteriores - Clicar no "+" para expandir |

|---|

|

- SST20707 - Síntese de Sistemas de Telecomunicações, nos semestres:

- 2015-1

- 2015-2

- 2016-1

- 2016-2

- 2017-1

- 2017-2

| Material preparado - Clicar no "+" para expandir | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Ementa e referências bibliográficasInformações da disciplina

Diário de aula

AulasApresentação da disciplina

Dispositivos lógicos programáveis - PLDPLDs em sistemas digitaisSistema digital: Saída digital definida em função de processamento realizado em entrada digital.

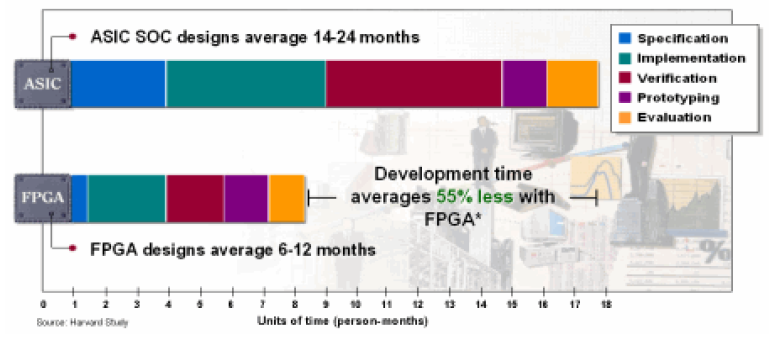

Os sistemas digitais foram por muito tempo projetados usando a chamada lógica fixa, composta por CIs (circuitos integrados) TTL que implementavam portas lógicas. Em meados de 1970, foram introduzidos os PLDs (Programmable Logic Devices), chips de uso geral cujo hardware pode ser configurado para atender especificações. Com os PLDs, sistemas digitais poderiam ser projetados a partir de CIs genéricos, com funções definidas a partir de configurações armazenadas em memórias. Desta forma, os PLDs possuem as seguintes vantagens sobre sistemas de lógica fixa [2]:

Uma alternativa de projeto é o uso de microcontroladores, dispositivos programáveis a nível de software. Porém, mesmo nesses casos, os PLDs possuem vantagens [3]:

Em função da arquitetura e tecnologia empregada, os PLDs foram classificados em SPLDs (simple PLDs) ou CPLDs (complex PLDs). SPLDsSão denominados SPLDs os seguintes dispositivos:

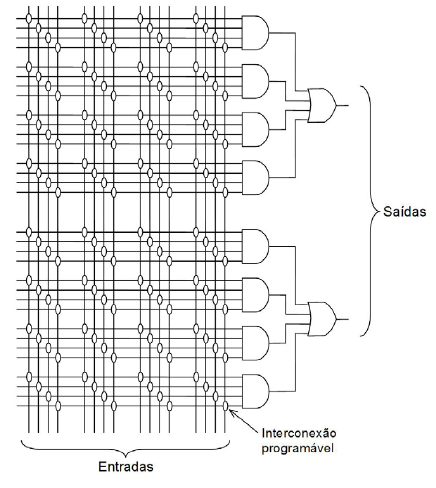

Um arranjo programável de portas AND seguido por um arranjo fixo de portas OR.

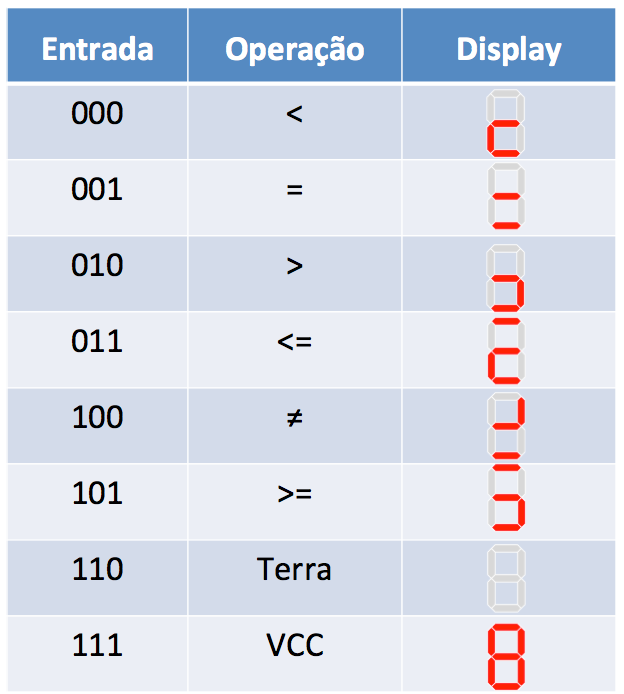

Essa foi a primeira implementação de PLDs, e se baseia no fato de que qualquer função lógica pode ser reescrita como uma soma de produtos (SOP - sum of products) [4]. Por exemplo, sendo abaixo a tabela verdade da soma aritmética de um bit u de uma posição de um circuito somador, como função de x e y e do carry ci

Sendo as linhas 2, 3, 5 e 8, as que possuem saída 1, podemos escrever u como [5]:

Muito semelhante aos PALs, os PLA diferenciam-se no fato de que tanto as ligações AND quanto OR são programáveis.

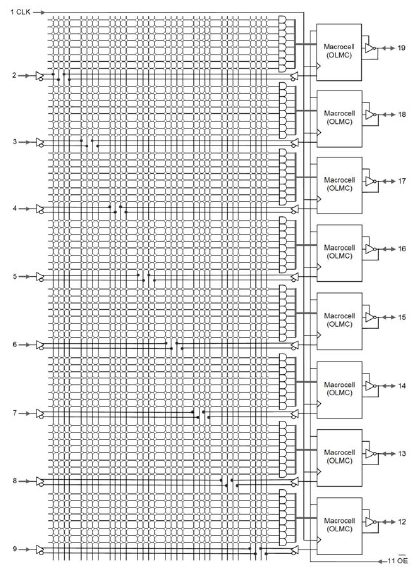

Características adicionais com relação aos PALs:

Um exemplo dessa arquitetura pode ser visto na figura abaixo:

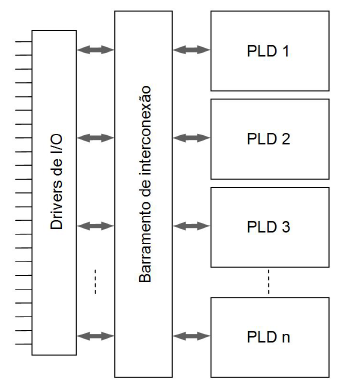

CPLDsComo o próprio nome já adianta, os CPLDs possuem arquitetura muito mais complexa que os SPLDs. De fato, os primeiros CPLDs eram formados pela interconexão programável de vários SPLDs, além de outros avanços. Na figura abaixo, a arquitetura básica de um CPLD:

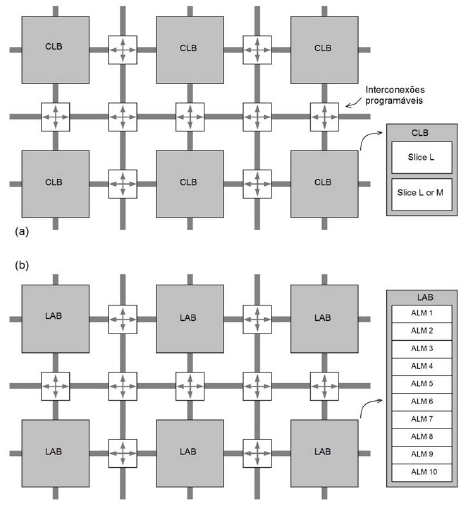

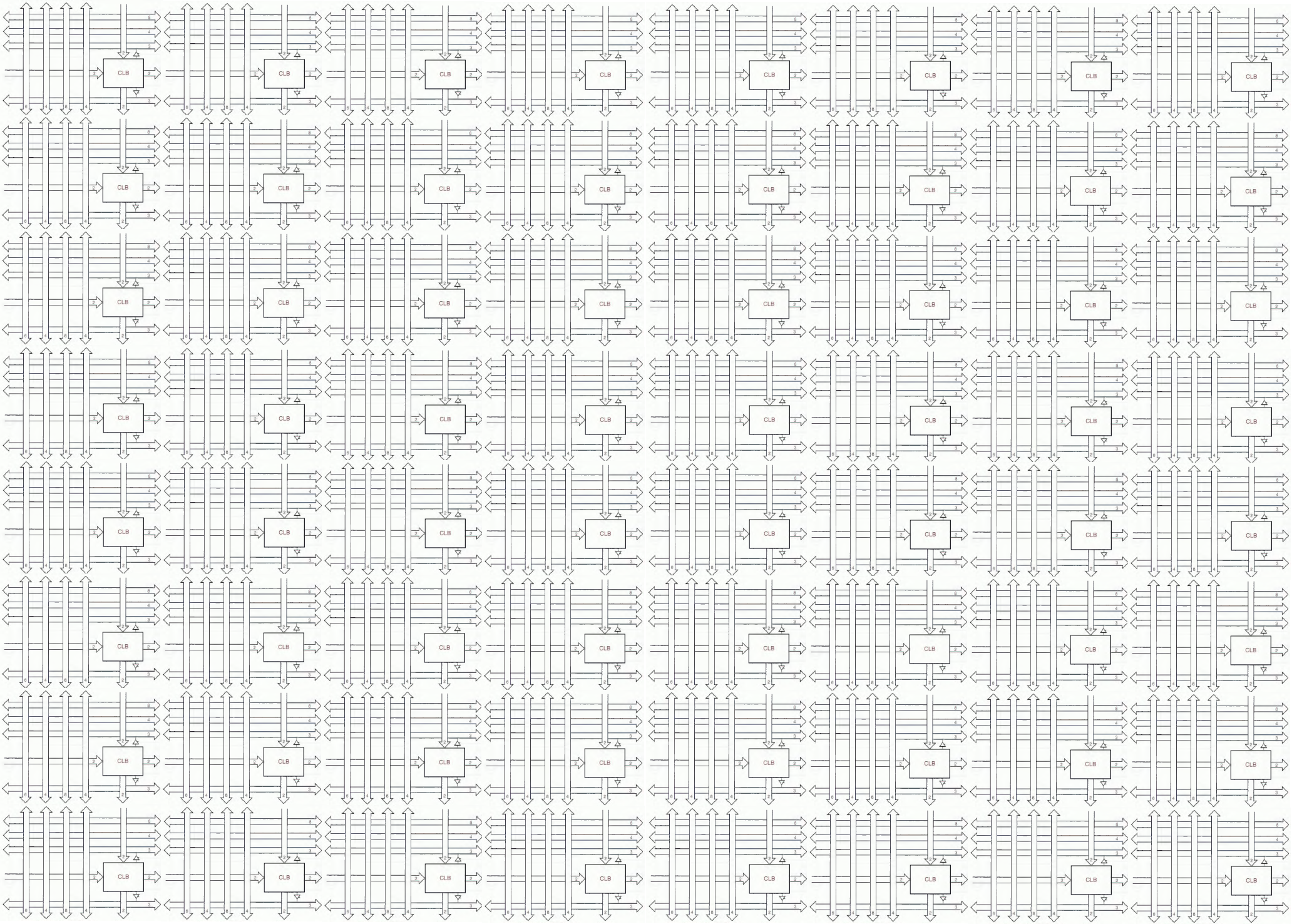

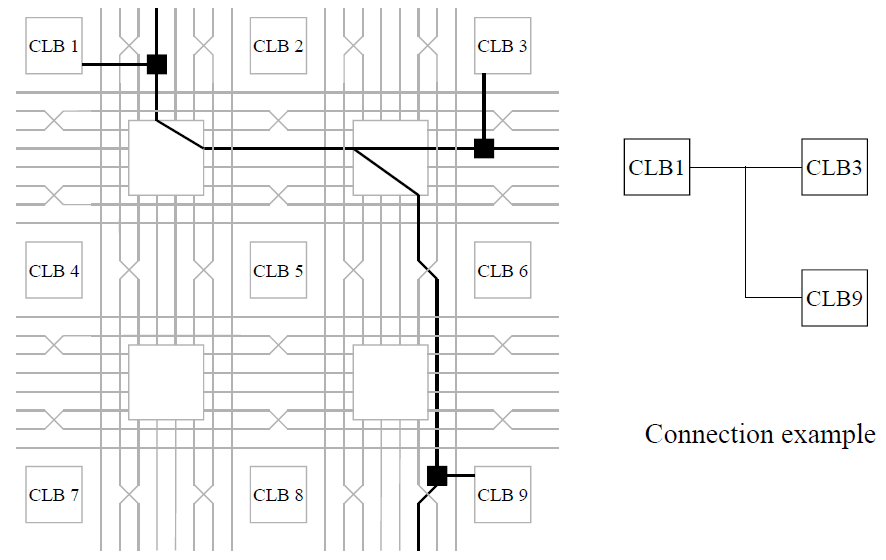

FPGAs - Field programmable gate arrays - Arranjo de portas programável em campoOs FPGAs estendem as capacidades dos CPLDs, sendo diferentes em arquitetura, tecnologia, características embutidas e custo. Por serem voláteis, precisam de uma memória de configuração não volátil para armazenar a programação do hardware. Uma simplificação da arquitetura de FPGAs pode ser vista na figura abaixo. No caso, CLBs (configurable logic blocks) e LABs (logic array blocks) são blocos semelhantes à SPLDs GAL.

Além desses blocos, FPGAs costumam possuir também:

Comparação entre dispositivosUma comparação entre os dispositivos vistos nesta aula pode ser vista na figura abaixo:

onde as características de armazenamento do programa são:

Informações complementares

Referências

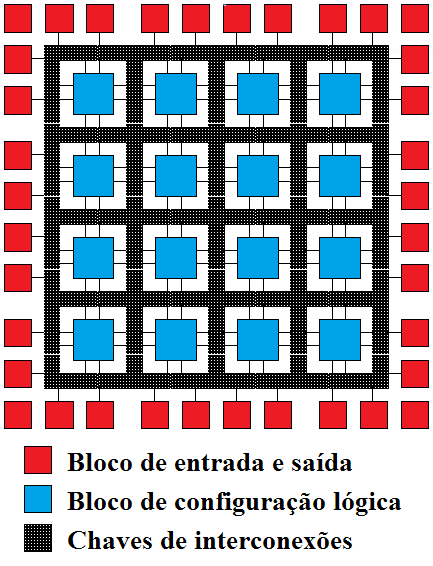

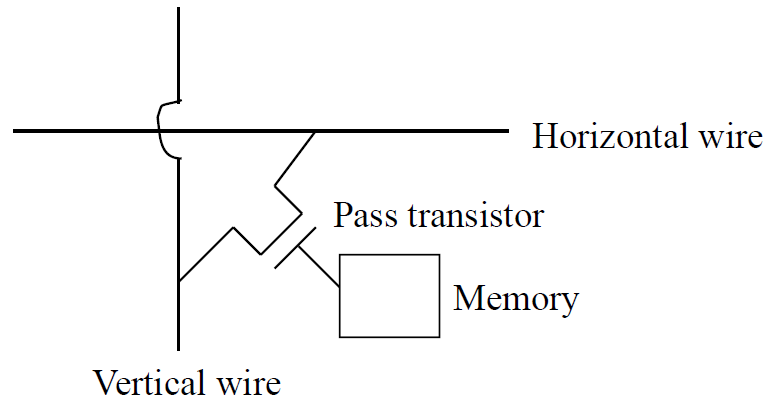

Tecnologia de FPGAOs FPGAs são compostos por três tipos de componentes:

Os 3 blocos são interconectados em duas dimensões, otimizando as conexões entre os blocos

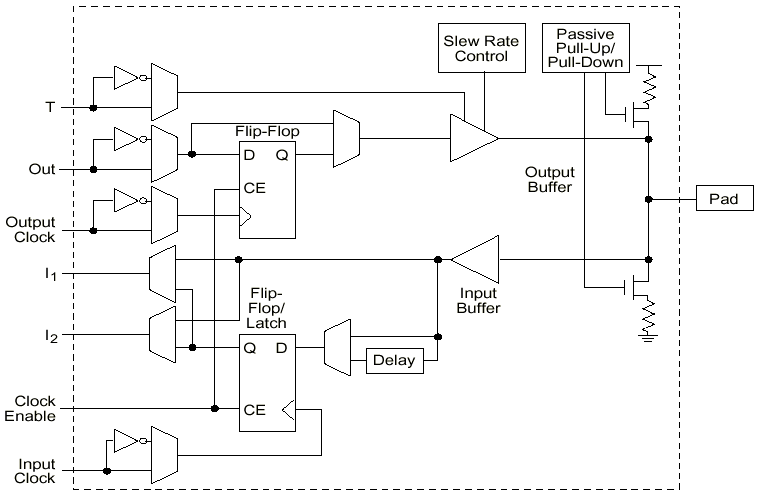

IOBSão usados para fazer a interface de entrada e saída do FPGA. Consiste em um buffer de entrada e um de saída, ambos com flip-flops, permitindo que saídas com clocks sejam disponibilizadas sem encontrar atrasos significantes e reduzindo a necessidade de manter sinais de entrada por muito tempo.

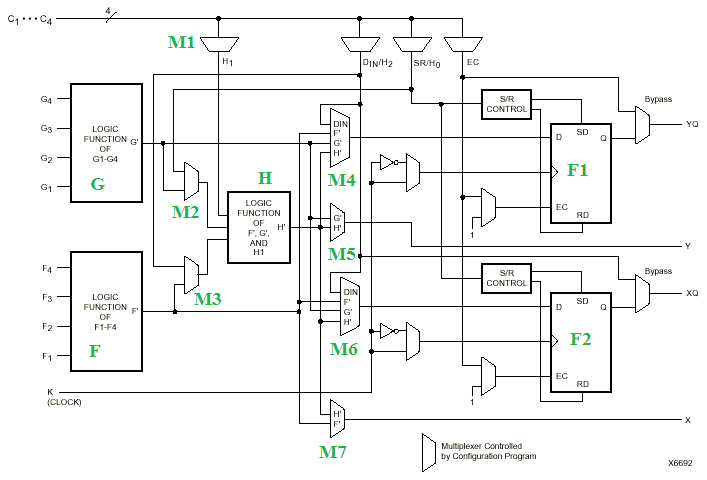

CLB [3]Contêm a lógica do FPGA, como mostra a simplificação abaixo:

Neste bloco:

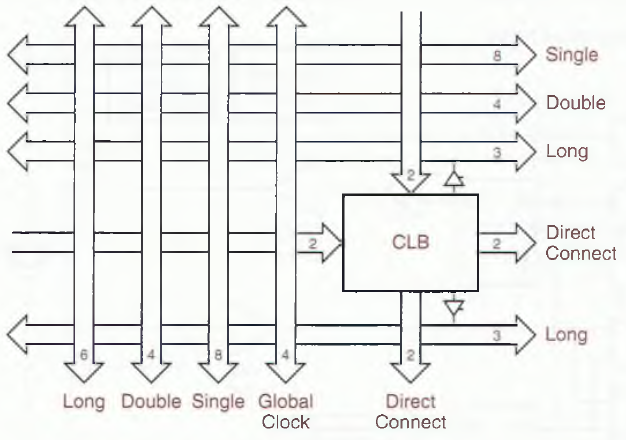

As funções lógicas são implementadas a partir de suas tabelas verdade nos elementos lógicos usando uma memória chamada de Lookup Table (LUT). Com isso, um bloco de configuração lógica também pode ser usado como uma memória, em diferentes configurações dependendo dos multiplexadores. Nesses casos, as entradas F1 a F4 e G1 a G4 fornecem endereços, e as entradas C1 a C4 fornecem os dados e sinais de enable. Chaves de interconexõesOs CLBs estão imersos numa rede de interconexões configuráveis. As conexões possíveis por cada bloco lógico podem ser vistas na figura abaixo.

Um FPGA com 64 blocos de configuração lógica seriam a repetição dessa figura numa matriz de 8x8

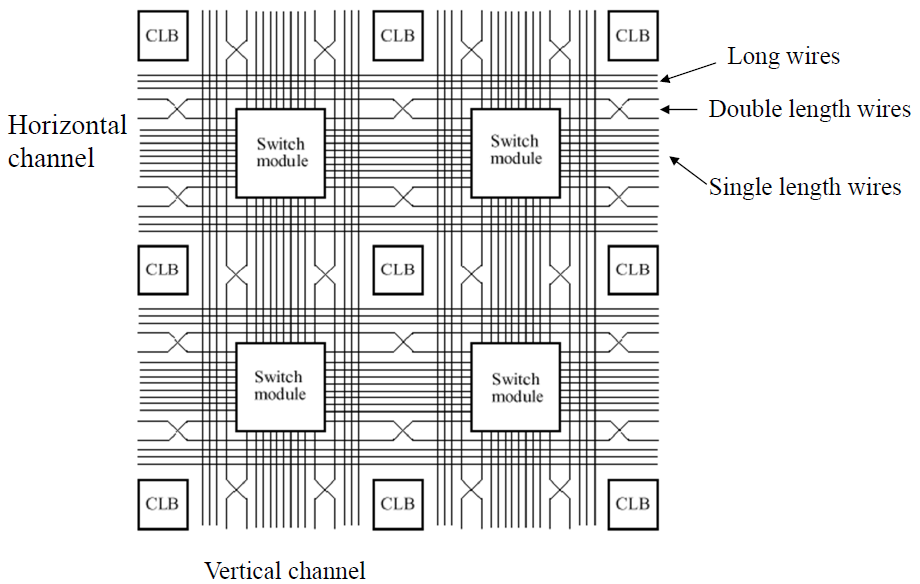

Para fazer a ligação entre CLBs vizinhos, o caminho unidirecional direct pode ser utilizado. Porém, para o roteamento de dados em maiores "distâncias", 3 outros caminhos são disponíveis, dispostos como a figura abaixo:

Na figura, uma Matriz de Comutação Programável (Programmable Switch Matrix - PSM) pode ser vista, além dos 3 caminhos indiretos:

Os blocos PSM introduzem atraso na propagação do sinal no FPGA. Os 3 caminhos introduzem versatilidade ao balancear atrasos e propagação em longas distâncias. O bloco PSM efetua a conexão entre pinos seguindo o esquema da figura abaixo. No esquema, os círculos vermelhos são chamados de Elementos de Comutação Programável (Programmable Switch Element - PSE).

Com isso, várias formas de conexão são possíveis, como exemplifica a figura a seguir:

NOTA: Os nomes dos blocos disponíveis nesta aula seguem os termos utilizados pela Xilinx, e os blocos referem-se a

uma família específica, a XC4000E. Para fabricantes diferentes, ou mesmo famílias diferentes, mudanças podem

ser observadas. Para informações sobre a arquitetura dos FPGAs da Altera, consultar [7].

Tabela comparativa entre FPGAsA tabela a seguir é um exemplo de dados de fabricantes, no caso, da Xilinx.

Informações complementares (Altera)Toda a arquitetura apresentada aqui foi baseada nos dispositivos fabricados pela Xilinx. Como dito acima, mais informação sobre dispositivos Altera pode ser encontrada na referência [7], além do curso abaixo:

Referências

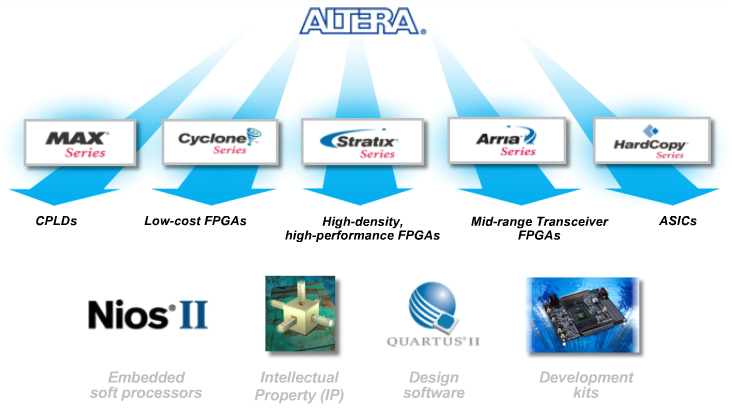

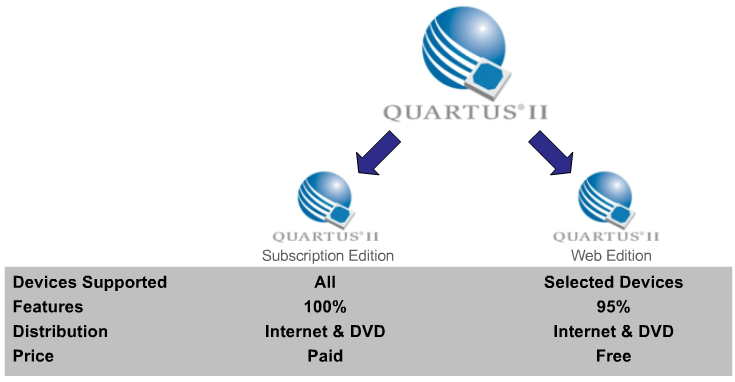

Projetos em FPGAAlteraA Altera é uma das maiores fabricantes de FPGAs e CPLDs. Há no seu portfólio PLDs dos mais baixo custo até dos mais avançados do mercado. O Quartus II é o software de desenvolvimento de PLDs da Altera.

LicençaA licença de uso é dada da seguinte forma:

Uma comparação entre as edições Web e Full está disponível em Link. Para configurar uma licença, acessar Link. A licença Web é gerada em Link. Acesso ao Quartus IIPara acessar o Quartus II, ver página (Uso do Quartus II nos Labs do IFSC). Para acesso ao Quartus II via servidor Cloud, ver página (Acesso ao IFSC-CLOUD) Como obter informaçõesA Altera preparou uma série de materiais sobre o desenvolvimento usando o Quartus II. Existem cursos on-line e presenciais, pagos e gratuitos:

Quartus IIAbaixo, um roteiro para o reconhecimento do software da Altera:

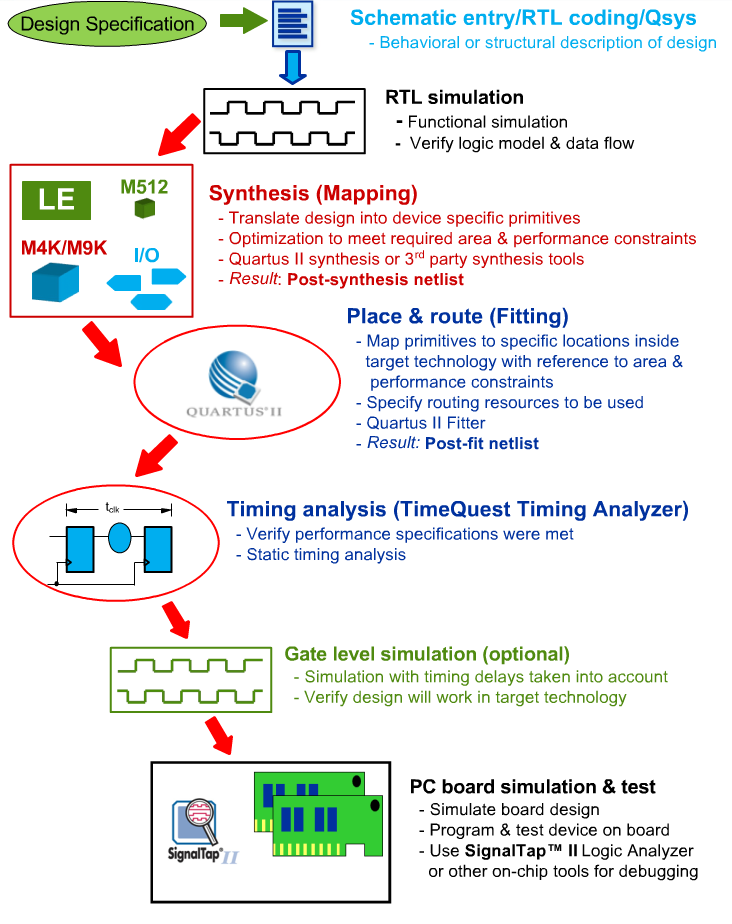

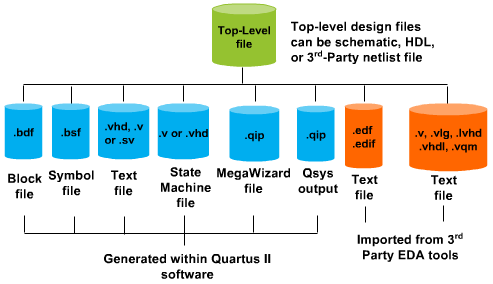

Fluxo de desenvolvimento em PLDs

Projeto no Quartus II

Formas de desenvolvimentoIr em File -> New, e selecionar um dos Design Files disponíveis.

Nesta aula, usaremos o desenvolvimento via Esquemático - Block File.

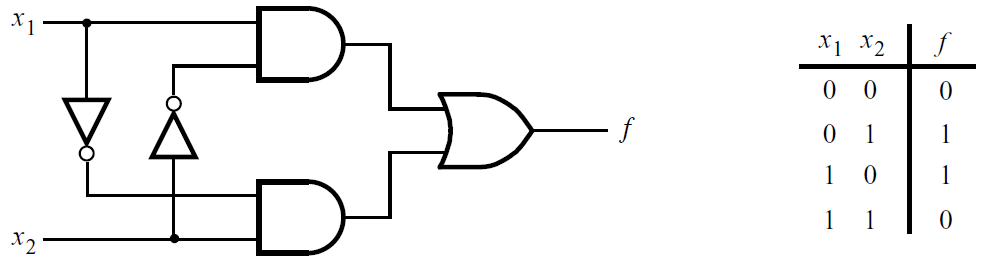

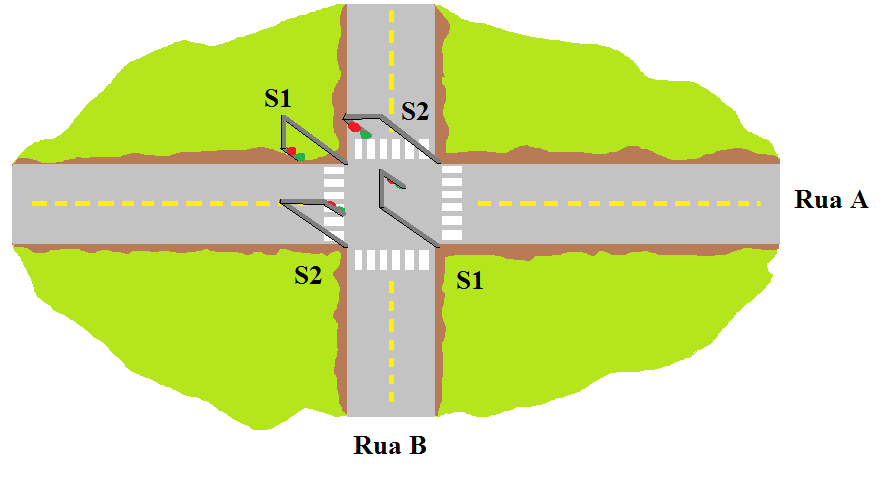

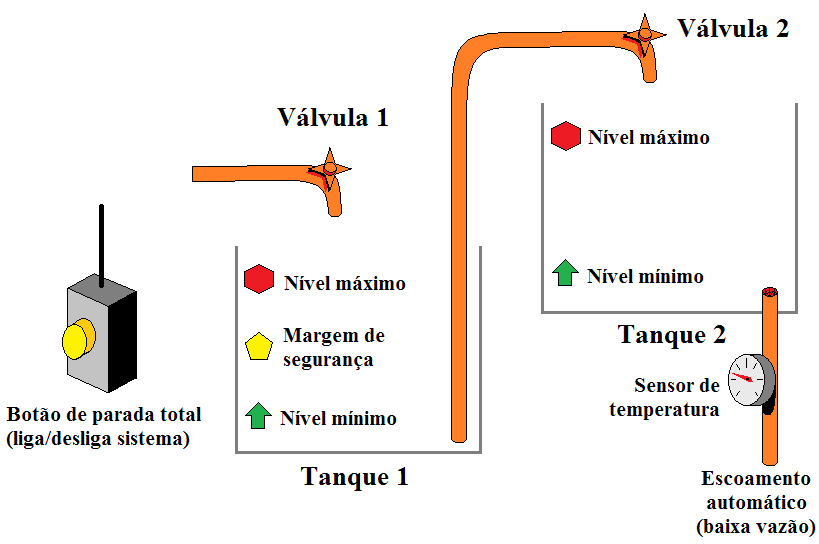

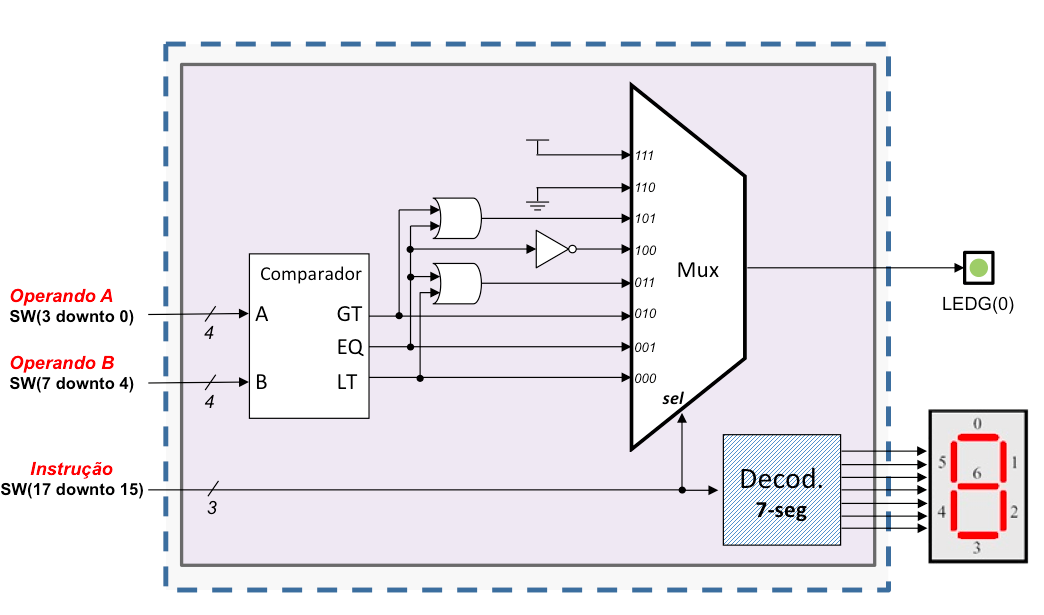

Desenvolvimento via esquemáticoUm exemplo de sistema será usado para apresentar a ferramenta. O sistema que será desenvolvido está disponível na figura abaixo:

O desenvolvimento é feito a partir dos seguintes passos:

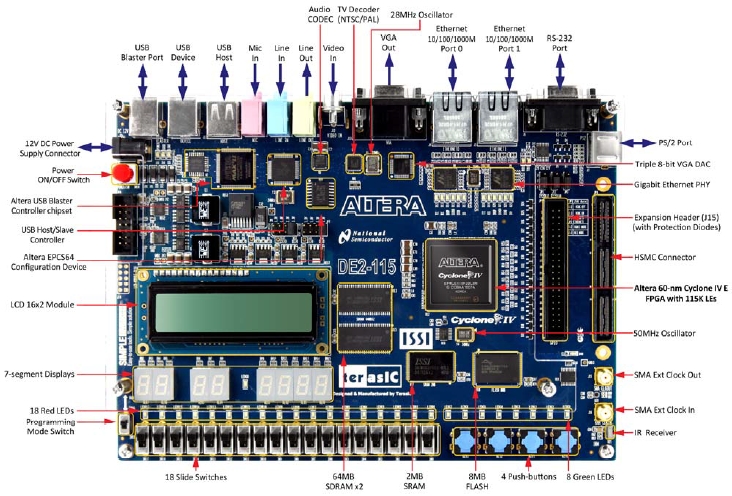

Utilizando o FPGAO kit DE2-115O Kit Altera DE2-115 pode ser visto na figura abaixo.

Algumas características do kit:

Informações sobre kits da AlteraVeja abaixo um resumo dos kits da Altera mais comumente utilizados. Informação importante e constantemente utilizada é a distribuição da pinagem do FPGA no kit.

Exercício 1 - EsquemáticoExecutar o roteiro disponível em Link. São informações complementares ao roteiro:

Outros exercícios

Referências

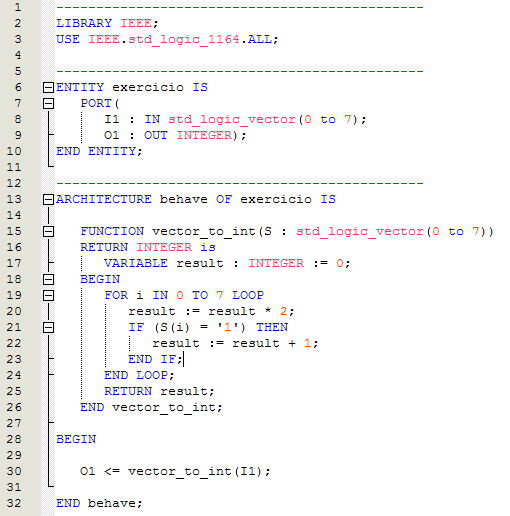

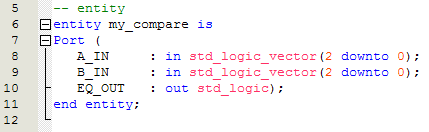

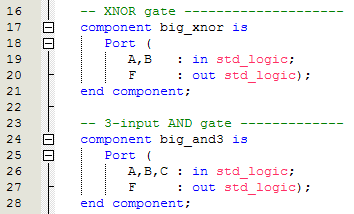

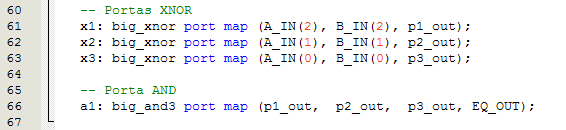

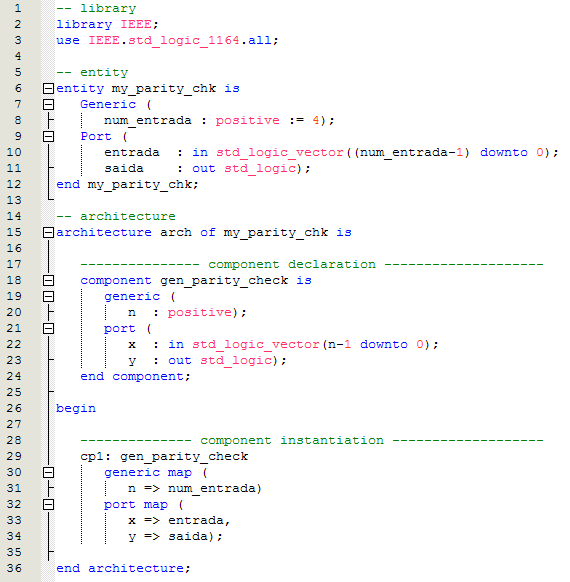

Introdução ao VHDLVHDL vem de VHSIC (Very High Speed Integrated Circuito) Hardware Description Language. É a linguagem padrão IEEE para a descrição de hardware na indústria.

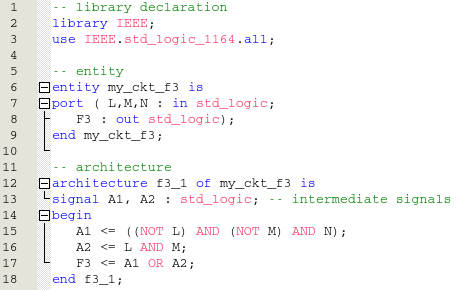

Unidades do código VHDLO código VHDL é inicialmente dividido em 3 seções: PACKAGE ENTITY ARCHITECTURE PACKAGEDeclara as bibliotecas utilizadas no sistema. Usa o formato:

Duas LIBRARYs disponibilizadas automaticamente:

A declaração do pacote IEEE ficaria assim:

ENTITYDefine a visão externa do modelo (símbolo). Usa o formato:

onde:

ARCHITECTUREDefine a função do modelo (esquemático). Segue o formato:

onde:

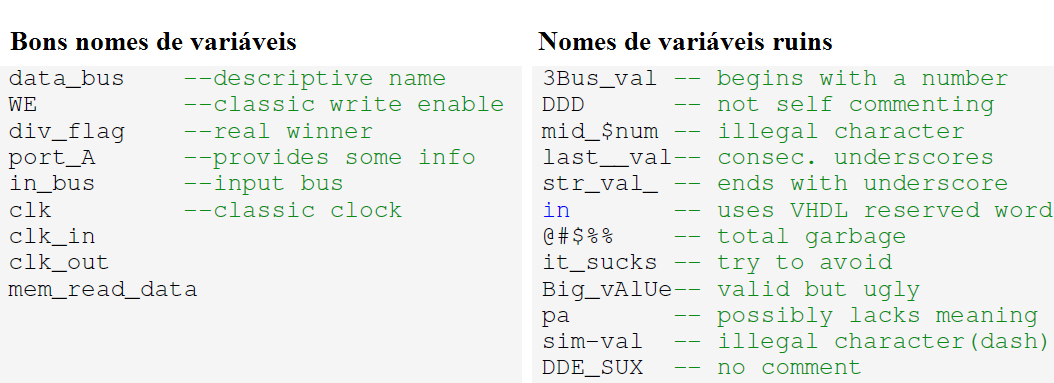

Nomes para identificadoresOs identificadores das entidades, arquiteturas e portas devem ser compactos e informativos. Abaixo, exemplos de nomes bons e ruins.

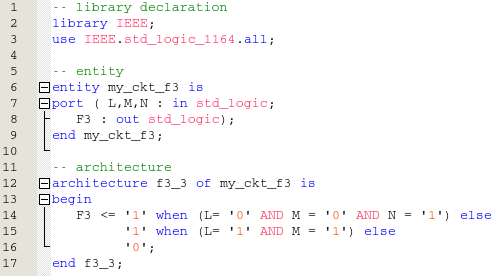

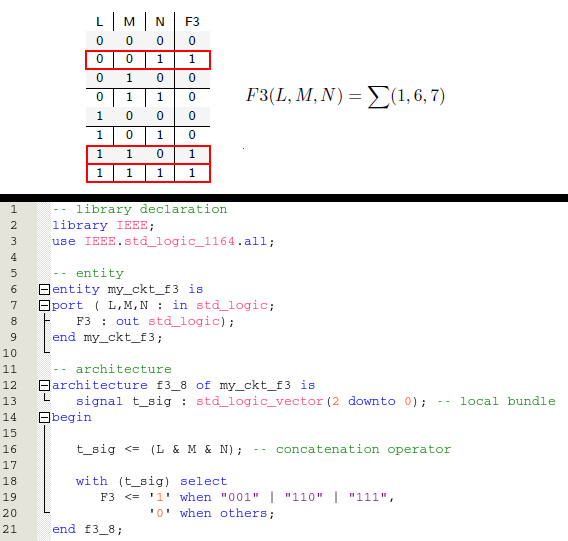

Desenvolvimento via VHDLUm exemplo de sistema será usado para apresentar o Quartus II e o VHDL. O sistema que será desenvolvido está disponível na figura abaixo:

O desenvolvimento é feito a partir dos seguintes passos:

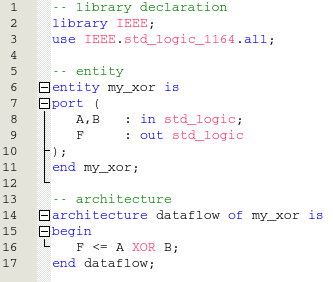

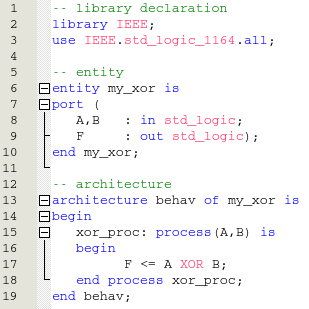

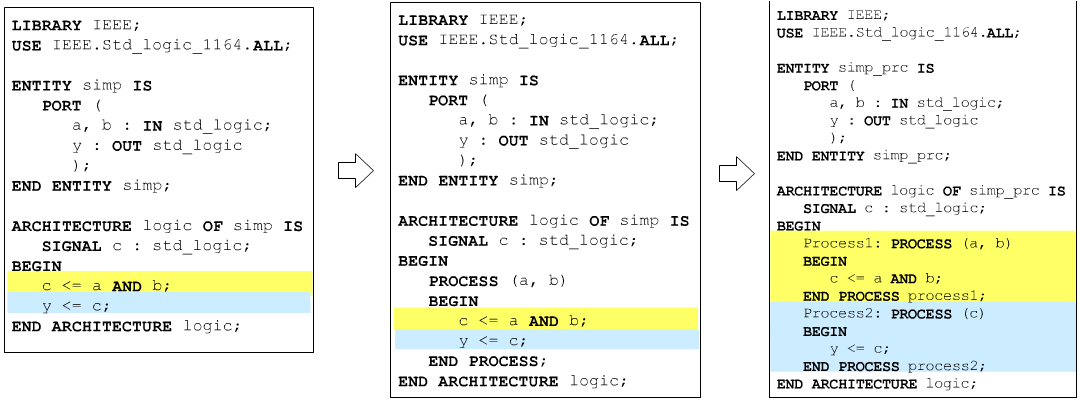

Concorrência do códigoOs código VHDL tem uma característica importante que é a concorrência. Assim, todas as instruções tem a mesma procedência, diferentemente das linguagens de programação. O exemplo abaixo demonstra isso:

A solução do problema pode ser vista abaixo:

Erros clássicosEm desenvolvimento com VHDL, são comuns os seguintes erros [3]:

Tarefa - Introdução ao VHDLLer os capítulos 1, 2 e 3 do livro [4], resolvendo os exercícios do capítulo 3. Referências

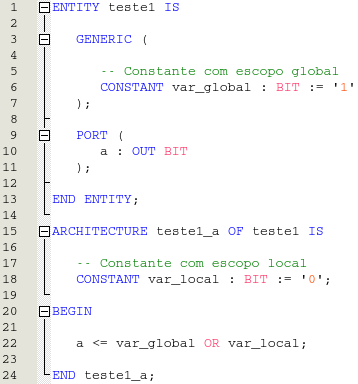

Objetos e atribuiçõesObjetosHá quatro tipos de objetos em VHDL: CONSTANT, SIGNAL, VARIABLE e FILE. Vamos ver agora os dois primeiros [1]. CONSTANTÉ uma forma de atribuir um valor constante a um nome. Não pode então ser alterada durante a execução. É utilizada para melhorar:

A declaração segue o formato:

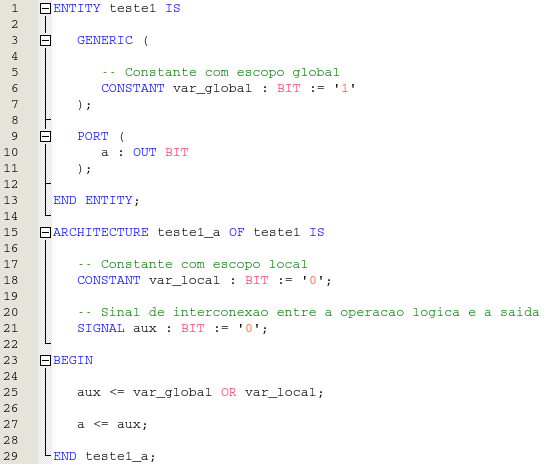

SIGNALRepresenta a interconexão entre blocos. É declarada da seguinte forma:

Um valor inicial é opcionalmente passado ao objeto, da seguinte forma:

Bit e múltiplos bitsNa atribuição de valores binários, há diferenças de declaração entre um único bit ou múltiplos bits:

IndexaçãoÉ possível atribuir valores à membros específicos de um barramento (vetor). Abaixo, alguns exemplos ilustrativos:

É possível ainda usar vírgulas e os operadores OTHERS e => para fazer atribuições específicas [2]:

Bases numéricasÉ possível atribuir à barramentos valores em bases numéricas diferentes. Para isso, o seguinte formato pode ser usado:

Atribuições simultâneasUma das maiores diferenças de VHDL para linguagens de programação de software é que as atribuições do código VHDL são simultâneas. De fato, todas as atribuições dentro de uma arquitetura representam processos implícitos que executam em paralelo. Quando um sinal de entrada do processo é alterado, o novo valor é imediatamente atribuído à variável. São três os tipos de atribuições simultâneas no VHDL: SimplesSão da forma:

No exemplo abaixo, há dois processos implícitos, cujas atribuições de sinais são feitas simultaneamente:

CondicionalSão da forma:

O exemplo abaixo representa dois multiplexadores (A e B) em série, onde:

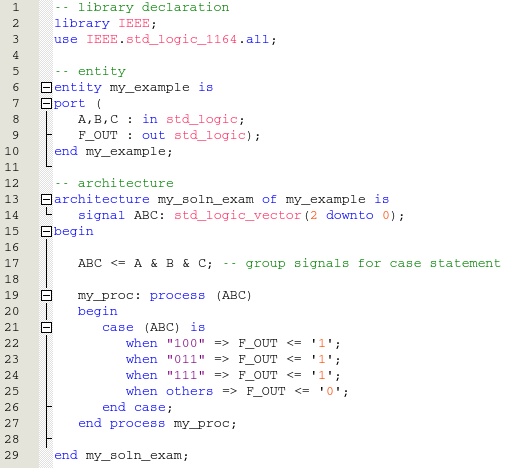

De certa forma, o operador condicional é semelhante ao operador if em linguagens de programação de software. De seleçãoSão da forma: