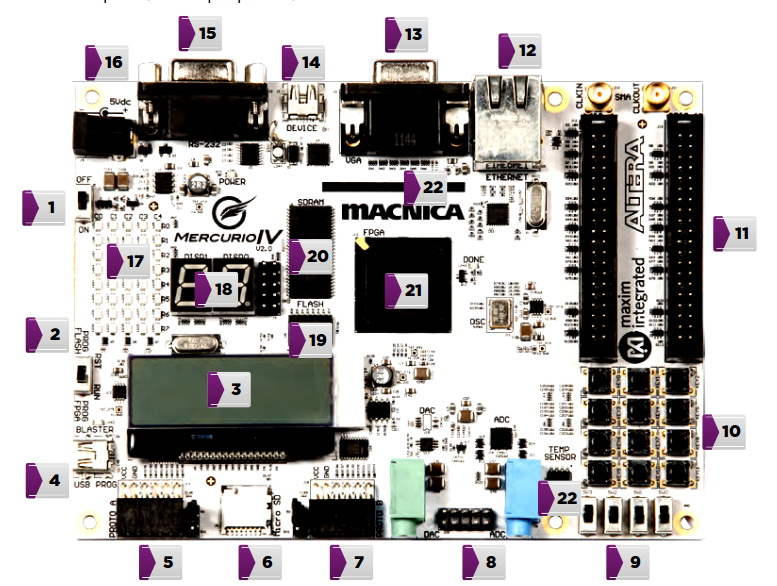

Pinagem dos dispositivos de entrada e saída do kit MERCURIO IV

Para encontrar as informações completas sobre o kit Mercurio IV consulte diretamente o Manual do Usuário, [1] e o Diagrama Esquemático, [2] do fabricante. Para facilitar o acesso as informações mais utilizadas nos projetos didáticos, são listadas a seguir alguns dos pinos e sua ligação externa no kit.

Family=Cyclone IV E, device=EP4CE30F23C7

O FPGA que equipa a placa Mercurio IV é uma Cyclone IV EP4CE30F23, a qual possui 30 mil elementos lógicos.

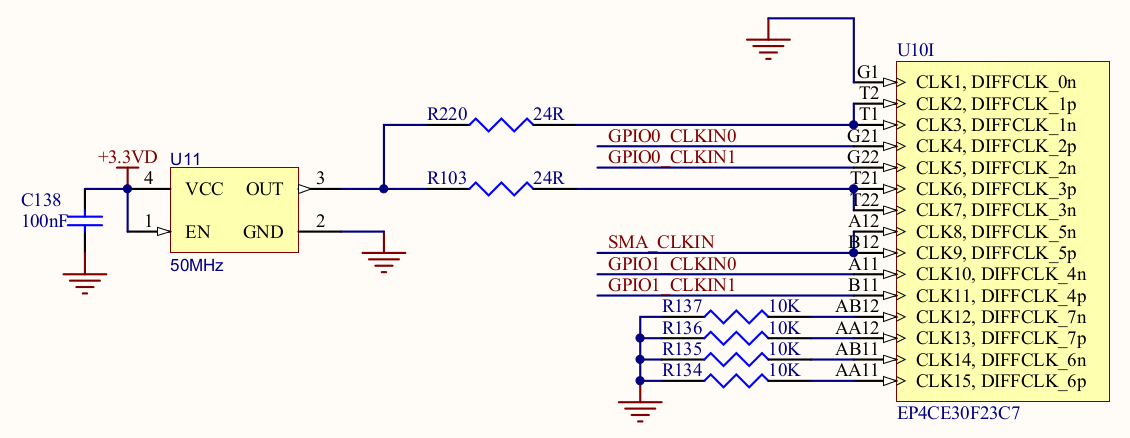

1 Clock

O clock de entrada do FPGA é de 50 MHz. O sinal de CLOCK_50MHZ está disponível nos pinos T1, T2, T21 e T22 do FPGA. Um clock externo diferente pode ser conectado ao FPGA através do conector SMA (SMA_CLKIN), e da mesma forma um clock internamente gerado por ser conectado o conector SMA (SMA_CLKOUT).

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| CLOCK_50MHz | PIN_T1 | 50 MHz clock input | 3.3V |

| CLOCK1_50MHz | PIN_T2 | 50 MHz clock input | 3.3V |

| CLOCK2_50MHz | PIN_T21 | 50 MHz clock input | 3.3V |

| CLOCK3_50MHz | PIN_T22 | 50 MHz clock input | 3.3V |

| SMA_CLKIN | PIN_A12 | SMA clock input | 3.3V |

| SMA_CLKIN1 | PIN_B12 | SMA clock input | 3.3V |

| SMA_CLKOUT | PIN_E6 | SMA clock outpur | 3.3V |

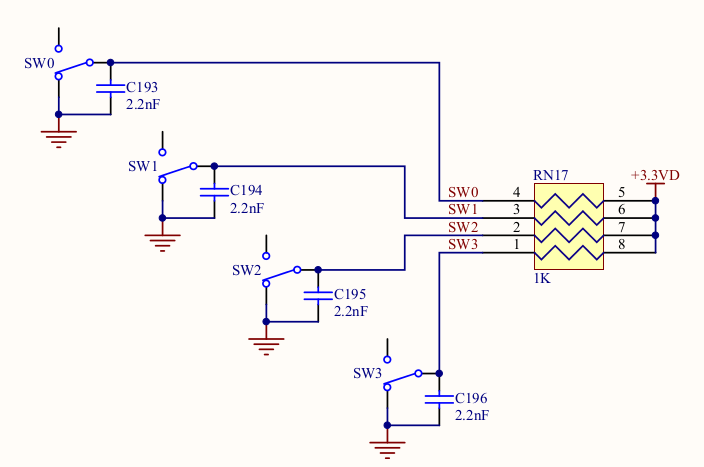

2 Chaves

A placa Mercurio® IV possui quatro chaves do tipo Slide Switch que são conectadas diretamente ao FPGA. Se a chave estiver posicionada na parte de baixo, o nível lógico na porta do FPGA será ‘0’, se a chave estiver posicionada para cima o nível lógico produzido será ‘1’. Elas estão ligadas a filtros RC, porém, mesmo assim, pode ser interessante implementar um processo de debounce do sinal, a fim de evitar glitches na troca de posição das chaves.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| SW[0] | PIN_V21 | Chave tipo Slide Switch 3 | 3.3V |

| SW[1] | PIN_W22 | Chave tipo Slide Switch 2 | 3.3V |

| SW[2] | PIN_W21 | Chave tipo Slide Switch 1 | 3.3V |

| SW[3] | PIN_Y22 | Chave tipo Slide Switch 0 | 3.3V |

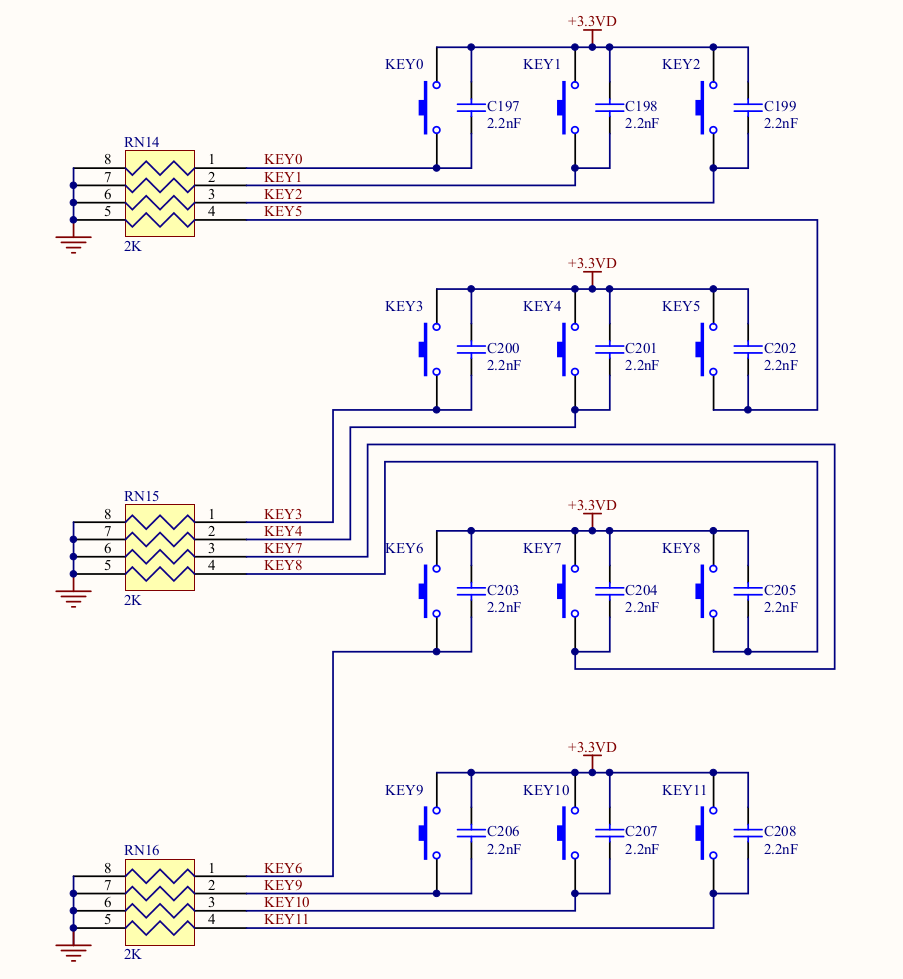

3 Teclado numérico

Na placa Mercurio IV existe uma organização de 12 botões do tipo push button que estão arranjados de forma a simular um teclado telefônico. Os botões não pressionados geram sinal de nível Lógico baixo na entrada do FPGA, e quando apertados geram um pulso de nível lógico alto.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| KEY[0] | PIN_V22 | Botão tipo Push Button 0 | 3.3V |

| KEY[1] | PIN_U20 | Botão tipo Push Button 1 | 3.3V |

| KEY[2] | PIN_U22 | Botão tipo Push Button 2 | 3.3V |

| KEY[3] | PIN_U16 | Botão tipo Push Button 3 | 3.3V |

| KEY[4] | PIN_W20 | Botão tipo Push Button 4 | 3.3V |

| KEY[5] | PIN_U21 | Botão tipo Push Button 5 | 3.3V |

| KEY[6] | PIN_V15 | Botão tipo Push Button 6 | 3.3V |

| KEY[7] | PIN_W17 | Botão tipo Push Button 7 | 3.3V |

| KEY[8] | PIN_W19 | Botão tipo Push Button 8 | 3.3V |

| KEY[9] | PIN_W15 | Botão tipo Push Button 9 | 3.3V |

| KEY[10] | PIN_U17 | Botão tipo Push Button 10 | 3.3V |

| KEY[11] | PIN_Y17 | Botão tipo Push Button 11 | 3.3V |

4 Placa de Expansão com 16 chaves

A Mercurio IV é acompanhada de uma placa de expansão com 16 chaves, dispostas em dois grupos de 8. O grupo da esquerda posicionado sobre o conector de GPIO compreede as chaves do grupo A (SA[0..7]), e as da direita as chaves do grupo B (SB[0..7]). Estas chaves estão ligadas a um filtro RC, porém ainda é indicado utilizar processos de eliminação de repique para evitar a introdução de glitches na FPGA. A placa pode ser conectada em uma das interfaces GPIO, porém é recomendado utilizar a interface GPIO0 (o conector "DE DENTRO") para evitar a inversão da placa, o que pode levar a problemas de sobretensão por haver um sinal de 5V no GPIO0.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| SA[0] | PIN_E16 | Chave tipo Slide Switch 0 | 3.3V |

| SA[1] | PIN_H22 | Chave tipo Slide Switch 1 | 3.3V |

| SA[2] | PIN_F16 | Chave tipo Slide Switch 2 | 3.3V |

| SA[3] | PIN_F19 | Chave tipo Slide Switch 3 | 3.3V |

| SA[4] | PIN_H21 | Chave tipo Slide Switch 4 | 3.3V |

| SA[5] | PIN_J22 | Chave tipo Slide Switch 5 | 3.3V |

| SA[6] | PIN_F20 | Chave tipo Slide Switch 6 | 3.3V |

| SA[7] | PIN_H19 | Chave tipo Slide Switch 7 | 3.3V |

| SB[0] | PIN_J21 | Chave tipo Slide Switch 0 | 3.3V |

| SB[1] | PIN_K21 | Chave tipo Slide Switch 1 | 3.3V |

| SB[2] | PIN_H20 | Chave tipo Slide Switch 2 | 3.3V |

| SB[3] | PIN_H18 | Chave tipo Slide Switch 3 | 3.3V |

| SB[4] | PIN_L22 | Chave tipo Slide Switch 4 | 3.3V |

| SB[5] | PIN_L21 | Chave tipo Slide Switch 5 | 3.3V |

| SB[6] | PIN_J18 | Chave tipo Slide Switch 6 | 3.3V |

| SB[7] | PIN_M21 | Chave tipo Slide Switch 7 | 3.3V |

5 Matriz de Leds

A matriz de LEDs da placa Mercurio IV é composta por oito linhas e cinco colunas de LEDs, conforme a Figura 13. Cada linha e cada coluna está conectada a um pino do FPGA, portanto, para acender apenas o LED superior esquerdo, por exemplo, é necessário colocar a linha superior e a coluna esquerda em nível baixo, os demais sinais devem permanecer em nível alto (lógica invertida). Ou seja, o acesso à matriz deve ser multiplexado, ou por linhas ou por colunas.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| LEDM_C[0] | PIN_J7 | Coluna 0 da matriz de LEDs | 3.3V |

| LEDM_C[1] | PIN_J6 | Coluna 1 da matriz de LEDs | 3.3V |

| LEDM_C[2] | PIN_K8 | Coluna 2 da matriz de LEDs | 3.3V |

| LEDM_C[3] | PIN_J8 | Coluna 3 da matriz de LEDs | 3.3V |

| LEDM_C[4] | PIN_L8 | Coluna 4 da matriz de LEDs | 3.3V |

| LEDM_R[0] | PIN_F10 | Linha 0 da matriz de LEDs | 3.3V |

| LEDM_R[1] | PIN_C8 | Linha 1 da matriz de LEDs | 3.3V |

| LEDM_R[2] | PIN_E9 | Linha 2 da matriz de LEDs | 3.3V |

| LEDM_R[3] | PIN_G9 | Linha 3 da matriz de LEDs | 3.3V |

| LEDM_R[4] | PIN_F9 | Linha 4 da matriz de LEDs | 3.3V |

| LEDM_R[5] | PIN_F8 | Linha 5 da matriz de LEDs | 3.3V |

| LEDM_R[6] | PIN_G8 | Linha 6 da matriz de LEDs | 3.3V |

| LEDM_R[7] | PIN_H11 | Linha 7 da matriz de LEDs | 3.3V |

- Datasheet

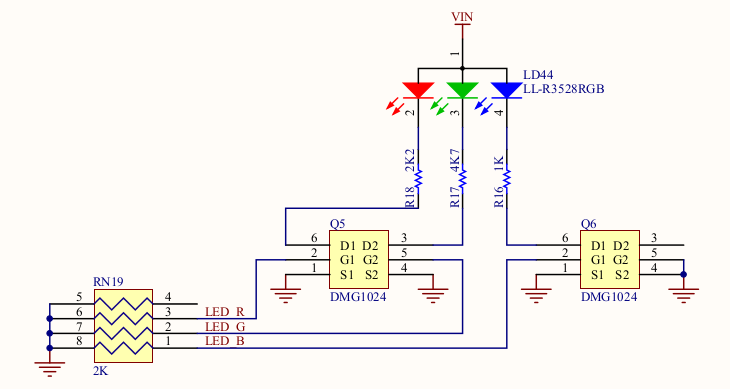

6 Led RGB

O LED RGB de alto brilho possui três elementos internos, o vermelho, o verde e o azul. Esses três elementos são utilizados para que o LED possa emitir sete cores diferentes:

- Vermelho – elemento R;

- Verde – elemento G;

- Azul – elemento B;

- Amarelo – elementos R e G;

- Ciano – elementos G e B;

- Magenta – elementos R e B;

- Branco – elementos R, G e B.

Cada elemento possui um pino associado, sendo os três elementos conectados ao FPGA e o pino comum é conectado ao VCC. Assim o FPGA pode ativar ou desativar cada elemento do LED RGB colocando ‘0’ no pino associado, sendo possível gerar as sete cores do LED.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| LED_R | PIN_D7 | Elemento vermelho do LED RGB | 3.3V |

| LED_G | PIN_D6 | Elemento verde do LED RGB | 3.3V |

| LED_B | PIN_E7 | Elemento azul do LED RGB | 3.3V |

- Datasheets

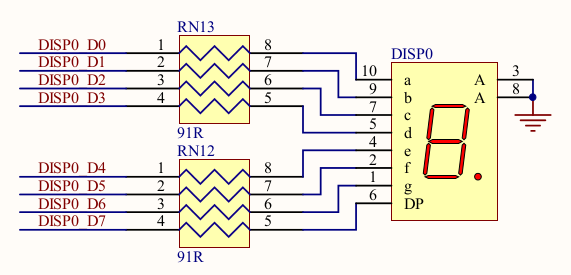

7 Display de 7 segmentos

Na placa Mercurio IV existem dois displays de 7 segmentos arranjados um ao lado do outro, para ser possível exibir um número com dois algarismos. O display DISP0 fica a direita e o DISP1 a esquerda. Cada display possui um barramento de oito sinais ligado no FPGA, sete sinais para os segmentos e um sinal para o ponto decimal. Os displays são do tipo Catodo Comum, portanto, nível ‘1’ no pino de entrada acende o segmento do display e nível ‘0’ apaga o segmento.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| DISP0_D[0] | PIN_V2 | Segmento A - Display 0 | 3.3V |

| DISP0_D[1] | PIN_V1 | Segmento B - Display 0 | 3.3V |

| DISP0_D[2] | PIN_U2 | Segmento C - Display 0 | 3.3V |

| DISP0_D[3] | PIN_U1 | Segmento D - Display 0 | 3.3V |

| DISP0_D[4] | PIN_Y2 | Segmento E - Display 0 | 3.3V |

| DISP0_D[5] | PIN_Y1 | Segmento F - Display 0 | 3.3V |

| DISP0_D[6] | PIN_W2 | Segmento G - Display 0 | 3.3V |

| DISP0_D[7] | PIN_W1 | Ponto decimal - Display 0 | 3.3V |

| DISP1_D[0] | PIN_R5 | Segmento A - Display 1 | 3.3V |

| DISP1_D[1] | PIN_T5 | Segmento B - Display 1 | 3.3V |

| DISP1_D[2] | PIN_T3 | Segmento C - Display 1 | 3.3V |

| DISP1_D[3] | PIN_T4 | Segmento D - Display 1 | 3.3V |

| DISP1_D[4] | PIN_M6 | Segmento E - Display 1 | 3.3V |

| DISP1_D[5] | PIN_N7 | Segmento F - Display 1 | 3.3V |

| DISP1_D[6] | PIN_N6 | Segmento G - Display 1 | 3.3V |

| DISP1_D[7] | PIN_P6 | Ponto decimal - Display 1 | 3.3V |

- Datasheet

8 SDRAM

A placa Mercurio IV possui um chip de SDRAM de 512Mbits (64 MBytes). As tabelas abaixo apresentam as o timming para configuração do controlador de memória e o roteamento dos pinos para a FPGA da placa. Para integração com o NIOS2, é necessário utilizar um PLL para dar um atraso de 3ns na fase do clock encaminhado ao chip de memória.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| SDRAM_A[0] | PIN_P2 | SDRAM Address Bit 0 | 3v3 |

| SDRAM_A[1] | PIN_R1 | SDRAM Address Bit 1 | 3v3 |

| SDRAM_A[2] | PIN_P3 | SDRAM Address Bit 2 | 3v3 |

| SDRAM_A[3] | PIN_R2 | SDRAM Address Bit 3 | 3v3 |

| SDRAM_A[4] | PIN_P4 | SDRAM Address Bit 4 | 3v3 |

| SDRAM_A[5] | PIN_P5 | SDRAM Address Bit 5 | 3v3 |

| SDRAM_A[6] | PIN_N5 | SDRAM Address Bit 6 | 3v3 |

| SDRAM_A[7] | PIN_M4 | SDRAM Address Bit 7 | 3v3 |

| SDRAM_A[8] | PIN_N1 | SDRAM Address Bit 8 | 3v3 |

| SDRAM_A[9] | PIN_M2 | SDRAM Address Bit 9 | 3v3 |

| SDRAM_A[10] | PIN_P1 | SDRAM Address Bit 10 | 3v3 |

| SDRAM_A[11] | PIN_M3 | SDRAM Address Bit 11 | 3v3 |

| SDRAM_A[12] | PIN_L6 | SDRAM Address Bit 12 | 3v3 |

| SDRAM_BA[0] | PIN_J4 | SDRAM Bank Select Bit 0 | 3v3 |

| SDRAM_BA[1] | PIN_H2 | SDRAM Bank Select Bit 1 | 3v3 |

| SDRAM_D[0] | PIN_B2 | SDRAM Data Bit 0 | 3v3 |

| SDRAM_D[1] | PIN_B1 | SDRAM Data Bit 1 | 3v3 |

| SDRAM_D[2] | PIN_C2 | SDRAM Data Bit 2 | 3v3 |

| SDRAM_D[3] | PIN_C1 | SDRAM Data Bit 3 | 3v3 |

| SDRAM_D[4] | PIN_D2 | SDRAM Data Bit 4 | 3v3 |

| SDRAM_D[5] | PIN_E3 | SDRAM Data Bit 5 | 3v3 |

| SDRAM_D[6] | PIN_F2 | SDRAM Data Bit 6 | 3v3 |

| SDRAM_D[7] | PIN_F1 | SDRAM Data Bit 7 | 3v3 |

| SDRAM_D[8] | PIN_J2 | SDRAM Data Bit 8 | 3v3 |

| SDRAM_D[9] | PIN_H6 | SDRAM Data Bit 9 | 3v3 |

| SDRAM_D[10] | PIN_H5 | SDRAM Data Bit 10 | 3v3 |

| SDRAM_D[11] | PIN_J3 | SDRAM Data Bit 11 | 3v3 |

| SDRAM_D[12] | PIN_G3 | SDRAM Data Bit 12 | 3v3 |

| SDRAM_D[13] | PIN_G4 | SDRAM Data Bit 13 | 3v3 |

| SDRAM_D[14] | PIN_G5 | SDRAM Data Bit 14 | 3v3 |

| SDRAM_D[15] | PIN_E4 | SDRAM Data Bit 15 | 3v3 |

| SDRAM_DQM[0] | PIN_E1 | SDRAM Byte Enable 0 | 3v3 |

| SDRAM_DQM[1] | PIN_J5 | SDRAM Byte Enable 1 | 3v3 |

| SDRAM_CLK | PIN_E5 | SDRAM Clock In | 3v3 |

| SDRAM_CKE | PIN_M5 | SDRAM Clock Enable | 3v3 |

| SDRAM_CAS_N | PIN_M1 | SDRAM Column Address Strobe (N) | 3v3 |

| SDRAM_CS_N | PIN_H1 | SDRAM Chip Select (N) | 3v3 |

| SDRAM_RAS_N | PIN_N2 | SDRAM Row Address Strobe (N) | 3v3 |

| SDRAM_WE_N | PIN_J1 | SDRAM Write Enable (N) | 3v3 |

- Datasheet

9 Utilizando o display LCD

Na placa Mercurio® IV está instalado um display LCD 16x2 caracteres. Esse display possui um mapa de caracteres, que pode ser utilizado para escrever no display. Além do mapa de caracteres, existe uma memória DDRAM utilizada para o mapeamento do display diretamente, ou seja, existem 32 endereços da DDRAM que seus valores são exibidos no display, segundo o mapa de caracteres.colocado em nível alto quando se deseja realizar uma operação.

A configuração do display e a escrita dos caracteres é feita pelo barramento LCD_DATA[7..0] e pelos sinais LCD_EN, LCD_RS e LCD_RW. LCD_RW em nível alto indica que será feita uma leitura e em nível baixo uma escrita, LCD_RS em nível alto indica que o acesso será feito na memória do display e em nível baixo indica que o acesso será feito num registrador de configuração do display. O sinal LCD_EN é colocado em nível alto quando se deseja realizar uma operação.

Resta então o sinal LCD_BACKLIGHT, que é utilizado para ligar ou desligar o backlight do display

| Nome do sinal | Pino do FPGA | Descrição |

|---|---|---|

| LCD_BACKLIGHT | V10 | Controlador do backlight |

| LCD_EN | V9 | Operation Enable, inicia uma operação com o LCD |

| LCD_RS | U9 | Register Select, seleciona se o acesso é em registrador ('0') ou em memória ('1') |

| LCD_RW | U8 | Read Write, indica se é uma leitura ('1') ou escrita ('0') |

| LCD_D[0] | V8 | Bit 0 do barramento de comando/dado - LSB |

| LCD_D[1] | V7 | Bit 1 do barramento de comando/dado |

| LCD_D[2] | V6 | Bit 2 do barramento de comando/dado |

| LCD_D[3] | V5 | Bit 3 do barramento de comando/dado |

| LCD_D[4] | V4 | Bit 4 do barramento de comando/dado |

| LCD_D[5] | Y4 | Bit 5 do barramento de comando/dado |

| LCD_D[6] | V3 | Bit 6 do barramento de comando/dado |

| LCD_D[7] | Y3 | Bit 7 do barramento de comando/dado - MSB |

10 Utilizando o conversor AD

O conversor analógico-digital do kit Mercurio IV possui duas entradas analógicas diferenciais, ou 4 entradas single ended, dois canais de conversão paralelos e duas saídas digitais seriais. O conversor AD possui resolução de 12 bits e se comunica com o FPGA Cyclone IV através de um barramento serial SPI, que opera nos modos 0 ou 3. O conversor não possui nenhuma entrada no barramento SPI, apenas as saídas relativas a cada canal de conversão, então, o controle do conversor é feito através de alguns sinais digitais de entrada, como ADC_CNVST e ADC_SD.

| Nome do sinal | Pino do FPGA | Descrição |

|---|---|---|

| ADC_CNVST | AB18 | Sinaliza que uma nova conversão deve ser iniciada |

| ADC_CS_N | AA17 | Chip Select |

| ADC_DOUT[0] | AB19 | Saída para conversão no modo single ou para o canal 1 em modo dual |

| ADC_DOUT[1] | AA19 | Saída para o canal 2 em modo dual |

| ADC_REFSEL | AB17 | Define qual será a tensão de referência para ADC |

| ADC_SCLK | AA18 | Clock da comunicação serial |

| ADC_SD | AA16 | Seleção entre os modos single ou dual |

| ADC_UB | AB20 | Seleção entre modo unipolar ou modo bipolar (entradas diferenciais) |

| ADC_SEL | AB16 | Seleciona se serão utilizadas as entradas analógicas primárias ou secundárias (modo unipolar apenas) |

11 Utilizando o conversor DA

O conversor digital-analógico possui dois canais de conversão e duas saídas analógicas, porém possui apenas uma entrada serial, pela qual os dois buffers de conversão são alimentados e todas as configurações do conversão são realizadas. A única entrada digital que não faz parte do barramento SPI é um sinal de clear assíncrono, DAC_CLR_N, que limpa os buffers de conversão, fazendo as duas saídas irem para zero (nível mínimo de tensão). A comunicação SPI do conversor DA pode ser nos modos 1 ou 2. Todo comando enviado para o conversor tem 24 bits de comprimento, portanto, após o sinal DAC_CS_N ir para nível lógico baixo, os 24 bits devem ser enviados pelo pino DAC_DIN que será registrado nas bordas de descida de DAC_SCLK.

| Nome do sinal | Pino do FPGA | Descrição |

|---|---|---|

| DAC_CLR_N | AA15 | Limpa os buffers do conversor, colocando as saídas em zero |

| DAC_CS_N | AB15 | Chip Select |

| DAC_DIN | AB14 | Entrada de dado da comunicação serial |

| DAC_SCLK | AA14 | Clock da comunicação serial |

12 Outros

Na placa Mercurio IV existe um chip SDRAM de 512Mbits conectado à FPGA. O modelo do chip SDRAM é IS42S16320B (ISSI). Ele possui quatro bancos de memória, sendo que cada um possui 8 M x 16 bits. Cada banco é estruturado em 8192 linhas (13 bits para enumerar) e 1024 colunas (10 bits para enumerar).

NOTA: Tabelas wiki geradas com o Tables Generator