SST20707-2015-1 - Avaliação 1 - Equipe 1

Ir para navegação

Ir para pesquisar

1 Questão 1: Cruzamento de duas ruas

- IN: sensores std_logic_vector(1 downto 0);

- OUT: semaforoA, semaforoB std_logic;

- Para resolver o problema foi utilizado atribuição de seleção através dos sensores.

- Quando houver carro na rua B (identificado pelo sensor[0]) o semaforoB acende(verde); Quando houver carro na rua A (identificado pelo sensor[1]) o semaforoA acende(verde); Quando houver carros em ambas as ruas, o semaforoA liga(verde), pois tem prioridade sobre o semaforoB.

- Tabela verdade:

| Entradas | Saídas | ||

|---|---|---|---|

| Sensor[1] | Sensor[0] | SemaforoA | SemaforoB |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

- Código:

library ieee; use ieee.std_logic_1164.all; entity questao1 is port( --Entradas: sensores 1 e 2 --Saidas: semafaros 1 e 2 sensores : in std_logic_vector(1 downto 0); semafaroA, semafaroB : out std_logic); end entity; architecture funcio of questao1 is begin with sensores select semafaroA <= '1' when "10", '1' when "11", '0' when others; with sensores select semafaroB <= '1' when "01", '0' when others; end architecture;

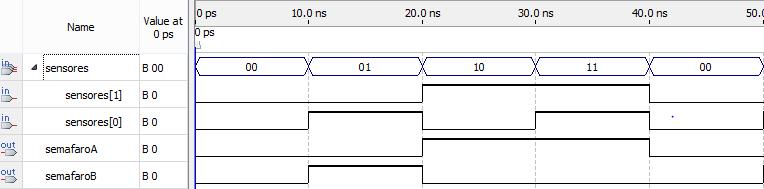

- Forma de onda:

2 Questão 2: Um amplificador e três aparelhos

- IN: disco, fita, radio std_logic;

- OUT: amp_disco, amp_fita, amp_radio std_logic;

- Para resolver o problema foi utilizado atribuição de seleção através dos equipamentos (disco, fita e rádio) que foi implementado a partir da tabela verdade.

- Quando apenas o rádio está ligado, o amp_radio é comutado; Quando apenas a fita está ligada, ou a fita e o rádio estão ligados, o amp_fita é comutado; Quando o disco está ligado, o amp_disco é comutado, independente das outras opções de fita ou rádio.

- Tabela verdade:

| Entradas] | Saídas | ||||

|---|---|---|---|---|---|

| Disco | Fita | Radio | amp_D | amo_F | amp_R |

| 0 | 0 | 0 | o | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 |

- Código:

library ieee; use ieee.std_logic_1164.all; entity questao2 is port( --Entradas: amplificador --Saidas: disco, fita e radio amplificador: in std_logic_vector(2 downto 0); disco, fita, radio: out std_logic); end entity; architecture funcio of questao2 is begin with amplificador select radio <= '1' when "001", '0' when others; with amplificador select fita <= '1' when "010", '1' when "011", '0' when others; with amplificador select disco <= '1' when "100", '1' when "101", '1' when "110", '1' when "111", '0' when others; end architecture;

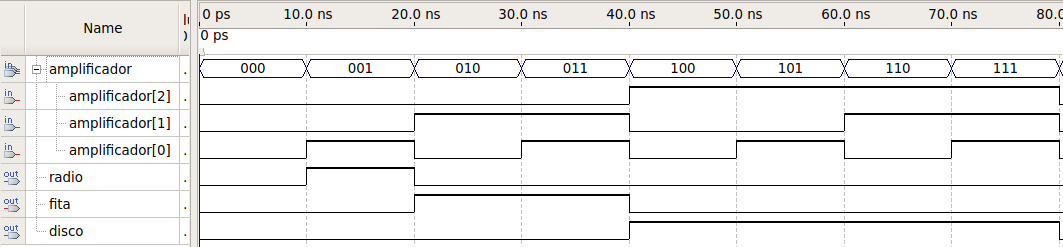

- Forma de onda:

3 Questão 3: Intercomunicadores

- IN: presidente, vice, engenharia, seção std_logic;

- OUT: ch_presidente, ch_vice, ch_engenharia, ch_seção std_logic;

- Para resolver o problema é usado uma abordagem "Data-flow", através de uma atribuição por seleção.

- Quando a seção está ligada, a comutação resulta em ch_secao; Quando a engenharia está ligada, ou engenharia e seção estão ligadas, a comutação resulta em ch_eng; Quando vice está ligada, ou engenharia e/ou seção estão ligadas, ch_vice é comutada; Quando presidente está ligada, a comutação é ch_pres, independente das demais entradas.

- Tabela verdade:

| Entradas | Saídas | ||||||

|---|---|---|---|---|---|---|---|

| Pres | Vice | Eng | Seção | ch_P | ch_V | ch_E | ch_S |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

- Código:

library IEEE; use IEEE.std_logic_1164.all; entity questao3 is port (presidente, vice, engenharia, chefe_secao : in std_logic; ch_pres, ch_vice, ch_enge, ch_secao : out std_logic ); end questao3; architecture arquitetura of questao3 is constant ligado : std_logic := '1'; constant desligado : std_logic := '0'; signal sel : std_logic_vector(3 downto 0); begin sel <= presidente & vice & engenharia & chefe_secao; ch_pres <= ligado when ( sel(3)='1' ) else desligado; ch_vice <= ligado when ( ( sel(3)='0' ) and ( sel(2)='1' ) ) else desligado; ch_enge <= ligado when ( ( sel(3)='0' ) and ( sel(2)='0' ) and ( sel(1)='1' ) ) else desligado; ch_secao <= ligado when ( ( sel(3)='0' ) and ( sel(2)='0' ) and ( sel(1)='0' ) and ( sel(0)='1' )) else desligado; end architecture;

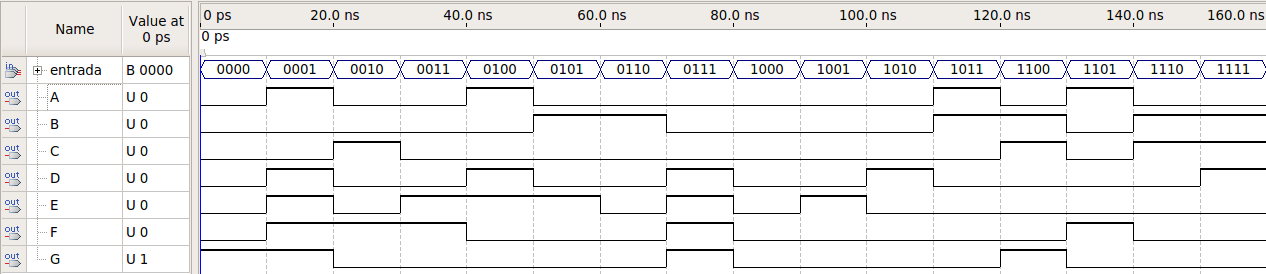

- Forma de onda:

4 Questão 4: Display de 7 segmentos

- IN: entrada std_logic_vector(3 downto 0)

- OUT: A,B,C,D,E,F,G std_logic

- Display de 7 segmentos, com a entrada sendo um vetor de 4 bits e a saída 7 bits. Na saída, os bits em 0 tornam o display ativo.

- Tabela verdade:

| Entradas | Saídas | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Entr1 | Entr2 | Entr3 | Entr4 | A | B | C | D | E | F | G |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 |

- Código

-- Library library IEEE; use IEEE.std_logic_1164.all; -- Entity entity quarta is port ( -- Sinais de entrada, 4 entradas para 16 saídas entrada : in std_logic_vector(3 downto 0); -- Sinais de saída, 7 saídas para representar os números hexa A,B,C,D,E,F,G : out std_logic ); end quarta; architecture display of quarta is -- Este será o sinal "completo" que depois será atribuído as saídas signal S : std_logic_vector(0 to 6); begin -- Atribuição dos valores de entrada para o vetor S de acordo com os valores da entrada de 0 a F with entrada select -- Para o resultado em S considerar: Led superior A, superior direito B, abaixo C, led de baixo D,esquerda de baixo E, -- esquerda de cima F e o Led do meio G. S <= "0000001" when "0000", -- 0 "1001111" when "0001", -- 1 "0010010" when "0010", -- 2 "0000110" when "0011", -- 3 "1001100" when "0100", -- 4 "0100100" when "0101", -- 5 "0100000" when "0110", -- 6 "0001111" when "0111", -- 7 "0000000" when "1000", -- 8 "0000100" when "1001", -- 9 "0001000" when "1010", -- A "1100000" when "1011", -- B "0110001" when "1100", -- C "1000010" when "1101", -- D "0110000" when "1110", -- E "0111000" when "1111", -- F "1111111" when others; -- Atribuição do vetor S para as saídas do sistema A <= S(0); B <= S(1); C <= S(2); D <= S(3); E <= S(4); F <= S(5); G <= S(6); end display;

- Forma de onda:

5 Questão 5: Tanque com fluido

- IN: on_off, sensor_min, sensor_max;

- OUT: valvula_entrada, valvula_saida;

- Para resolver o problema é usado uma abordagem "Data-flow", através de duas atribuições condicionais as válvulas são "ativadas" ou "desativadas".

- A válvula de entrada está ligada quando o sensor de nível mínimo está ativo, ou quando nenhum dos dois sensores estão ativos e a válvula de saída está desligada.

- A válvula de saída está ligada quando o sensor de nível máximo está ativo, ou quando nenhum dos dois sensores estão ativos e a válvula de entrada está desligada.

- O sistema só funciona quando estiver ligado através da entrada "on/off".

- A função do sistema que controla as válvulas é deixar o nível de fluído sempre entre o nível mínimo e o máximo.

- Tabela verdade:

| Entradas | auxiliares | Saídas | ||||

|---|---|---|---|---|---|---|

| on_off | sensor_min | sensor_max | aux_val1 | aux_val2 | Valvula_entrada | Valvula_saida |

| 0 | x | x | x | x | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 | x | x |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | x | x |

| 1 | 0 | 1 | 0 | 0 | x | x |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 | x | x |

| 1 | 0 | 1 | 1 | 1 | x | x |

| 1 | 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | x | x |

| 1 | 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 1 | x | x |

| 1 | 1 | 1 | 0 | 0 | x | x |

| 1 | 1 | 1 | 0 | 1 | x | x |

| 1 | 1 | 1 | 1 | 0 | x | x |

| 1 | 1 | 1 | 1 | 1 | x | x |

- * Os dois sensores nunca estão ativos ao mesmo tempo

- ** As duas válvulas nunca estão ativas ao mesmo tempo

- Código:

library IEEE; use IEEE.std_logic_1164.all; entity questao5 is port ( on_off, sensor_min, sensor_max : in std_logic; valvula_entrada, valvula_saida : out std_logic ); end questao5; architecture arquitetura of questao5 is constant ligado : std_logic := '1'; constant desligado : std_logic := '0'; signal aux_val1 : std_logic := '0'; signal aux_val2 : std_logic := '0'; begin aux_val1 <= ligado when ( on_off='1' and ((sensor_min='1') or (sensor_max='0' and aux_val2='0')) ) else desligado; valvula_entrada <= aux_val1; aux_val2 <= ligado when ( on_off='0' or ((sensor_max='1') or (sensor_min='0' and aux_val1='0')) ) else desligado; valvula_saida <= aux_val2; end architecture;

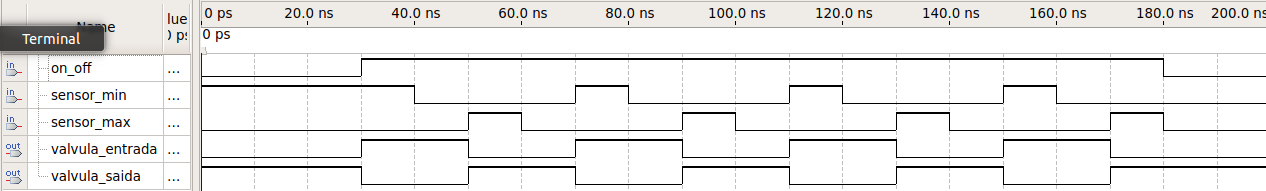

- Forma de onda:

- [0 a 30.0ns]

- O sistema esta desligado.

- A válvula de saída fica aberta para esvaziar o reservatório.

- Como o reservatório está vazio, o sensor de nível mínimo fica ativo.

- [30.0ns a 50.0ns]

- O sistema esta ligado.

- O reservatório está em nível mínimo

- A válvula de saída é desligada

- A válvula de entrada fica aberta até o reservatório chegar ao nível máximo

- [50.0ns a 70.0ns]

- O sistema esta ligado.

- O reservatório chega ao nível máximo

- A válvula de entrada é desligada

- A válvula de saída fica aberta até o reservatório chegar ao nível mínimo

- [0 a 30.0ns]

6 Questão 6: Cruzamento de três ruas

- IN: ruaA, ruaB, ruaC std_logic;

- OUT: semaforo1, semaforo2, semaforo3 std_logic;

- Para resolver o problema foi utilizado atribuição de seleção através da variável "ruas", que é uma concatenação das entradas(ruaA, ruaB e ruaC).

- Tabela verdade:

| Entradas] | Saídas | ||||

|---|---|---|---|---|---|

| ruaA | ruaB | ruaC | semaforo1 | semaforo2 | semaforo3 |

| 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 |

- Código:

library ieee; use ieee.std_logic_1164.all; entity questao6 is port( ruaA, ruaB, ruaC: in std_logic; semafaro1, semafaro2, semafaro3: out std_logic); end entity; architecture funcio of questao6 is signal ruas : std_logic_vector(2 downto 0); begin ruas <= (ruaA & ruaB & ruaC); with (ruas) select semafaro1 <= '1' when "000", '1' when "100", '1' when "110", '1' when "111", '0' when others; with (ruas) select semafaro2 <= '1' when "010", '1' when "011", '0' when others; with (ruas) select semafaro3 <= '1' when "001", '1' when "101", '1' when "110", '0' when others; end architecture;

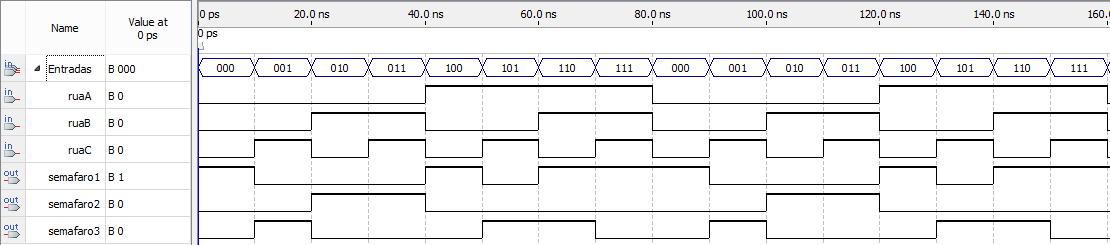

- Forma de onda:

7 Questão 7: Tanque de dois níveis, com sensor de temperatura

- IN: on_off, temp_alta, temp_baixa, sensores_val1, sensores_val2;

- OUT: valvula1, valvula2, alarme_falha, temperatura;

- Para resolver o problema é usado uma abordagem mista, ou seja, abordagem "Behavioral" (comportamental) e "Data-Flow".

- Abordagem "Behavioral":

- Válvula 2: está ligada quando o sensor de nível mínimo está ativo.

- Válvula 1: está ligada quando o sensor de nível mínimo está ativo ou quando a válvula 2 esta ativa.

- O gerenciamento das válvulas só funciona quando o sistema esta ligado e sem erros nos sensores.

- Abordagem "Behavioral":

- Abordagem "Data-Flow":

- Temperatura: pode estar em três níveis, muito alta, estável e muito baixa e depende dos dois sensores de temperatura

- Margem de segurança: informa ao monitor que o nível de reservatório 1 esta na margem de segurança, depende da entrada

- Permissão: para o sistema funcionar deve estar ligado e sem erros nos sensores de entrada

- Abordagem "Data-Flow":

- Código:

library IEEE; use IEEE.std_logic_1164.all; entity questao7 is port ( on_off, temp_alta, temp_baixa, margem_in : in std_logic; sensores_val1, sensores_val2 : in std_logic_vector (1 downto 0); valvula1, valvula2, alarme_falha, margem_out : out std_logic; temperatura : out std_logic_vector (2 downto 0) ); end questao7; architecture arquitetura of questao7 is constant ligado : std_logic := '1'; constant desligado : std_logic := '0'; signal aux_val1 : std_logic := '0'; signal aux_val2 : std_logic := '0'; signal aux_alarme : std_logic := '0'; signal permissao : std_logic := '0'; signal temp_in : std_logic_vector (1 downto 0); begin -- é preciso de sinais auxiliares para usar os sinais como entrada nos processos valvula2 <= aux_val2; valvula1 <= aux_val1; alarme_falha <= aux_alarme; -- juntando sinais dos sensores de temperatura temp_in <= temp_alta & temp_baixa; -- processo responsável por ligar/desligar valvula 2 -- valvula 2 só depende de seus sensores process (sensores_val2,permissao) is begin -- se sistema tem permissão, funcionara normalmente if(permissao='1')then -- se a valvula estiver desligada if (aux_val2 = '0')then -- se a valvula estiver desligada e sensor mínimo estiver ativado, ligar valvula if (sensores_val2(0) = '1')then aux_val2 <= ligado; end if; -- se a vlvula estiver ligada elsif (aux_val2 = '1') then -- se a valvula estiver ligada e sensor máximo estiver ativado, desligar valvula -- quando o tranque esta enchendo a valvula fica ligada quando os dois sensores estão desligados if (sensores_val2(1) = '1')then aux_val2 <= desligado; end if; end if; else -- se sistema não tem permissao a valvula sera deligada aux_val2 <= desligado; end if; end process; -- processo responsável por ligar/desligar valvula 1 -- valvula 1 depende de seus sensores e de valvula2 process (sensores_val1,aux_val2) is begin -- se sistema tem permissão, funcionara normalmente if(permissao='1')then -- se a valvula 1 estiver desligada if (aux_val1 = '0')then -- valvula sera ligada se sensor mínimo estiver ativado ou se valvula 2 estiver ligada if (sensores_val1(0) = '1' or aux_val2 = '1')then aux_val1 <= ligado; end if; -- se a valvula estiver ligada elsif (aux_val1 = '1') then -- valvula 1 só sera desligada quando chegar ao nível maximo -- não importa se foi ativada pelo sensor mínimo ou pela valvula 2 if (sensores_val1(1) = '1') then aux_val1 <= desligado; end if; end if; else -- se sistema não tem permissao a valvula sera deligada aux_val1 <= desligado; end if; end process; -- verifica temperatura e informa na saida seu estado (muitoquente,estávelou muito frio) ------------------------------- -- temperatura(0) = muito baixa -- temperatura(1) = estavel -- temperatura(2) = muito alta ------------------------------- WITH temp_in SELECT temperatura <= "010" WHEN "00", "001" WHEN "01", "100" WHEN "10", "000" WHEN OTHERS; -- verifica erros nos sensores -- existe erro se sensores de maximo e minimo estão ligados ao mesmo tempo -- existe erro se sensores de temp_alta e temp_min estão ligados ao mesmo tempo aux_alarme <= '1' WHEN (sensores_val1="11" or sensores_val2="11" or temp_in="11") ELSE '0'; -- Permissao para sustema funcionar --sistema só funciona quando esta ligado e não existe erro permissao <= '1' when (on_off='1' and aux_alarme='0') else '0'; -- Informa ao monitor se nível de agua esta na margem de segurança na valvula 1 margem_out <= margem_in; end architecture;

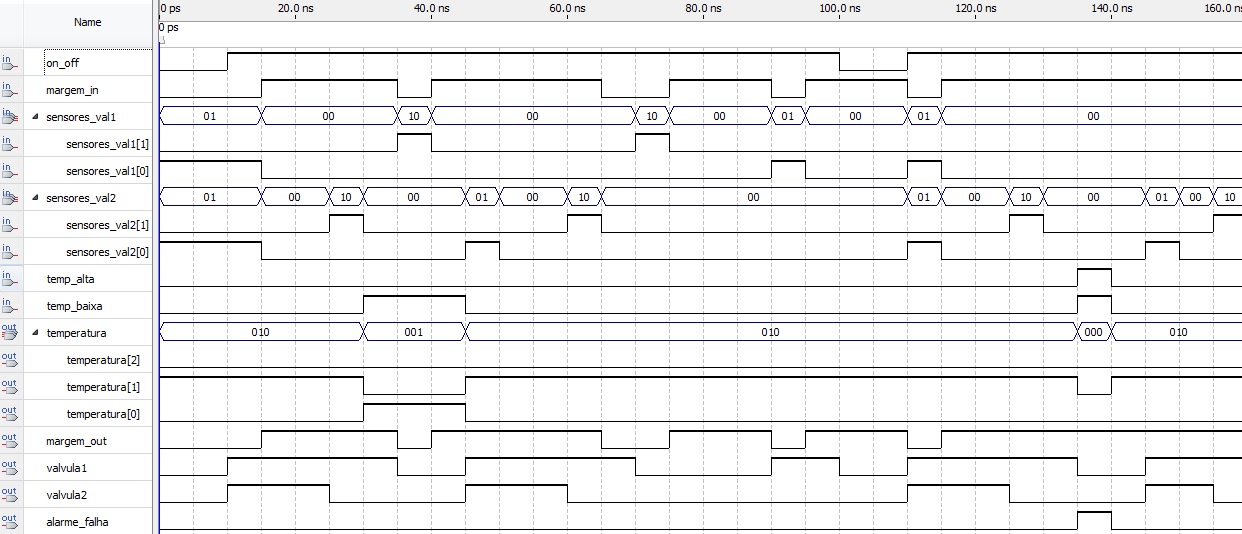

- Forma de onda:

- Tabela verdade:

- Permissao

| Auxiliar | Entrada | Saída |

|---|---|---|

| aux_alarme | on_off | permissao |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

- Válvula 2

| Auxiliar | Entradas | Saída | ||

|---|---|---|---|---|

| permissao | aux_val2 | sensores_val2(1) | sensores_val2(0) | valvula2 |

| 0 | x | x | x | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | x |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | x |

- Válvula 1

| Auxiliar | Entradas | Saída | |||

|---|---|---|---|---|---|

| permissao | aux_val1 | aux_val2 | sensores_val1(1) | sensores_val1(0) | valvula1 |

| 0 | x | x | x | x | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | x |

| 1 | 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | x |

| 1 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | x |

| 1 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | x |

- Temperatura

| Entrada | Saídas | |||

|---|---|---|---|---|

| temp_alta | temp_baixa | temperatura(2) | temperatura(1) | temperatura(0) |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

- * temperatura(2)= temperatura alta, temperatura(1) = temperatura estável e temperatura(0)= temperatura baixa

- Margem de segurança

| Entrada | Saída |

|---|---|

| margem_in | margem_out |

| 0 | 0 |

| 1 | 1 |

8 Questão 8: Circuito aritmético

- IN: a,b std_logic_vector(7 downto 0); cin : in std_logic;

- OUT: cout std_logic; soma std_logic_vector(7 downto 0);

- Para realizar o processo de soma binária, é necessário um bit de carry in (cin/vem-um) e um bit de carry out(cout/vai-um);

- Para solucionar esse problema, foi utilizado um process com sensibilidade das entradas (a,b e cin), onde nele, foi realizado um for loop que fosse de i=0 até i=7, já que o somador é de 8 bits, e em cada loop ele realiza as seguintes operações:

- Código:

library ieee; use ieee.std_logic_1164.all; entity somador8bits is port( a,b : in std_logic_vector(7 downto 0); cin : in std_logic; cout : out std_logic; soma : out std_logic_vector(7 downto 0) ); end entity; architecture funcio of somador8bits is begin process(a,b,cin) variable b_carry : std_logic_vector(8 downto 0); begin b_carry(0) := cin; for i in 0 to 7 loop soma(i) <= a(i) xor b(i) xor b_carry(i); b_carry (i + 1) := (a(i) and b(i)) or (a(i) and b_carry(i)) or (b(i) and b_carry(i)); end loop; cout <= b_carry(7); end process; end architecture;

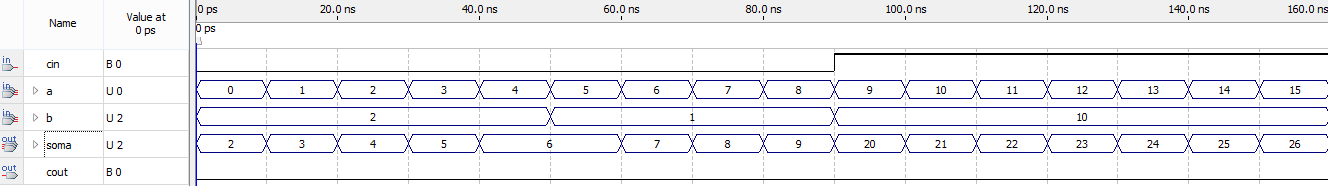

- Forma de onda: