Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

(→ATUAL) |

|||

| (416 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

==Registro on-line das aulas== | ==Registro on-line das aulas== | ||

===Unidade 1 - Introdução a disciplina=== | ===Unidade 1 - Introdução a disciplina=== | ||

| − | * | + | * 6 ENCONTROS |

{{collapse top | expand=true | Unidade 1 - Introdução a disciplina}} | {{collapse top | expand=true | Unidade 1 - Introdução a disciplina}} | ||

| − | + | ;Encontro 1 (26 jul): | |

| − | ; | ||

* [[DLP1-EngTel (Plano de Ensino) | APRESENTAÇÃO DA DISCIPLINA]] | * [[DLP1-EngTel (Plano de Ensino) | APRESENTAÇÃO DA DISCIPLINA]] | ||

| − | |||

* A [[DLP1-EngTel (página) | PÁGINA DA DISCIPLINA]] contem os materiais que não alteram entre semestre. | * A [[DLP1-EngTel (página) | PÁGINA DA DISCIPLINA]] contem os materiais que não alteram entre semestre. | ||

* Nesta página está o [[DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke | REGISTRO DIÁRIO E AVALIAÇÕES]]. | * Nesta página está o [[DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke | REGISTRO DIÁRIO E AVALIAÇÕES]]. | ||

| − | * | + | * A entrega de atividades e avaliações será através da [https://moodle.ifsc.edu.br/course/view.php?id=699 plataforma Moodle]. A inscrição dos alunos é automática a partir do SIGAA. |

| − | * Para a comunicação entre professor-aluno, além dos avisos no SIGAA, utilizaremos o [https://mail.google.com/chat/u/0/#chat/space/ | + | * Para a comunicação entre professor-aluno, além dos avisos no SIGAA, utilizaremos o [https://mail.google.com/chat/u/0/#chat/space/AAAAu052zos chat institucional]. A princípio todos os alunos já estão previamente cadastrados pelo seu email institucional. Confiram enviando uma mensagem de apresentação. |

| − | + | *Durante as aulas é recomendado que o aluno utilize os softwares '''Quartus''' e '''Modelsim''' instalados nas maquinas do laboratório, mas estes também podem ser usados através da '''Nuvem do IFSC'''. | |

| − | * | + | * Nas aulas é recomendado que o aluno utilize os softwares '''Quartus Light''' e '''ModelSim''' instalado nas máquinas do laboratório ou então acesse estes softwares através da [[Acesso ao IFSC-CLOUD (NUVEM)|NUVEM do IFSC]]. |

| + | ;LER PARA O PRÓXIMO ENCONTRO: | ||

| + | *Seção 4.1 a 4.5 de [http://www.vhdl.us/book/Pedroni_VHDL_3E_Chapter4.pdf Review of Field Programmable Gate Arrays (FPGAs)], Volnei A. Pedroni. (ou para quem preferir em português, leia as seções 18.1 a 18.3 do livro: PEDRONI, Volnei A '''Eletrônica Digital Moderna e VHDL: Princípios Digitais, Eletrônica Digital, Projeto Digital, Microeletrônica e VHDL'''; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. ISBN 9788535234657. Têm 16 exemplares disponíveis na [https://biblioteca.ifsc.edu.br/ Biblioteca do campus]. Número de chamada: 621.392 P372e) | ||

| + | *Seção 2.1 Dispositivos lógicos programáveis do TCC [[Integração de ramais analógicos com FPGA utilizando processador softcore]], Renan Rodolfo da Silva. | ||

| − | ; | + | ;Encontro 2 (28 jul): |

*Introdução aos dispositivos lógicos programáveis: | *Introdução aos dispositivos lógicos programáveis: | ||

:* Conceito, tipos de PLDs | :* Conceito, tipos de PLDs | ||

| − | + | :* SPLD: | |

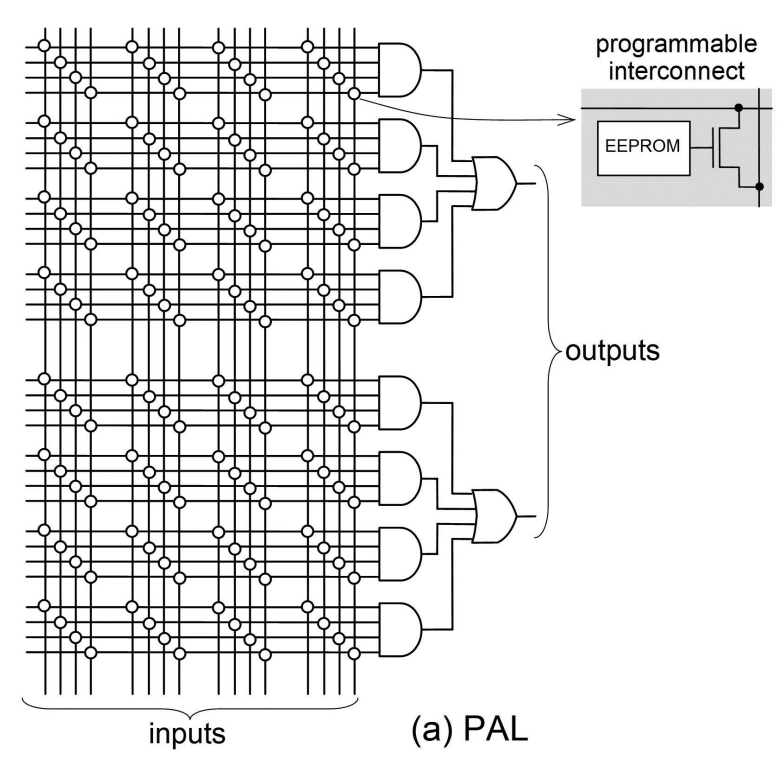

| − | ::* | + | ::*PAL (e.g. [[Media: PAL16.pdf| PAL16 da Texas Instruments (1984)]]) |

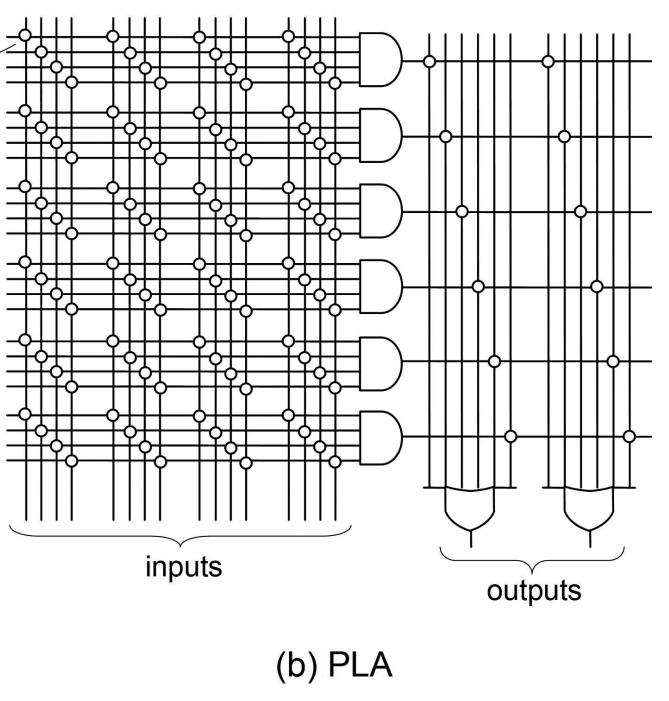

| − | + | ::*PLA (e.g. [[Media: PLS100.pdf| PLS100 da Philips Semiconductors (1993)]]) | |

| − | + | ::*GAL (e.g. [[Media: GAL16V8.pdf| GAL16V8 da Lattice (2004)]]) | |

| + | :* CPLDs (e.g. [[Media: ATF2500C.pdf| ATF2500C da Atmel (2008)]], [https://br.mouser.com/c/ds/semiconductors/programmable-logic-ics/cpld-complex-programmable-logic-devices/ Complex Programmable Logic Devices Datasheets - Mouser]) | ||

| − | {{fig|1. | + | {{collapse top | expand=true| Exemplos de PLDs}} |

| + | {{fig|1.1|Exemplo de PAL| PedroniFig4_4a.png| 400 px | http://www.vhdl.us/book/Pedroni_VHDL_3E_Chapter4.pdf}} | ||

| − | {{fig|1. | + | {{fig|1.2|Exemplo de PLA| PedroniFig4_4b.png| 400 px | http://www.vhdl.us/book/Pedroni_VHDL_3E_Chapter4.pdf}} |

| − | {{fig|1. | + | {{fig|1.3|Macrobloco do PLD EP300 da ALTERA| ep310_macrocell.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} |

| − | {{fig|1. | + | {{fig|1.4|Macrocélula dos PLDs Clássicos EP600, EP900, EP1800 da ALTERA (1999)| Macrocell_EP900.png| 400 px | https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ds/archives/classic.pdf}} |

| − | {{fig|1.6|Architetura do CPLD MAX 5000 da ALTERA| max_5000_architecture.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} | + | {{fig|1.5|Architetura do PLD EP1800 da ALTERA| ep1800_block_diagram.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} |

| + | |||

| + | {{fig|1.6|Architetura do PLD EP1800 da ALTERA| ep1800_block_diagram2.jpg| 400 px | https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ds/archives/classic.pdf}} | ||

| + | |||

| + | {{fig|1.7|Pinagem e tipos de encapsulamento do PLD EP1800 da ALTERA| PackagePinOut_EP1810.png| 400 px | https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ds/archives/classic.pdf }} | ||

| + | |||

| + | {{fig|1.8|Architetura do CPLD MAX 5000 da ALTERA| max_5000_architecture.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | :* | + | :* Ver preços em |

| − | ::* [https://www. | + | ::*[https://www.arrow.com/ ARROW] |

| + | ::*[https://www.digikey.com/ Digikey] | ||

| + | ::*[https://mouser.com Mouser Electronics] | ||

| + | ::*[https://www.newark.com/ Newark] | ||

:* Fabricantes de DLPs/FPGAs e familias de DLPs atuais. | :* Fabricantes de DLPs/FPGAs e familias de DLPs atuais. | ||

::*[https://www.altera.com/products/fpga/overview.html ALTERA/INTEL] - Stratix, Arria, Cyclone, Max | ::*[https://www.altera.com/products/fpga/overview.html ALTERA/INTEL] - Stratix, Arria, Cyclone, Max | ||

| − | ::*[https://www.xilinx.com/products/silicon-devices/fpga.html Xilinx] - Virtex, Kintex, Artix, Zynq (SoC) | + | ::*[https://www.xilinx.com/products/silicon-devices/fpga.html Xilinx/AMD] - Virtex, Kintex, Artix, Zynq (SoC) |

| − | ::*[ | + | ::*[https://www.microchip.com/en-us/products/fpgas-and-plds/fpgas Microchip] - Igloo, PolarFire |

::*[http://www.latticesemi.com/Products.aspx#_D5A173024E414501B36997F26E842A31 Lattice] - ECP, iCE, Mach | ::*[http://www.latticesemi.com/Products.aspx#_D5A173024E414501B36997F26E842A31 Lattice] - ECP, iCE, Mach | ||

| − | + | ;PARA O PRÓXIMO ENCONTRO: | |

| − | + | *[https://www.intel.com/content/www/us/en/products/details/fpga/platforms.html See why Microsoft chose Intel FPGAs to accelerate their next generation cloud infrastructure] | |

| − | + | *[https://www.youtube.com/watch?v=ecyyZ6zTLic Microsoft's Bing* Intelligent Search with Intel® FPGAs] | |

| − | + | ||

| − | + | ;Encontro 3 (1 ago): | |

| − | : | + | * [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 1 e 2 |

| − | |||

| − | ; | + | ;PARA O PRÓXIMO ENCONTRO: |

| − | * | + | * Leia a assista a alguns dos vídeos sobre a historia e processo de produção dos chips. |

| − | + | :*[https://www.semiwiki.com/forum/content/1535-brief-history-fabless-semiconductor-industry.html A Brief History of the Fabless Semiconductor Industry] | |

| + | :*[http://www.semiwiki.com/forum/content/1539-brief-history-tsmc.html Taiwan Semiconductor Manufacturing Corporation (TSMC)], [http://www.globalfoundries.com/ GLOBALFOUNDRIES] | ||

| + | :*[https://www.linkedin.com/pulse/free-copy-fabless-transformation-semiconductor-industry-daniel-nenni-1 Fabless: The Transformation of the Semiconductor Industry, 2014] - Download free | ||

| + | :*[https://www.youtube.com/watch?v=W3rfVpkNquA Produção do FinFET], [https://www.youtube.com/watch?v=d9SWNLZvA8g] | ||

| + | :*[https://en.wikipedia.org/wiki/3_nm_process 3 nm process], [https://en.wikipedia.org/wiki/Multigate_device multi-gate MOSFET] | ||

| + | :*[https://www.youtube.com/watch?v=UvluuAIiA50 GLOBALFOUNDRIES Sand to Silicon], [https://www.youtube.com/watch?v=F2KcZGwntgg How Microchips are made] - Processo de fabricação de um chip | ||

| + | :*[https://en.wikipedia.org/wiki/Foundry_model Foundries], [https://en.wikipedia.org/wiki/List_of_semiconductor_fabrication_plants List of semiconductor fabrication plants] | ||

| + | :*[https://www.youtube.com/watch?v=GU87SH5e0eI A dependência do mundo com a TMSC] | ||

| − | + | ;Encontro 4 (4 ago): | |

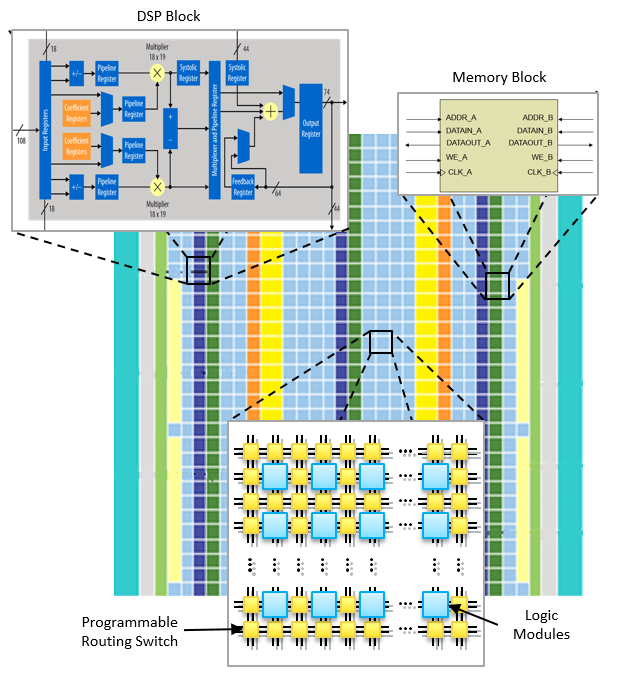

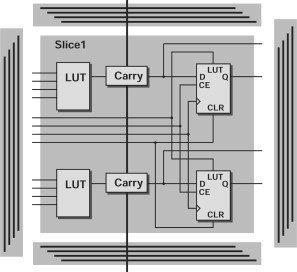

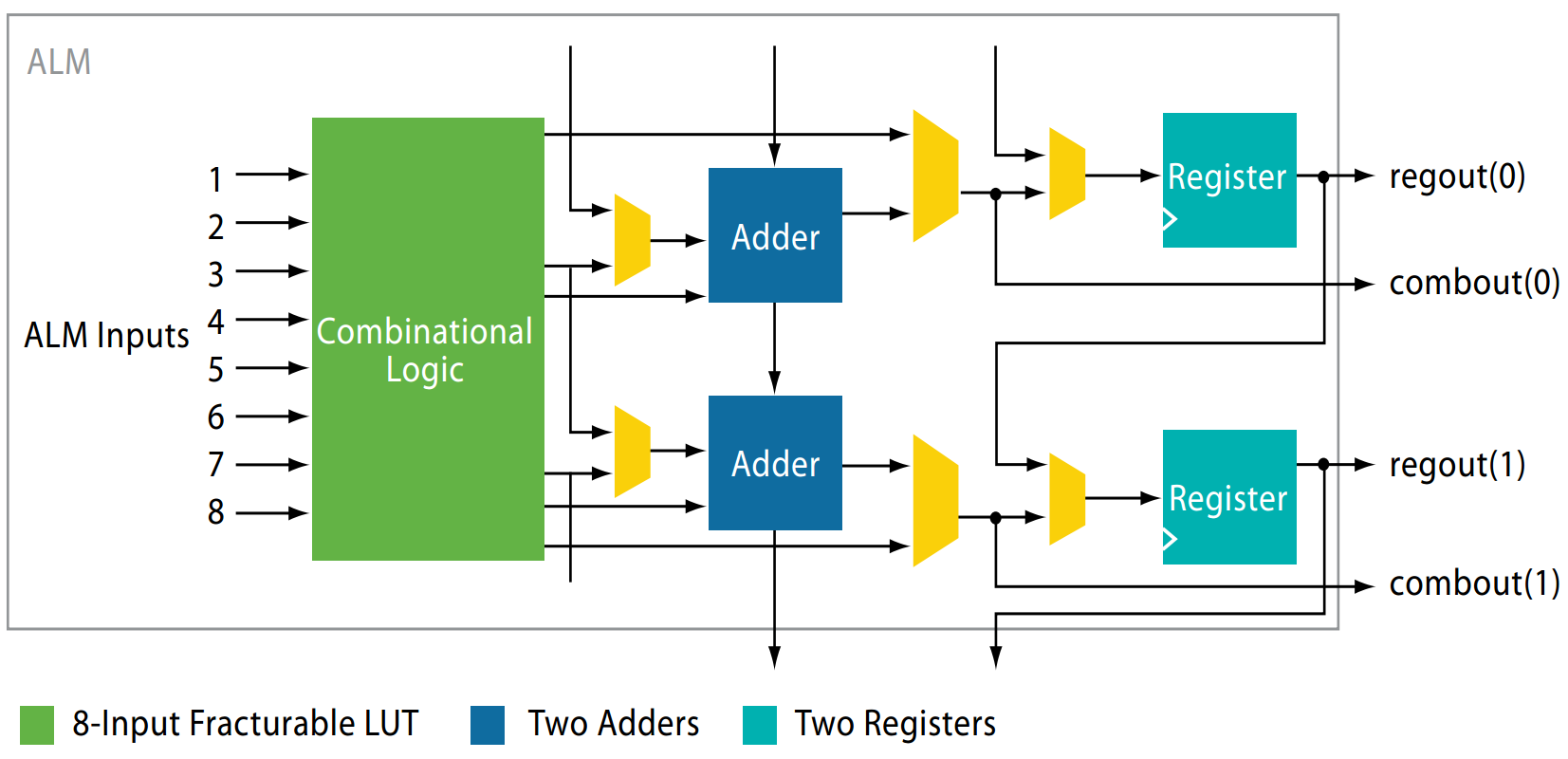

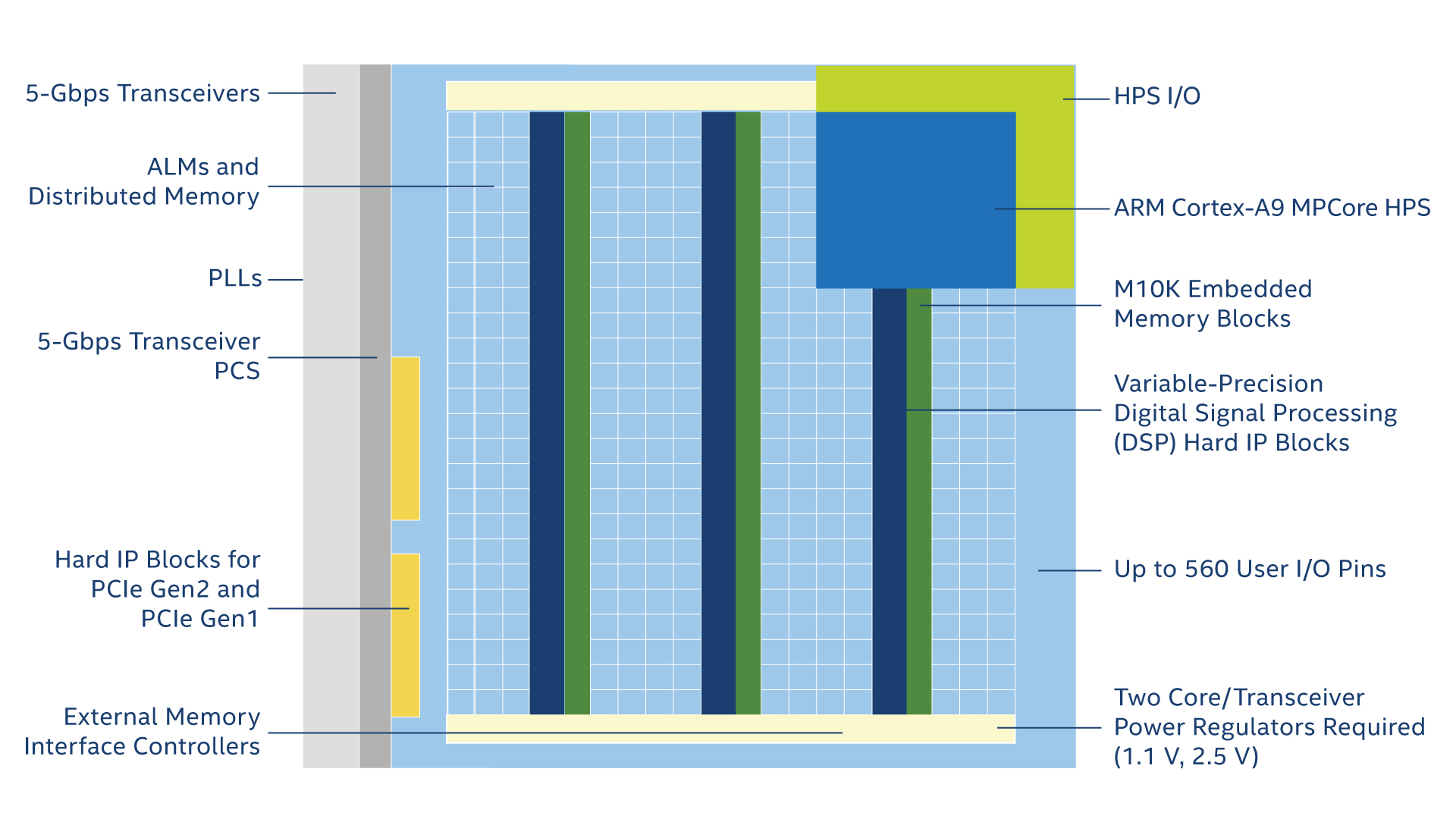

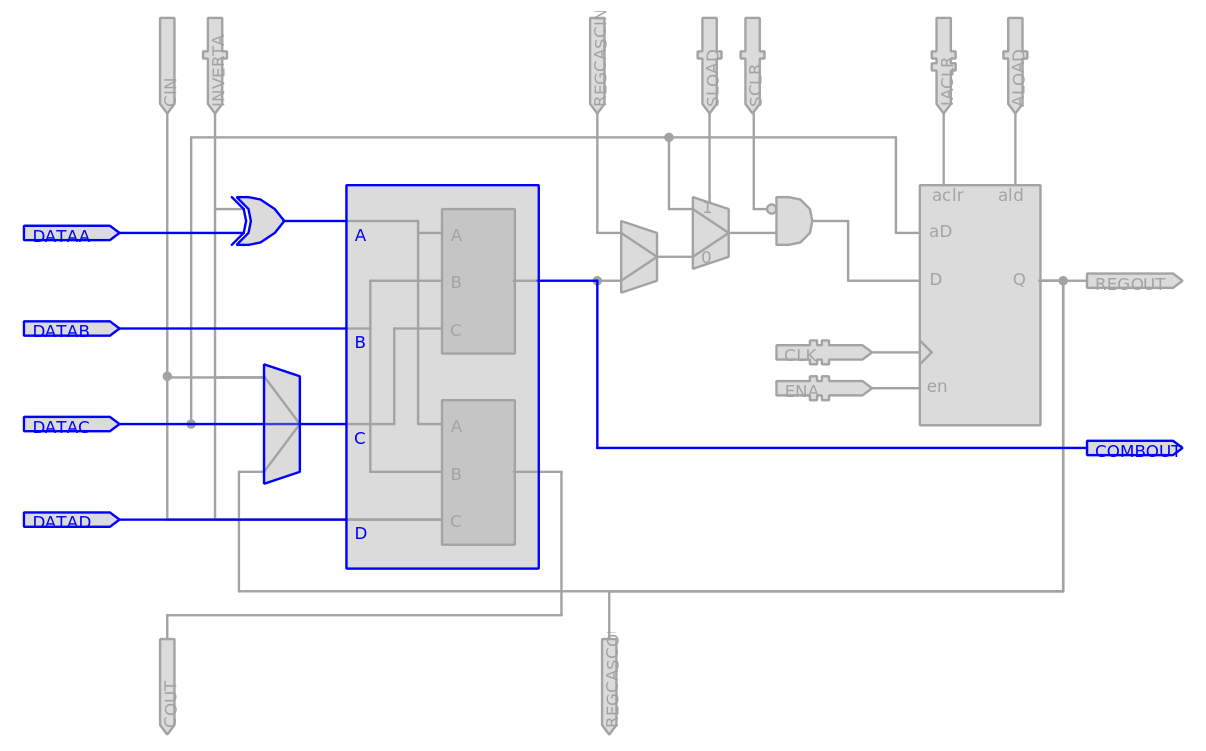

| + | * Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, LUT, Flip_flop D, RAM, DSP, Clock, PLL, DLL, I/O | ||

| + | {{collapse top | expand=true |Exemplos de FPGA}} | ||

| − | |||

| − | {{fig|1. | + | {{fig|1.7|Arquitetura de um FPGA | Architecture_FPGAs.png| 600 px | https://www.intel.com/content/www/us/en/docs/programmable/683176/18-1/fpga-overview-opencl-standard.html}} |

| − | {{fig|1. | + | {{fig|1.8|Diagrama simplificado da CLB de um FPGA ARM/Xilinx | CLB_FPGAs.jpg| 600 px | https://www.sciencedirect.com/science/article/pii/B9780750678667500032#f14}} |

| + | |||

| + | {{fig|1.9|Diagrama simplificado da ALM de um FPGA Intel/Altera | ALM_LUT_FPGAs.png| 600 px | https://www.intel.com/content/www/us/en/content-details/771003/fpga-architecture-8-input-lut-legacy-white-paper.html}} | ||

| + | |||

| + | {{fig|1.10|Arquitetura do Cyclone® V Intel/Altera | CycloneV_FPGAs.jpg| 600 px | https://www.intel.com.br/content/www/br/pt/products/details/fpga/cyclone/v/article.html}} | ||

{{fig|1.11|Leiaute de um FPGA Xilinx genérico | Leiaute2_FPGAs.jpg| 600 px | https://www.sciencedirect.com/science/article/pii/B9780750678667500032 }} | {{fig|1.11|Leiaute de um FPGA Xilinx genérico | Leiaute2_FPGAs.jpg| 600 px | https://www.sciencedirect.com/science/article/pii/B9780750678667500032 }} | ||

| Linha 69: | Linha 92: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | |||

| − | |||

| − | ; | + | ;PARA O PRÓXIMO ENCONTRO: |

| + | * Leia a assista a alguns dos vídeos sobre FPGAs. | ||

| + | :*[https://youtu.be/v2ZloNgU-EE Tecnologia FPGA Intel - Macnica DHW] | ||

| + | :*[https://www.sciencedirect.com/science/article/pii/B9780750678667500032 Chapter 2 - FPGA Fundamentals], R.C. Cofer, Benjamin F. Harding, Science Direct | ||

| + | :*[https://edisciplinas.usp.br/pluginfile.php/530826/mod_resource/content/1/DISPOSITIVOS%20L%C3%93GICOS%20PROGRAM%C3%81VEIS_2014.pdf Dispositivos Lógicos Programáveis], L.M.R. Codá, USP | ||

| − | + | ;CURIOSIDADES: | |

| − | : | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | *[https://www. | + | * Quais são os tipos de [[Níveis lógicos]] utilizados. |

| − | * | + | * [[Como as portas lógicas são implementadas com transistores CMOS]] |

| − | *https:// | + | *[https://www.computerhistory.org/siliconengine/timeline/ The Silicon Engine Timeline], Computer History Museum (CHM) |

| − | ; | + | *[https://www10.edacafe.com/book/ASIC/CH04/CH04.1.php The Antifuse], [https://www.youtube.com/watch?v=7qa1dsCpMMo EEPROM], [https://www.youtube.com/watch?v=ELl3abwYQ90&list=PL9B4edd-p2agcmJl2EscTdLudLv58uXHt&index=1 What Is Flash Memory] |

| − | *[https://www. | + | *[https://numato.com/blog/differences-between-fpga-and-asics/ FPGA Vs ASIC: Differences Between Them And Which One To Use?] |

| + | |||

| + | ;Encontro 5 (8 ago): | ||

| + | * [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 3 e 4 | ||

| + | *Exemplo de um Circuito para cálculo da '''distância de Hamming'''. | ||

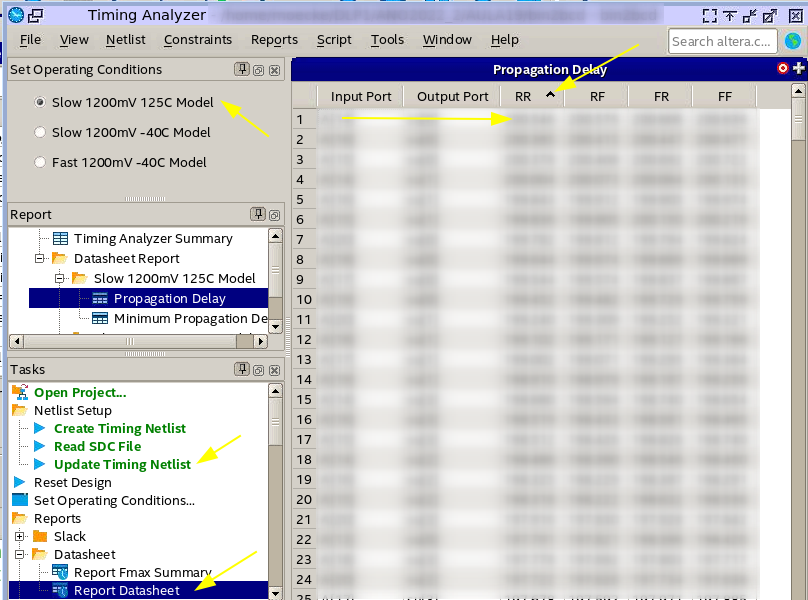

| + | :*[[Medição de tempos de propagação em circuitos combinacionais]] | ||

| + | :* Os alunos devem utilizar a nuvem para realizar a atividade. | ||

| + | :*[https://wiki.sj.ifsc.edu.br/index.php/Medi%C3%A7%C3%A3o_de_tempos_de_propaga%C3%A7%C3%A3o_em_circuitos_combinacionais#Inserindo_restri.C3.A7.C3.B5es_de_atraso_m.C3.A1ximo_para_o_compilador Inserindo restrições de atraso máximo para o compilador] | ||

| + | :* Objetivos: Copiar e colar o código no Quartus; diferença entre analise e síntese e compilação; observar o RTL (usar UNGROUP); simulação funcional e simulação temporal; observar os atrasos de propagação na simulação temporal. | ||

| + | ;PARA CONHECER MAIS: | ||

| + | * Ler pag. 413 a 431 de <ref name="PEDRONI2010a"> PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657 </ref> ou pag. 495 a 501 de de <ref name="PEDRONI2010b"> PEDRONI, Volnei A. '''Circuit Design and Simulation with VHDL'''; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 </ref>. | ||

| + | * [https://en.wikipedia.org/wiki/Field-programmable_gate_array#History FPGA History] | ||

| + | * [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Design_and_programming FPGA Design and programming] | ||

| + | * [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Basic_process_technology_types FPGA Basic process technology types] | ||

| + | * [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Major_manufacturers FPGA Major manufacturers] | ||

| + | * Assistir [https://www.coursera.org/lecture/intro-fpga-design-embedded-systems/1-many-types-of-fpgas-EWo0n Many types of FPGAs] Coursera | ||

| + | * O que é um Schmitt trigger? | ||

| + | :*[https://youtu.be/d-7Oyd8o8hE?t=93 Um pouco de lab] - lab até o minuto 5:20, depois um exemplo com AMPOP | ||

| + | :*[https://howtomechatronics.com/how-it-works/electrical-engineering/schmitt-trigger/ como funciona] | ||

| + | * O que é a JTAG? | ||

| + | :*[https://www.corelis.com/educationdownload/JTAG-Tutorial.pdf Como funciona para testes e programação] - In-System-Programming pag.7 | ||

| + | ;Notícias recentes do mundo dos DLPs: | ||

| + | *[https://newsroom.intel.com/press-kits/intel-acquisition-of-altera/#:~:text=Intel%20and%20Altera%20announced%20on,transaction%20closed%20December%2028%2C%202015. Intel Acquisiton of Altera] | ||

| + | <i> | ||

| + | :Intel and Altera announced on June 1, 2015, that they had entered into a definitive agreement under which Intel would acquire Altera for $54 per share in an all-cash transaction valued at approximately '''$16.7 billion'''. The transaction closed December 28, 2015. | ||

| + | </i> | ||

| + | |||

| + | *[https://press.siemens.com/global/en/event/siemens-closes-acquisition-mentor-graphics Siemens closes acquisition of Mentor Graphics (Munich, 14 November 2016)] | ||

| + | <i> | ||

| + | :With the recent closing of its acquisition of electronic design automation (EDA) software leader, Mentor Graphics Corporation, Siemens sets out to underscore the significant customer value it envisions for both Electronic Systems and Integrated Circuit (IC) design tools. Mentor is now part of Siemens' product lifecycle management (PLM) software business, making the combined organization the world's leading supplier of industrial software used for product design, simulation, verification, testing and manufacturing. Siemens completes '''$4.5 billion''' purchase of Mentor Graphics [https://www.oregonlive.com/silicon-forest/2017/03/siemens_completes_45_billion_p.html]. | ||

| + | </i> | ||

| + | |||

| + | *[https://www.amd.com/en/press-releases/2022-02-14-amd-completes-acquisition-xilinx AMD Completes Acquisition of Xilinx], [https://www.crn.com/news/components-peripherals/amd-completes-49b-xilinx-acquisition-largest-chip-deal-in-history AMD Completes $49B Xilinx Acquisition, Largest Chip Deal In History] | ||

| + | <i> | ||

| + | :AMD (NASDAQ: AMD) today (SANTA CLARA, Calif. 02/14/2022) announced the completion of its acquisition of Xilinx in an all-stock transaction. The acquisition, originally announced on October 27, 2020, creates the industry’s high-performance and adaptive computing leader with significantly expanded scale and the strongest portfolio of leadership computing, graphics and adaptive SoC products. | ||

| + | :AMD said it has completed its '''$49 billion''' acquisition of Xilinx to create the “industry’s high-performance and adaptive computing leader,” marking the largest chip deal in history. With the acquisition, AMD is expanding beyond its purview of CPUs and GPUs with a large portfolio of reprogrammable chips called field programmable gate arrays, or FPGAs, that it said will significantly expand the company’s opportunities in data centers, embedded computing and telecommunications. Xilinx also has a footprint in other markets, like defense, broadcast and consumer electronics, which will help expand its total addressable market to $135 billion from $80 billion, according to AMD. | ||

| + | </i> | ||

| + | |||

| + | <!-- | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| + | ;Encontro 6 (28 fev.): | ||

| + | * [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 3 | ||

| + | *Exemplo de um Circuito para cálculo da '''distância de Hamming'''. | ||

| + | :*[[Medição de tempos de propagação em circuitos combinacionais]] | ||

| + | :* Os alunos devem utilizar a nuvem para realizar a atividade. | ||

| + | :* O professor estará disponível através do chat da UC e pelo link de meet disponibilizado no chat.[https://wiki.sj.ifsc.edu.br/index.php/Medi%C3%A7%C3%A3o_de_tempos_de_propaga%C3%A7%C3%A3o_em_circuitos_combinacionais#Inserindo_restri.C3.A7.C3.B5es_de_atraso_m.C3.A1ximo_para_o_compilador Inserindo restrições de atraso máximo para o compilador] | ||

| + | :* Objetivos: Copiar e colar o código no Quartus; diferença entre analise e síntese e compilação; observar o RTL (usar UNGROUP); simulação funcional e simulação temporal; observar os atrasos de propagação na simulação temporal. | ||

| + | --> | ||

{{collapse bottom}} | {{collapse bottom}} | ||

===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== | ===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== | ||

| − | * | + | * 10 ENCONTROS |

{{collapse top| expand = true | Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS}} | {{collapse top| expand = true | Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS}} | ||

| − | ;Encontro | + | ;Encontro 6 (11 ago.) |

* Introdução ao VHDL e ambiente EDA - QUARTUS | * Introdução ao VHDL e ambiente EDA - QUARTUS | ||

* Estrutura do código VHDL | * Estrutura do código VHDL | ||

| Linha 161: | Linha 213: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | Exemplo | + | ;Encontro 8 (7 mar.) |

| + | * Exemplo - Descrição de um multiplexador de 4 entradas | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

entity mux_novo is | entity mux_novo is | ||

| Linha 223: | Linha 276: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | |||

| − | |||

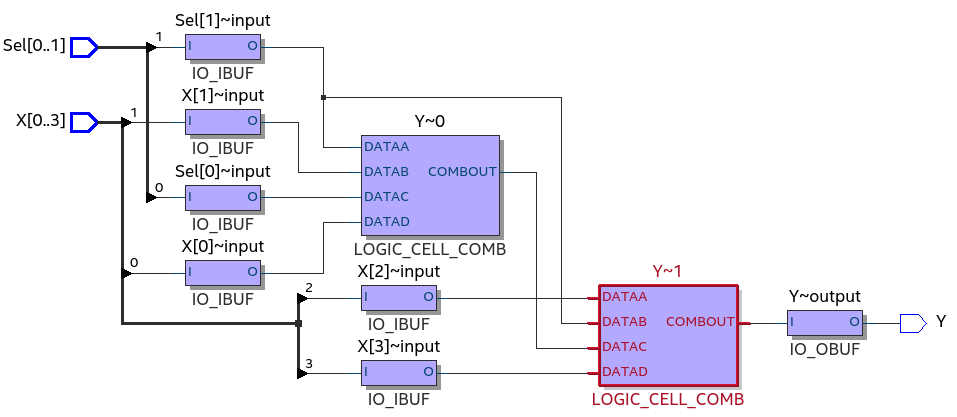

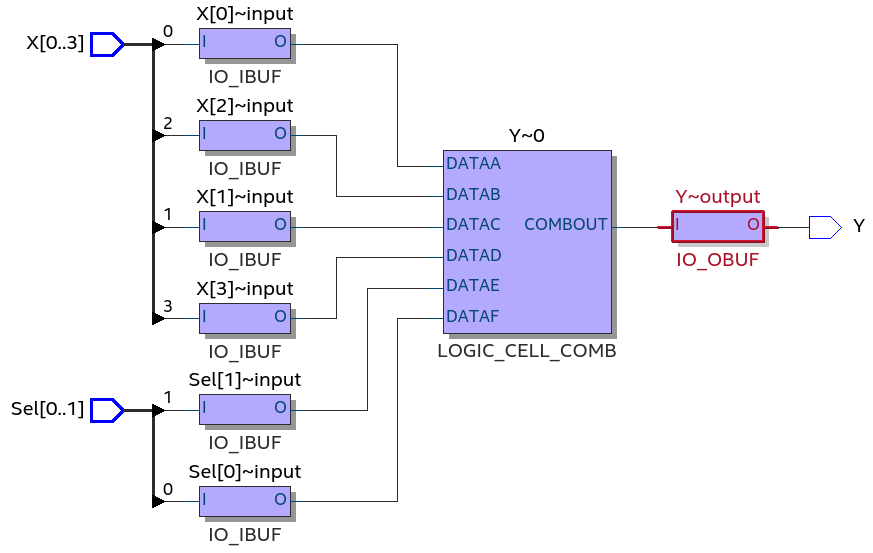

* Faça a análise e sintese do mux_novo, associando a architecture v_logica_pura, depois v_WITH_SELECT, depois v_WHEN e por último v_IF_ELSE. | * Faça a análise e sintese do mux_novo, associando a architecture v_logica_pura, depois v_WITH_SELECT, depois v_WHEN e por último v_IF_ELSE. | ||

| Linha 232: | Linha 283: | ||

{{fig|2.3|Código RTL do mux 4x1 v_WITH_SELECT| RTL_mux4x1v3.png| 200 px |}} | {{fig|2.3|Código RTL do mux 4x1 v_WITH_SELECT| RTL_mux4x1v3.png| 200 px |}} | ||

:'''OBS''': [https://en.wikipedia.org/wiki/Register-transfer_level Register Transfer-Level] (RTL) é uma abstração na qual o circuito é descrito em termos de fluxo de sinais entre os registradores presentes no hardware e as operações combinacionais realizadas com esses dados. | :'''OBS''': [https://en.wikipedia.org/wiki/Register-transfer_level Register Transfer-Level] (RTL) é uma abstração na qual o circuito é descrito em termos de fluxo de sinais entre os registradores presentes no hardware e as operações combinacionais realizadas com esses dados. | ||

| − | |||

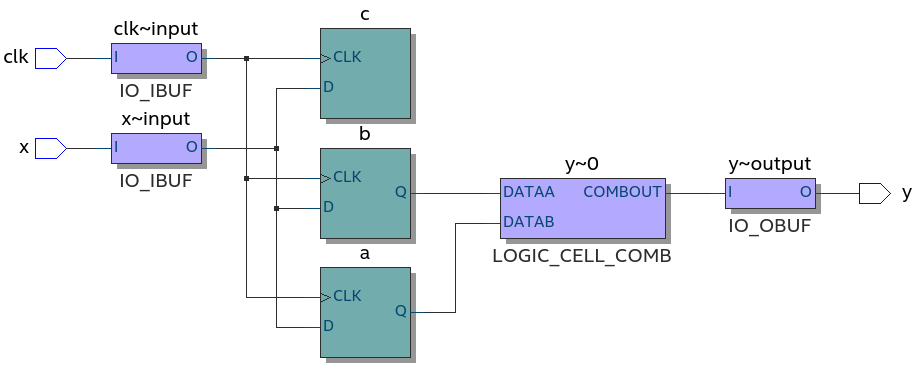

* Note a que ao verificar o Technology Map Viewer, nos 3 primeiros casos serão usados os mesmos elementos lógicos. | * Note a que ao verificar o Technology Map Viewer, nos 3 primeiros casos serão usados os mesmos elementos lógicos. | ||

{{fig|2.4|Technology Map do mux 4x1 para a família Cyclone | TM_mux4x1.png| 400 px |}} | {{fig|2.4|Technology Map do mux 4x1 para a família Cyclone | TM_mux4x1.png| 400 px |}} | ||

| − | |||

* Note que o elemento lógico acima possui uma LUT (LookUp Table) que basicamente implementa o circuito combinacional através de uma tabela de consulta (Tabela Verdade), a qual pode ser visualizada clicando com o botão Direito do Mouse e selecionando Properties, juntamente com Mapa de Karnaugh e seu Circuito Lógico representado por portas. Todas as representações são equivalentes. | * Note que o elemento lógico acima possui uma LUT (LookUp Table) que basicamente implementa o circuito combinacional através de uma tabela de consulta (Tabela Verdade), a qual pode ser visualizada clicando com o botão Direito do Mouse e selecionando Properties, juntamente com Mapa de Karnaugh e seu Circuito Lógico representado por portas. Todas as representações são equivalentes. | ||

| Linha 248: | Linha 297: | ||

{{fig|2.5|Technology Map do mux 4x1 para a família Stratix III | TM_mux4x1_S3.png| 400 px |}} | {{fig|2.5|Technology Map do mux 4x1 para a família Stratix III | TM_mux4x1_S3.png| 400 px |}} | ||

| + | ;Encontro 7 (15 ago.) | ||

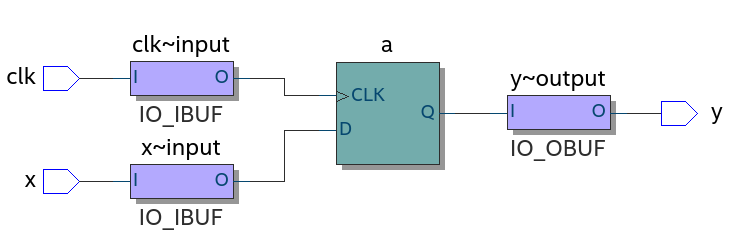

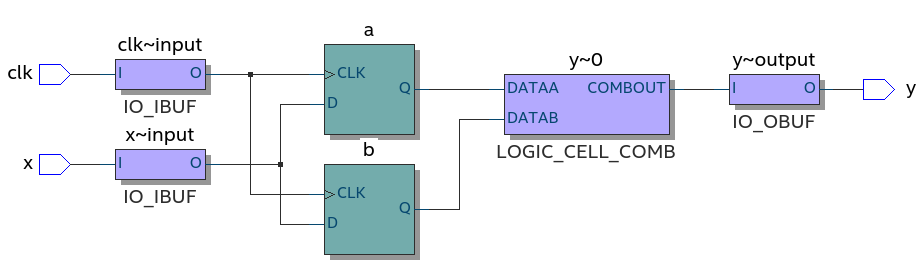

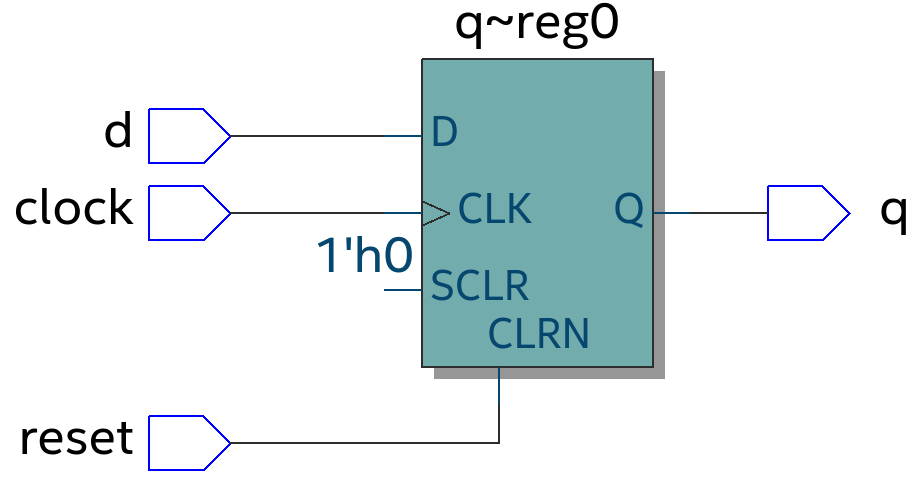

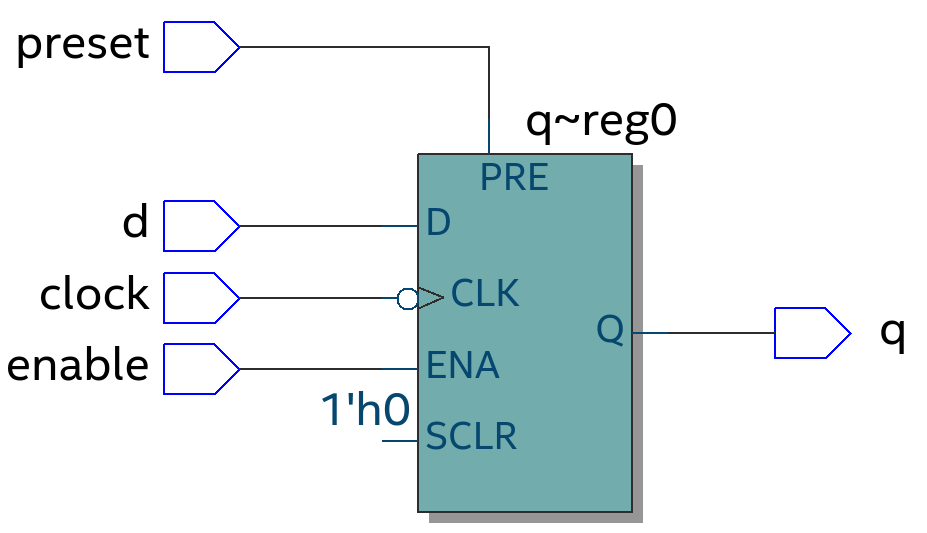

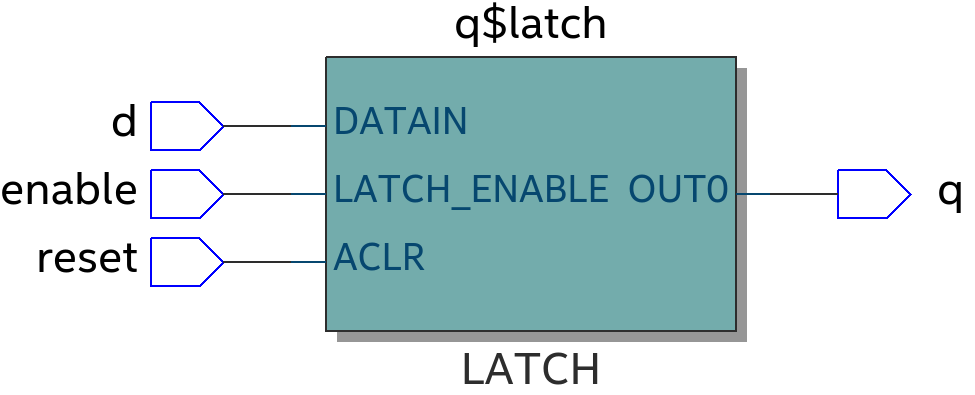

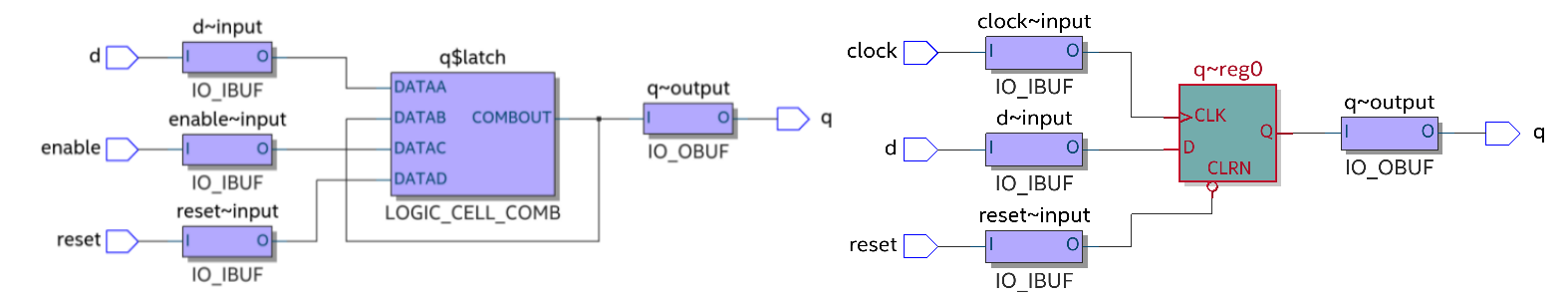

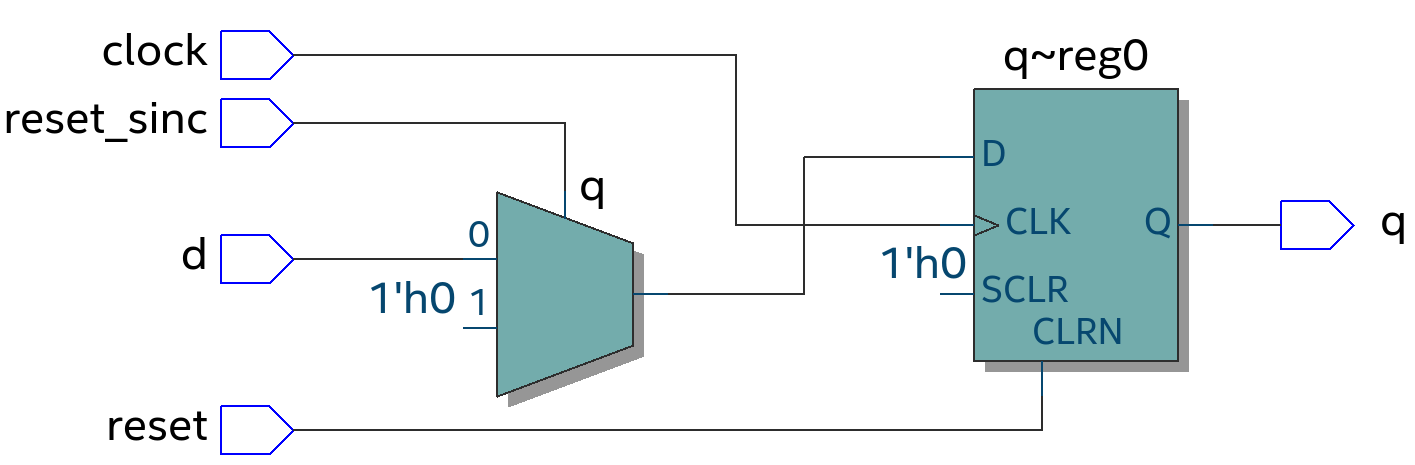

* Exemplo 2.2 (VHDL) - programação de um flip-flop | * Exemplo 2.2 (VHDL) - programação de um flip-flop | ||

| Linha 288: | Linha 338: | ||

| − | |||

* Uso de alguns sites auxiliares para a programação em VHDL: | * Uso de alguns sites auxiliares para a programação em VHDL: | ||

:*[[Preparando para gravar o circuito lógico no FPGA]] | :*[[Preparando para gravar o circuito lógico no FPGA]] | ||

:*[[Palavras reservadas do VHDL]] | :*[[Palavras reservadas do VHDL]] | ||

:*[http://g2384.github.io/work/VHDLformatter.html VHDL Beautifier, Formatter] - para formatar automaticamente um código VHDL. | :*[http://g2384.github.io/work/VHDLformatter.html VHDL Beautifier, Formatter] - para formatar automaticamente um código VHDL. | ||

| − | |||

| − | + | ;Encontro 8 (18 ago.) | |

| − | |||

| − | |||

| − | |||

| − | + | *[[Simulação Funcional usando o ModelSim]] | |

| − | * | + | *Funcionamento do ModelSim: GUI, caracteristicas, testbench |

| − | + | *Prática do Modelsim com bin2bcd | |

| − | + | *Faça a simulação inserindo os valores 64, 99, 09, 00, 01, 109, 190. | |

| + | *Perceba que com 7 bits na entrada, o número 190 não é representado corretamente, pois necessita de 8 bits. | ||

| + | *Perceba que a conversão para BCD do número 109 não é correta, pois o algoritmo implementado só preve a separação de dezena e unidade, e portanto não trata a centena. | ||

| − | ;Encontro 9 | + | ;Encontro 9 (22 ago.) |

| − | * | + | * [[Simulação Funcional usando o ModelSim]] - completar passos 11 e 12. |

| − | + | * Uso das bibliotecas no VHDL. | |

| − | + | :*Library '''std''' | |

| − | + | ::O Package '''standard''': é parte do VHDL desde a primeira versão (1987). Ela contem definição de tipos de dados (BIT, INTEGER, BOOLEAN, CHARACTER, etc.) e seus operadores logicos, aritméticos, de comparação e shift. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | * Uso das bibliotecas no VHDL. | ||

| − | :*Library '''std''' | ||

| − | ::O Package '''standard''': é parte do VHDL desde a primeira versão (1987). Ela contem definição de tipos de dados (BIT, INTEGER, BOOLEAN, CHARACTER, etc.) e seus operadores logicos, aritméticos, de comparação e shift. | ||

::O Package textio fornece os recurso para o tratamento de textos e arquivos, que podem ser utilizados na simulação. | ::O Package textio fornece os recurso para o tratamento de textos e arquivos, que podem ser utilizados na simulação. | ||

*Como declarar e usar os pacotes da biblioteca '''std'''. | *Como declarar e usar os pacotes da biblioteca '''std'''. | ||

| Linha 344: | Linha 366: | ||

use std.textio.all; | use std.textio.all; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | *Onde estão os arquivos dessa biblioteca na versão Quartus | + | *Onde estão os arquivos dessa biblioteca na versão Quartus instalada nos computadores do IFSC e na IFSC_CLOUD? |

| − | ls /opt/ | + | ls /opt/intelFPGA/20.1/quartus/libraries/vhdl/std |

:*Library '''ieee''' | :*Library '''ieee''' | ||

| Linha 374: | Linha 396: | ||

*Onde estão os arquivos dessa biblioteca na versão Quartus II versão 13.0sp1 instalada nos computadores do IFSC e na IFSC_CLOUD? | *Onde estão os arquivos dessa biblioteca na versão Quartus II versão 13.0sp1 instalada nos computadores do IFSC e na IFSC_CLOUD? | ||

::Os pacotes padrão: | ::Os pacotes padrão: | ||

| − | + | /opt/intelFPGA/20.1/quartus/libraries/vhdl/ieee | |

::Os pacotes não padrão: | ::Os pacotes não padrão: | ||

| − | + | /opt/intelFPGA/20.1/quartus/libraries/vhdl/mentor/arithmetic (Mentor Graphics) | |

| − | + | /opt/intelFPGA/20.1/quartus/libraries/vhdl/synopsys/ieee (Synopsys) | |

*Os arquivos dessa biblioteca do padrão (versão 2008) estão apenas disponíveis a partir do Quartus II versão 16.0 instalado na IFSC_CLOUD? | *Os arquivos dessa biblioteca do padrão (versão 2008) estão apenas disponíveis a partir do Quartus II versão 16.0 instalado na IFSC_CLOUD? | ||

ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008 | ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008 | ||

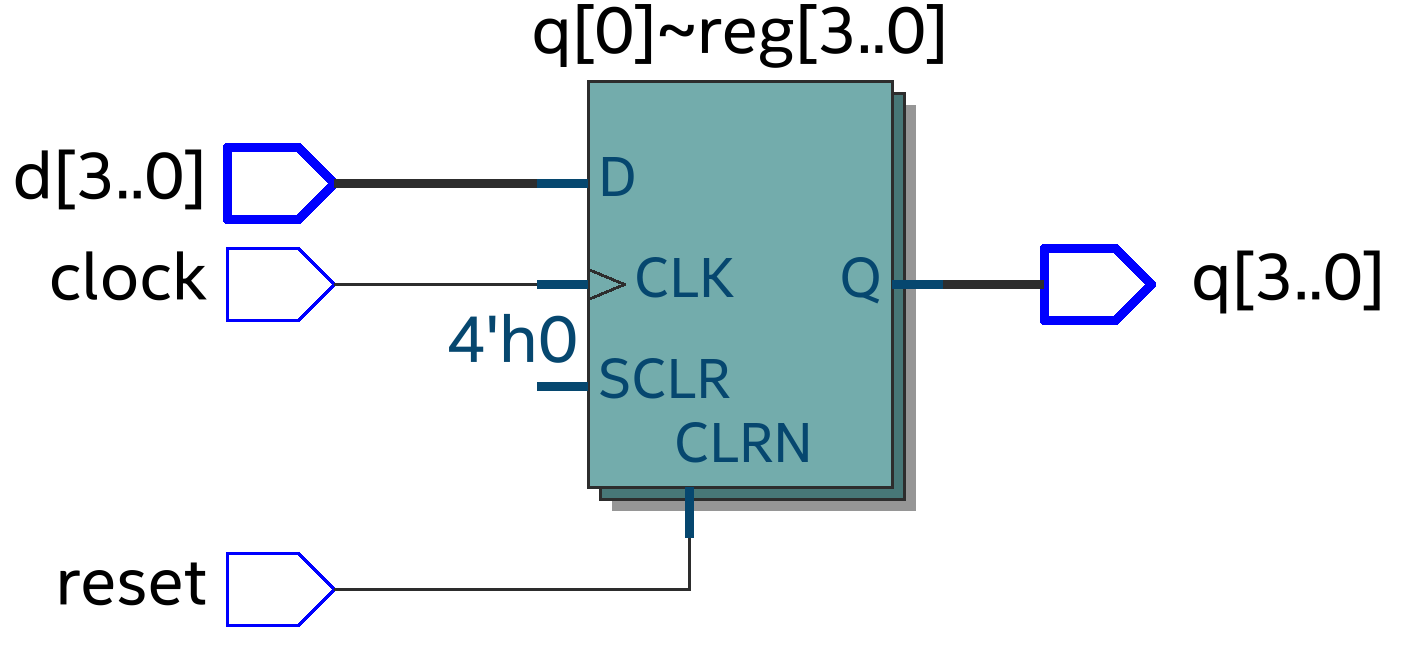

| − | + | * Exemplo 2.3 (VHDL e Modelsim) - programação de um circuito somador com registrador | |

| − | + | : Realizar a simulação funcional do circuito | |

| − | + | : Observar o "Technology Map" e o "RTL" do circuito | |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

LIBRARY ieee; | LIBRARY ieee; | ||

| Linha 412: | Linha 434: | ||

END ARCHITECTURE; | END ARCHITECTURE; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | :: Acrescente saídas para o sinal '''sum''' e para o sinal '''comp''', de modo a poder observar estes sinais no simulador | + | :: Acrescente saídas para o sinal '''sum''' e para o sinal '''comp''', de modo a poder observar estes sinais no simulador Modelsim e realize nova simulação funcional. |

{{fig|2.10|Código RTL do Exemplo 2.3| RTL_Ex2_3_Pedronib.png| 400 px |}} | {{fig|2.10|Código RTL do Exemplo 2.3| RTL_Ex2_3_Pedronib.png| 400 px |}} | ||

| − | + | ;Encontro 10 (23 ago.) | |

| − | + | *Exemplo de um '''contador''' em VHDL. [https://en.wikipedia.org/wiki/VHDL#Example:_a_counter COUNTER] na página de VHDL da Wikipedia. | |

| − | + | <syntaxhighlight lang=vhdl> | |

| − | + | library IEEE; | |

| − | + | use IEEE.std_logic_1164.all; | |

| − | + | use IEEE.numeric_std.all; -- for the unsigned type | |

| + | entity COUNTER is | ||

| + | generic ( | ||

| + | WIDTH : in natural := 32); | ||

| + | port ( | ||

| + | RST : in std_logic; | ||

| + | CLK : in std_logic; | ||

| + | LOAD : in std_logic; | ||

| + | DATA : in std_logic_vector(WIDTH-1 downto 0); | ||

| + | Q : out std_logic_vector(WIDTH-1 downto 0)); | ||

| + | end entity COUNTER; | ||

| − | + | architecture RTL of COUNTER is | |

| − | |||

| − | + | begin | |

| − | === | + | process(all) is |

| − | + | begin | |

| + | if RST then | ||

| + | Q <= (others => '0'); | ||

| + | elsif rising_edge(CLK) then | ||

| + | if LOAD='1' then | ||

| + | Q <= DATA; | ||

| + | else | ||

| + | Q <= std_logic_vector(unsigned(Q) + 1); | ||

| + | end if; | ||

| + | end if; | ||

| + | end process; | ||

| − | + | end architecture RTL; | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | |||

| − | |||

| − | :* | + | :*[[Restringir a frequencia máxima de clock no Quartus II]] |

| − | + | :* Objetivos: Copiar e colar o código no Quartus; diferença entre analise e síntese e compilação; observar o RTL (usar UNGROUP); simulação funcional e simulação temporal (considerando o tempo de propagação). Em função da dificuldade na realização da simulação temporal com o Modelsim, será utilizado excepcionalmente o QSIM para este fim. | |

| − | |||

| − | |||

| − | |||

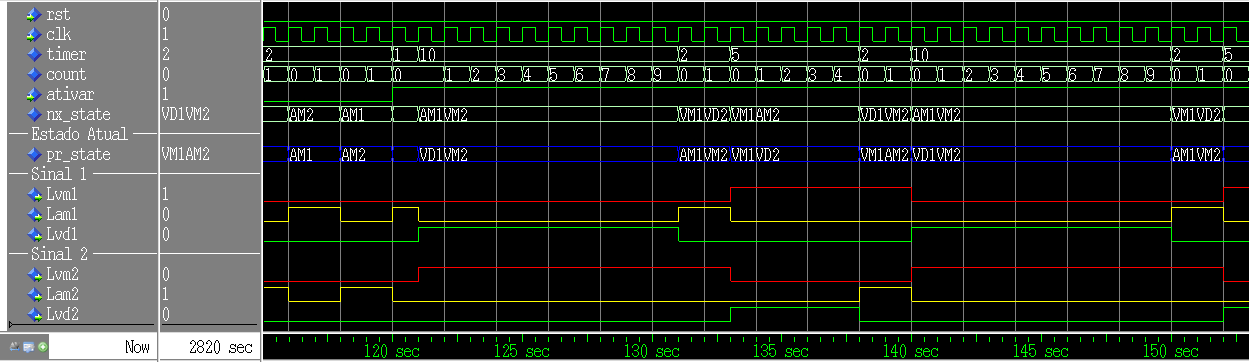

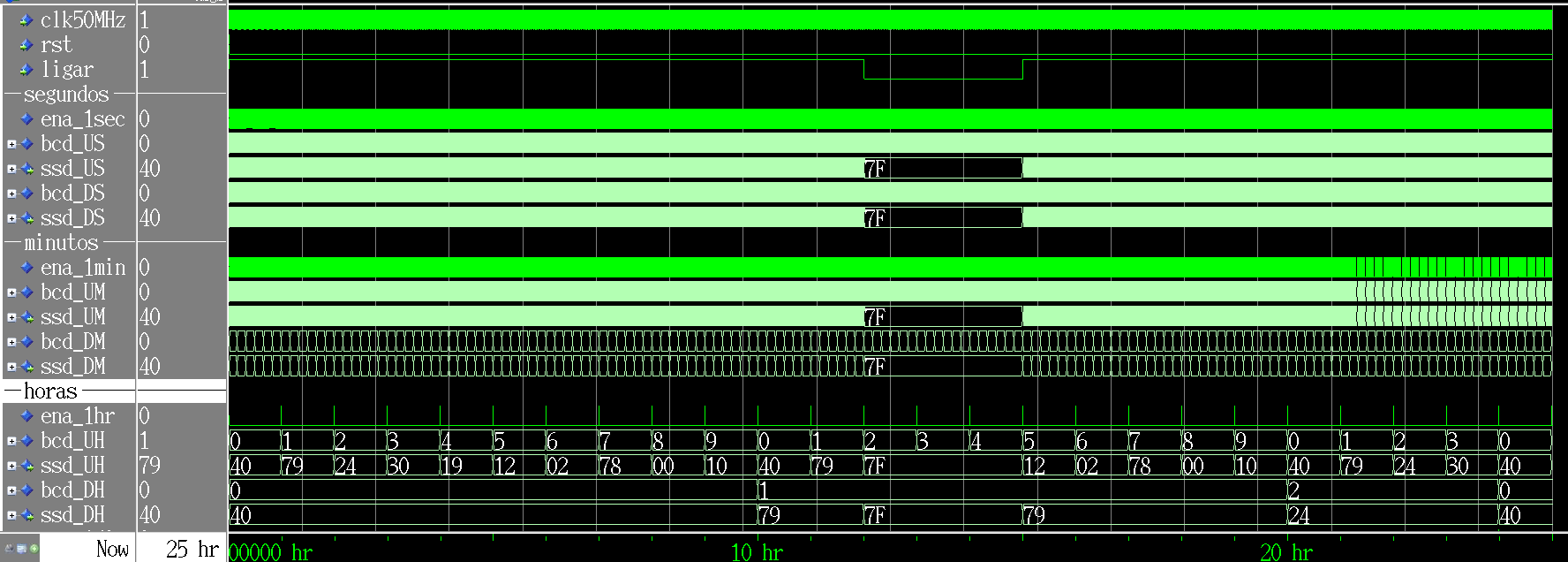

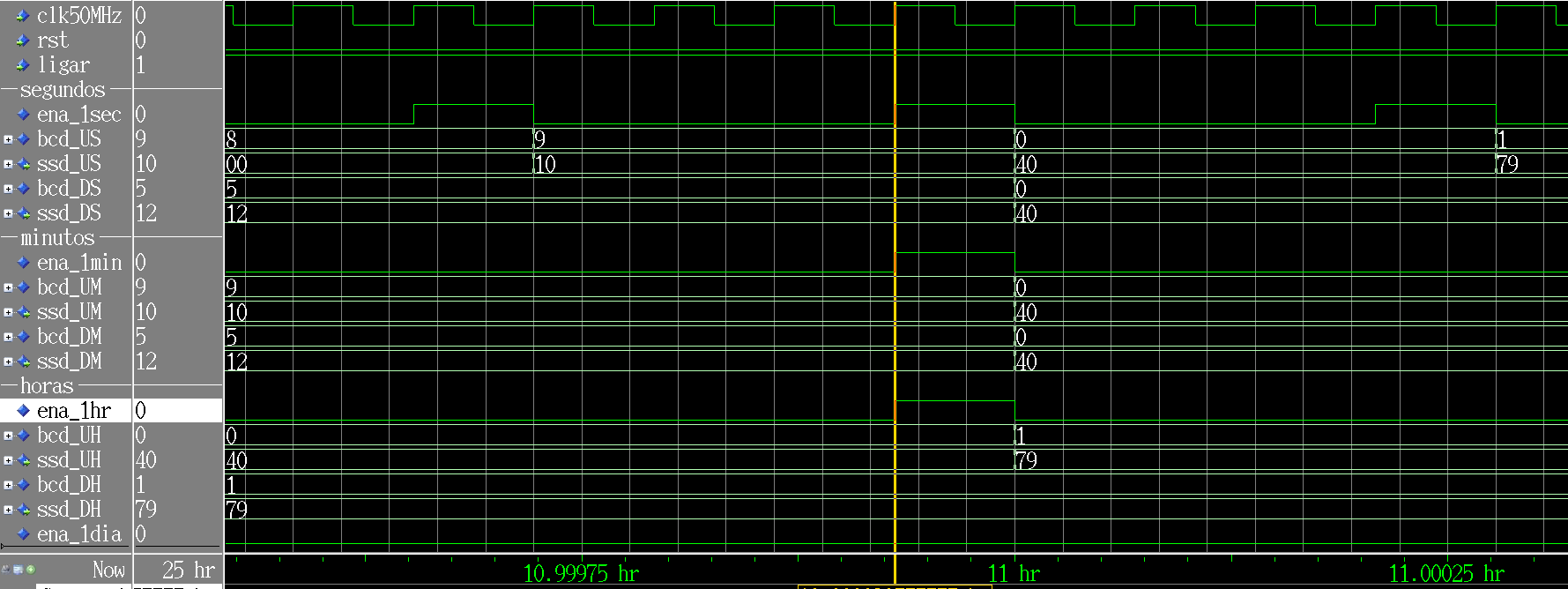

| − | + | *Ao realizar as simulações funcional e temporal do circuito '''Flip-Flop4''' ou do '''Counter''', será possível perceber que enquanto na simulação funcional, as mudanças ocorrem instantaneamente, na temporal, todos os tempos de propagação em vias e nos elementos lógicos são considerados. OBserve atentamente nas duas figuras a seguir as diferenças. | |

| − | |||

| − | |||

| − | |||

| − | + | {{fig|2.6|Simulação funcional com QSIM de 4 FF - 100ns| SIM1_4FF.png| 800 px |}} | |

| − | |||

| − | |||

| − | + | {{fig|2.7|Simulação Temporal com QSIM de 4 FF - 100ns| SIM2_4FF.png| 800 px |}} | |

| − | |||

| − | : | + | :Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existem atrasos variáveos de cerca de ~6ns nestas mudanças. |

| − | |||

| − | |||

| − | |||

| − | : | + | ''IMPORTANTE:'' Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possível verificar se o circuito atende as restrições de tempo. |

| − | |||

| − | |||

| − | * | + | * Para definir as restrições de tempo do clock por exemplo, pode ser adicionado um arquivo .sdc ao projeto definindo a frequência do clock esperada através da seguinte linha: |

| − | |||

| − | + | create_clock -name CLK50MHz -period 50MHz [get_ports {*}] | |

| − | |||

| − | + | *Ver pag. 3 a 24 de <ref name="PEDRONI2010b"> PEDRONI, Volnei A. '''Circuit Design and Simulation with VHDL'''; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 </ref> | |

| − | |||

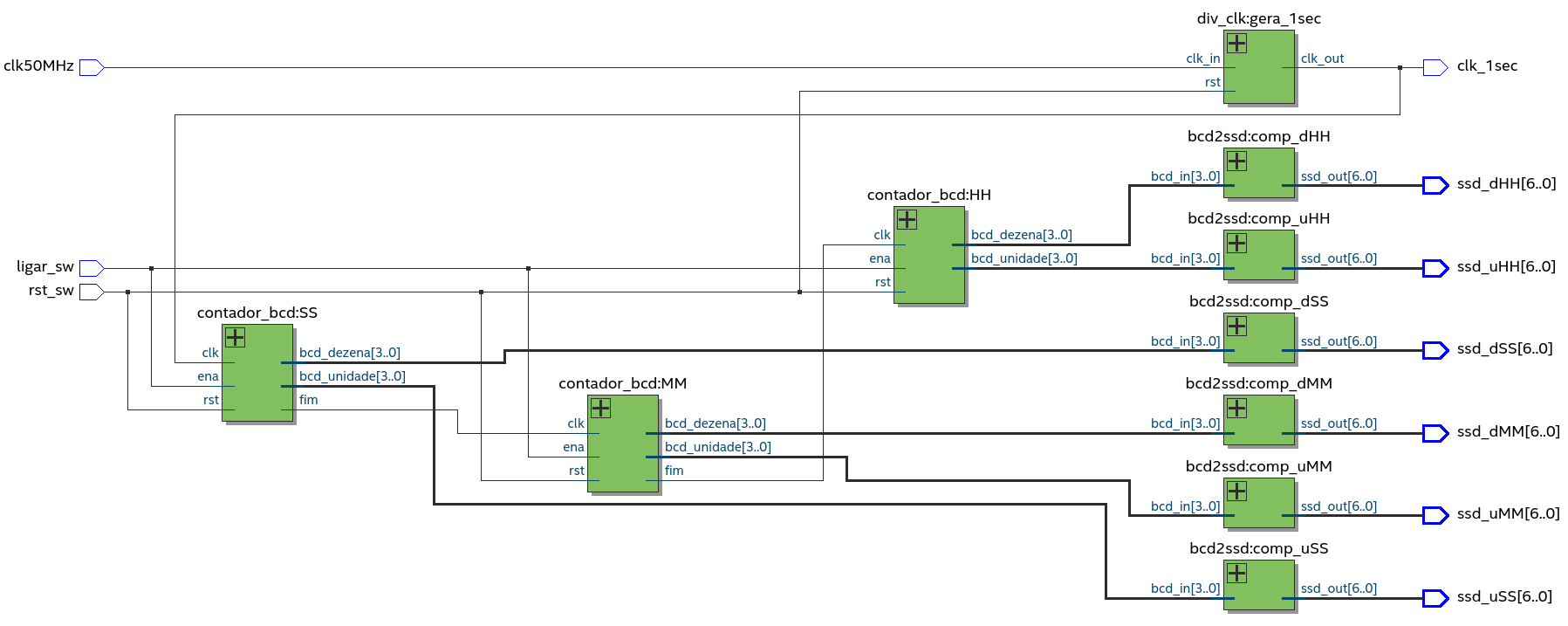

| − | + | ;Encontro 11 e 12 (25 e 29 ago.) | |

| − | + | :* utilizar o código do '''contador''' em VHDL. [https://en.wikipedia.org/wiki/VHDL#Example:_a_counter COUNTER] na página de VHDL da Wikipedia. | |

| − | + | :* Definir a pinagem das chaves e leds conforme o kit a ser utilizado. | |

| − | + | :* Perceber o problema do repique das chaves. | |

| − | + | ::Ver [[Dicas de como eliminar o repique das chaves mecânicas]] | |

| + | :: Ler sobre o problema do repique das chaves mecânicas [https://my.eng.utah.edu/~cs5780/debouncing.pdf A Guide to Debouncing] | ||

| + | *Realizar [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE3_-_Programa.C3.A7.C3.A3o_do_kit_Mercurio_IV AE3 - Programação do kit Mercurio IV]. | ||

| + | *Medir o repique da chave e a solução com osciloscópio. | ||

| + | {{collapse bottom}} | ||

| − | + | ===Unidade 3 - Tipos de Dados e Operadores em VHDL=== | |

| + | * 10 ENCONTROS | ||

| + | {{collapse top | expand=true | Unidade 3 - Tipos de Dados e Operadores em VHDL}} | ||

| + | ;Encontro 13 (1 set.) | ||

| + | *Comentários no código (duplo traço --) | ||

| + | -- Isso eh uma linha de comentario | ||

| + | y <= a * b ; --o sinal y recebe o resultado da multiplicacao a x b | ||

| + | *Representação de caracteres, strings e números em VHDL. No circuito, os caracteres são representados através de bits de acordo com a [https://www.lookuptables.com/text/ascii-table tabela ASCII] básica (00 a 7F). A definição dessa tabela é feita o pacote '''[[standard.vhd]]''' da biblioteca '''std'''. | ||

| + | :*Caracteres (entre aspas simples) | ||

| + | caracter: 'A' 'x' '#' (com aspas simples) | ||

| + | :*Palavras (entre aspas duplas), é definida no VHDL como um vetor de caracteres. | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | type string is array (positive range <>) of character; | |

| − | + | </syntaxhighlight> | |

| + | |||

| + | string: "IFSC" "teste" "teste123" | ||

| − | + | :*Números em geral | |

| + | elemento ("bit") único: '0' '1' 'Z' (entre aspas simples) | ||

| + | vetor de elementos ("bits"): "0110" "101001Z" (entre aspas duplas) | ||

| + | vetor de 1 elemento ("bit"): "0" "1" (entre aspas duplas) | ||

| + | inteiros: 5 1101 1102 (sem aspas) | ||

| − | -- | + | :*Números binários: |

| − | + | 0 -> '0' | |

| + | 7 (em base 2) -> "0111" ou b"0111" ou B"0111" | ||

| + | 1023 (em base 2) -> "001111111111" ou b"1111111111" ou B"1111111111" | ||

| − | -- | + | :*Números octais: |

| + | 44 (em base 8) -> 5*8^1 + 4*8^0 -> O"54" ou o"54" | ||

| + | 1023 (em base 8)-> 1*8^3 + 7*8^2 + 7*8^1 + 7*8^0 -> o"1777" 8#1777# | ||

| − | + | :*Números Hexadecimais: | |

| − | + | 1023 (em base 16) -> 3*16^2 + 15*16^1 + 15*16^0 = X"3FF" ou x"3FF" 16#3FF# | |

| − | |||

| − | |||

| − | |||

| − | + | :*Números decimais: | |

| + | 1023 -> 1023 ou 1_023 | ||

| + | 1000 -> 1000 ou 1_000 ou 1E3 ou 10#1000# | ||

| + | ::Cuidado ao usar o "_" pois algumas ferramentas não o reconhecem. | ||

| + | |||

| + | :*Números em outras bases (de 2 a 16) | ||

| + | 85 (em base 5) -> (3*5^2 + 2*5^1 + 0*5^0) -> 5#320# | ||

| + | 1539 (em base 3) -> (2*3^2+0*3^1+1*3^0)*3^4 -> 3#201#E4 | ||

| + | |||

| + | *Tipos de dados em VHDL. | ||

| + | :*Objetos de VHDL: '''CONSTANT''', '''SIGNAL''', '''VARIABLE''', '''FILE'''. | ||

| + | O objeto '''CONSTANT''' pode ser declarado na parte declarativa da ENTITY, ARCHITECTURE, PACKAGE, PACKAGE_BODY, BLOCK, GENERATE, PROCESS, FUNCTION e PROCEDURE. | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | |||

| − | |||

| − | + | constant <constant_name> : <type> := <constant_value>; | |

| − | |||

| − | -- | + | -- Declarações comuns de constantes |

| − | |||

| − | + | constant GND : std_logic := '0'; | |

| − | + | constant VCC : std_logic := '1'; | |

| − | + | constant SSD_0 : std_logic_vector(0 to 6) := "1111110"; | |

| − | + | constant MAX : natural := 44; | |

| − | |||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | O objeto '''SIGNAL''' pode ser declarado na parte declarativa da ENTITY, ARCHITECTURE, PACKAGE, BLOCK, GENERATE. Os sinais não podem ser declarados no código sequencial (PROCESS, FUNCTION e PROCEDURE), mas podem ser usados. | |

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | -- Signal sem valor default | |

| + | -- Para atribuir um valor a um signal use "<=" como operador. | ||

| − | + | signal <name> : <type>; | |

| − | |||

| − | |||

| − | + | -- Signal com valor default | |

| − | + | signal <name> : <type> := <default_value>; | |

| − | + | -- Declarações comuns de signals | |

| − | |||

| + | signal <name> : std_logic; | ||

| + | signal <name> : std_logic_vector(<msb_index> downto <lsb_index>); | ||

| + | signal <name> : integer; | ||

| + | signal <name> : integer range <low> to <high>; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | O objeto '''VARIABLE''' (variável) só pode ser declarada e usada dentro do escopo no código sequencial (PROCESS, FUNCTION e PROCEDURE). | |

| − | : | + | <syntaxhighlight lang=vhdl> |

| − | :: | + | -- Variables devem ser declarada em process ou subprogramas. |

| + | -- Para atribuir um valor a um variable use ":=" como operador. | ||

| + | |||

| + | -- Variable sem valor default. | ||

| + | variable <name> : <type>; | ||

| + | |||

| + | -- Variable com valor default. | ||

| + | variable <name> : <type> := <default_value>; | ||

| − | + | -- Declarações comuns de variables | |

| + | variable <name> : std_logic; | ||

| + | variable <name> : std_logic_vector(<msb_index> downto <lsb_index>); | ||

| + | variable <name> : integer; | ||

| + | variable <name> : integer range <low> to <high>; | ||

| + | </syntaxhighlight> | ||

| − | + | :*Palavra chave '''OTHERS''' para formação de agregados | |

| + | Exemplos de declaração de CONSTANT, SIGNAL, VARIABLE, inicializando o valor usando o agregados | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | package standard is | + | CONSTANT a: BIT_VECTOR(5 DOWNTO 0) := (OTHERS => '0'); -- "000000" |

| − | type boolean is (false,true); | + | |

| − | type bit is ('0', '1'); | + | CONSTANT b: BIT_VECTOR(7 DOWNTO 0) := (7 => '0', OTHERS => '1'); -- "01111111" |

| − | type severity_level is (note, warning, error, failure); | + | CONSTANT c: BIT_VECTOR(7 DOWNTO 0) := (7 => '0', 6 DOWNTO 0 => '1'); -- "01111111" |

| + | CONSTANT d: BIT_VECTOR(7 DOWNTO 0) := "01111111"; | ||

| + | |||

| + | SIGNAL e: STD_LOGIC_VECTOR(7 DOWNTO 0); -- Not initialized | ||

| + | SIGNAL f: STD_LOGIC_VECTOR(1 TO 8) := (2|3|8 => '1', 4 => 'Z', OTHERS => '0' ); -- "011Z0001" | ||

| + | |||

| + | VARIABLE g: BIT_VECTOR(1 TO 16); -- Not initialized | ||

| + | VARIABLE h: BIT_VECTOR(1 TO 16) := (1 TO 8 => '1', OTHERS => '0'); -- "1111111100000000" | ||

| + | |||

| + | </syntaxhighlight> | ||

| + | |||

| + | :: Ver pag. 31 a 35 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | :* Bibliotecas padrão IEEE ('''[[Std logic 1164.vhd]]''', '''[[Numeric std.vhd]]'''). | ||

| + | ::* '''ATENÇÃO!!! Não use as bibliotecas que não são padrão (''std_logic_arith, std_logic_unsigned, std_logic_signed''''') | ||

| + | |||

| + | * Classificação dos tipos de dados. | ||

| + | |||

| + | A biblioteca [[standard.vhd]] define os tipos BIT, BIT_VECTOR, BOOLEAN, INTEGER, NATURAL, POSITIVE, CHARACTER, STRING. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | package standard is | ||

| + | type boolean is (false,true); | ||

| + | type bit is ('0', '1'); | ||

| + | type severity_level is (note, warning, error, failure); | ||

type integer is range -2147483647 to 2147483647; | type integer is range -2147483647 to 2147483647; | ||

type real is range -1.0E308 to 1.0E308; | type real is range -1.0E308 to 1.0E308; | ||

| Linha 579: | Linha 655: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| + | |||

| + | ;Encontro 14 (5 set.) | ||

A biblioteca [[Std logic 1164.vhd]] define os tipos STD_(U)LOGIG, STD_(U)LOGIG_VECTOR. | A biblioteca [[Std logic 1164.vhd]] define os tipos STD_(U)LOGIG, STD_(U)LOGIG_VECTOR. | ||

| Linha 626: | Linha 704: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | |||

A biblioteca [[Numeric std.vhd]] define os tipos UNSIGNED e SIGNED. | A biblioteca [[Numeric std.vhd]] define os tipos UNSIGNED e SIGNED. | ||

| Linha 635: | Linha 712: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | A biblioteca [[Numeric std.vhd]] ainda define os operadores (abs, "+", "-", "*", " | + | A biblioteca [[Numeric std.vhd]] ainda define os operadores (abs, "+", "-", "*", "/", rem, mod, sll, slr, ror, rol), comparações ("=", '/=', ">", ">=", "<", "<=") e operadores lógicos (not, and, nand, or, nor, xor, xnor) para os tipos SIGNED e UNSIGNED. Além disso também define algumas funções muito utilizadas como: |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 668: | Linha 745: | ||

| BIT || standard || std || valores '0', '1' || sintetizável | | BIT || standard || std || valores '0', '1' || sintetizável | ||

|- | |- | ||

| − | | INTEGER || standard || std || números inteiros de 32 bits [de -2^31 até + (2^31 - 1)] || sintetizável | + | | INTEGER || standard || std || números inteiros de 32 bits [de -2^31-1 até + (2^31 - 1)] || sintetizável |

|- | |- | ||

| NATURAL || standard || std || números inteiros não negativos [de 0 até + (2^31 - 1)] || sintetizável | | NATURAL || standard || std || números inteiros não negativos [de 0 até + (2^31 - 1)] || sintetizável | ||

| Linha 678: | Linha 755: | ||

| BIT_VECTOR || standard || std || vetor de BIT || sintetizável | | BIT_VECTOR || standard || std || vetor de BIT || sintetizável | ||

|- | |- | ||

| − | | INTEGER_VECTOR || standard || std || vetor de INTEGER || sintetizável | + | | INTEGER_VECTOR || standard (2008) || std || vetor de INTEGER || sintetizável |

|- | |- | ||

| REAL || standard || std || números reais [de -1.0E-38 até + 1.0E38] || simulação | | REAL || standard || std || números reais [de -1.0E-38 até + 1.0E38] || simulação | ||

| Linha 710: | Linha 787: | ||

* Tipos de dados predefinidos: FIXED e FLOAT (apenas conhecer) | * Tipos de dados predefinidos: FIXED e FLOAT (apenas conhecer) | ||

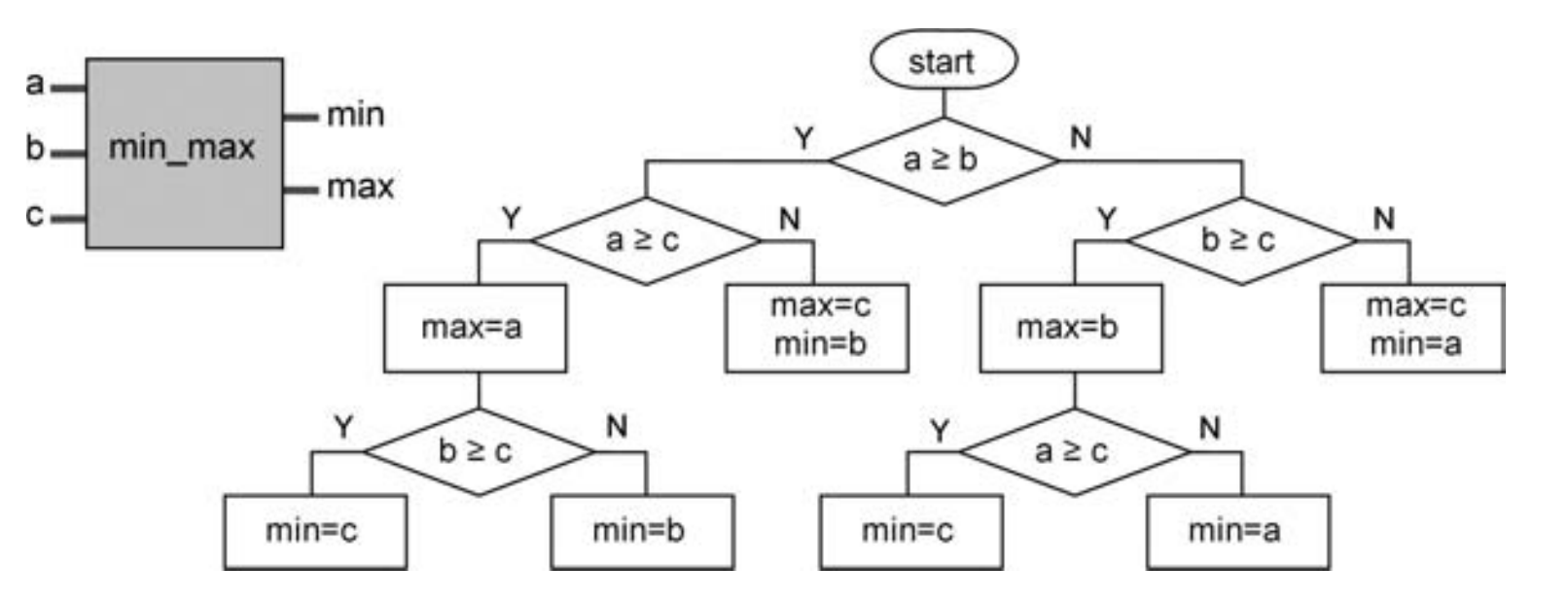

| − | + | * '''Desafio 1''' - Fazer um circuito que detecte se existe alguma vaga vazia em um lote de 9 vagas. A entrada '''x(n)''' está baixo '0' se a vaga está vazia, e alto '1' se tem carro. A saída '''y''' estará alta '1' sempre que houver uma ou mais vagas vazias, e em baixo '0' se não houver nenhuma vaga. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | * '''Desafio 1''' - Fazer um circuito que detecte se existe alguma vaga vazia em um lote de 9 vagas. A entrada '''x(n)''' está baixo '0' se a vaga está vazia, e alto '1' se tem carro. A saída '''y''' estará alta '1' sempre que houver uma ou mais vagas vazias, e em baixo '0' se não houver nenhuma vaga. | ||

*Faça a simulação do circuito para ver se está funcionando, | *Faça a simulação do circuito para ver se está funcionando, | ||

| Linha 725: | Linha 797: | ||

{{fig|3.2| Simulação do contador de vagas | cntvagas9.png | 800 px |}} | {{fig|3.2| Simulação do contador de vagas | cntvagas9.png | 800 px |}} | ||

| + | ;Encontro 15 (6 set.) | ||

* Exemplo 3.1 Buffer Tri-state | * Exemplo 3.1 Buffer Tri-state | ||

| Linha 753: | Linha 826: | ||

::* Analise se seria possível modificar as portas para o tipo '''bit'''. | ::* Analise se seria possível modificar as portas para o tipo '''bit'''. | ||

:: '''Importante''': O terceiro estado 'Z' só pode ser usado em saídas, e a sua realização nos FPGAs só ocorre nos nós de I/O. | :: '''Importante''': O terceiro estado 'Z' só pode ser usado em saídas, e a sua realização nos FPGAs só ocorre nos nós de I/O. | ||

| + | ;Curiosidade: Existem circuitos comerciais que implementam essa função three-state [https://www.ti.com/lit/ds/symlink/sn74lvc16244a-q1.pdf?ts=1681232207751&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FSN74LVC16244A-Q1 16 buffers], [https://www.ti.com/lit/ds/symlink/sn74lv244a-ep.pdf?ts=1681237777688&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FSN74LV244A-EP 8 buffers], [https://www.ti.com/lit/ds/symlink/sn74auc1g126.pdf?ts=1681222704977&ref_url=https%253A%252F%252Fwww.google.com%252F 1 buffer]. Porque não utilizar um CPLD ou FPGA em seu lugar? | ||

| + | ;Encontro 16 (12 set.) | ||

:* Exemplo 3.2 Circuito com Saida "don't care" | :* Exemplo 3.2 Circuito com Saida "don't care" | ||

| Linha 778: | Linha 853: | ||

* '''Desafio 3''' - Fazer um circuito que detecte se existe alguma vaga vazia em um lote de 9 vagas. A entrada '''x(n)''' está baixo '0' se a vaga está vazia, e alto '1' se tem carro. A saída '''y''' estará alta '1' sempre que houver uma ou mais vagas vazias, e em baixo '0' se não houver nenhuma vaga. Inspirado na descrição VHDL acima, tente resolver esse problema usando ''don't care''. | * '''Desafio 3''' - Fazer um circuito que detecte se existe alguma vaga vazia em um lote de 9 vagas. A entrada '''x(n)''' está baixo '0' se a vaga está vazia, e alto '1' se tem carro. A saída '''y''' estará alta '1' sempre que houver uma ou mais vagas vazias, e em baixo '0' se não houver nenhuma vaga. Inspirado na descrição VHDL acima, tente resolver esse problema usando ''don't care''. | ||

| − | |||

:'''Importante''': O ''don't care'' não funciona como se espera para uma entrada, por isso, use ''don't care'' apenas para saídas. | :'''Importante''': O ''don't care'' não funciona como se espera para uma entrada, por isso, use ''don't care'' apenas para saídas. | ||

| Linha 785: | Linha 859: | ||

std_match(x, "1----") -- funciona em VHDL | std_match(x, "1----") -- funciona em VHDL | ||

| − | {{collapse | + | :* Tipos de dados: SIGNED e UNSIGNED |

| + | |||

| + | :* Exemplo 3.3 Multiplicador de 4x4 bits (UN)SIGNED e INTEGER | ||

| + | |||

| + | {{collapse top | expand=true| Código Multiplicador}} | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | --LIBRARY ieee; | ||

| + | --USE ieee.numeric_std.all; | ||

| + | --USE ieee.std_logic_1164.all; | ||

| − | + | ENTITY multiplicador4x4 IS | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | -- multiplicador usando INTEGER (positivos) | |

| − | + | -- PORT (a, b: IN INTEGER RANGE 0 TO 15; -- min(a) = 0; max(a) = 15 -> 4 bits | |

| + | -- y: OUT INTEGER RANGE 0 TO 225); -- min(a*b) = 0, max(a*b) = 225 -> 8 bits | ||

| − | + | -- multiplicador usando INTEGER (positivos e negativos) | |

| − | + | -- PORT (a, b: IN INTEGER RANGE -8 TO 7; -- min(a) = -8; max(a) = 7 -> 4 bits | |

| + | -- y: OUT INTEGER RANGE -56 TO 64); -- min(a*b) = -56, max(a*b) = 64 -> 8 bits | ||

| − | + | -- multiplicador usando UNSIGNED | |

| + | -- PORT (a, b: IN UNSIGNED(3 DOWNTO 0); -- min(a) = 0; max(a) = 15 <- 4 bits | ||

| + | -- y: OUT UNSIGNED(7 DOWNTO 0)); -- min(a*b) = 0, max(a*b) = 225 -> 8 bits | ||

| − | === | + | -- multiplicador usando SIGNED |

| − | + | -- PORT (a, b: IN SIGNED(3 DOWNTO 0); -- min(a) = -8; max(a) = 7 <- 4 bits | |

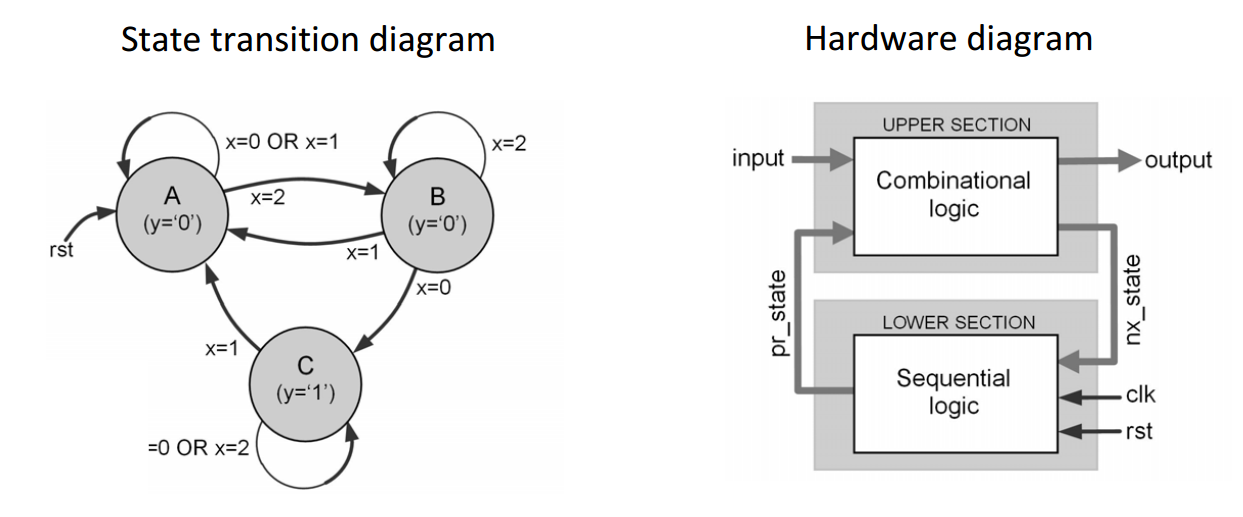

| − | + | -- y: OUT SIGNED(7 DOWNTO 0)); -- min(a*b) = -56, max(a*b) = 64 -> 8 bits | |

| − | + | ||

| − | + | ||

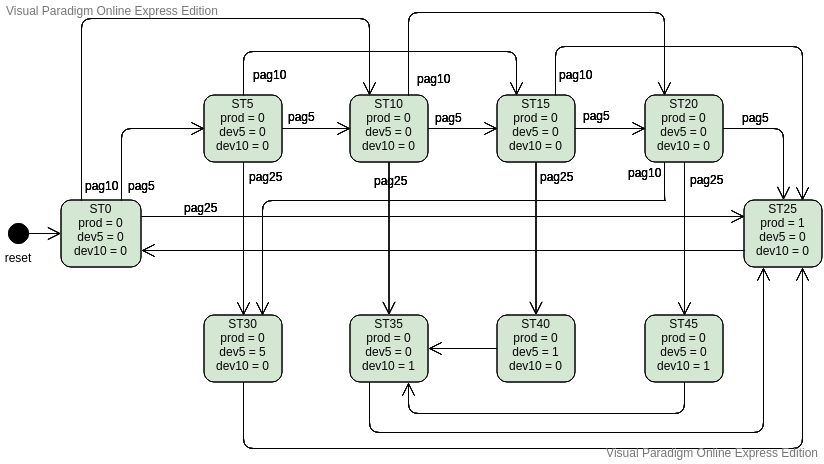

| − | * | + | -- multiplicador usando STD_LOGIC_VECTOR |

| − | * | + | -- PORT (a, b: IN STD_LOGIC_VECTOR(3 DOWNTO 0); -- min(a) = 0; max(a) = 15 <- 4 bits |

| + | -- y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); -- min(a*b) = 0, max(a*b) = 225 -> 8 bits | ||

| + | |||

| + | -- multiplicador usando STD_LOGIC_VECTOR | ||

| + | -- PORT (a, b: STD_LOGIC_VECTOR(3 DOWNTO 0); -- min(a) = -8; max(a) = 7 <- 4 bits | ||

| + | -- y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); -- min(a*b) = -56, max(a*b) = 64 -> 8 bits | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | END ENTITY; | |

| − | |||

| − | |||

| − | + | ARCHITECTURE v1 OF multiplicador4x4 IS | |

| − | + | BEGIN | |

| − | + | y <= a * b; | |

| − | + | END ARCHITECTURE; | |

| − | + | </syntaxhighlight> | |

| − | |||

| − | |||

| − | |||

| − | |||

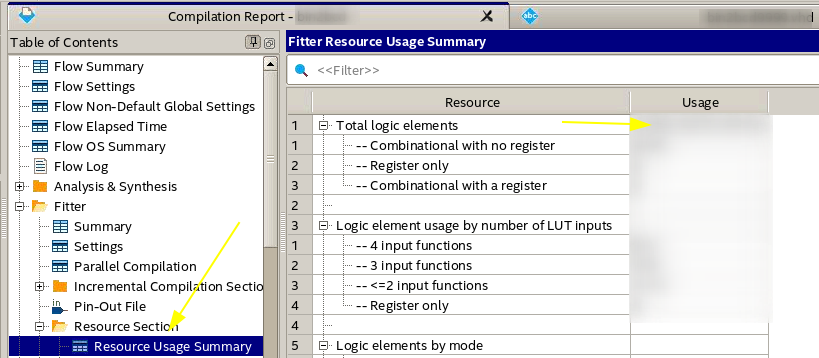

| − | * | + | *Observar o número de elementos lógicos, bits usados para representar as entradas e saídas. |

| − | + | *Observar o código RTL obtido. | |

| + | *Realizar a simulação com entradas UNSIGNED e INTEGER na faixa de valores de 0 até 15, e analisar se o valor da saída está correto. | ||

| + | *Realizar a simulação com entradas SIGNED e INTEGER na faixa de valores de -8 até 7, e analisar se o valor da saída está correto. | ||

| + | *Realizar a simulação com entradas STD_LOGIC_VECTOR na faixa de valores de 0 até 15, e analisar se o valor da saída está correto. Neste caso será necessário realizar uma conversão de STD_LOGIC_VECTOR para UNSIGNED antes de efetuar a operação de "*", e após a operação é necessário fazer a operação inversa UNSIGNED para STD_LOGIC_VECTOR | ||

| + | *Realizar a simulação com entradas STD_LOGIC_VECTOR na faixa de valores de -8 até 7, e analisar se o valor da saída está correto. Neste caso será necessário realizar uma conversão de STD_LOGIC_VECTOR para SIGNED antes de efetuar a operação de "*", e após a operação é necessário fazer a operação inversa SIGNED para STD_LOGIC_VECTOR | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | === | + | <center> |

| − | + | {{Mensagem | |

| − | ; | + | |indent = |

| − | * | + | |title= |

| − | + | |equation = <big> Ler e guardar a página sobre [[Aritmética com vetores em VDHL]] </big> | |

| − | * | + | |cellpadding= 6 |

| + | |border | ||

| + | |border colour = #0073CF | ||

| + | |background colour=#F5FFFA}} | ||

| + | </center> | ||

| + | |||

| + | |||

| + | :: Ver pag. 39 a 54 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | ;Encontro 17 (15 set.) | ||

| + | *Operadores em VHDL. | ||

| + | :* Operadores predefinidos: Atribuição, Lógicos, Aritméticos, Comparação, Deslocamento, Concatenação, "Matching". | ||

| + | |||

| + | ;Operadores aritméticos: | ||

| + | São suportados nos tipos de dados: INTEGER, NATURAL, POSITIVE, SIGNED e UNSIGNED. Com VHDL 2008 também suportado para UFIXED, SFIXED e FLOAT. | ||

| + | |||

| + | soma (+) | ||

| + | subtração (-) | ||

| + | multiplicação (*) | ||

| + | divisão (/) | ||

| + | exponenciação (**) | ||

| + | valor absoluto (ABS) | ||

| + | resto (REM ''remainder'') | ||

| + | módulo (MOD) | ||

| + | |||

| + | Não há restrições para síntese de circuitos com os operadores, exceto para '''"**"''' que necessita de expoente estático ('''a**5''') ou base estática ('''5**a'''). | ||

| + | |||

| + | O operador '''x/y''' é a divisão inteira com sinal. | ||

| + | :Exemplos: 9/10 = 0; -7/3 = -2; 9/-4 = -2; 20/(-4) = -5. | ||

| + | |||

| + | O operador '''ABS x''' retorna o valor absoluto de x. | ||

| + | :Exemplos: ABS 6 = 6; ABS -11 = 11. | ||

| + | |||

| + | O operador '''x REM y''' retorna o resto de '''x/y''' com sinal de '''x'''. Esse operador realiza a operação '''x REM y = x - (x/y)*y'''. | ||

| + | :Exemplos: 9 REM 10 = 9; -7 REM 3 = -1; 9 REM -4 = 1; 20 REM (-4) = 0. | ||

| + | |||

| + | O operador '''x MOD y''' retorna o resto de '''x/y''' com sinal de '''y'''. Esse operador realiza a operação '''x MOD y = x REM y + a*y''', onde '''a = 1''' quando o sinal de x é diferente do sinal de y, e '''a = 0''' se os sinais de x e y são iguais. | ||

| + | :Exemplos: 9 MOD 10 = 9 ; -7 MOD 3 = 2; 9 MOD -4 = -3; 20 REM (-4) = 0. | ||

| + | |||

| − | + | :: Ver pag. 91 a 97 de <ref name="PEDRONI2010b"/> | |

| − | |||

| − | |||

| − | |||

| − | <syntaxhighlight lang=vhdl> | + | ;Exemplo de uso de operadores aritméticos: |

| − | entity | + | :* Exemplo conversor de binário para [[BCD - Binary-coded decimal]] de dois dígitos decimais (00 a 99). Para ilustrar são utilizadas os operadores DIVISOR e RESTO. Note a quantidade de elementos lógicos utilizados. É possível reduzir essa quantidade, aproveitando resultados intermediários e evitando a realização de uma nova divisão pelo uso do operador REM. Faça uma segunda implementação que reduza significativamente o número de elementos lógicos. |

| − | + | ||

| − | + | <syntaxhighlight lang=vhdl> | |

| − | + | library ieee; | |

| − | + | use ieee.std_logic_1164.all; | |

| − | + | use ieee.numeric_std.all; | |

| − | + | ||

| − | + | entity bin2bcd is | |

| − | + | port | |

| − | + | ( | |

| + | |||

| + | A : in std_logic_vector (6 downto 0); | ||

| + | sd, su : out std_logic_vector (3 downto 0) | ||

| + | ); | ||

| + | end entity; | ||

| + | |||

| + | architecture ifsc_v1 of bin2bcd is | ||

| + | signal A_uns : unsigned (6 downto 0); | ||

| + | signal sd_uns, su_uns : unsigned (6 downto 0); | ||

| − | |||

| − | |||

begin | begin | ||

| − | + | sd <= std_logic_vector(resize(sd_uns, 4)); | |

| − | + | su <= std_logic_vector(resize(su_uns, 4)); | |

| − | + | sd_uns <= A_uns/10; | |

| − | + | su_uns <= A_uns rem 10; | |

| − | + | A_uns <= unsigned(A); | |

| − | + | end architecture; | |

| − | + | ||

| − | + | architecture ifsc_v2 of bin2bcd is | |

| − | + | ||

| − | + | begin | |

| − | + | -- Implemente o circuito usando a definição de REM que é: x REM y = x - (x/y)*y | |

| − | + | end architecture; | |

| − | + | ||

| − | + | configuration bin2bcd_cfg of bin2bcd is | |

| − | + | --A instrução '''configuration''' associa a '''entity''' bin2bcd a '''architecture'''. | |

| − | + | for ifsc_v1 end for; | |

| + | --Para associar a '''entity''' bin2bcd a '''architecture''' ifsc_v2 comente a linha acima e descomente a linha abaixo. | ||

| + | -- for ifsc_v2 end for; | ||

| + | end configuration; | ||

| + | </syntaxhighlight> | ||

| + | |||

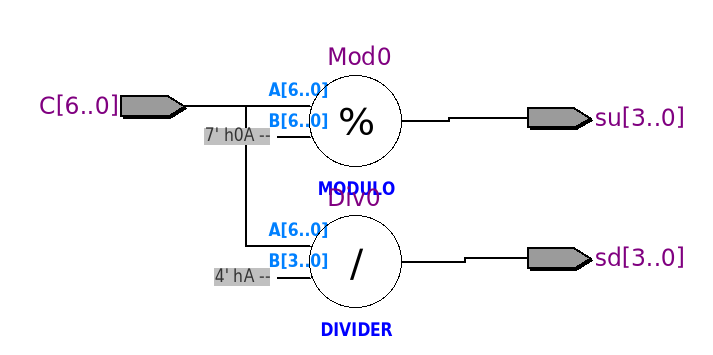

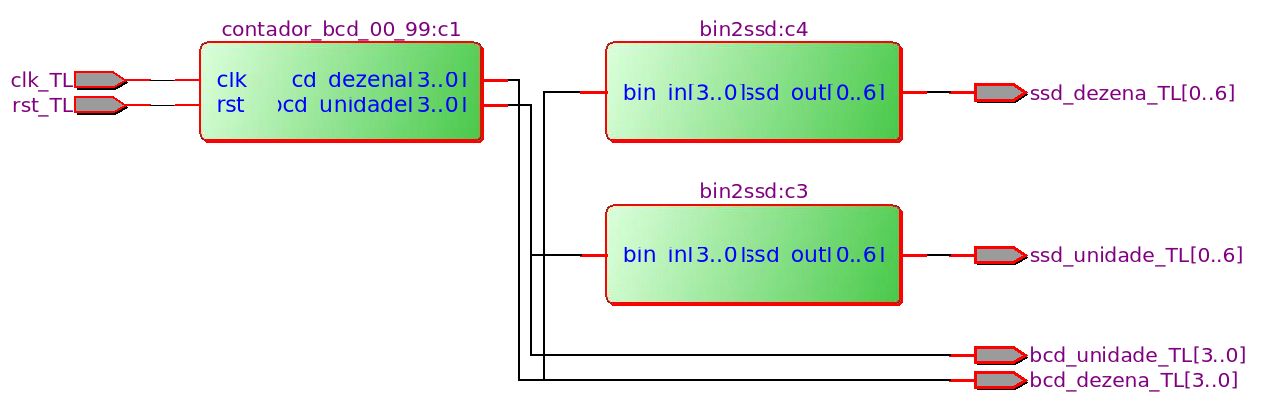

| + | {{fig|3.2| RTL do conversor de Binário para BCD com 2 digitos | bin2bcdDU_RTL.png | 600 px |}} | ||

| + | |||

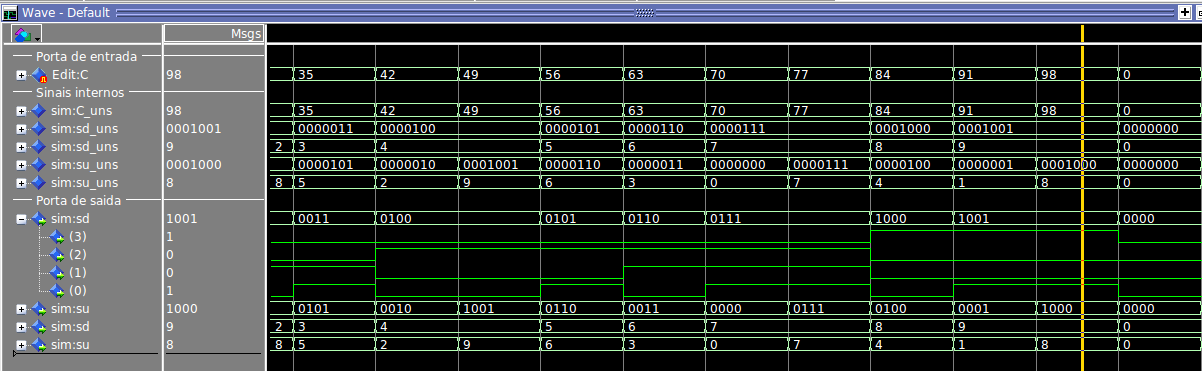

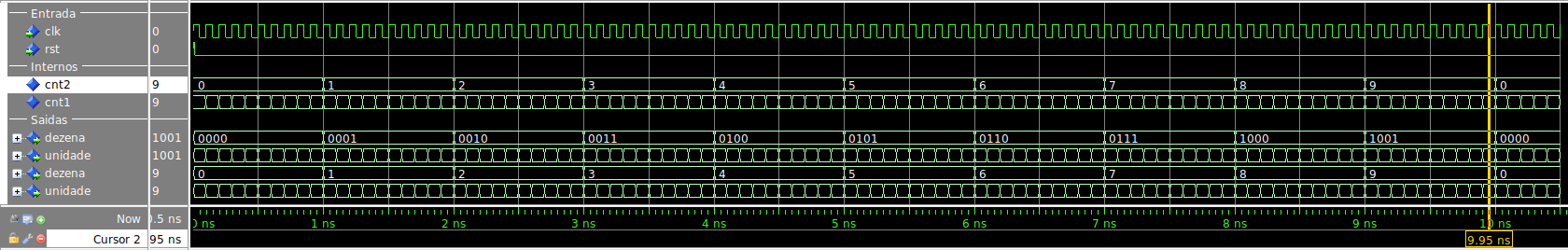

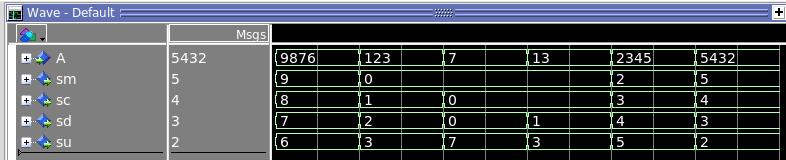

| + | {{fig|3.3| Simulação do conversor de Binário para BCD com 2 digitos | bin2bcdDU_modelsim.png | 1000 px |}} | ||

| + | |||

| + | |||

| + | ;Encontro 18 (19 set.) | ||

| + | ;Operadores lógicos: | ||

| + | São suportados nos tipos de dados: BIT, BIT_VECTOR, BOOLEAN, STD_(U)LOGIC, STD_(U)LOGIC_VECTOR, SIGNED e UNSIGNED. Com VHDL 2008 também suportado para BOOLEAN_VECTOR, UFIXED, SFIXED e FLOAT. | ||

| + | |||

| + | NOT | ||

| + | AND | ||

| + | NAND | ||

| + | OR | ||

| + | NOR | ||

| + | XOR | ||

| + | XNOR | ||

| + | |||

| + | Apenas o operador NOT tem precedência sobre os demais | ||

| + | y <= a AND b XOR c -- é equivalente a (a AND b) XOR c | ||

| + | y <= NOT a AND b -- é equivalente a (NOT a) AND b. | ||

| + | y <= a NAND b -- é equivalente a NOT (a AND b) | ||

| + | |||

| + | * Operadores de deslocamento (SHIFT) | ||

| + | :*SLL (''Shift Left Logic'') - Deslocamento a esquerda lógico (preenchimento com '0's das posições a direita. | ||

| + | :*SRL (''Shift Right Logic'') - Deslocamento a direita lógico (preenchimento com '0's das posições a esquerda. | ||

| + | :*SLA (''Shift Left Arithmetic'') - Deslocamento a esquerda aritmético (posições liberadas da direita mantém o bit lsb) | ||

| + | :*SRA (''Shift Right Arithmetic'') - Deslocamento a direita aritmético (posições liberadas da esquerda mantém o bit msb) | ||

| + | :*ROL (''Rotate Left'') - Deslocamento circular a esquerda ( o bit que sai na esquerda é retornado na direita) | ||

| + | :*ROR (''Rotate Right'') - Deslocamento circular a direita ( o bit que sai na direita é retornado na esquerda) | ||

| + | |||

| + | signal a: bit_vector(7 downto 0) := "01100101"; | ||

| + | y <= a SLL 2; -- y <= "100101'''00'''" (y <= a(5 downto 0) & "00";) | ||

| + | y <= a SLA 2; -- y <= "100101'''11'''" (y <= a(5 downto 0) & a(0) & a(0);) | ||

| + | y <= a ROL 2; -- y <= "100101'''01'''" (y <= a(5 downto 0) & a(7 downto 6);) | ||

| + | y <= a ROR 2; -- y <= "'''01'''011001" (y <= a(1 downto 0) & a(7 downto 2);) | ||

| + | |||

| + | ::Esses operadores são suportados nos tipos BIT_VECTOR, (UN)SIGNED. Em VHDL 2008 também para BOOLEAN_VECTOR, STD_(U)LOGIG_VECTOR, UFIXED e SFIXED. | ||

| + | |||

| + | * Operador de concatenação ('''&''') | ||

| + | ::Esse operador é suportado nos tipos BIT_VECTOR, STD_(U)LOGIG_VECTOR, STRING e (UN)SIGNED. Em VHDL 2008 também para INTEGER_VECTOR e BOOLEAN_VECTOR. | ||

| + | ::É utilizado para agrupar objetos como mostrado nos comentários dos exemplos anteriores | ||

| + | |||

| + | *Operadores de comparação | ||

| + | ::São suportados nos tipos de dados: BIT, BIT_VECTOR, BOOLEAN, INTEGER, NATURAL, POSITIVE, CHARACTER, STRING, SIGNED e UNSIGNED. Com VHDL 2008 também suportado para BOOLEAN_VECTOR, INTEGER_VECTOR, UFIXED, SFIXED e FLOAT. | ||

| + | Igualdade (=) | ||

| + | Diferença (/=) | ||

| + | Menor que (<) | ||

| + | Menor ou igual que (<=) | ||

| + | Maior que (>) | ||

| + | Maior ou igual que (>=) | ||

| + | |||

| + | *Operadores de comparação de associação (''matching comparison'') | ||

| + | ::Foram introduzidos no VHDL 2008, e tem o objetivo de tratar nos tipos baseados no STD_ULOGIC de forma igual os valores lógicos 'H'='1' e também 'L'='0', e 'X'='Z'='W'. São suportados nos tipos de dados: BIT, BIT_VECTOR, STD_(U)LOGIG, STD_(U)LOGIG_VECTOR, SIGNED e UNSIGNED. Com VHDL 2008 também suportado para UFIXED, SFIXED. | ||

| + | Igualdade (?=) | ||

| + | Diferença (?/=) | ||

| + | Menor que (?<) | ||

| + | Menor ou igual que (?<=) | ||

| + | Maior que (?>) | ||

| + | Maior ou igual que (?>=) | ||

| + | |||

| + | ;Atributos em VHDL: | ||

| + | * Atributos de síntese: | ||

| + | Em VHDL existem diversos atributos de sintese que controlam a forma como o processo de "Analysis & Synthesis" é realizado pelo Quartus II. Uma listagem completa pode ser encontrada em: | ||

| + | *[https://www.intel.com/content/www/us/en/programmable/quartushelp/current/index.htm#hdl/vhdl/vhdl_file_dir.htm VHDL Synthesis Attributes and Directives] - Quartus Prime Pro Edition Help version 18.1 | ||

| + | |||

| + | :* '''ATTRIBUTE enum_encoding''' [https://www.intel.com/content/www/us/en/programmable/quartushelp/current/index.htm#hdl/vhdl/vhdl_file_dir_enum_encoding.htm] | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | type fruit is (apple, orange, pear, mango); | ||

| + | attribute enum_encoding : string; | ||

| + | attribute enum_encoding of fruit : type is "11 01 10 00"; | ||

| + | </syntaxhighlight> | ||

| + | :* '''ATTRIBUTE chip_pin''' [https://www.intel.com/content/www/us/en/programmable/quartushelp/current/index.htm#hdl/vhdl/vhdl_file_dir_chip.htm] | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity foo is | ||

| + | port (sel : in std_logic; | ||

| + | data : in std_logic_vector(3 downto 0); | ||

| + | o : out std_logic); | ||

| + | end foo; | ||

| + | architecture rtl of foo is | ||

| + | |||

| + | attribute chip_pin : string; | ||

| + | attribute chip_pin of sel : signal is "C4"; | ||

| + | attribute chip_pin of data : signal is "D1, D2, D3, D4"; | ||

| + | begin | ||

| + | -- Specify additional code | ||

end architecture; | end architecture; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | <i> | |

| − | + | O uso desse atributo sobrepõe a atribuição dos pinos através da IDE do Quartus II, e por isso não é recomendável. | |

| − | + | ||

| − | + | O atributo de síntese chip_pin pode ser usado apenas em portas da entidade "top-level" do projeto. . | |

| − | + | </i> | |

| − | + | ||

| − | + | ;Encontro 20 (20 set.) | |

| − | + | :* '''ATTRIBUTE keep''' [https://www.intel.com/content/www/us/en/programmable/quartushelp/current/index.htm#hdl/vhdl/vhdl_file_dir_keep.htm] | |

| − | + | O atributo de síntese KEEP, sinaliza ao processo de "Analysis & Synthesis" para manter intacto um determinado signal ou componente. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | * | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | signal a,b,c : std_logic; | |

| − | + | attribute keep: boolean; | |

| + | attribute keep of a,b,c: signal is true; | ||

| + | </syntaxhighlight> | ||

| + | ::* Exemplo 4.4: Delay line (Síntese e Simulação temporal sem o com o atributo keep) | ||

| + | ::* Exemplo 5.8 Gerador de Pulsos estreitos | ||

| + | |||

| + | * '''ATTRIBUTE preserve''' [https://www.intel.com/content/www/us/en/programmable/quartushelp/current/index.htm#hdl/vhdl/vhdl_file_dir_preserve.htm], [https://www.intel.com/content/www/us/en/programmable/quartushelp/current/index.htm#logicops/logicops/def_preserve_fanout_free_node.htm]. | ||

| − | + | <syntaxhighlight lang=vhdl> | |

| − | + | signal a,b,c : std_logic; | |

| + | attribute preserve: boolean; | ||

| + | attribute preserve of a,b,c: signal is true; | ||

| + | </syntaxhighlight> | ||

| + | * '''ATTRIBUTE noprune'''[https://www.intel.com/content/www/us/en/programmable/quartushelp/current/index.htm#hdl/vhdl/vhdl_file_dir_noprune.htm]. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | signal reg1: std_logic; | ||

| + | attribute noprune: boolean; | ||

| + | attribute noprune of reg1: signal is true; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | |||

| − | |||

| − | + | {{collapse top| bg=lightyellow | Exemplo 4.5: Registros redundantes}} | |

| − | + | Síntese sem e com os atributos keep, preserve e noprune | |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | ENTITY redundant_registers IS | |

| − | + | PORT ( | |

| − | + | clk, x: IN BIT; | |

| − | + | y: OUT BIT); | |

| − | + | END ENTITY; | |

| + | |||

| + | ARCHITECTURE arch OF redundant_registers IS | ||

| + | SIGNAL a, b, c: BIT; | ||

| + | |||

| + | ATTRIBUTE keep: BOOLEAN; | ||

| + | ATTRIBUTE keep of a,b,c: SIGNAL IS FALSE; | ||

| + | |||

| + | ATTRIBUTE preserve: BOOLEAN; | ||

| + | ATTRIBUTE preserve OF a, b, c: SIGNAL IS FALSE; | ||

| + | |||

| + | ATTRIBUTE noprune: BOOLEAN; | ||

| + | ATTRIBUTE noprune OF a, b, c: SIGNAL IS FALSE; | ||

| + | |||

| − | + | BEGIN | |

| − | + | PROCESS (clk) | |

| − | + | BEGIN | |

| − | + | IF (clk'EVENT AND clk='1') THEN | |

| − | + | a <= x; | |

| − | + | b <= x; | |

| − | + | c <= x; | |

| − | + | END IF; | |

| − | + | END PROCESS; | |

| − | + | y <= a AND b; | |

| − | + | END ARCHITECTURE; | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

</syntaxhighlight> | </syntaxhighlight> | ||

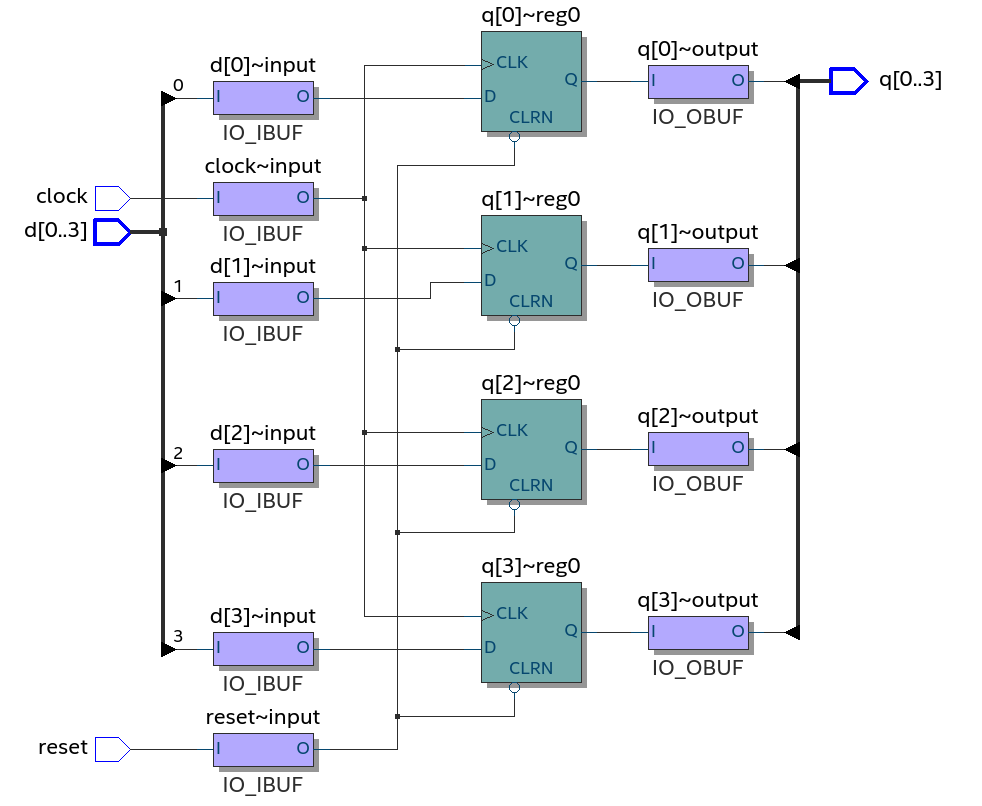

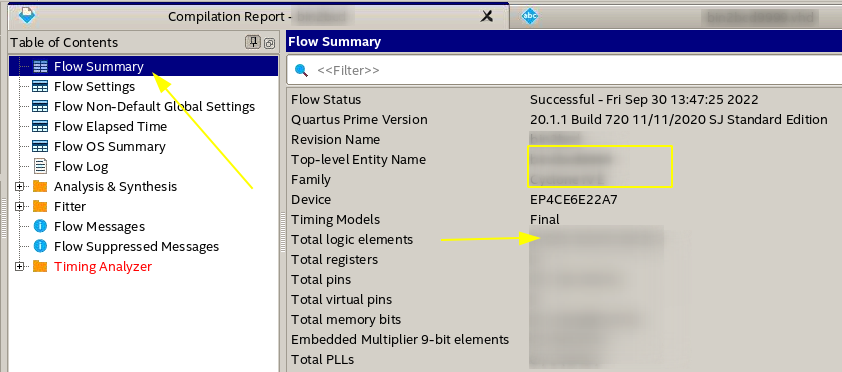

| − | + | Após a compilação do código acima, observe o número de elementos lógicos obtidos, observe o '''Technology Map''' dos circuitos gerados e verifique a localização dos FFs no '''Chip Planner'''. | |

| − | + | {{fig|3.4| Technology Map do circuito compilado sem Attribute | Ex4_5_NoAttribute.png | 400 px |}} | |

| + | |||

| + | {{fig|3.5| Technology Map do Circuito com Attribute Preserve (or Keep) | Ex4_5_PreserveAttribute.png | 400 px |}} | ||

| − | + | {{fig|3.6| Technology Map do Circuito com Attribute Noprune | Ex4_5_NopruneAttribute.png | 400 px |}} | |

| − | |||

| − | |||

| − | + | : Ver pag. 91 a 111 de <ref name="PEDRONI2010b"/> | |

| − | + | {{collapse bottom}} | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | * Atributos predefinidos são definidos no padrão [https://ieeexplore-ieee-org.ez130.periodicos.capes.gov.br/stamp/stamp.jsp?tp=&arnumber=8938196 1076-2019 - IEEE Standard for VHDL Language Reference Manual]. Esse documento pode ser acesso via o portal Periódicos Capes acesso CAFE. | |

| − | * | + | Para cada atributo existe uma descrição completa como mostrado a seguir. |

| − | + | P'LEFT Kind: Value. | |

| − | : | + | Prefix: Any prefix P that is appropriate for an object with a scalar type or subtype T, or an alias thereof, or that denotes any scalar type or subtype T. |

| − | : | + | Result type: Same type as T. |

| − | : | + | Result: The left bound of T. |

| − | : | + | A seguir estão listados alguns dos atributos mais utilizados. |

| − | |||

| − | |||

| − | + | :*16.2.2 Predefined attributes of types and objects (p.270) | |

| + | P'LEFT - The left bound of T. | ||

| + | P'RIGHT - The right bound of T. | ||

| + | P'HIGH - The upper bound of T. | ||

| + | P'LOW - The lower bound of T. | ||

| + | P'ASCENDING - It is TRUE if T is defined with an ascending range; FALSE otherwise. | ||

| + | P'LENGTH - maximum(0, T’POS(T’HIGH) – T’POS(T’LOW) + 1) | ||

| + | P'RANGE - The range T'LEFT to T'RIGHT if the range of T is ascending, or the range T'LEFT downto T'RIGHT if the range of T is descending | ||

| + | P'REVERSE_RANGE - The range T'RIGHT downto T'LEFT if the range of T is ascending, or the range T'RIGHT to T'LEFT if the range of T is descending | ||

| + | T'POS(X) - The position number of the value of the parameter | ||

| + | T'VAL(X) - The value whose position number is the universal_integer value corresponding to X. | ||

| − | + | :*16.2.3 Predefined attributes of arrays (p.275) | |

| − | + | A'LEFT [(N)] - Left bound of the Nth index range of A | |

| − | + | A'RIGHT [(N)] - Right bound of the Nth index range of A | |

| − | + | A'HIGH [(N)] - Upper bound of the Nth index range of A | |

| − | + | A'LOW [(N)] - Lower bound of the Nth index range of A. | |

| − | + | A'RANGE [(N)] - The range A'LEFT(N) to A'RIGHT(N) if the Nth index range of A is ascending, or the range A'LEFT(N) downto A'RIGHT(N) if the Nth index range of A is descending | |

| − | + | A'REVERSE_RANGE [(N)] - The range A'RIGHT(N) downto A'LEFT(N) if the Nth index range of A is ascending, or the range A'RIGHT(N) to A'LEFT(N) if the Nth index range of A is descending. | |

| − | + | A'LENGTH [(N)] - Number of values in the Nth index range | |

| − | + | A'ASCENDING [(N)] - TRUE if the Nth index range of A is defined with an ascending range; FALSE otherwise. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | :*16.2.4 Predefined attributes of signals (p. 277) | |

| − | + | S'EVENT - A value that indicates whether an event has just occurred on signal S. | |

| − | + | S'LAST_VALUE - For a signal S, if an event has occurred on S in any simulation cycle, S'LAST_VALUE returns the value of S prior to the update of S in the last simulation cycle in which an event occurred; otherwise, S'LAST_VALUE returns the current value of S. | |

| − | + | ||

| − | + | :*16.2.5 Predefined attributes of named entities (p. 279) | |

| − | + | E'SIMPLE_NAME - The simple name, character literal, or operator symbol of the named entity | |

| − | |||

| − | |||

| − | + | ;Encontro 21 (22 set.) | |

| − | + | * Atributos definidos pelo usuário; | |

| − | ; | + | <syntaxhighlight lang=vhdl> |

| − | + | attribute attribute_name: attribute_type; | |

| + | attribute attribute_name of entity_tag [signature]: entity_class is value; | ||

| + | </syntaxhighlight> | ||

| − | * | + | * Tipos definidos pelo usuário: |

| − | + | :* Escalares (Inteiros e Enumerados) | |

| − | + | :* Tipos de Array 1D x 1D, 2D , 1D x 1D x 1D, 3D. Ver : [[Array em VHDL]] | |

| − | |||

| − | * | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | * | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | {{collapse top| bg=lightyellow | Exemplo 3.5: Array de Integers 1D x 1D}} | |

| − | {{collapse top | bg=lightyellow | | + | O código abaixo cria um '''array''' de inteiros e utiliza as entradas "row" para fazer a leitura dos dados em uma tabela declarada como '''constant'''. |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

entity array_1Dx1D_integer is | entity array_1Dx1D_integer is | ||

| Linha 1 159: | Linha 1 234: | ||

end architecture; | end architecture; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| + | Responda as seguintes perguntas: | ||

| + | :1) Faça um desenho que represente o ARRAY declarado acima. | ||

| + | :2) Quantos bits são necessários para representar esse ARRAY? | ||

| + | :3) Qual o valor na saída quando a entrada row = 2? | ||

| + | :4) Quantos elementos lógicos são necessários para fazer a síntese deste circuito? | ||

| − | : | + | {{collapse bottom}} |

| − | + | ||

| − | + | {{collapse top| bg=lightyellow | Exemplo 3.6: Array de bits 1D x 1D }} | |

| − | + | O código abaixo cria um '''array''' de bits e utiliza as entradas "row" e "column" para fazer a leitura dos dados em uma tabela declarada como '''constant'''. | |

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 1 186: | Linha 1 265: | ||

('0', '1', '1', '1')); -- 7 | ('0', '1', '1', '1')); -- 7 | ||

begin | begin | ||

| − | + | -- slice1 <= table(row)(column); | |

| − | + | -- slice2 <= table(row)(1 to 2); | |

| − | + | -- slice3 <= table(row)); | |

| − | + | -- slice4 <= table(1 TO 3)(column); | |

| − | + | -- slice4 <= table(1)(column) & table(2)(column) & table(3)(column); | |

| − | + | -- gen : for i in 1 to 3 generate | |

| − | + | -- slice4(i) <= table(i)(column); | |

| − | + | -- end generate; | |

end architecture; | end architecture; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | : | + | Responda as seguintes perguntas: |

| − | : | + | :1) Faça um desenho que represente o ARRAY declarado acima. |

| − | : | + | :2) Quantos bits são necessários para representar esse ARRAY? |

| − | : | + | :3) Descomente uma a uma as linhas na architecture. Verifique quais são aceitas pelo compilador? As 3 últimas formam um bloco único |

| + | |||

| + | {{collapse bottom}} | ||

| + | |||

| + | |||

| + | ;Encontro 22 (29 set.) | ||

| + | {{collapse top| bg=lightyellow | Exemplo 3.7: Array de bits 2D }} | ||

| + | O código abaixo cria um '''array''' de bits e utiliza as entradas "row" e "column" para fazer a leitura dos dados em uma tabela declarada como '''constant'''. | ||

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

entity array_2D_bits is | entity array_2D_bits is | ||

| Linha 1 217: | Linha 1 302: | ||

architecture teste of array_2D_bits is | architecture teste of array_2D_bits is | ||

type a2D_bits is array (1 to 3, 1 to 4) of bit; | type a2D_bits is array (1 to 3, 1 to 4) of bit; | ||

| − | constant table : a2D_bits := ((' | + | constant table : a2D_bits := (('1', '1', '1', '1'), |

| − | (' | + | ('0', '1', '0', '1'), ('0', '1', '1', '1') |

); | ); | ||

begin | begin | ||

--slice1 <= table(row, column); | --slice1 <= table(row, column); | ||

--slice2 <= table(row, 1 TO 2); | --slice2 <= table(row, 1 TO 2); | ||

| − | --slice3 <= table(row | + | --slice3 <= table(row); |

--slice4 <= table(1 TO 3, column); | --slice4 <= table(1 TO 3, column); | ||

| − | --slice4 <= table(1, column) & table(2, column) & | + | --slice4 <= table(1, column) & table(2, column) & table(3, column) |

--gen : for i in 1 to 3 generate | --gen : for i in 1 to 3 generate | ||

-- slice4(i) <= table(i, column); | -- slice4(i) <= table(i, column); | ||

| Linha 1 231: | Linha 1 316: | ||

end architecture; | end architecture; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| + | Responda as seguintes perguntas: | ||

| + | :1) Faça um desenho que represente o ARRAY declarado acima. | ||

| + | :2) Quantos bits são necessários para representar esse ARRAY? | ||

| + | :3) Descomente uma a uma as linhas na architecture. Verifique quais são aceitas pelo compilador? As 3 últimas formam um bloco único | ||

| + | |||

| + | No exemplo acima, note que os limites da instrução '''for generate''' podem ser definidos usando os atributos do array. Assim a linha poderia ser descrita também usando os atributos do objeto ou do tipo: | ||

| + | gen : for i in 1 to 3 generate | ||

| + | Usando os atributos '''left''' e '''right''' da primeira dimensão do array (1 to 3) do objeto ('''table''') ou tipo ('''a2D_bits''') | ||

| + | gen : for i in table'left(1) to table'right(1) generate | ||

| + | gen : for i in a2D_bits'left(1) to a2D_bits'right(1) generate | ||

| + | Usando os atributos '''low''' e '''high''' | ||

| + | gen : for i in table'low(1) to table'high(1) generate | ||

| + | gen : for i in a2D_bits'low(1) to a2D_bits'high(1) generate | ||

| + | Usando os atributos '''range''' ou '''reverse_range''' | ||

| + | gen : for i in table'reverse_range(1) generate | ||

| + | gen : for i in table'range(1) generate | ||

| + | gen : for i in a2D_bits'reverse_range(1) generate | ||

| + | gen : for i in a2D_bits'range(1) generate | ||

| + | Usando o atributo '''length''' | ||

| + | gen : for i in 1 to table'length(1) generate | ||

| + | gen : for i in 1 to a2D_bits'length(1) generate | ||

| + | |||

| + | {{collapse bottom}} | ||

| + | ;Notas importantes: | ||

| + | |||

| + | A retirada de fatias (SLICES) dos ARRAYs só pode ser feita se o array foi definido com um vetor de vetores (1Dx1D ou 1Dx1Dx1D). Ainda assim é necessário respeitar a ordem dos índices do VETOR. No caso abaixo é ascendente (TO), e dentro dos limites (1 to 4). | ||

| + | |||

| + | type a1Dx1D_bit is array (1 to 3) of BIT_VECTOR(1 to 4); | ||

| + | |||

| + | * A retirada de fatias (SLICES) dos ARRAYs por coluna ou em ARRAY 2D ou 3D pode ser feita usando a retirada de elemento a elemento e concatenando-os ou atribuindo-os diretamente ao vetor de saída. | ||

| − | + | type a2D_bits is array (1 to 3, 1 to 4) of bit; | |

| − | + | type a3D_bits is array (1 to 3, 1 to 4, 1 to 2) of bit; | |

| − | |||

| − | |||

| − | + | :Concatenando por linha (ROW) ou coluna (COLUMN). | |

| − | + | <syntaxhighlight lang=vhdl> | |

| − | + | slice3 <= table(row, 1) & table(row, 2) & & table(row, 3) & & table(row, 4); | |

| + | slice4 <= table(1, column) & table(2, column) & table(3, column); | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :Amostrando elemento a elemento por linha (ROW) ou coluna (COLUMN | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | |||

gen1 : for j in 1 to 4 generate | gen1 : for j in 1 to 4 generate | ||

slice3(j) <= table(row, j); | slice3(j) <= table(row, j); | ||

end generate; | end generate; | ||

| − | |||

gen2 : for i in 1 to 3 generate | gen2 : for i in 1 to 3 generate | ||

slice4(i) <= table(i, column); | slice4(i) <= table(i, column); | ||

| Linha 1 251: | Linha 1 366: | ||

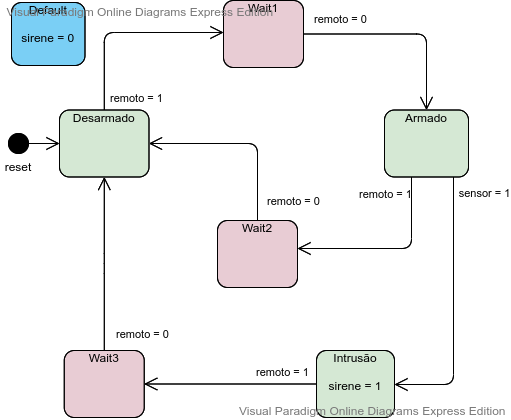

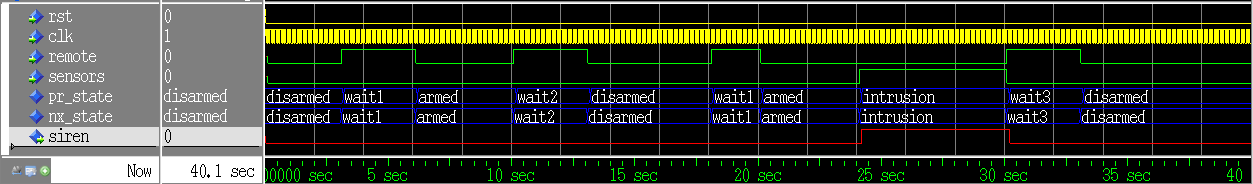

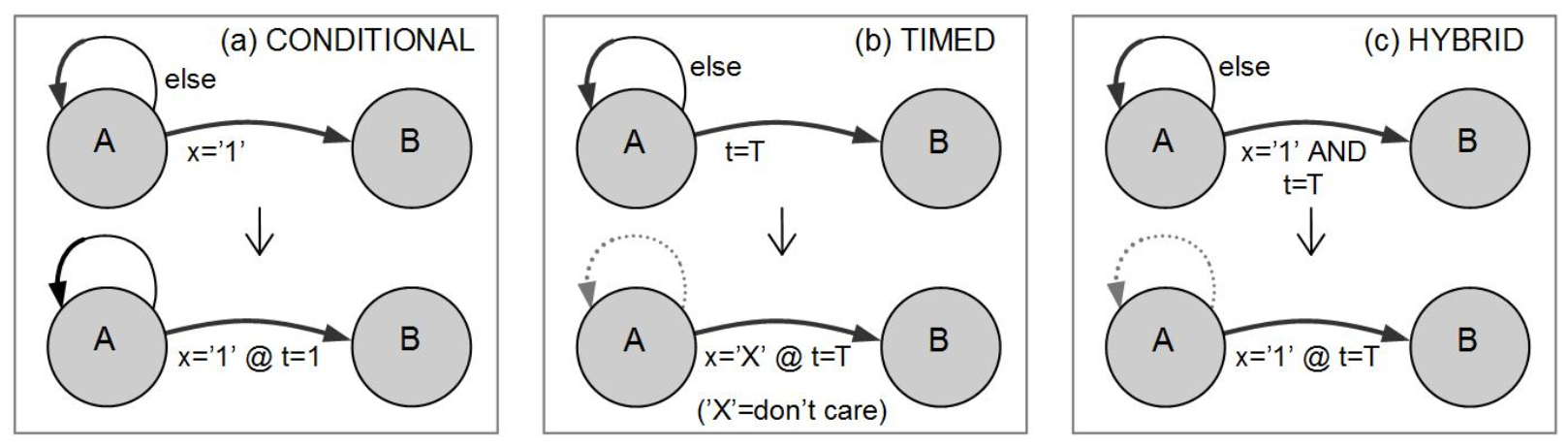

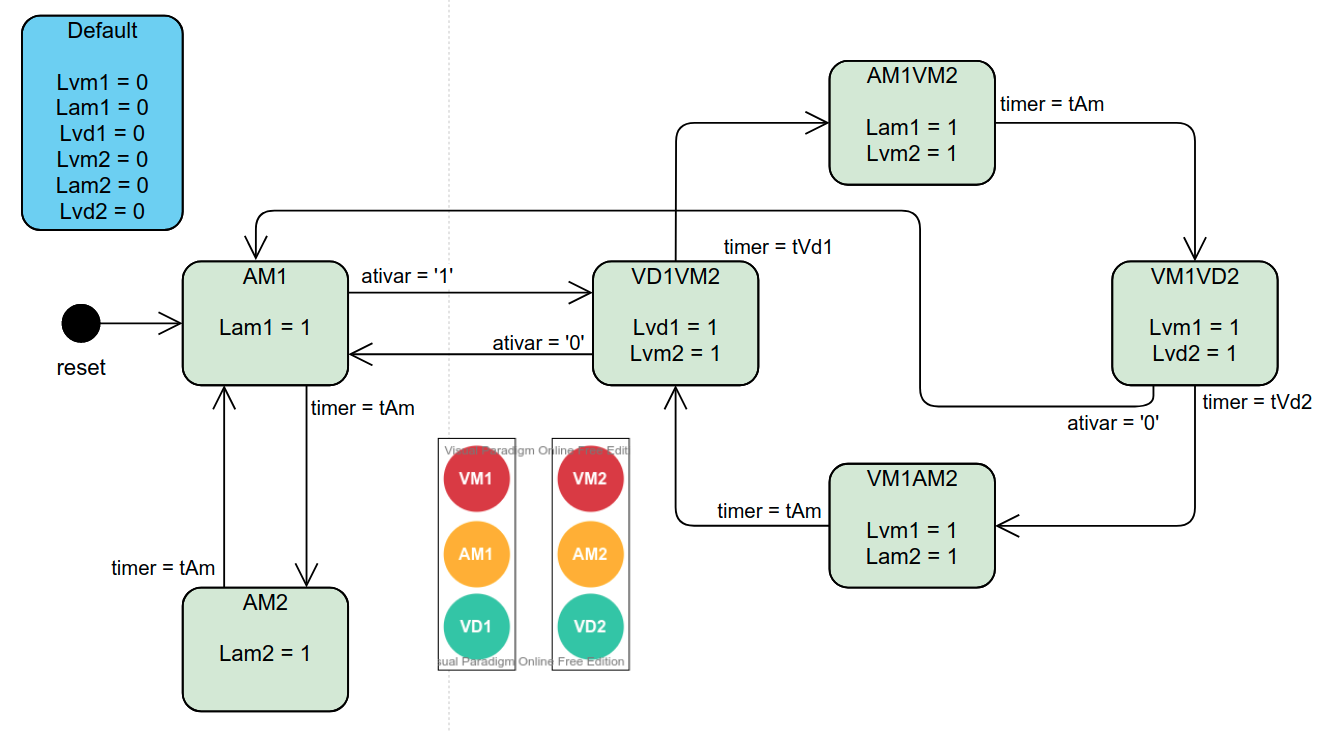

</syntaxhighlight> | </syntaxhighlight> | ||