Medição de tempos de propagação em circuitos combinacionais - Quartus Prime

Este procedimento está descrito para o Quartus Prime. Se você está usando o Quartus II, siga o procedimento descrito em Medição de tempos de propagação em circuitos combinacionais - Quartus II.

1 Circuito exemplo: Cálculo da distância de Hamming

O circuito abaixo realiza o cálculo da distância de Hamming entre dois sinais. O hardware está descrito em VHDL de forma genérica para permitir o estudo dos diferentes tempo de propagação e área do chip ocupado pelo circuito conforme as restrições de tempo impostas. Os valores de N e M definem respectivamente o tamanho dos vetor de entrada a e b e do vetor de saída y. A distância de Hamming é fornecida através de um número binário sem sinal. Note que M = ceil(log2(N)), ou seja para N = 8 bits => M = 4 bits, pois o número 8 é representado como "1000".

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity hamming_distance is

generic (

N: natural := 25;

M: natural := 5); -- M = ceil(log2(N))

port(

a, b : in std_logic_vector (N-1 downto 0);

y : out std_logic_vector (M-1 downto 0));

end entity;

architecture ifsc_arch_gen of hamming_distance is

signal diff: unsigned (N-1 downto 0);

signal sum: unsigned (M-1 downto 0);

begin

diff <= unsigned(a xor b);

process (diff)

variable tmp : integer range 0 to N;

begin

tmp := 0;

for i in diff'range loop

tmp := tmp + to_integer(unsigned'('0' & diff(i)));

end loop;

sum <= to_unsigned(tmp,M);

end process;

y <= std_logic_vector(sum);

end architecture;

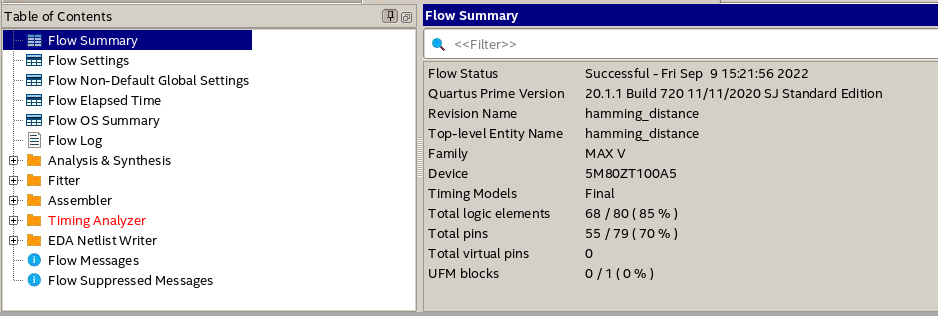

Na sequência abaixo, foi utilizado o Quartus Prime 20.1.1 Build 720 11/11/2020 SJ Standard Edition, compilando o circuito para a família MAX V de CPLDs da INTEL, dispositivo 5M80ZT100A5. Em função de termos uma menor quantidade de elementos lógicos (80), os resultados mostrados abaixo são melhor visualizados neste dispositivo do que em dispositivos maiores, mas sinta-se livre para escolher dispositivos com mais elementos lógicos. Note que eventualmente ao utilizar vetores de entrada maiores, o compilador pode acusar falta de pinos para mapear todas as portas do circuito. Neste caso utilize dispositivos com maior número de de pinos.

Para realizar a verificações abaixo descritas, inicialmente crie um projeto com o código VHDL do circuito hamming_distance e realize a compilação (Processing > Start Compilation).

2 Área ocupada no DLP pelo circuito

Verifique o número de Elementos lógicos utilizados pelo circuito. No caso mostrado abaixo estão sendo utilizados 68 elementos lógicos entre os 80 disponíveis. Note que o dispositivo tem ao todo 100 pinos, sendo utilizados 55 dos 79 que estão disponíveis como pinos de I/O.

Figura 1 - Relatório de compilação do projeto

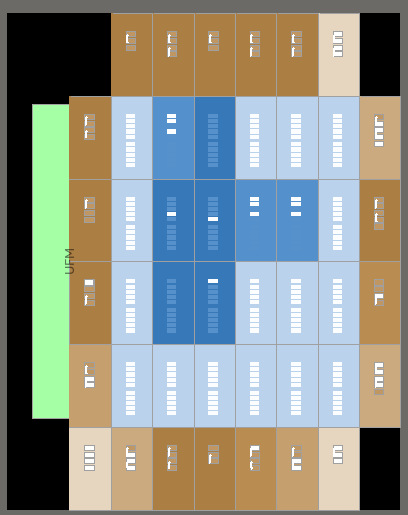

Observe a disposição desses elementos no Chip Planner (Tools > Chip Planner). Note que como nenhuma restrição de tempo foi inserida, os elementos lógicos utilizados estão espalhado no dispositivo. Note que a intensidade da cor azul indica a taxa de ocupação.

Figura 2 - Disposição dos elementos lógicos utilizados

3 Tempo de Propagação entre entrada e saída

Para determinar os tempos de propagação entre cada pino de entrada e os pinos de saída a versão Quartus II apresentada o relatório de Propagation Delay, diretamente no Compilation Report. Na versão Quartus Prime é necessário utilizar o aplicativo Timing Analyser para obter esse report.

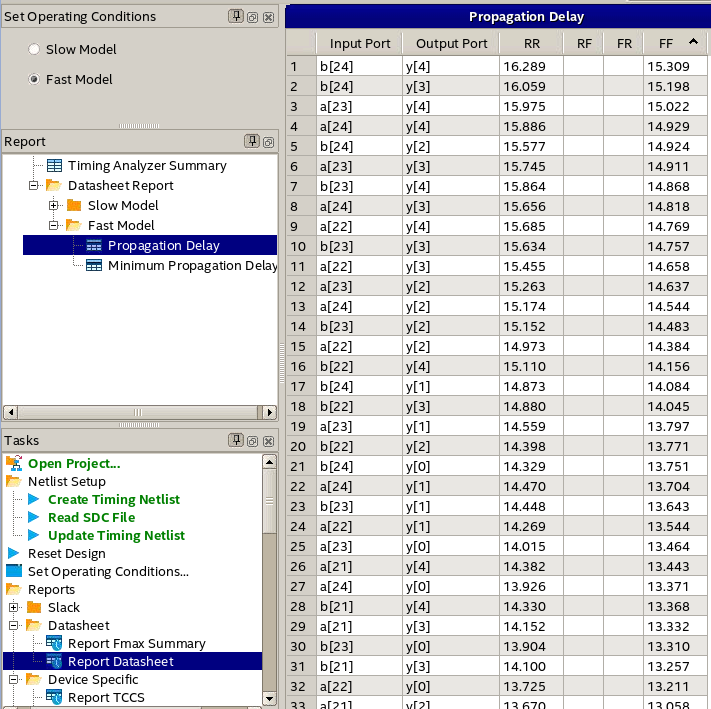

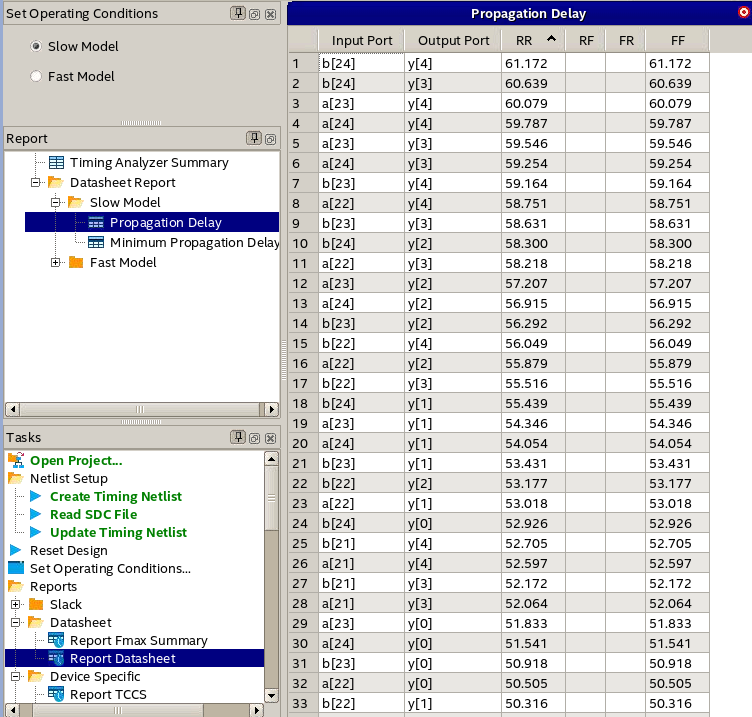

Abra o Timing Analyser (Tools > Timing Analyzer), em seguida na janela Task clique em [Reports > Datasheet Report] O relatório de atraso de propagação (Propagation Delay) será mostrado.

Para encontrar o caminho crítico ("Critical Path") do circuito ordene os tempos de propagação do maior para menor. No exemplo da figura abaixo o caminho crítico é entre a entrada b[24] e saída y[4], com tempo de propagação de 16.289 ns, no Fast Model e 61.172 ns no Slow Model. Os modelos citados correspondem a uma análise para as piores e melhores condições de PVT (processo, voltagem, e temperatura) para o funcionamento do dispositivo. Para saber mais a respeito leia Modelos de Temporização nos FPGAs.

Figura 3 - Tempos de Propagação Fast Model

Figura 4 - Tempos de Propagação Slow Model

4 Visualização dos tempos de propagação no Chip Planner

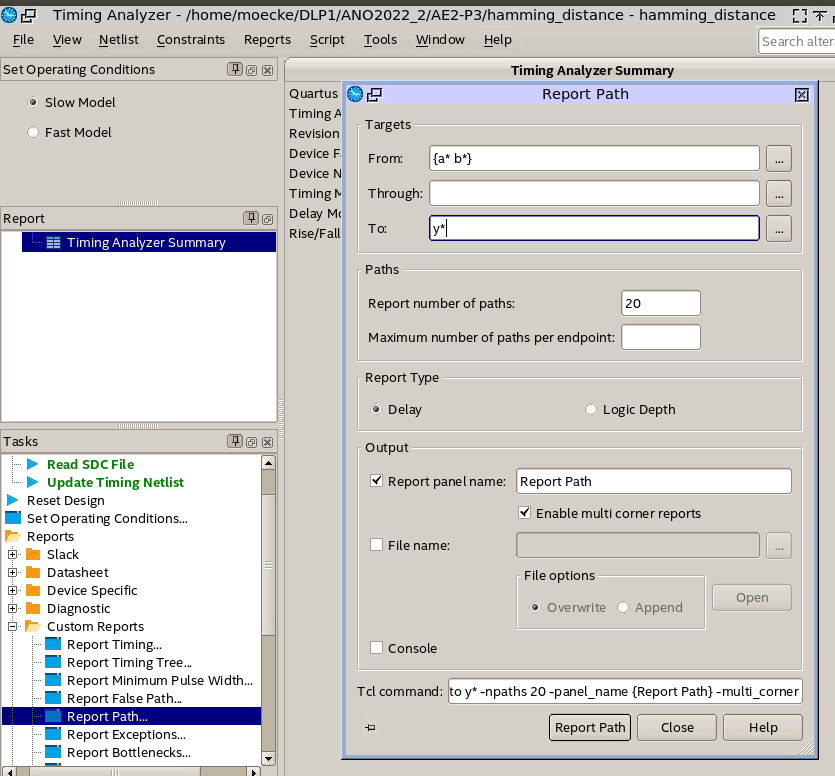

Uma das formas de visualizar os tempos de propagação no Chip Planner é utilizando a ferramenta Timing Analyser. Abra o Timing Analyser (Tools > Timing Analyzer), em seguida na janela Task clique em [Reports > Custom Reports > Report Path...], e defina as portas de entrada (Targets > From: {a* b*}), as portas de saída (Targets > To: y*), e o número de caminhos a serem relatados (Report number of paths: 20). e clique em [Report Path]..

Figura 5 - Configuração do Report Path

Se no lugar da interface gráfica quiser usar um comando tcl, digite o comando abaixo no Console:

report_path -from {a* b*} -to y* -npaths 20 -panel_name {Report Path} -multi_corner

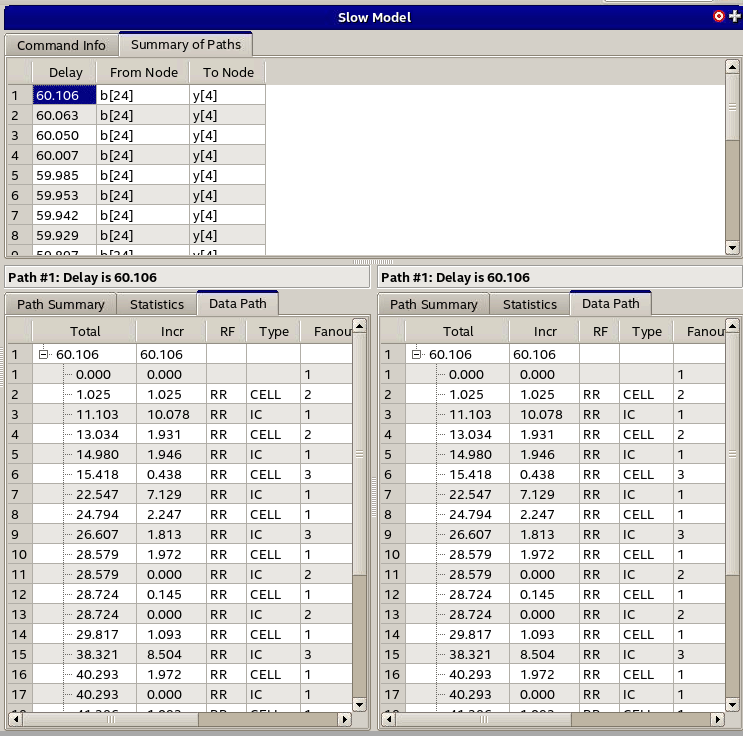

Figura 6 - Resultados do Report Path

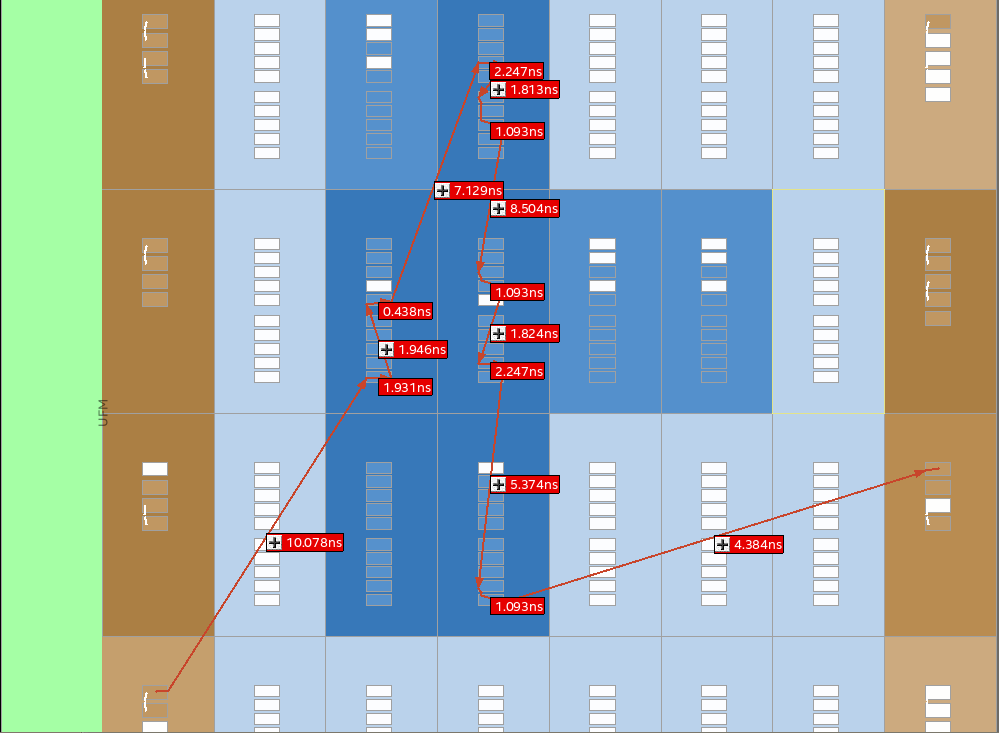

Na tela do Report Path, selecione os tempos que deseja visualizar (use o botão esquerdo do mouse junto com a tecla [Shift]), e em seguida use o botão direito do mouse e selecione (Locate Path... > Locate in [x] Chip Planner). Na Janela Locate History, selecione um dos caminhos, e expanda os caminhos parciais [+] e selecione (View > Show Delays) para visualizar os tempos de propagação parcial no Chip Planner. No caso mostrado o tempo total de propagação entre a porta b[24] e y[4] é de 60,106 ns. Note que os maiores tempos de propagação parcial ocorrem entre os pinos do DLP e o primeiro e último elemento lógico, tanto na entrada (1,025 + 10,078 ns) como na saída (4,384 + 2,082 ns).

Figura 7 - Resultado do

ATENÇÃO!! Eventualmente se forem selecionados muitos tempos de propagação, pode ocorrer algum erro interno no Quartus. Por isso recomendamos observar um caminho por vez.

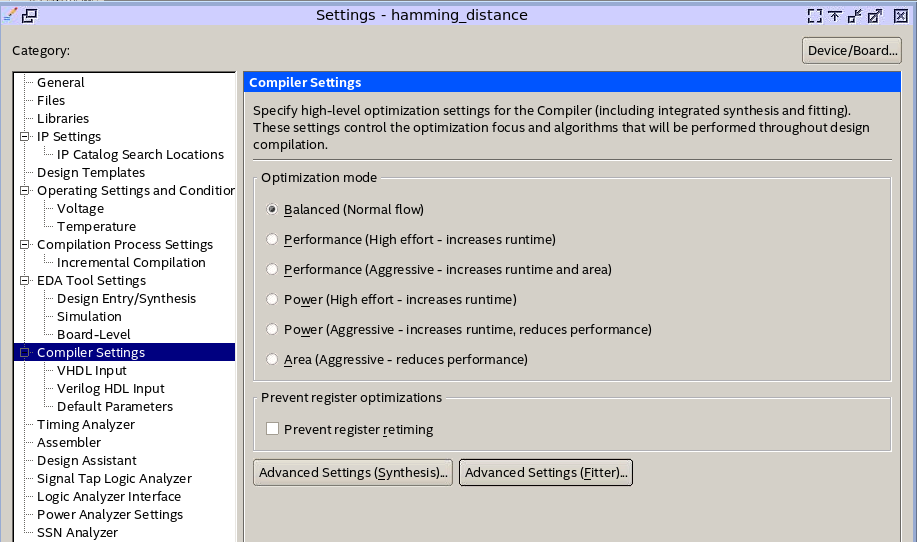

5 Configurando o compilador

O compilador do Quartus II possui diversas configurações que podem ser controladas pelo usuário para melhorar o desempenho, reduzir a área, reduzir a potência.

Figura 8 - Opções de compilação

Realize diferentes compilações após alterar o modo de otimização. Em [Assignments > Setting] selecione a [Category: Compiler Settings] e em Optimization Technique:

- por default está selecionado [x] Balanced (Normal flow) .

- selecione uma das opções de [x] Performance para "procurar" reduzir o tempo de propagação e/ou aumentar a frequência máxima do sistema.

- selecione uma das opções de [x] Power para "procurar" reduzir a potência utilizados no sistema.

- selecione [x] Area para "procurar" reduzir o número de elementos lógicos utilizados no sistema.

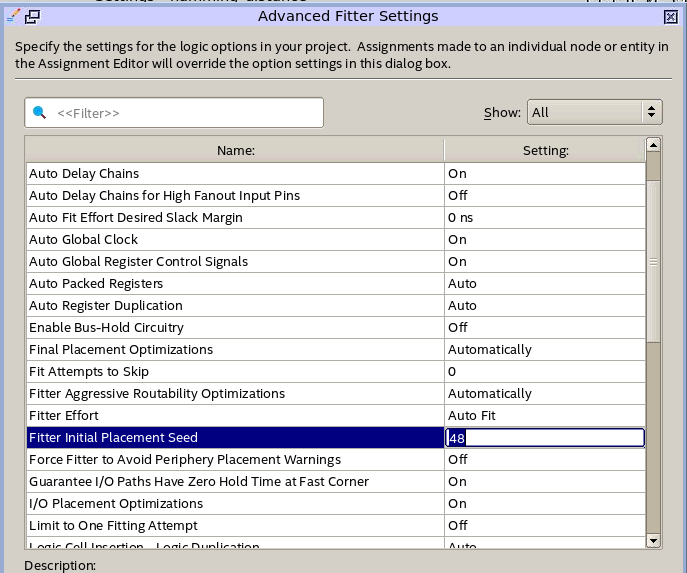

Existem outras opções disponíveis [Advanced Settings (Synthesis)] [Advanced Settings (Fitter)], mas não recomendamos alterar essas opções, exceto a Fitter Initial Placement Seed. [1]

Experimente outras sementes iniciais (valores inteiros positivos {1 4 8 89 ...), que são utilizados para determinar um ponto inicial diferente para o projeto. Mudar esse valor pode produzir um circuito melhor ou não. Normalmente esse recurso permite obter pequenas variações.

Figura 9 - Semente inicial do Fitter

A ferramenta Design Space Explorer II permite variar as configurações das sementes e também técnicas de otimização, de forma semi-automática.

6 Inserindo restrições de atraso máximo para o compilador

Para restringir o tempo de propagação entre entrada(s) e saída(s), é necessário acrescentar ao projeto um arquivo .sdc [File > New > Synopsys Design Constraints File] (Synopsys Design Constraints File). No exemplo abaixo é inserida um restrição de máximo atraso (set_max_delay) entre todas as portas de entradas para todas as portas de saída de 50 ns. Para inserir esta restrição salve um arquivo sdc1.sdc com o seguinte conteúdo:

set_max_delay -from [get_ports *] -to [get_ports *] 50

Recompile o projeto e refaça as analises indicadas acima. Note que a alocação dos elementos lógicos no PFGA irá mudar para atender a esta restrição de tempo.

No exemplo utilizado, com uma semente inicial = 48, foi possível reduzir o tempo de propagação para 46.866 ns

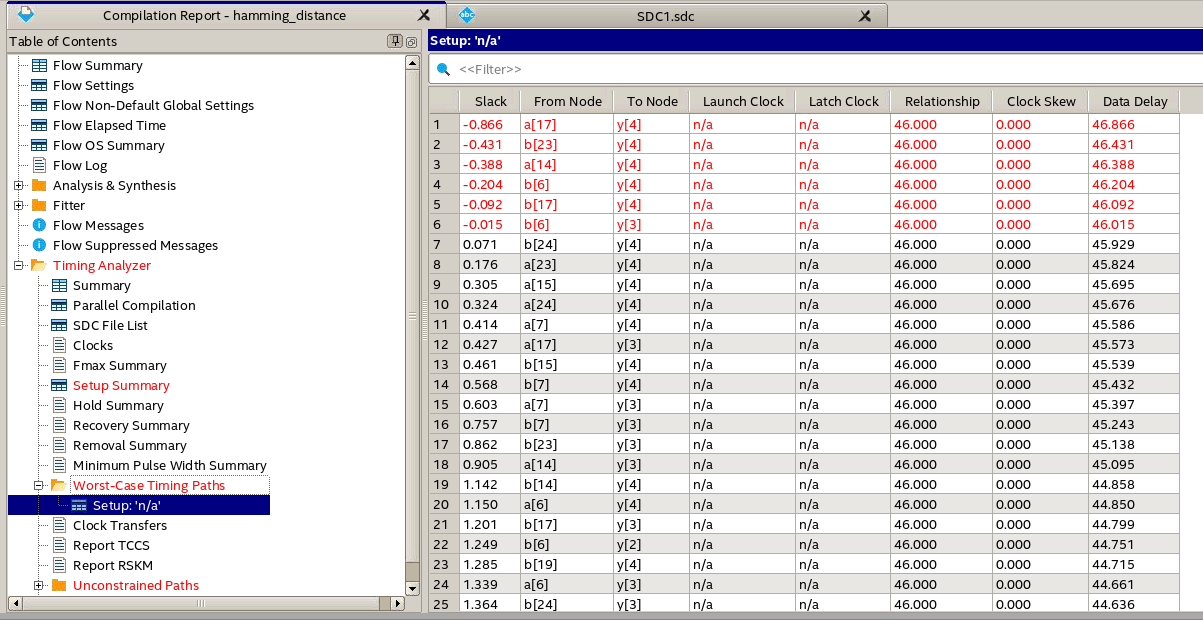

7 Restrições de tempo não atendidas

Experimente com outras restrições de tempo, e verifique se o compilador consegue um circuito que atenda as restrições. No exemplo, usando um restrição de 46 ns, o compilador não conseguiu obter exito.

set_max_delay -from [get_ports *] -to [get_ports *] 46

Inicialmente note que ocorre uma mensagem de Critical Warning na janela Messages

Critical Warning (332148): Timing requirements not met

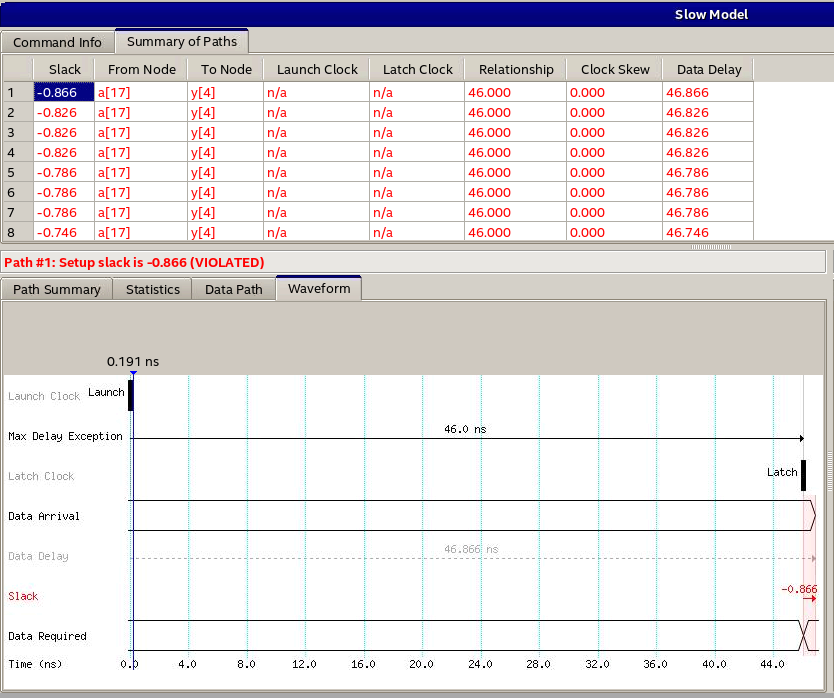

Ao analisar o Compilation Report em [Compilation Report > Timing Analyser > Worst-Case Timing Paths] note que alguns valores estão em vermelho, mostrando um Slack negativo. Indicando que o Data Delay superou o atraso máximo especificado de 46 ns.

Figura 9 - Timing Report - Negative Slack

Uma análise adicional pode ser feita utilizando a ferramenta Timing Analyser (Tools > Timing Analyser). Na janela Tasks, selecione o Report Timing (Reports > Custom Reports > Report Timing...), e defina as portas de entrada (Targets > From: {a* b*}), as portas de saída (Targets > To: y*), e o número de caminhos a serem relatados (Report number of path: 100). e clique em [Report Timing].

Se no lugar da interface gráfica quiser usar um comando tcl, digite o comando abaixo no Console:

report_timing -from {a* b*} -to y* -setup -npaths 100 -detail full_path -panel_name {Report Timing}

Figura 10 - Detalhes do timing Report - Negative Slack

Note que a aba Waveform mostra graficamente o significado dos valores dos tempos de propagação.

- Max Delay Exception: Valor especificado no arquivo .sdc

- Data Arrival: O tempo de propagação calculado

- Slack: Valor negativo mostrando que a restrição não foi atendida

- Data Required: Corresponde ao tempo em que o dado deveria estar disponível.

No exemplo mostrado temos que o dado deveria estar disponível em 46.000 ns, mas apenas chega em 46.866 ns, o que dá um slack de 0.866 ns.

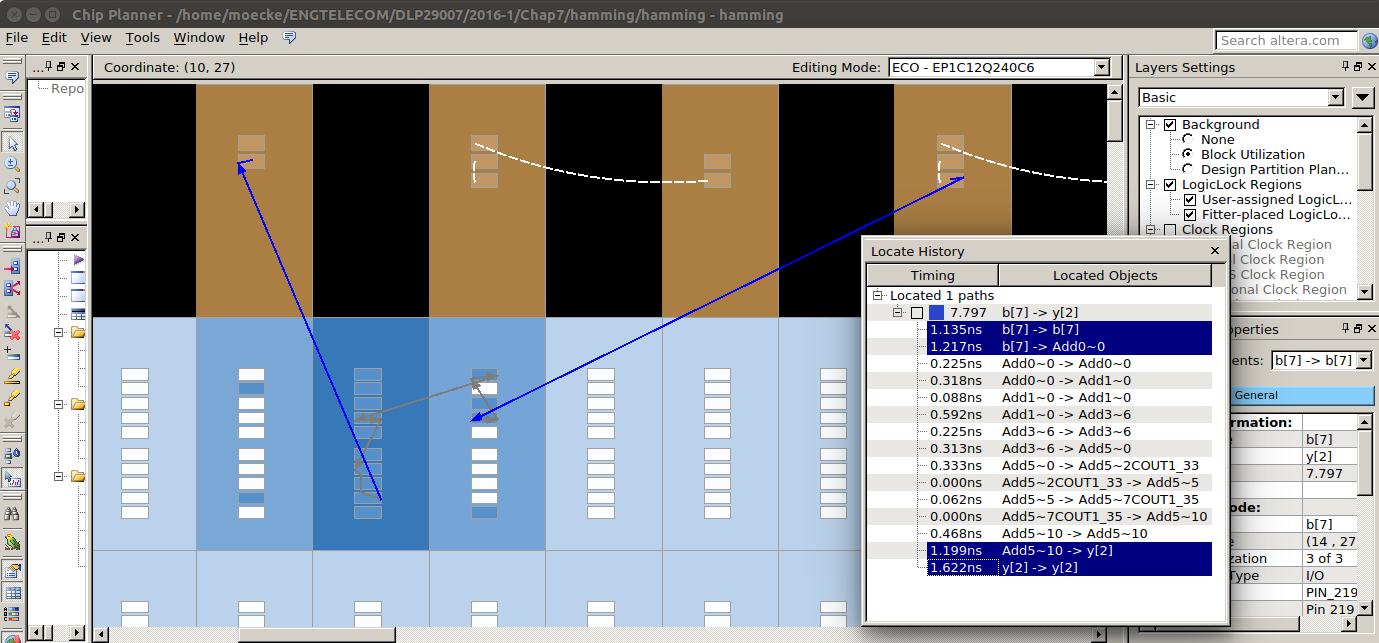

8 Detalhamento dos tempos de propagação no Chip

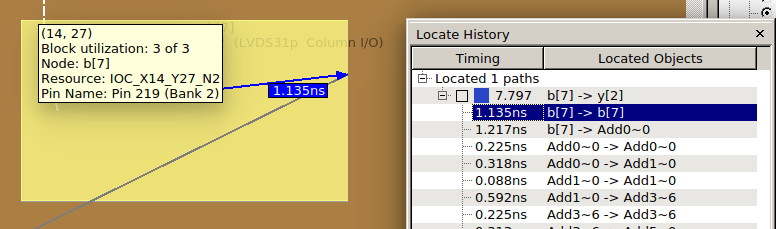

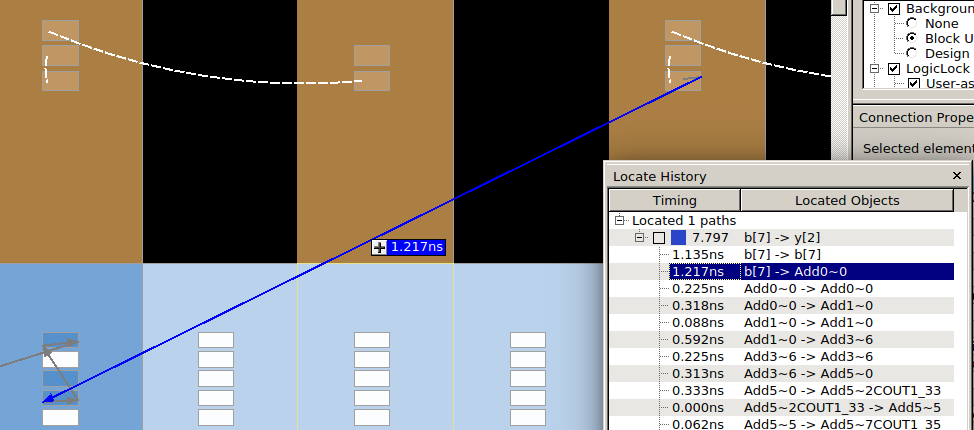

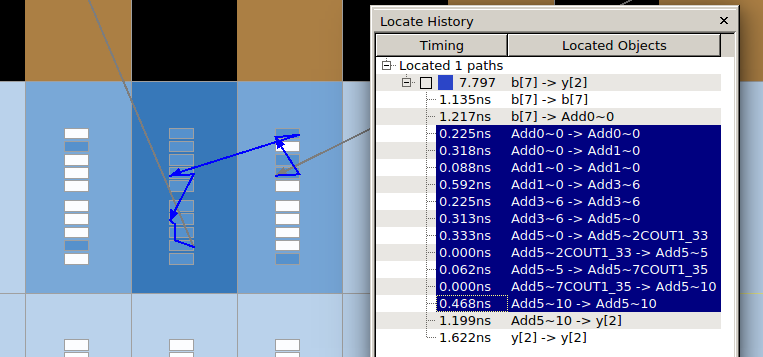

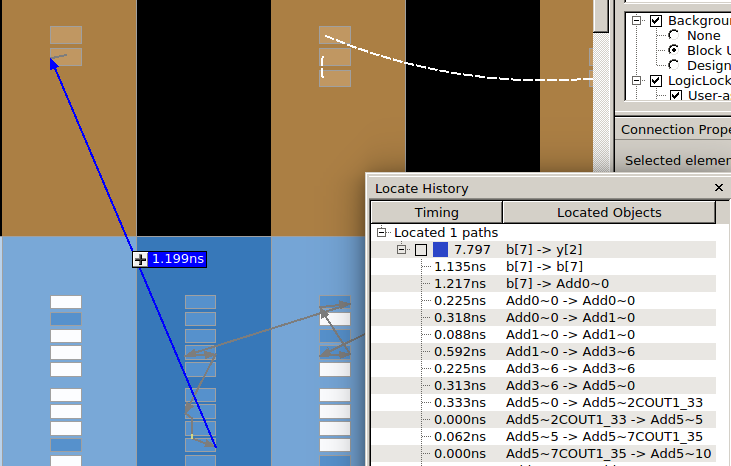

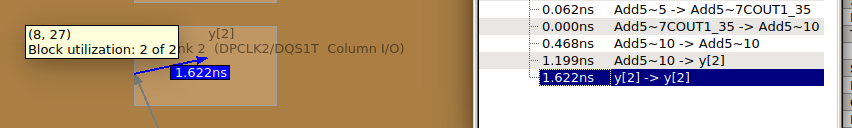

A figura abaixo mostra alguns tempos de propagação do circuito "hamming_distance" com N = 8 e M = 4, e max_delay = 9 ns. Os valores selecionados na imagem maior correspondem aos tempos de propagação nos pinos de I/O e tempo de chegada ao primeiro LE e saída do ultimo LE. Os valores não selecionados são os correspondentes aos tempos de propagação do primeiro elemento lógico até o último elemento lógico, e correspondem em parte a propagação nas trilhas e em parte a propagação dentro dos elementos lógicos.

Na sequencia são mostradas várias figuras que detalham os valores e as áreas correspondentes no chip.

Neste exemplo o tempo de propagação dentro do pino de entrada é de 1,135 ns.

Neste exemplo o tempo de propagação do pino de entrada até o primeiro elemento lógico é de 1,217 ns.

Neste exemplo o tempo de propagação do primeiro elemento lógico até o último elemento lógico é de 2,624 ns.

Neste exemplo o tempo de propagação do último elemento lógico até o pino de saída é de 1,199 ns.

Neste exemplo o tempo de propagação dentro do pino de saída é de 1,622 ns.

9 Referencias externas

- Timing Analysis Overview, Quartus II 13.1 - ALTERA/INTEL

- The Quartus II TimeQuest Timing Analyzer, Quartus II 13.1 - ALTERA/INTEL

- Arquivo:Wp-01139-timing-model.pdf