Especificando o valor de Power-Up do flip-flop D

Ir para navegação

Ir para pesquisar

Ao usar registradores (flip_flops), você pode definir o valor que cada flip_flop assume ao ser energizado, definindo o valor inicial no momento da declaração do sinal:

signal <nome_saida_FF> : std_logic := '1';

ou da porta da entidade

port ( ... <nome_saida_FF> : out std_logic := '1');

Se nada for declarado (por default) o flip_flop irá assumir o valor 0 no power-up.

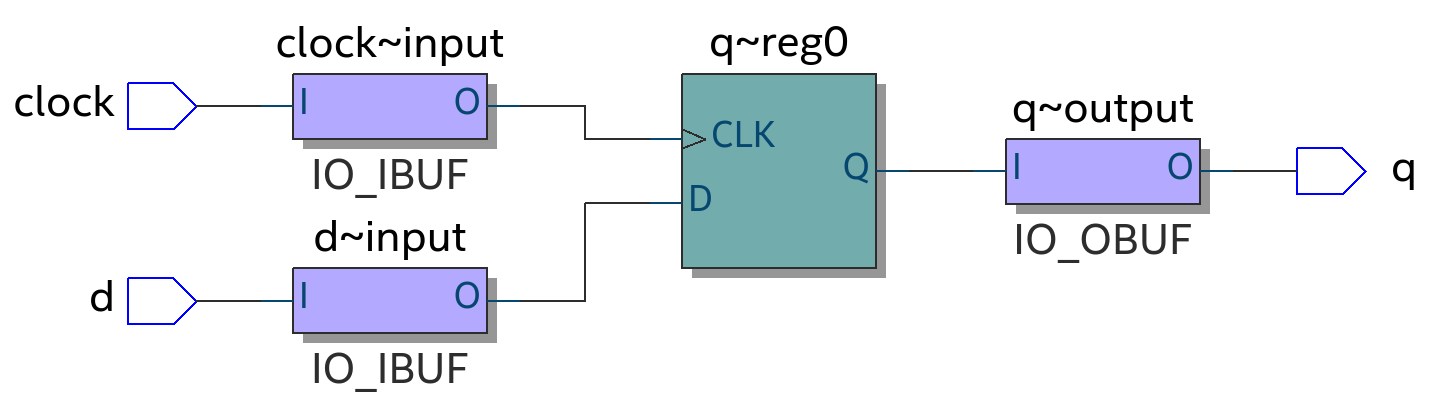

Figura 1 - Technology Map de Flip-flop D de borda de subida com power-up BAIXO (default)

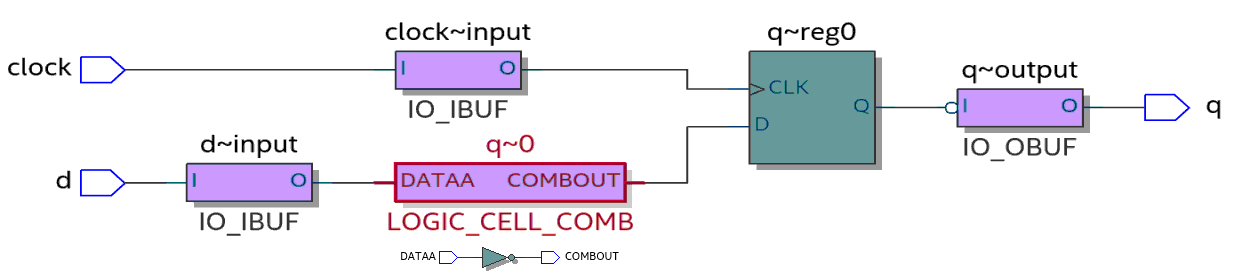

Se for definido um valor 1 no power-up, será acrescentado um inversor na entrada de dados e na saída do flip-flop.

Figura 2 - Technology Map de Flip-flop D de borda de subida, com power-up ALTO

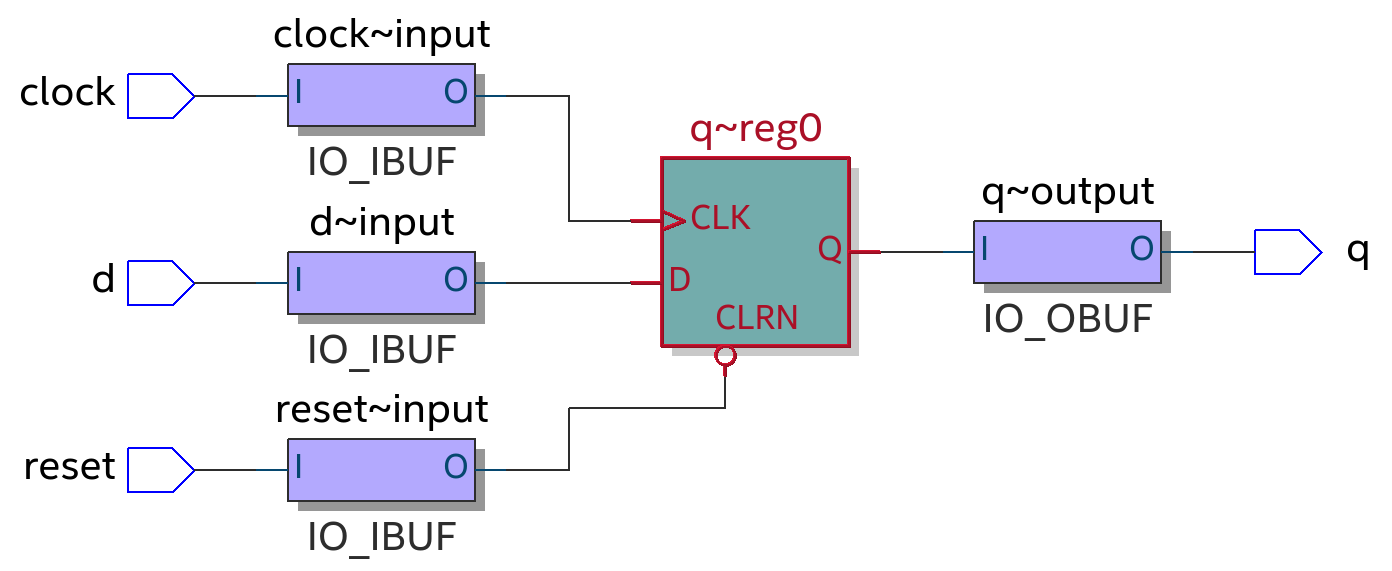

Caso seja especificado um valor de power-up e também usado um sinal de reset assincrono no flip-flop, a especificação do valor de power-up será ignorada.

Figura 3 - Technology Map de Flip-flop D de borda de subida, com power-up ALTO, mas com reset assincrono

- Ver

- 1.5.1.1. Specifying a Power-Up Value - INTEL

- 1.5.1. Register Power-Up Values - INTEL