Mudanças entre as edições de "CIL-EngTel (página)"

| (181 revisões intermediárias por 11 usuários não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

| + | __INDEX__ | ||

| + | |||

{{DivulgueEngtelecom}} | {{DivulgueEngtelecom}} | ||

| Linha 5: | Linha 7: | ||

==[[CIL-EngTel (Plano de Ensino) | Plano de Ensino]]== | ==[[CIL-EngTel (Plano de Ensino) | Plano de Ensino]]== | ||

| − | == | + | ==Slides utilizados em sala== |

| − | *[[ | + | #[http://docente.ifsc.edu.br/odilson/CIL29003/Pedroni_Cap_1_Introducao.pdf Introdução - Pedroni Cap. 1] |

| + | #[http://docente.ifsc.edu.br/odilson/CIL29003/Pedroni_Cap_2_Representacoes_Binarias.pdf Representações Binárias - Pedroni Cap. 2] | ||

| + | #[http://docente.ifsc.edu.br/odilson/CIL29003/Pedroni_Cap_3_Aritmetica_Binaria.pdf Aritmética Binária - Pedroni Cap. 3] | ||

| + | #[http://docente.ifsc.edu.br/odilson/CIL29003/Pedroni_Cap_4_Introducao_Circuitos_Digitais.pdf Introdução aos Circuitos Digitais - Pedroni Cap. 4] | ||

| + | #[http://docente.ifsc.edu.br/odilson/CIL29003/Pedroni_Cap_5_Algebra_Booleana.pdf Álgebra Booleana - Pedroni Cap. 5] | ||

| + | #[http://docente.ifsc.edu.br/odilson/CIL29003/Pedroni_Cap_10_Familias_Logicas.pdf Famílias Lógicas - Pedroni Cap. 10] | ||

| + | #[http://docente.ifsc.edu.br/odilson/CIL29003/Pedroni_Cap_11_Circuitos_combinacionais_Logicos.pdf Circuitos Combinacionais Lógicos - Pedroni Cap. 11] | ||

| + | #[http://docente.ifsc.edu.br/odilson/CIL29003/Pedroni_Cap_12_Circuitos_combinacionais_Aritmeticos.pdf Circuitos Combinacionais Aritméticos - Pedroni Cap. 12] | ||

| + | #[http://docente.ifsc.edu.br/odilson/CIL29003/Pedroni_Cap_13_Registradores.pdf Registradores - Pedroni Cap. 13] | ||

| + | #[http://docente.ifsc.edu.br/odilson/CIL29003/Pedroni_Cap_14_Circuitos_Sequenciais.pdf Circuitos Sequenciais - Pedroni Cap. 14] | ||

| + | |||

| + | ==Listas de Estudo e Exercícios== | ||

| + | |||

| + | Seções do livro do Pedroni a estudar: | ||

| + | *1.1 ==> 1.8 e 1.10 | ||

| + | *2.1 ==> 2.9 | ||

| + | *3.1 ==> 3.7 | ||

| + | *4.1 ==> 4.8 e 4.10 ==> 4.13 | ||

| + | *5.1 ==> 5.6 e 5.9 | ||

| + | *10.1 ==> 10.3, 10.5, 10.6 e 10.9 | ||

| + | *11.1, 11.5 ==> 11.7 e 11.13. | ||

| + | *12.1 ==> 12.3, 12.5, 12.6, 12.10 ==> 12.13 e 12.15. | ||

| + | *13.1, 13.2, 13.3.1, 13.4, 13.10. | ||

| + | *14.2, 14.3, 14.5, 14.7. | ||

| + | |||

| + | {{Collapse top | left = yes | title = Lista de Exercícios}} | ||

| + | |||

| + | #Converta para decimal | ||

| + | ##<math>100110_2</math> | ||

| + | ##<math>11110_2</math> | ||

| + | ##<math>111011_2</math> | ||

| + | ##<math>1010000_2</math> | ||

| + | ##<math>11000101_2</math> | ||

| + | ##<math>11001100110101_2</math> | ||

| + | ##<math>14_8</math> | ||

| + | ##<math>67_8</math> | ||

| + | ##<math>153_8</math> | ||

| + | ##<math>1544_8</math> | ||

| + | ##<math>2063_8</math> | ||

| + | ##<math>479_16</math> | ||

| + | ##<math>4AB_16</math> | ||

| + | ##<math>BDE_16</math> | ||

| + | ##<math>F0CA_16</math> | ||

| + | ##<math>2D3F_16</math> | ||

| + | #Converta para a base indicada: | ||

| + | ##<math> 1428_{10} = X_{16} </math> | ||

| + | ##<math> 428_{10} = X_{8}</math> | ||

| + | ##<math> 28_{10} = X_{2}</math> | ||

| + | ##<math> F0F0_{16} = X_{2}</math> | ||

| + | ##<math> 1427_{8} = X_{16}</math> | ||

| + | ##<math> 1001010_{2} = X_{16}</math> | ||

| + | ##<math> 1001010_{10} = X_{16}</math> | ||

| + | ##<math> 1428_{16} = X_{8}</math> | ||

| + | #Livro Pedroni: 2.16 ==> 2.38 | ||

| + | #Qual é o maior e menor valor decimal que se consegue representar em complemento de dois com 8 dígitos binários? | ||

| + | #Livro Pedroni: 3.1 ==> 3.22 | ||

| + | #Livro Pedroni: 4.6 ==> 4.16, 4.18, 4.19, 4.26 ==> 4.31 | ||

| + | #O consumo de potência em um circuito lógico é dividido em estática e dinâmica. Defina cada uma dessa potências e quais são as providências a serem tomadas para sua minimização. | ||

| + | #Liste os três tipos de ''buffer''. Qual é sua função lógica? Quais são suas principais aplicações? | ||

| + | #Livro Pedroni: 5.1, 5.5, 5.8 ==> 5.19, 5.22 ==> 5.28, 5.30 ==> 5.38. | ||

| + | #Utilizando álgebra Booleana simplifique as seguintes funções lógicas, mostre todo o processo: | ||

| + | ##y=a.b+c'+(c.d)' | ||

| + | ##y=((a.b)'+{c.d)')' | ||

| + | ##y=(a+b'+c).(a+c+d')' | ||

| + | ##y=(a+b)'.c.(a+c).b' | ||

| + | ##y=((a+b)'.c)+((b.d)'.(a'+(b.d))) | ||

| + | #Para cada uma das funções lógicas da questão anterior, monte a tabela-verdade equivalente. | ||

| + | #Derive uma equação SOP mínima (irredutível) para cada uma das funções Booleanas representadas pelas tabelas-verdade da questão anterior, fazendo uso de mapas de Karnaugh. | ||

| + | #Livro Pedroni: 10.4 ==> 10.17 | ||

| + | #Livro Pedroni: 11.8 ==> 11.12, 11.14 ==> 11.21, 11.23, 11.27 e 11.28 | ||

| + | #Livro Pedroni: 12.1 ==> 12.3, 12.6a) 12.6b), 12.9 ==> 12.12, 12.16, 12.17, 12.22 | ||

| + | #Exercícios Livro Pedroni: | ||

| + | ##13.2, 13.7, 13.8, 13.9 | ||

| + | ##14.1 ==> 14.5, 14.8, 14.23, 14.33, 14.37, 14.38, 14.39. | ||

| + | #Para o gerador de sequências pseudorandômicas da Figura 14.30, calcule a sequência dos 25 primeiros bits produzidos pelo circuito, após a execução de um Reset no sistema. | ||

| + | #Faça o diagrama de ligações para um SR de 16 bits, com entrada série e saída paralela, baseado no [http://www.ti.com/lit/ds/symlink/sn74als164a.pdf sn74als164a] | ||

| + | #Faça um diagrama de tempo que explicite a entrada e saída do valor 10001101 no SR [http://www.ti.com/lit/ds/symlink/sn74als165.pdf sn74als165] | ||

| + | #Faça um diagrama de tempo que mostre a entrada serial do valor 1110 com deslocamento para a direita e, em seguida, o valor 1011 com deslocamento para a esquerda no [http://www.ti.com/lit/ds/symlink/sn74as194.pdf sn74as194]. | ||

| + | #Faça um diagrama de tempo que mostre a entrada serial do valor 1110 com deslocamento para a direita e, em seguida, entrada paralela do valor 1011 com deslocamento para a direita no [http://www.ti.com/lit/ds/symlink/sn74as194.pdf sn74as194]. | ||

| + | #Faça o diagrama de ligações para obter duas versões de um contador módulo 10, baseado no [http://www.ti.com/lit/ds/symlink/sn74ls90.pdf SN74LS90]. | ||

| + | #Faça o diagrama de ligações para obter um contador de 2 à 8, baseado no [http://www.ti.com/lit/ds/symlink/sn54als163b.pdf SN54ALS162B]. | ||

| + | #Faça o diagrama de ligações para obter um contador módulo 256 ascendente, baseado no [http://www.ti.com/lit/ds/symlink/sn74als191a.pdf SN74ALS191A]. | ||

| + | #Faça o diagrama de ligações para obter um contador módulo 256 descendente, baseado no [http://www.ti.com/lit/ds/symlink/sn74als193a.pdf SN74ALS193A]. | ||

| + | #Faça o diagrama de ligações para obter um contador de 12 à 0, baseado no [http://www.ti.com/lit/ds/symlink/sn74als169b.pdf SN74ALS169B]. | ||

| + | #Faça o diagrama de ligações para obter um contador decimal ascendente, baseado no [http://www.ti.com/lit/ds/symlink/sn74192.pdf SN74LS192]. | ||

| + | {{Collapse bottom}} | ||

| − | + | <!-- ==Desenvolvimento Pedagógico== | |

| − | + | *[[CIL29003-2018-1|CIL29003 2018-1 - Prof. Heron Eduardo de Lima Ávila]] e [[Odilson Tadeu Valle]] | |

| − | == | + | *[[CIL29003-2017-2|CIL29003 2017-2 - Prof. Odilson T. Valle]] |

| − | * | + | *[[CIL29003-2017-1|CIL29003 2017-1 - Prof. Odilson T. Valle]] |

| − | * | + | *[[CIL29003-2016-2|CIL29003 2016-2 - Prof. Odilson T. Valle]] |

| − | * | + | *[[CIL29003-2016-1|CIL29003 2016-1 - Prof. Odilson T. Valle]] |

| + | *[[CIL29003-2015-2|CIL29003 2015-2 - Prof. Odilson T. Valle]] | ||

| + | *[[CIL29003-2015-1|CIL29003 2015-1 - Prof. Odilson T. Valle]] --> | ||

| − | == | + | ==[[Software e equipamentos recomendados para programação de FPGAs]]== |

| − | |||

==Circuitos Integrados Comerciais== | ==Circuitos Integrados Comerciais== | ||

| Linha 25: | Linha 113: | ||

Esta página [http://quarndon.co.uk/WallChart/wc74.php?p=0] também apresenta uma rápida visualização da pinagem dos CIs mais antigos do tipo DIP. | Esta página [http://quarndon.co.uk/WallChart/wc74.php?p=0] também apresenta uma rápida visualização da pinagem dos CIs mais antigos do tipo DIP. | ||

| − | + | ===Listagem de circuitos integrados=== | |

| + | [https://pt.wikipedia.org/wiki/Lista_dos_circuitos_integrados_da_s%C3%A9rie_7400 Lista dos circuitos integrados da série 7400] | ||

===Circuitos Lógicos=== | ===Circuitos Lógicos=== | ||

| + | *'''Buffer''' | ||

| + | :* 3-Estados - [http://www.ti.com/lit/ds/symlink/sn74ahc1g125.pdf 74AHC1G125] <small> <math> I_OL = 8 mA; I_OH = -8 mA </math></small> | ||

| + | :* 3-Estados e Driver - [http://www.ti.com/lit/ds/symlink/sn74ahc541.pdf 74AHC541] <small> <math> I_OL = 50 mA; I_OH = -50 mA </math></small> | ||

| + | :* Dreno aberto - [http://www.ti.com/lit/ds/symlink/sn74lv07a.pdf 74LV07A] <small> The open-drain outputs require pullup resistors to perform correctly and can be connected to other open-drain outputs to implement active-low wired-OR or active-high wired-AND functions. </small> | ||

| + | :* Coletor aberto - [http://www.ti.com/lit/ds/symlink/sn7407.pdf 7407] | ||

| + | <!--[[Arquivo:Schmitt_trigger_symbol.svg |150 px]] --> | ||

| + | :*Schmitt trigger - [http://www.ti.com/lit/ds/symlink/sn74auc1g17.pdf SN74AUC1G17]<small> @<math> VCC = 2,3 V; V_T+ = 1,11 V; V_T- = 0,58 V </math></small> | ||

| + | ::*ver [https://en.wikipedia.org/wiki/Schmitt_trigger wikipedia] | ||

| + | ::*ver [http://www.falstad.com/circuit/ Simulador de circuitos do Falstad] Circuits > Op-Amps > Schmitt-trigger | ||

| + | ::*ver aplicações para esses circuitos [http://www.ti.com/lit/an/scea046/scea046.pdf] | ||

*'''Inversor''' - 6 Inversor - [http://www.ti.com/lit/ds/symlink/sn54als04b.pdf 74X04]; | *'''Inversor''' - 6 Inversor - [http://www.ti.com/lit/ds/symlink/sn54als04b.pdf 74X04]; | ||

| + | ::*ver o funcionamento do circuito inversor CMOS [http://www.falstad.com/circuit/ Simulador de circuitos do Falstad] Circuits > Logic Families > CMOS > Inverter | ||

*'''AND''' - 4 Porta AND2 - [http://www.ti.com/lit/ds/symlink/sn54als08.pdf 74X08], 3 Porta AND3 - [http://www.ti.com/lit/ds/symlink/sn54as11.pdf 74X11], 2 Porta AND4 - [http://www.ti.com/lit/ds/symlink/sn74als21a.pdf 74X21]. | *'''AND''' - 4 Porta AND2 - [http://www.ti.com/lit/ds/symlink/sn54als08.pdf 74X08], 3 Porta AND3 - [http://www.ti.com/lit/ds/symlink/sn54as11.pdf 74X11], 2 Porta AND4 - [http://www.ti.com/lit/ds/symlink/sn74als21a.pdf 74X21]. | ||

*'''NAND''' - 4 Porta NAND2 - [http://www.ti.com/lit/ds/sdls025b/sdls025b.pdf 74X00], 3 Porta NAND3 - [http://www.ti.com/lit/ds/symlink/sn54as10.pdf 74X10], 2 Porta NAND4 - [http://www.ti.com/lit/ds/symlink/sn74ls20.pdf 74X20]; 1 Porta NAND8 - [http://www.ti.com/lit/ds/symlink/sn74ls30.pdf 74X30]; 1 Porta NAND13 - [http://www.ti.com/lit/ds/symlink/sn74als133.pdf 74X133]. | *'''NAND''' - 4 Porta NAND2 - [http://www.ti.com/lit/ds/sdls025b/sdls025b.pdf 74X00], 3 Porta NAND3 - [http://www.ti.com/lit/ds/symlink/sn54as10.pdf 74X10], 2 Porta NAND4 - [http://www.ti.com/lit/ds/symlink/sn74ls20.pdf 74X20]; 1 Porta NAND8 - [http://www.ti.com/lit/ds/symlink/sn74ls30.pdf 74X30]; 1 Porta NAND13 - [http://www.ti.com/lit/ds/symlink/sn74als133.pdf 74X133]. | ||

| + | ::*ver o funcionamento do circuito NAND CMOS [http://www.falstad.com/circuit/ Simulador de circuitos do Falstad] Circuits > Logic Families > CMOS > CMOS NAND | ||

*'''NOR''' - 4 Porta NOR2 - [http://www.ti.com/lit/ds/symlink/sn74als02a.pdf 74X02]; 3 Porta NOR3 - [http://www.ti.com/lit/ds/symlink/sn74als27a.pdf 74X27]; 2 Porta NOR5 - [http://www.ti.com/lit/ds/symlink/dm74ls260.pdf 74X260]. | *'''NOR''' - 4 Porta NOR2 - [http://www.ti.com/lit/ds/symlink/sn74als02a.pdf 74X02]; 3 Porta NOR3 - [http://www.ti.com/lit/ds/symlink/sn74als27a.pdf 74X27]; 2 Porta NOR5 - [http://www.ti.com/lit/ds/symlink/dm74ls260.pdf 74X260]. | ||

| + | ::*ver o funcionamento do circuito NOR CMOS [http://www.falstad.com/circuit/ Simulador de circuitos do Falstad] Circuits > Logic Families > CMOS > CMOS NOR | ||

*'''OR''' - 4 Porta OR2 - [http://www.ti.com/lit/ds/symlink/sn74ls32.pdf 74X32]. | *'''OR''' - 4 Porta OR2 - [http://www.ti.com/lit/ds/symlink/sn74ls32.pdf 74X32]. | ||

*'''XOR''' - 4 Porta XOR2 - [http://www.ti.com/lit/ds/symlink/sn74ls86a.pdf 74X86]; 4 Porta XOR2 - [http://www.ti.com/lit/ds/symlink/sn74ls386a.pdf 74X386]. | *'''XOR''' - 4 Porta XOR2 - [http://www.ti.com/lit/ds/symlink/sn74ls86a.pdf 74X86]; 4 Porta XOR2 - [http://www.ti.com/lit/ds/symlink/sn74ls386a.pdf 74X386]. | ||

*'''XNOR''' - 4 Porta XNOR2 - [http://www.ti.com/lit/ds/symlink/sn74ls266.pdf 74X266]. | *'''XNOR''' - 4 Porta XNOR2 - [http://www.ti.com/lit/ds/symlink/sn74ls266.pdf 74X266]. | ||

| − | |||

===Circuitos Lógicos Combinacionais=== | ===Circuitos Lógicos Combinacionais=== | ||

| + | *Decodificador/Demultiplexador 3 para 8 linhas - [http://www.ti.com/lit/ds/symlink/sn54als138a.pdf 74X138] | ||

| + | *2x Decodificador/Demultiplexador 2 para 4 linhas [http://www.ti.com/lit/ds/symlink/sn54als139.pdf 74X139] | ||

| + | *Decodificador/Driver BCD para Sete Segmentos - [http://www.ti.com/lit/ds/symlink/sn7447a.pdf 74X47/48/49] | ||

| + | *Decodificador/Demultiplexador 3 para 8 linhas com Latch - [http://www.ti.com/lit/ds/symlink/sn54als137a.pdf 74X137] | ||

| + | *Codificador de prioridade 8 linhas para 3 linhas - [http://www.ti.com/lit/ds/symlink/sn54ls148.pdf 74x48] | ||

*Multiplexador/Seletor de 8 para 1 - [http://www.ti.com/lit/ds/symlink/sn54als151.pdf 74X151] | *Multiplexador/Seletor de 8 para 1 - [http://www.ti.com/lit/ds/symlink/sn54als151.pdf 74X151] | ||

*2x Multiplexador/Seletor de 4 para 1 - [http://www.ti.com/lit/ds/symlink/sn54als153.pdf 74X153] | *2x Multiplexador/Seletor de 4 para 1 - [http://www.ti.com/lit/ds/symlink/sn54als153.pdf 74X153] | ||

*4x Multiplexador/Seletor de 2 para 1 - [http://www.ti.com/lit/ds/symlink/sn54als158.pdf 74X157/158] | *4x Multiplexador/Seletor de 2 para 1 - [http://www.ti.com/lit/ds/symlink/sn54als158.pdf 74X157/158] | ||

| − | |||

| − | |||

| − | |||

*Decodificador BCD para 10 linhas decimais [http://www.ti.com/lit/ds/symlink/sn74ls42.pdf 74X42] | *Decodificador BCD para 10 linhas decimais [http://www.ti.com/lit/ds/symlink/sn74ls42.pdf 74X42] | ||

| − | |||

*Codificador de Prioridade de 8 para código binário - [http://www.ti.com/lit/ds/symlink/sn74ls148.pdf 74X148] | *Codificador de Prioridade de 8 para código binário - [http://www.ti.com/lit/ds/symlink/sn74ls148.pdf 74X148] | ||

*Gerador de Paridade Par e Impar de 9 bits - [http://www.ti.com/lit/ds/symlink/sn74ls280.pdf 74X280] | *Gerador de Paridade Par e Impar de 9 bits - [http://www.ti.com/lit/ds/symlink/sn74ls280.pdf 74X280] | ||

| Linha 51: | Linha 153: | ||

===Circuitos Aritméticos Combinacionais=== | ===Circuitos Aritméticos Combinacionais=== | ||

*Somador de 4 bits - [http://www.ti.com/lit/ds/symlink/sn54ls283.pdf 74X283] | *Somador de 4 bits - [http://www.ti.com/lit/ds/symlink/sn54ls283.pdf 74X283] | ||

| − | *Unidade de Lógica e Aritmética - [http://www. | + | *Unidade de Lógica e Aritmética - [http://www.esi.uclm.es/www/isanchez/apuntes/ci/74181.pdf 74X181]. |

| + | *Multiplicador de 4 bits. Obs: integrando o 74284 e 74285 [http://docente.ifsc.edu.br/odilson/CIL29003/74284.pdf 74284]. | ||

*Look Ahead Carry Generator - [http://www.ti.com/lit/ds/symlink/sn54s182.pdf 74X182] | *Look Ahead Carry Generator - [http://www.ti.com/lit/ds/symlink/sn54s182.pdf 74X182] | ||

*Comparador BCD - [http://www.ti.com/lit/ds/sdls123/sdls123.pdf 74X85] | *Comparador BCD - [http://www.ti.com/lit/ds/sdls123/sdls123.pdf 74X85] | ||

*Comparador de magnitude de 8 bits - [http://www.ti.com/lit/ds/symlink/sn54ls688.pdf 74X688] | *Comparador de magnitude de 8 bits - [http://www.ti.com/lit/ds/symlink/sn54ls688.pdf 74X688] | ||

*Comparador de igualdade de 8 bits - [http://www.ti.com/lit/ds/symlink/sn74als521.pdf 74X521] | *Comparador de igualdade de 8 bits - [http://www.ti.com/lit/ds/symlink/sn74als521.pdf 74X521] | ||

| − | *Multiplicador binário de 4 bits por 4 bits - [http://www.ti.com/lit/ds/symlink/sn74284.pdf 74X284/285] | + | <!-- *Multiplicador binário de 4 bits por 4 bits - [http://www.ti.com/lit/ds/symlink/sn74284.pdf 74X284/285] --> |

<!-- *Multiplicador binário de 2 bits por 4 bits - [http://www.ti.com/lit/ds/sdls150/sdls150.pdf 74X261] --> | <!-- *Multiplicador binário de 2 bits por 4 bits - [http://www.ti.com/lit/ds/sdls150/sdls150.pdf 74X261] --> | ||

===Circuitos Sequenciais=== | ===Circuitos Sequenciais=== | ||

| − | *Registrador de deslocamento | + | *Registrador de deslocamento [http://www.ti.com/lit/ds/symlink/sn74als164a.pdf 74X164] 8-bit Saída Paralela, [http://www.ti.com/lit/ds/symlink/sn74als165.pdf 74X165], [http://www.ti.com/lit/ds/symlink/sn74als166.pdf 74X166] 8-bits Carga Parelela e saída serial, [http://www.ti.com/lit/ds/symlink/sn74as194.pdf 74x194] 4-Bit Bidirectional Universal Shift Registers, [http://www.ti.com/lit/ds/symlink/sn74als299.pdf 74x299] 8-Bit Universal Shift/Storage Registers With 3-State Outputs. |

*Contador Assíncrono [http://www.ti.com/lit/ds/symlink/sn74ls90.pdf 74X90/92/93] - 74X90- Decada, 74X92 - Duzia, 74X93 - Binário 4 bits, [http://www.ti.com/lit/ds/symlink/sn74ls390.pdf 74X390] - 2x Decada, | *Contador Assíncrono [http://www.ti.com/lit/ds/symlink/sn74ls90.pdf 74X90/92/93] - 74X90- Decada, 74X92 - Duzia, 74X93 - Binário 4 bits, [http://www.ti.com/lit/ds/symlink/sn74ls390.pdf 74X390] - 2x Decada, | ||

| − | * | + | *Contadores Síncronos |

| − | + | **Binário e decádico ascendente/descendente: [http://www.ti.com/lit/ds/symlink/sn54ls669.pdf 74x669/668]; | |

| + | **Binário e decádico ascendente, com Clear: [http://www.ti.com/lit/ds/symlink/sn54als163b.pdf 74X161/162/163]; | ||

| + | **Binário ascendente/descendente: [http://www.ti.com/lit/ds/symlink/sn74als191a.pdf 74X191]; | ||

| + | **Binário e decádico ascendente/descendente, dois pinos de clock distintos, indicado somente para contar eventos, não tempo, com Clear: [https://www.ti.com/lit/gpn/sn74ls193 74X192/193]; | ||

| + | **Binário ascendente/descendente: [http://www.ti.com/lit/ds/symlink/sn74als169b.pdf 74X169]; | ||

| + | *Registradores com DFF [http://www.ti.com/lit/ds/symlink/sn54als174.pdf 74X174] Hex D-type Flip-Flops With Clear, [http://www.ti.com/lit/ds/symlink/sn54als273.pdf 74X273] Octal D-type Flip-Flops With Clear | ||

==Materiais de apoio as aulas== | ==Materiais de apoio as aulas== | ||

| Linha 69: | Linha 177: | ||

*[http://mathworld.wolfram.com/Hexadecimal.html Sistema de numeração hexadecimal] | *[http://mathworld.wolfram.com/Hexadecimal.html Sistema de numeração hexadecimal] | ||

*[http://mathworld.wolfram.com/Octal.html Sistema de numeração octal] | *[http://mathworld.wolfram.com/Octal.html Sistema de numeração octal] | ||

| + | *[[Multiplicação Binária]] | ||

| + | *[[Display de 7 segmentos]] | ||

*[http://ocw.mit.edu/courses/electrical-engineering-and-computer-science/6-002-circuits-and-electronics-spring-2007/video-lectures/lecture-4/ A abstração Digital] - MIT, Prof. Anant Agarwal | *[http://ocw.mit.edu/courses/electrical-engineering-and-computer-science/6-002-circuits-and-electronics-spring-2007/video-lectures/lecture-4/ A abstração Digital] - MIT, Prof. Anant Agarwal | ||

*[http://ocw.mit.edu/courses/electrical-engineering-and-computer-science/6-002-circuits-and-electronics-spring-2007/video-lectures/lecture-5/ Conhecendo o interior das portas lógicas] - MIT, Prof. Anant Agarwal | *[http://ocw.mit.edu/courses/electrical-engineering-and-computer-science/6-002-circuits-and-electronics-spring-2007/video-lectures/lecture-5/ Conhecendo o interior das portas lógicas] - MIT, Prof. Anant Agarwal | ||

| + | *[https://www.youtube.com/watch?v=gnhNKITVVZ8 Projeto de sistema digital] | ||

| + | *[http://e2e.ti.com/cfs-file.ashx/__key/communityserver-discussions-components-files/138/6320.Voltages.jpg Tensões de entrada e saída nas familias lógicas] | ||

| + | *Algumas informações muito úteis sobre as famílias lógicas, migração, níveis de tensão, encapsulamento podem ser vistas no [TI - Logic Guide http://www.ti.com/lit/sg/sdyu001aa/sdyu001aa.pdf]. | ||

*[http://download.intel.com/newsroom/kits/22nm/pdfs/Intel_Transistor_Backgrounder.pdf A evolução do transistor MOS], [http://www.intel.com/content/www/us/en/history/museum-transistors-to-transformations-brochure.html] | *[http://download.intel.com/newsroom/kits/22nm/pdfs/Intel_Transistor_Backgrounder.pdf A evolução do transistor MOS], [http://www.intel.com/content/www/us/en/history/museum-transistors-to-transformations-brochure.html] | ||

| − | *Atualmente estamos na tecnologia de [http://en.wikipedia.org/wiki/22_nanometer 22nm], [http://download.intel.com/newsroom/kits/22nm/pdfs/22nm-Details_Presentation.pdf],já ingressando em [http://www.altera.com/literature/wp/wp-01201-fpga-tri-gate-technology.pdf 14 nm], [http://www.altera.com/devices/fpga/stratix-fpgas/stratix10/stx10-index.jsp]. No futuro qual será o tamanho do canal do GATE do transistor MOS [http://en.wikipedia.org/wiki/5_nanometer]? | + | *Atualmente estamos na tecnologia de [http://en.wikipedia.org/wiki/22_nanometer 22nm], [http://download.intel.com/newsroom/kits/22nm/pdfs/22nm-Details_Presentation.pdf],já ingressando em [http://www.altera.com/literature/wp/wp-01201-fpga-tri-gate-technology.pdf 14 nm]. [https://www.altera.com/solutions/technology/next-generation-technology/overview.html], [http://www.altera.com/devices/fpga/stratix-fpgas/stratix10/stx10-index.jsp]. No futuro qual será o tamanho do canal do GATE do transistor MOS [http://en.wikipedia.org/wiki/5_nanometer] [https://www.semiwiki.com/forum/content/5080-imec-cadence-disclose-5nm-test-chip.html Veja os teste com 5nm da IMEC e Cadence]? |

| + | *O menor transistor 4nm. [http://www.nature.com/nnano/journal/v5/n7/full/nnano.2010.95.html], [http://www.dailytech.com/article.aspx?newsid=18476] | ||

| + | |||

| + | <!--==Avaliações == | ||

| + | *Avaliação 1 | ||

| + | *Avaliação 2 | ||

| + | *Avaliação 3 | ||

| + | *Projeto Final | ||

| + | *Recuperação final --> | ||

==Aulas de Laboratório== | ==Aulas de Laboratório== | ||

| − | *[[Uso do software Quartus e QSIM para ensino de Circuitos Lógicos]] | + | {{Collapse top | left = yes | title = Orientações gerais para o uso do software Quartus}} |

| − | + | <span style="font-size:150%">As principais etapas para elaborar um projeto no Quartus são: | |

| − | + | #Crie um novo projeto. | |

| − | + | ##Todo projeto deve possuir um diretório exclusivo, onde estarão contidos todos os arquivos relacionados ao projeto. | |

| + | ##File > New Project Wizard > Next | ||

| + | ##Ao salvar arquivos e projetos tome '''sempre''' as seguintes precauções, sob pena de erros de compilação. | ||

| + | ###'''Não''' nomeie diretórios e/ou arquivos com espaço em branco, se necessário utilize "_" (''underline'') como caractere separador. | ||

| + | ###'''Não''' nomeie diretórios e/ou arquivos com caracteres especiais e/ou caracteres acentuados. | ||

| + | ###'''Não''' inicie o nome de projetos e/ou circuitos com caracteres numéricos e/ou caracteres especiais e/ou caracteres acentuados. | ||

| + | #Crie o(s) circuito(s) desejado(s). | ||

| + | ##Nos circuitos são adicionadas as portas lógicas, os CIs e as todas as conexões/ligações. | ||

| + | ##File > New > Block Diagram/Schematic File | ||

| + | #Compile cada circuito criado. | ||

| + | ##A compilação, entre outras coisas, verifica a existência ou não de erros no projeto. | ||

| + | ##Processing > Star Compilation | ||

| + | ##A compilação valerá para o circuito que esta no Top Level. Para escolher outro circuito acesse a aba Files >> tecla direita do mouse no circuito desejado >> Set as Top-Level Entity). | ||

| + | #Faça a simulação de cada circuito criado. | ||

| + | ##Existem a simulação funcional e temporal. Elas auxiliam o projetista a verificar se o circuito criado está funcionando de acordo com o planejado. | ||

| + | ## Para realizar a simulação, crie o arquivo que irá conter todas as formas de onda desejadas. | ||

| + | ##File > New > Verification/Debugging Files > University Program VWF. | ||

| + | ## Essa é uma das principais etapas pois será verificado se o circuito projetado esta se comportando conforme desejado. | ||

| + | #Faça a associação de pinos. | ||

| + | ##A associação de pinos nada mais é que a ligação do circuito projetado com o pinos reais da placa FPGA. | ||

| + | ##Assignments > Pin Planner. | ||

| + | #Programe e configure a FPGA. | ||

| + | ##Aqui é o momento onde se programa a placa FPGA com o código criado a partir dos circuitos projetados. | ||

| + | ##Tools > Programmer. | ||

| + | <span style="font-size:150%">Arquivando e recuperando projetos | ||

| + | #Procedimento para arquivar/salvar projetos | ||

| + | ##Project > Archive Project... > Archive file name: nome_do_projeto.qar | ||

| + | ##O arquivo será salvo em: '''/home/aluno/nome_do_projeto/output_files/nome_do_projeto.qar''' | ||

| + | ##Copie o arquivo para algum repositório particular remoto ou mande o mesmo (nome_do_projeto.qar) para o seu email. | ||

| + | #Procedimento para restaurar um projeto: | ||

| + | ##Baixe o arquivo .qar salvo em uma pasta local cujo nome não possua caracteres especiais e/ou acentuados. | ||

| + | ##Execute o Quartus. | ||

| + | ##Clique na opção '''Open Existing Project'''. | ||

| + | ##Navegue no gerenciador de arquivos até encontrar o '''.qar''' baixado, dê duplo clique no mesmo e '''OK'''. | ||

| + | <span style="font-size:150%">Criando um símbolo para um circuito | ||

| + | # Selecione, na IDE do Quartus II, o diagrama esquemático e [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK]. | ||

| + | #Note que um novo simbolo estará disponível para uso no diagrama esquemático com o nome FullAdder [Symbol >> Project >> FullAdder] | ||

| + | {{Collapse bottom}} | ||

| + | |||

| + | {{Collapse top | left = yes | title = Orientações para a gravação da FPGA}} | ||

| + | #Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. | ||

| + | #Confira a família e dispositivo a ser usado (Assignments > Devices), utilizando a família family='''Cyclone IV E''' com o dispositivo device='''EP4CE115F29C7''' ou com dispositivo '''device = EP4CE30F23C7''', e faça uma nova Análise e Síntese para que a nova pinagem do FPGA seja reconhecida pelo Quartus. | ||

| + | #Atribua os pinos do circuito aos pinos do FPGA utilizando o Pin Planner (Assignments > Pin Planner). | ||

| + | #Para descobrir a pinagem do FPGA e sua associação com os componentes do kit consulte as informações disponíveis em [[Interfaces de entrada e saída da DE2-115 | Pinagem dos dispositivos de entrada e saída do kit DE2-115 ]] ou [[Pinagem_dos_dispositivos_de_entrada_e_saída_do_kit_MERCURIO_IV]]. | ||

| + | #Verifique se todas as entradas e saídas do projeto estão conectadas corretamente aos pinos do FPGA. Nenhuma posição da coluna '''Location''' deve estar vazia. E nenhuma posição da coluna '''Direction''' deve estar em '''unknown'''. | ||

| + | #Verifique se os '''pinos não usados''' estão setados para entrada em 3-state ou 3-state com weak pull-up. | ||

| + | #Compile o projeto. Note que agora a numeração dos pinos também aparece no diagrama esquemático. | ||

| + | #No Quartus vá em (Tools > Programmer) para abrir a página de programação da placa. | ||

| + | #Selecione o Hardware (Hardware Setup > USB-Blaster). | ||

| + | #*Se não aparecer a [USB-BLASTER], e aparecer no seu lugar a [USB-BLASTER Variant], ou [No Hardware], então será necessário alterar os arquivos de configuração (precisa de senha de root), segundo o procedimento descrito em [[Configuração da USB para programação do FPGA via JTAG]]. | ||

| + | #*Caso ainda apresente algum problema siga os passos apresentados em [[Programando o FPGA através da USB-Blaster]]. | ||

| + | #Utilize o modo JTAG e clique em '''Start''' para começar a programação; | ||

| + | {{Collapse bottom}} | ||

| + | |||

| + | {{Collapse top | left = yes | title = Orientações para sincronismo e uso de clocks}} | ||

| + | #Para circuitos que necessitem de uma base de tempo, disponibilizamos dois circuitos prontos que fornecem bases de 1 ms e 1s. Para utilizá-los execute os passos: | ||

| + | ##Crie ou abra um projeto no Quartus, por exemplo, /home/aluno/meu_projeto. | ||

| + | ##Baixe o arquivo [http://docente.ifsc.edu.br/odilson/CIL29003/clk1ms.zip Clock de 1 ms] ou [http://docente.ifsc.edu.br/odilson/CIL29003/clk1s.zip Clock de 1 s], descompacte e salve no diretório raiz do projeto a ser utilizado, por exemplo, /home/aluno/meu_projeto. | ||

| + | ##Será criado um novo circuito que pode ser acessado por Symbol tool (ícone de uma porta AND no menu superior) > Project > clock1s ou clock1ms. | ||

| + | ##A entrada '''clock''' deverá ser conectada na base de tempo da própria FPGA (PIN_T1) e a saída com a base de tempo desejada é a '''cout'''. Os demais pinos deixa-se em aberto. | ||

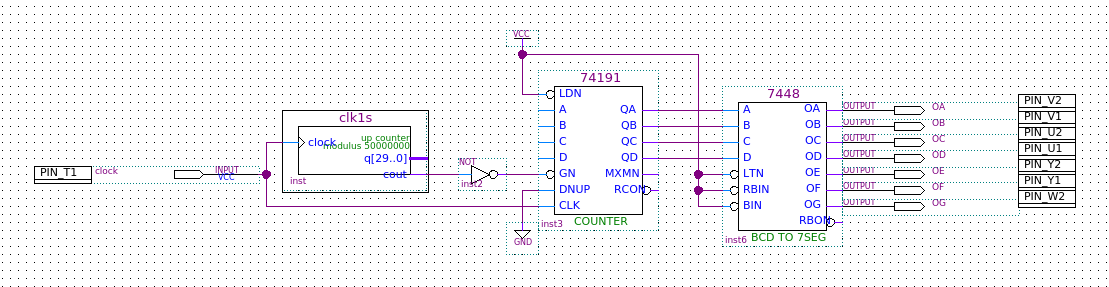

| + | #Para o bom funcionamento do FPGA é recomendado que todos os sub-sistemas sejam sincronizados, quando trabalham em base temporal. Na figura abaixo temos um exemplo desse sincronismo. <center> [[Arquivo:Sincronismo_blocos.png|600px|Exemplo de sincronismo]] </center> | ||

| + | *Perceba que o sinal de clock da FPGA é (PIN_T1) é utilizado para os dois circuito presentes. | ||

| + | {{Collapse bottom}} | ||

| + | |||

| + | {{Collapse top | left = yes | title = Orientações para criação do circuito ''debounce''}} | ||

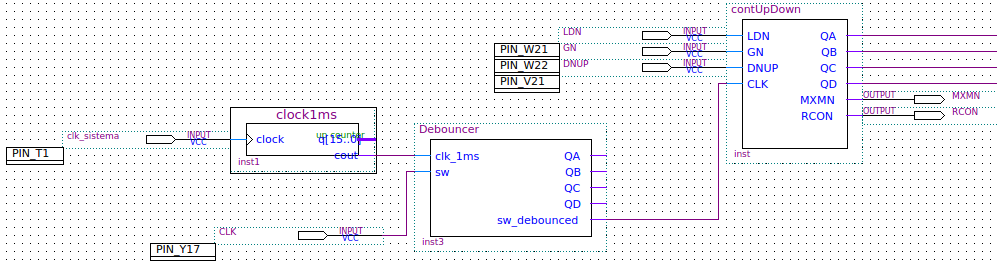

| + | *Normalmente uma chave apresenta os denominados repiques de sinal, ou seja, ao se alterar o estado da chave o sinal elétrico oscila várias vezes entre um nível lógico e outro, antes de estabilizar. No caso de esse sinal ser utilizado como clock para um determinado circuito, o mesmo pode receber vários pulsos, quando a intenção era um único pulso. | ||

| + | *Para evitar esse fenômeno pode-se fazer uso de um ''debounce'' que gera um atraso entre os estados, ocultando a sequência de pulsos gerados fisicamente pela chave. | ||

| + | *Para criar um ''debounce'' siga os seguintes passos: | ||

| + | #Baixe o arquivo [http://docente.ifsc.edu.br/odilson/CIL29003/clk1ms.zip Clock de 1 ms], descompacte e salve todos os arquivos no diretório raiz do projeto a ser utilizado, por exemplo, /home/aluno/meu_projeto. | ||

| + | #Baixe o arquivo [http://docente.ifsc.edu.br/odilson/CIL29003/Debounce.zip debounce], descompacte e salve todos os arquivos no diretório raiz do projeto a ser utilizado, por exemplo, /home/aluno/meu_projeto. | ||

| + | #Serão criados dois novos circuitos que podem ser acessados por Symbol tool (ícone de uma porta AND no menu superior) > Project > clock1ms ou Debouncer_v2. | ||

| + | # Volte ao diagrama do projeto, onde deseja introduzir o ''debounce'', e acrescente os blocos '''clock1ms''' e '''debounce''': Symbol Tool > Project > clk1ms e Symbol Tool > Project > debounce. | ||

| + | # Interligue os blocos: | ||

| + | ##A entrada '''clock''' do circuito '''clock1ms''' em '''PIN_T1'''. | ||

| + | ##A saída '''cout''' do circuito '''clock1ms''' em '''clk_1ms''' do circuito '''debounce'''. | ||

| + | ##A entrada '''sw''' do circuito '''debouncer''' na chave a ser utilizada no projeto. | ||

| + | ##A saída '''sw_debounced''' no '''CLK''' do contador ou circuito onde deseja-se o sinal "limpo" da chave. <center> [[Arquivo:Debouncer.png|600px|Uso do ''debounce'']] </center> | ||

| + | # Compile novamente o projeto. | ||

| + | {{Collapse bottom}} | ||

| + | |||

| + | {{Collapse top | left = yes | title = Orientações para programar utilizando a máquina local ou a Nuvem}} | ||

| + | #Há duas formas de executar o Quartus: | ||

| + | ##Acesso local: Nas máquinas dos laboratórios do campus basta rodar o '''Quartus versão 13'''. | ||

| + | ##Acesso remoto: basta acessar o site [https://nuvem.sj.ifsc.edu.br/ nuvem.sj.ifsc.edu.br] e seguir as orientações. Para acesso utilize os dados do portal de alunos. | ||

| + | #Em ambos os casos e '''somente no primeiro uso''', se necessário: | ||

| + | ##Ajuste o atalho para o navegador, para poder ler os manuais quando necessário, por meio de '''Tools > Options > Internet Connectivity''', no campo '''Web browser''' preencha: '''/usr/bin/firefox'''. | ||

| + | ##Verifique a [[Licença Quartus]] | ||

| + | #Outra opção é utilizar a versão ''free'' do [https://www.intel.com/content/www/us/en/programmable/downloads/download-center.html Quartus], que apresenta praticamente todas as funcionalidades da versão comercial, com certeza suficiente para o desenvolvimento de nossos projetos. | ||

| + | |||

| + | <span style="font-size:150%"> Dicas para programar usando a Nuvem do campus São José do IFSC. | ||

| + | #Acesse a [https://nuvem.sj.ifsc.edu.br/ Nuvem do campus São José do IFSC]. | ||

| + | #Execute o Quartus no terminal: <syntaxhighlight lang=bash> quartus & <Enter> </syntaxhighlight> | ||

| + | #Faça toda a programação e simulação do circuito na nuvem. | ||

| + | #Para os testes de hardware é necessário a transferência do arquivo da nuvem para o computador local. Detalhes em [[Acesso_ao_IFSC-CLOUD | Acesso ao IFSC_CLOUD]] | ||

| + | {{Collapse bottom}} | ||

| + | |||

| + | ===Pinagens das placas disponíveis=== | ||

| + | *[[Interfaces de entrada e saída da DE2-115 | Pinagem dos dispositivos de entrada e saída do kit DE2-115 ]] | ||

| + | *[[Pinagem dos dispositivos de entrada e saída do kit MERCURIO IV]] | ||

| + | ===Roteiros de Laboratórios=== | ||

| + | #[[Uso do software Quartus e QSIM para ensino de Circuitos Lógicos]] | ||

| + | #[[Experimento 5 para Circuitos Lógicos | Conversor BCD para display de sete segmentos]] | ||

| + | #[[Circuitos Lógicos Aritméticos]] | ||

| + | #[[Circuito de Multiplicação Binária]] | ||

| + | #[[Circuito de Comparação Binária]] | ||

| + | #[[Registrador de Deslocamento - BDF e QSIM]] | ||

| + | #[[Contador binário síncrono]] | ||

| + | #[[Minimização de funções lógicas com mapa de Karnaugh]] | ||

| + | #[[Modelo para uso em relatórios]] | ||

| + | |||

| + | ==[[Projetos Finais CIL29003]]== | ||

==Links auxiliares== | ==Links auxiliares== | ||

*[http://mathworld.wolfram.com/EyeofHorusFraction.html Sistema Binário do Egípcios] | *[http://mathworld.wolfram.com/EyeofHorusFraction.html Sistema Binário do Egípcios] | ||

| + | *[[Display de sete segmentos]] | ||

| + | *[http://www.wolframalpha.com/input/?i=1000+to+binary Wolfram Alfa] | ||

*[http://number.webmasters.sk/numerical.php Conversor de sistemas de numeração] | *[http://number.webmasters.sk/numerical.php Conversor de sistemas de numeração] | ||

| − | *[http://babbage.cs.qc.cuny.edu/IEEE-754 | + | *[http://babbage.cs.qc.cuny.edu/IEEE-754/ Conversores de número real para representação IEEE 754], [http://www.h-schmidt.net/FloatConverter/], [https://itunes.apple.com/us/app/ieee-fp/id325837744?mt=8 App para Iphone] |

| + | *[http://www.ti.com/lit/an/scea030a/scea030a.pdf Voltage Translation Between 3.3-V, 2.5-V, 1.8-V, and 1.5-V Logic Standards], [http://www.nostalcomp.cz/pdfka/prevody_urovni.pdf OLD] - Texas Instruments. | ||

| + | |||

{{ENGTELECO}} | {{ENGTELECO}} | ||

Edição atual tal como às 15h04min de 30 de novembro de 2023

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

Carga horária, Ementas, Bibliografia, Professores

Plano de Ensino

Slides utilizados em sala

- Introdução - Pedroni Cap. 1

- Representações Binárias - Pedroni Cap. 2

- Aritmética Binária - Pedroni Cap. 3

- Introdução aos Circuitos Digitais - Pedroni Cap. 4

- Álgebra Booleana - Pedroni Cap. 5

- Famílias Lógicas - Pedroni Cap. 10

- Circuitos Combinacionais Lógicos - Pedroni Cap. 11

- Circuitos Combinacionais Aritméticos - Pedroni Cap. 12

- Registradores - Pedroni Cap. 13

- Circuitos Sequenciais - Pedroni Cap. 14

Listas de Estudo e Exercícios

Seções do livro do Pedroni a estudar:

- 1.1 ==> 1.8 e 1.10

- 2.1 ==> 2.9

- 3.1 ==> 3.7

- 4.1 ==> 4.8 e 4.10 ==> 4.13

- 5.1 ==> 5.6 e 5.9

- 10.1 ==> 10.3, 10.5, 10.6 e 10.9

- 11.1, 11.5 ==> 11.7 e 11.13.

- 12.1 ==> 12.3, 12.5, 12.6, 12.10 ==> 12.13 e 12.15.

- 13.1, 13.2, 13.3.1, 13.4, 13.10.

- 14.2, 14.3, 14.5, 14.7.

| Lista de Exercícios |

|---|

|

Software e equipamentos recomendados para programação de FPGAs

Circuitos Integrados Comerciais

Para localizar os circuitos integrados comerciais existentes, consulte o Guia de produtos da Texas Instruments. Atualmente é muito comum o uso de circuitos integrados com uma única porta ou circuitos (ver Little Logic Guide). Nas listagens a seguir são mostrados as folhas de dados (Datasheet) de alguns circuitos comerciais, os quais também possuem uma implementação em VHDL disponível no software Quartus da ALTERA. O código 74X indica que o circuito pode estar disponível em diferentes famílias TTL e CMOS.

Um resumo das portas lógicas e demais circuitos da TI podem ser visualizados no guia de bolso. Os circuitos de 1 porta (páginas 79 a 84); de 2 portas (páginas 84 a 87); de 3 portas (páginas 87 e 88); e outros circuitos (páginas 161 a 288). Para a visualização da disponibilidade dos dispositivos lógicos nas diferentes famílias consulte a página 141 e 142.

Esta página [1] também apresenta uma rápida visualização da pinagem dos CIs mais antigos do tipo DIP.

Listagem de circuitos integrados

Lista dos circuitos integrados da série 7400

Circuitos Lógicos

- Buffer

- 3-Estados - 74AHC1G125

- 3-Estados e Driver - 74AHC541

- Dreno aberto - 74LV07A The open-drain outputs require pullup resistors to perform correctly and can be connected to other open-drain outputs to implement active-low wired-OR or active-high wired-AND functions.

- Coletor aberto - 7407

- Schmitt trigger - SN74AUC1G17 @

- ver wikipedia

- ver Simulador de circuitos do Falstad Circuits > Op-Amps > Schmitt-trigger

- ver aplicações para esses circuitos [2]

- Inversor - 6 Inversor - 74X04;

- ver o funcionamento do circuito inversor CMOS Simulador de circuitos do Falstad Circuits > Logic Families > CMOS > Inverter

- AND - 4 Porta AND2 - 74X08, 3 Porta AND3 - 74X11, 2 Porta AND4 - 74X21.

- NAND - 4 Porta NAND2 - 74X00, 3 Porta NAND3 - 74X10, 2 Porta NAND4 - 74X20; 1 Porta NAND8 - 74X30; 1 Porta NAND13 - 74X133.

- ver o funcionamento do circuito NAND CMOS Simulador de circuitos do Falstad Circuits > Logic Families > CMOS > CMOS NAND

- ver o funcionamento do circuito NOR CMOS Simulador de circuitos do Falstad Circuits > Logic Families > CMOS > CMOS NOR

- OR - 4 Porta OR2 - 74X32.

- XOR - 4 Porta XOR2 - 74X86; 4 Porta XOR2 - 74X386.

- XNOR - 4 Porta XNOR2 - 74X266.

Circuitos Lógicos Combinacionais

- Decodificador/Demultiplexador 3 para 8 linhas - 74X138

- 2x Decodificador/Demultiplexador 2 para 4 linhas 74X139

- Decodificador/Driver BCD para Sete Segmentos - 74X47/48/49

- Decodificador/Demultiplexador 3 para 8 linhas com Latch - 74X137

- Codificador de prioridade 8 linhas para 3 linhas - 74x48

- Multiplexador/Seletor de 8 para 1 - 74X151

- 2x Multiplexador/Seletor de 4 para 1 - 74X153

- 4x Multiplexador/Seletor de 2 para 1 - 74X157/158

- Decodificador BCD para 10 linhas decimais 74X42

- Codificador de Prioridade de 8 para código binário - 74X148

- Gerador de Paridade Par e Impar de 9 bits - 74X280

Circuitos Aritméticos Combinacionais

- Somador de 4 bits - 74X283

- Unidade de Lógica e Aritmética - 74X181.

- Multiplicador de 4 bits. Obs: integrando o 74284 e 74285 74284.

- Look Ahead Carry Generator - 74X182

- Comparador BCD - 74X85

- Comparador de magnitude de 8 bits - 74X688

- Comparador de igualdade de 8 bits - 74X521

Circuitos Sequenciais

- Registrador de deslocamento 74X164 8-bit Saída Paralela, 74X165, 74X166 8-bits Carga Parelela e saída serial, 74x194 4-Bit Bidirectional Universal Shift Registers, 74x299 8-Bit Universal Shift/Storage Registers With 3-State Outputs.

- Contador Assíncrono 74X90/92/93 - 74X90- Decada, 74X92 - Duzia, 74X93 - Binário 4 bits, 74X390 - 2x Decada,

- Contadores Síncronos

- Binário e decádico ascendente/descendente: 74x669/668;

- Binário e decádico ascendente, com Clear: 74X161/162/163;

- Binário ascendente/descendente: 74X191;

- Binário e decádico ascendente/descendente, dois pinos de clock distintos, indicado somente para contar eventos, não tempo, com Clear: 74X192/193;

- Binário ascendente/descendente: 74X169;

- Registradores com DFF 74X174 Hex D-type Flip-Flops With Clear, 74X273 Octal D-type Flip-Flops With Clear

Materiais de apoio as aulas

- Sistema de numeração binário

- Sistema de numeração hexadecimal

- Sistema de numeração octal

- Multiplicação Binária

- Display de 7 segmentos

- A abstração Digital - MIT, Prof. Anant Agarwal

- Conhecendo o interior das portas lógicas - MIT, Prof. Anant Agarwal

- Projeto de sistema digital

- Tensões de entrada e saída nas familias lógicas

- Algumas informações muito úteis sobre as famílias lógicas, migração, níveis de tensão, encapsulamento podem ser vistas no [TI - Logic Guide http://www.ti.com/lit/sg/sdyu001aa/sdyu001aa.pdf].

- A evolução do transistor MOS, [3]

- Atualmente estamos na tecnologia de 22nm, [4],já ingressando em 14 nm. [5], [6]. No futuro qual será o tamanho do canal do GATE do transistor MOS [7] Veja os teste com 5nm da IMEC e Cadence?

- O menor transistor 4nm. [8], [9]

Aulas de Laboratório

| Orientações gerais para o uso do software Quartus |

|---|

|

As principais etapas para elaborar um projeto no Quartus são:

Arquivando e recuperando projetos

Criando um símbolo para um circuito

|

| Orientações para a gravação da FPGA |

|---|

|

| Orientações para sincronismo e uso de clocks |

|---|

|

| Orientações para criação do circuito debounce |

|---|

|

| Orientações para programar utilizando a máquina local ou a Nuvem |

|---|

Dicas para programar usando a Nuvem do campus São José do IFSC.

|

Pinagens das placas disponíveis

- Pinagem dos dispositivos de entrada e saída do kit DE2-115

- Pinagem dos dispositivos de entrada e saída do kit MERCURIO IV

Roteiros de Laboratórios

- Uso do software Quartus e QSIM para ensino de Circuitos Lógicos

- Conversor BCD para display de sete segmentos

- Circuitos Lógicos Aritméticos

- Circuito de Multiplicação Binária

- Circuito de Comparação Binária

- Registrador de Deslocamento - BDF e QSIM

- Contador binário síncrono

- Minimização de funções lógicas com mapa de Karnaugh

- Modelo para uso em relatórios

Projetos Finais CIL29003

Links auxiliares

- Sistema Binário do Egípcios

- Display de sete segmentos

- Wolfram Alfa

- Conversor de sistemas de numeração

- Conversores de número real para representação IEEE 754, [10], App para Iphone

- Voltage Translation Between 3.3-V, 2.5-V, 1.8-V, and 1.5-V Logic Standards, OLD - Texas Instruments.