Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

| (237 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

==Registro on-line das aulas== | ==Registro on-line das aulas== | ||

===Unidade 1 - Introdução a disciplina=== | ===Unidade 1 - Introdução a disciplina=== | ||

| − | * | + | * 6 ENCONTROS |

{{collapse top | expand=true | Unidade 1 - Introdução a disciplina}} | {{collapse top | expand=true | Unidade 1 - Introdução a disciplina}} | ||

| − | + | ;Encontro 1 (26 jul): | |

| − | ;Encontro 1 ( | ||

* [[DLP1-EngTel (Plano de Ensino) | APRESENTAÇÃO DA DISCIPLINA]] | * [[DLP1-EngTel (Plano de Ensino) | APRESENTAÇÃO DA DISCIPLINA]] | ||

| − | |||

* A [[DLP1-EngTel (página) | PÁGINA DA DISCIPLINA]] contem os materiais que não alteram entre semestre. | * A [[DLP1-EngTel (página) | PÁGINA DA DISCIPLINA]] contem os materiais que não alteram entre semestre. | ||

* Nesta página está o [[DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke | REGISTRO DIÁRIO E AVALIAÇÕES]]. | * Nesta página está o [[DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke | REGISTRO DIÁRIO E AVALIAÇÕES]]. | ||

| − | * | + | * A entrega de atividades e avaliações será através da [https://moodle.ifsc.edu.br/course/view.php?id=699 plataforma Moodle]. A inscrição dos alunos é automática a partir do SIGAA. |

| − | * Para a comunicação entre professor-aluno, além dos avisos no SIGAA, utilizaremos o [https://mail.google.com/chat/u/0/#chat/space/ | + | * Para a comunicação entre professor-aluno, além dos avisos no SIGAA, utilizaremos o [https://mail.google.com/chat/u/0/#chat/space/AAAAu052zos chat institucional]. A princípio todos os alunos já estão previamente cadastrados pelo seu email institucional. Confiram enviando uma mensagem de apresentação. |

| − | * | + | *Durante as aulas é recomendado que o aluno utilize os softwares '''Quartus''' e '''Modelsim''' instalados nas maquinas do laboratório, mas estes também podem ser usados através da '''Nuvem do IFSC'''. |

| + | * Nas aulas é recomendado que o aluno utilize os softwares '''Quartus Light''' e '''ModelSim''' instalado nas máquinas do laboratório ou então acesse estes softwares através da [[Acesso ao IFSC-CLOUD (NUVEM)|NUVEM do IFSC]]. | ||

| + | ;LER PARA O PRÓXIMO ENCONTRO: | ||

| + | *Seção 4.1 a 4.5 de [http://www.vhdl.us/book/Pedroni_VHDL_3E_Chapter4.pdf Review of Field Programmable Gate Arrays (FPGAs)], Volnei A. Pedroni. (ou para quem preferir em português, leia as seções 18.1 a 18.3 do livro: PEDRONI, Volnei A '''Eletrônica Digital Moderna e VHDL: Princípios Digitais, Eletrônica Digital, Projeto Digital, Microeletrônica e VHDL'''; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. ISBN 9788535234657. Têm 16 exemplares disponíveis na [https://biblioteca.ifsc.edu.br/ Biblioteca do campus]. Número de chamada: 621.392 P372e) | ||

| + | *Seção 2.1 Dispositivos lógicos programáveis do TCC [[Integração de ramais analógicos com FPGA utilizando processador softcore]], Renan Rodolfo da Silva. | ||

| + | ;Encontro 2 (28 jul): | ||

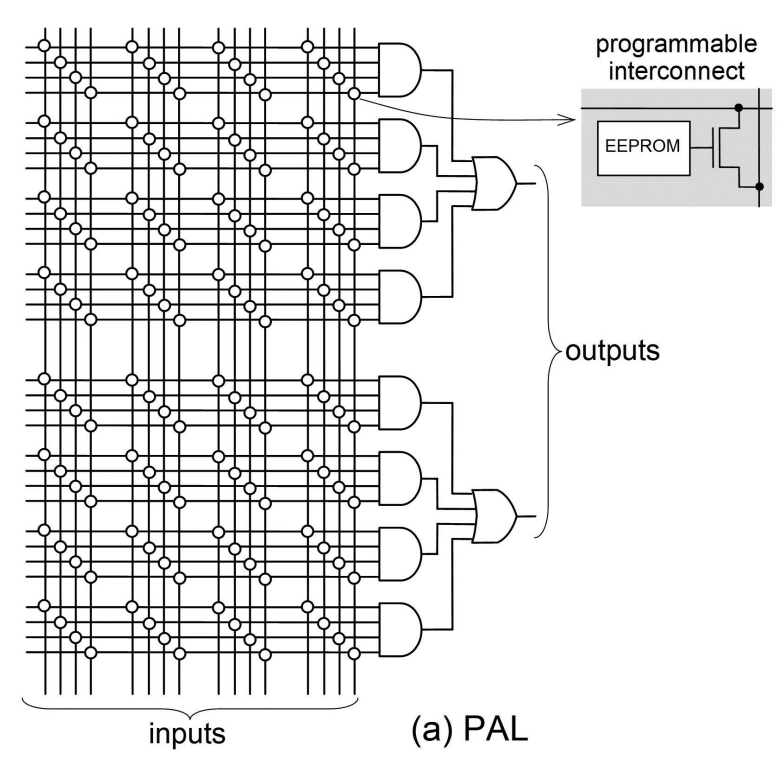

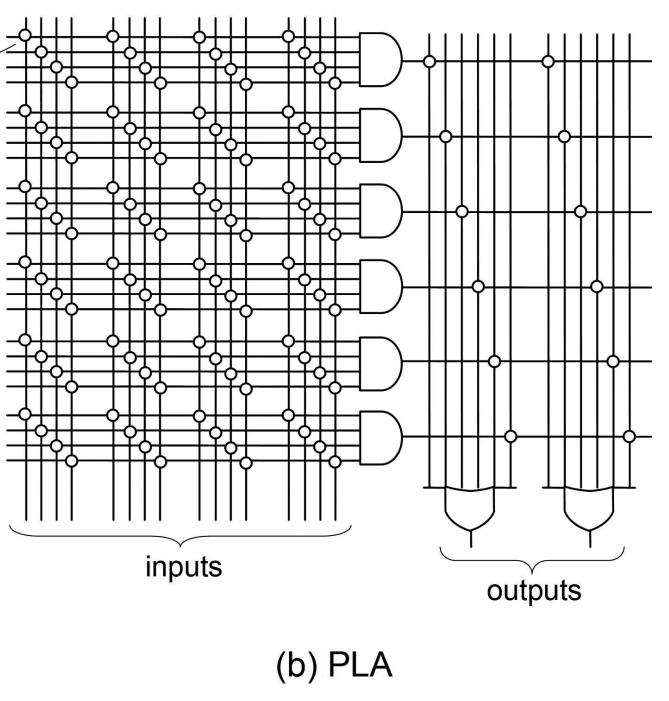

*Introdução aos dispositivos lógicos programáveis: | *Introdução aos dispositivos lógicos programáveis: | ||

:* Conceito, tipos de PLDs | :* Conceito, tipos de PLDs | ||

| − | + | :* SPLD: | |

| − | + | ::*PAL (e.g. [[Media: PAL16.pdf| PAL16 da Texas Instruments (1984)]]) | |

| + | ::*PLA (e.g. [[Media: PLS100.pdf| PLS100 da Philips Semiconductors (1993)]]) | ||

| + | ::*GAL (e.g. [[Media: GAL16V8.pdf| GAL16V8 da Lattice (2004)]]) | ||

| + | :* CPLDs (e.g. [[Media: ATF2500C.pdf| ATF2500C da Atmel (2008)]], [https://br.mouser.com/c/ds/semiconductors/programmable-logic-ics/cpld-complex-programmable-logic-devices/ Complex Programmable Logic Devices Datasheets - Mouser]) | ||

| − | {{collapse top | Exemplos de PLDs}} | + | {{collapse top | expand=true| Exemplos de PLDs}} |

| − | {{fig|1.1| | + | {{fig|1.1|Exemplo de PAL| PedroniFig4_4a.png| 400 px | http://www.vhdl.us/book/Pedroni_VHDL_3E_Chapter4.pdf}} |

| − | {{fig|1.2| | + | {{fig|1.2|Exemplo de PLA| PedroniFig4_4b.png| 400 px | http://www.vhdl.us/book/Pedroni_VHDL_3E_Chapter4.pdf}} |

| − | {{fig|1. | + | {{fig|1.3|Macrobloco do PLD EP300 da ALTERA| ep310_macrocell.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} |

| − | {{fig|1. | + | {{fig|1.4|Macrocélula dos PLDs Clássicos EP600, EP900, EP1800 da ALTERA (1999)| Macrocell_EP900.png| 400 px | https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ds/archives/classic.pdf}} |

| − | {{fig|1.5| | + | {{fig|1.5|Architetura do PLD EP1800 da ALTERA| ep1800_block_diagram.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} |

| − | {{fig|1.6|Architetura do CPLD MAX 5000 da ALTERA| max_5000_architecture.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} | + | {{fig|1.6|Architetura do PLD EP1800 da ALTERA| ep1800_block_diagram2.jpg| 400 px | https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ds/archives/classic.pdf}} |

| + | |||

| + | {{fig|1.7|Pinagem e tipos de encapsulamento do PLD EP1800 da ALTERA| PackagePinOut_EP1810.png| 400 px | https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ds/archives/classic.pdf }} | ||

| + | |||

| + | {{fig|1.8|Architetura do CPLD MAX 5000 da ALTERA| max_5000_architecture.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | + | :* Ver preços em | |

| − | :* | + | ::*[https://www.arrow.com/ ARROW] |

| − | ::* [https://www. | + | ::*[https://www.digikey.com/ Digikey] |

| + | ::*[https://mouser.com Mouser Electronics] | ||

| + | ::*[https://www.newark.com/ Newark] | ||

:* Fabricantes de DLPs/FPGAs e familias de DLPs atuais. | :* Fabricantes de DLPs/FPGAs e familias de DLPs atuais. | ||

::*[https://www.altera.com/products/fpga/overview.html ALTERA/INTEL] - Stratix, Arria, Cyclone, Max | ::*[https://www.altera.com/products/fpga/overview.html ALTERA/INTEL] - Stratix, Arria, Cyclone, Max | ||

| − | ::*[https://www.xilinx.com/products/silicon-devices/fpga.html Xilinx] - Virtex, Kintex, Artix, Zynq (SoC) | + | ::*[https://www.xilinx.com/products/silicon-devices/fpga.html Xilinx/AMD] - Virtex, Kintex, Artix, Zynq (SoC) |

| − | ::*[ | + | ::*[https://www.microchip.com/en-us/products/fpgas-and-plds/fpgas Microchip] - Igloo, PolarFire |

::*[http://www.latticesemi.com/Products.aspx#_D5A173024E414501B36997F26E842A31 Lattice] - ECP, iCE, Mach | ::*[http://www.latticesemi.com/Products.aspx#_D5A173024E414501B36997F26E842A31 Lattice] - ECP, iCE, Mach | ||

| − | + | ;PARA O PRÓXIMO ENCONTRO: | |

| − | + | *[https://www.intel.com/content/www/us/en/products/details/fpga/platforms.html See why Microsoft chose Intel FPGAs to accelerate their next generation cloud infrastructure] | |

| − | + | *[https://www.youtube.com/watch?v=ecyyZ6zTLic Microsoft's Bing* Intelligent Search with Intel® FPGAs] | |

| − | + | ||

| − | + | ;Encontro 3 (1 ago): | |

| − | : | + | * [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 1 e 2 |

| − | |||

| − | |||

| − | * | + | ;PARA O PRÓXIMO ENCONTRO: |

| + | * Leia a assista a alguns dos vídeos sobre a historia e processo de produção dos chips. | ||

:*[https://www.semiwiki.com/forum/content/1535-brief-history-fabless-semiconductor-industry.html A Brief History of the Fabless Semiconductor Industry] | :*[https://www.semiwiki.com/forum/content/1535-brief-history-fabless-semiconductor-industry.html A Brief History of the Fabless Semiconductor Industry] | ||

:*[http://www.semiwiki.com/forum/content/1539-brief-history-tsmc.html Taiwan Semiconductor Manufacturing Corporation (TSMC)], [http://www.globalfoundries.com/ GLOBALFOUNDRIES] | :*[http://www.semiwiki.com/forum/content/1539-brief-history-tsmc.html Taiwan Semiconductor Manufacturing Corporation (TSMC)], [http://www.globalfoundries.com/ GLOBALFOUNDRIES] | ||

:*[https://www.linkedin.com/pulse/free-copy-fabless-transformation-semiconductor-industry-daniel-nenni-1 Fabless: The Transformation of the Semiconductor Industry, 2014] - Download free | :*[https://www.linkedin.com/pulse/free-copy-fabless-transformation-semiconductor-industry-daniel-nenni-1 Fabless: The Transformation of the Semiconductor Industry, 2014] - Download free | ||

| − | |||

:*[https://www.youtube.com/watch?v=W3rfVpkNquA Produção do FinFET], [https://www.youtube.com/watch?v=d9SWNLZvA8g] | :*[https://www.youtube.com/watch?v=W3rfVpkNquA Produção do FinFET], [https://www.youtube.com/watch?v=d9SWNLZvA8g] | ||

| − | :*[https://en.wikipedia.org/wiki/ | + | :*[https://en.wikipedia.org/wiki/3_nm_process 3 nm process], [https://en.wikipedia.org/wiki/Multigate_device multi-gate MOSFET] |

:*[https://www.youtube.com/watch?v=UvluuAIiA50 GLOBALFOUNDRIES Sand to Silicon], [https://www.youtube.com/watch?v=F2KcZGwntgg How Microchips are made] - Processo de fabricação de um chip | :*[https://www.youtube.com/watch?v=UvluuAIiA50 GLOBALFOUNDRIES Sand to Silicon], [https://www.youtube.com/watch?v=F2KcZGwntgg How Microchips are made] - Processo de fabricação de um chip | ||

:*[https://en.wikipedia.org/wiki/Foundry_model Foundries], [https://en.wikipedia.org/wiki/List_of_semiconductor_fabrication_plants List of semiconductor fabrication plants] | :*[https://en.wikipedia.org/wiki/Foundry_model Foundries], [https://en.wikipedia.org/wiki/List_of_semiconductor_fabrication_plants List of semiconductor fabrication plants] | ||

| + | :*[https://www.youtube.com/watch?v=GU87SH5e0eI A dependência do mundo com a TMSC] | ||

| − | + | ;Encontro 4 (4 ago): | |

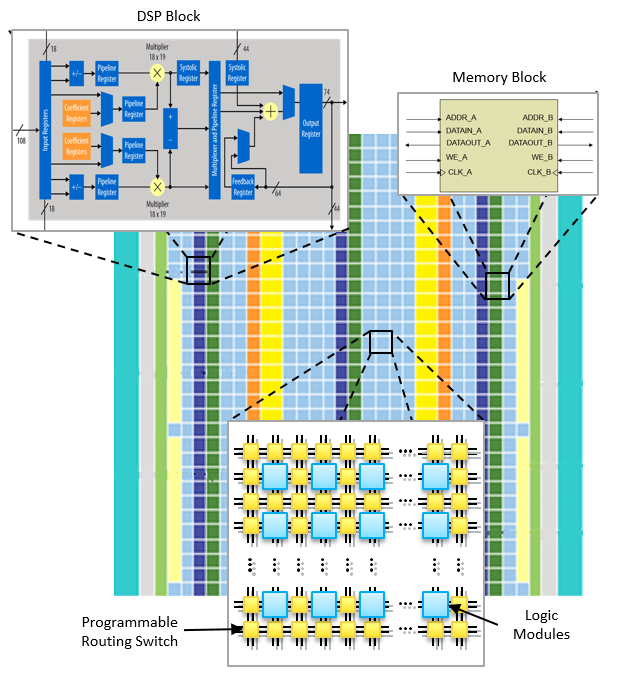

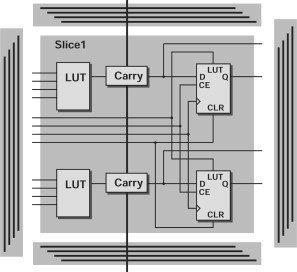

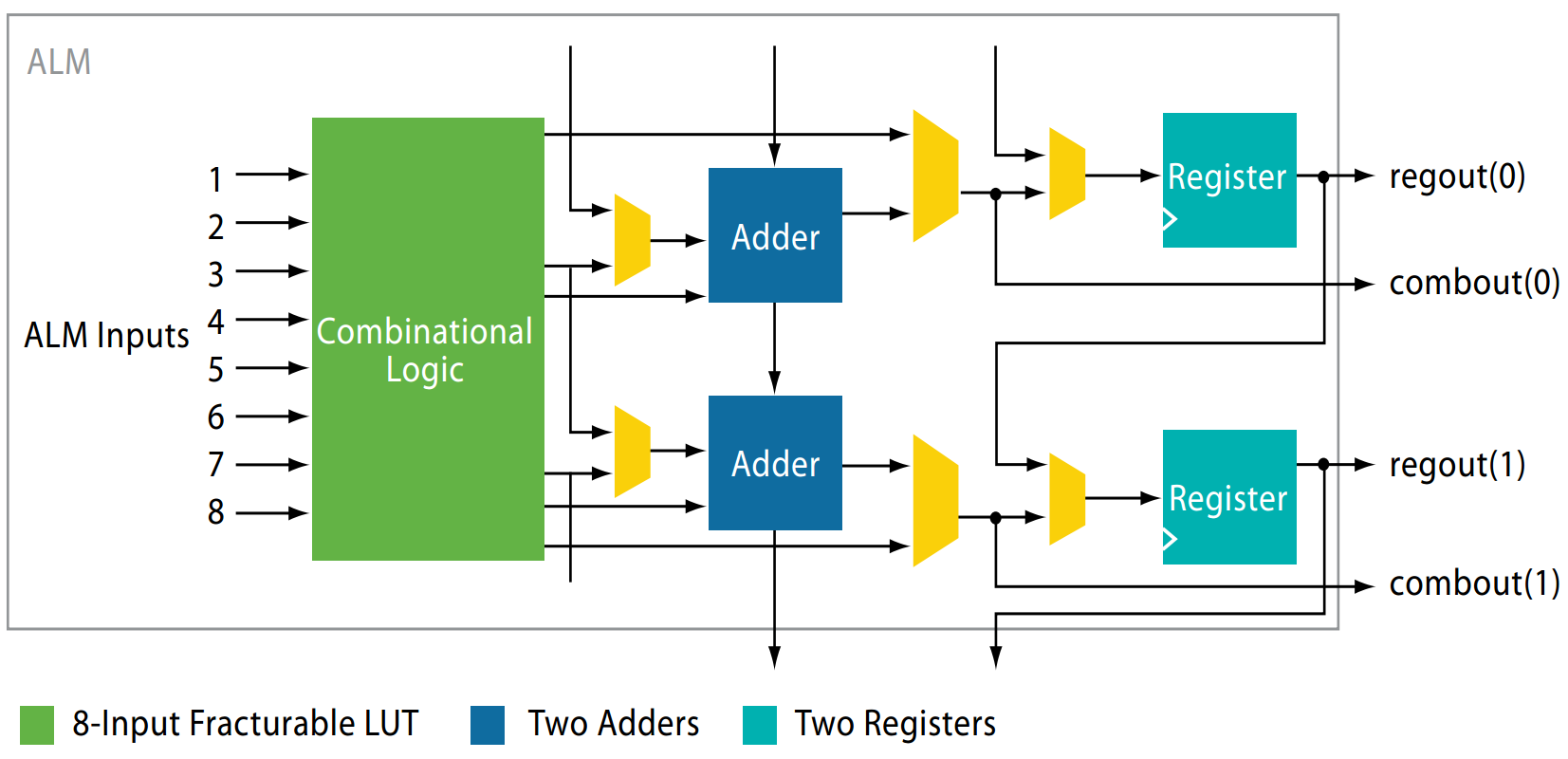

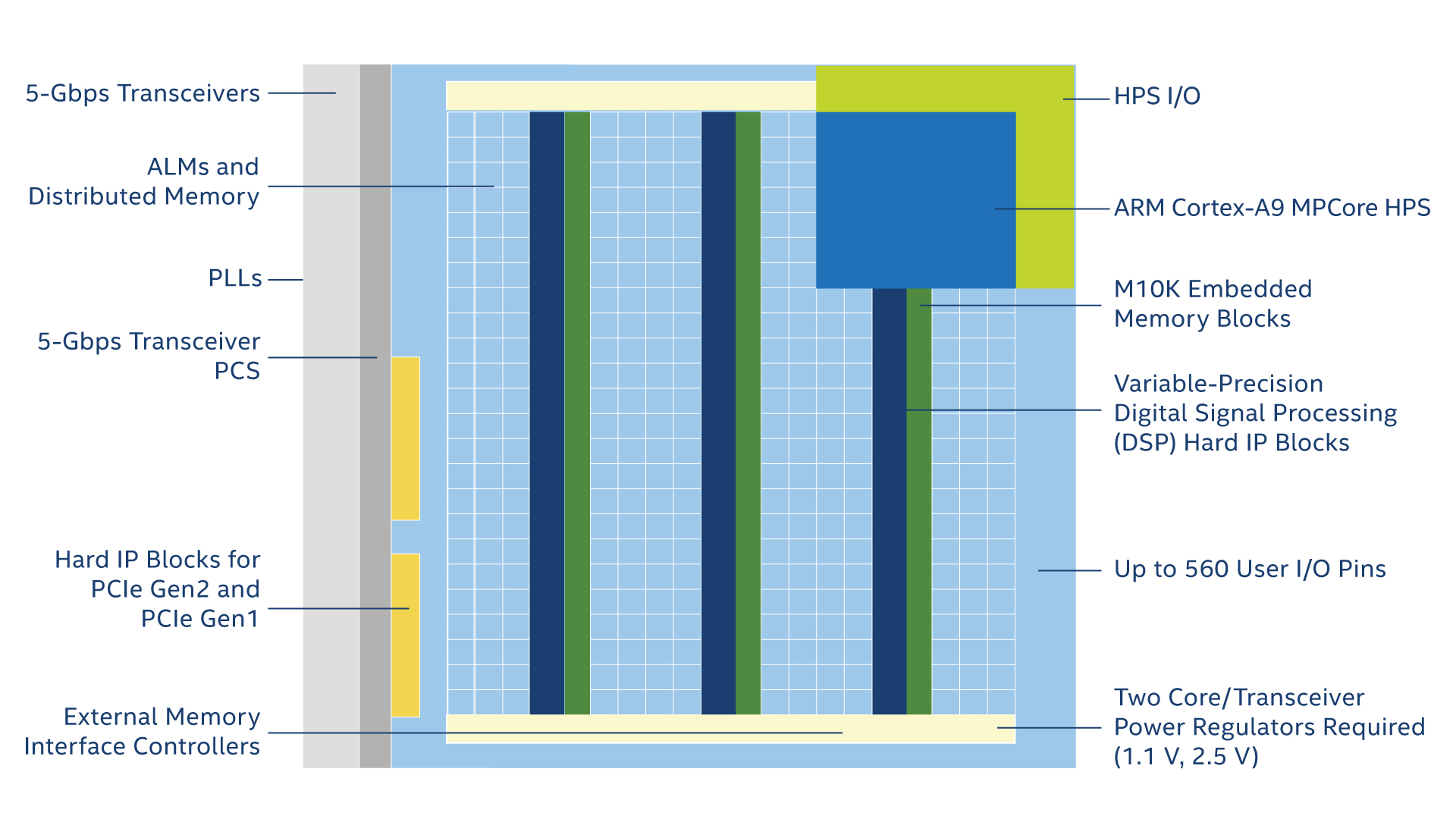

| − | + | * Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, LUT, Flip_flop D, RAM, DSP, Clock, PLL, DLL, I/O | |

| − | * | + | {{collapse top | expand=true |Exemplos de FPGA}} |

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | {{fig|1.7|Arquitetura de um FPGA | Architecture_FPGAs.png| 600 px | https://www.intel.com/content/www/us/en/docs/programmable/683176/18-1/fpga-overview-opencl-standard.html}} | |

| − | + | {{fig|1.8|Diagrama simplificado da CLB de um FPGA ARM/Xilinx | CLB_FPGAs.jpg| 600 px | https://www.sciencedirect.com/science/article/pii/B9780750678667500032#f14}} | |

| − | {{ | ||

| − | {{fig|1. | + | {{fig|1.9|Diagrama simplificado da ALM de um FPGA Intel/Altera | ALM_LUT_FPGAs.png| 600 px | https://www.intel.com/content/www/us/en/content-details/771003/fpga-architecture-8-input-lut-legacy-white-paper.html}} |

| − | {{fig|1. | + | {{fig|1.10|Arquitetura do Cyclone® V Intel/Altera | CycloneV_FPGAs.jpg| 600 px | https://www.intel.com.br/content/www/br/pt/products/details/fpga/cyclone/v/article.html}} |

| − | |||

| − | |||

| − | |||

| − | |||

{{fig|1.11|Leiaute de um FPGA Xilinx genérico | Leiaute2_FPGAs.jpg| 600 px | https://www.sciencedirect.com/science/article/pii/B9780750678667500032 }} | {{fig|1.11|Leiaute de um FPGA Xilinx genérico | Leiaute2_FPGAs.jpg| 600 px | https://www.sciencedirect.com/science/article/pii/B9780750678667500032 }} | ||

| Linha 90: | Linha 92: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | |||

| − | * | + | ;PARA O PRÓXIMO ENCONTRO: |

| + | * Leia a assista a alguns dos vídeos sobre FPGAs. | ||

| + | :*[https://youtu.be/v2ZloNgU-EE Tecnologia FPGA Intel - Macnica DHW] | ||

| + | :*[https://www.sciencedirect.com/science/article/pii/B9780750678667500032 Chapter 2 - FPGA Fundamentals], R.C. Cofer, Benjamin F. Harding, Science Direct | ||

| + | :*[https://edisciplinas.usp.br/pluginfile.php/530826/mod_resource/content/1/DISPOSITIVOS%20L%C3%93GICOS%20PROGRAM%C3%81VEIS_2014.pdf Dispositivos Lógicos Programáveis], L.M.R. Codá, USP | ||

| − | : | + | ;CURIOSIDADES: |

| − | |||

| − | + | * Quais são os tipos de [[Níveis lógicos]] utilizados. | |

| − | + | * [[Como as portas lógicas são implementadas com transistores CMOS]] | |

| − | + | *[https://www.computerhistory.org/siliconengine/timeline/ The Silicon Engine Timeline], Computer History Museum (CHM) | |

| − | : | + | *[https://www10.edacafe.com/book/ASIC/CH04/CH04.1.php The Antifuse], [https://www.youtube.com/watch?v=7qa1dsCpMMo EEPROM], [https://www.youtube.com/watch?v=ELl3abwYQ90&list=PL9B4edd-p2agcmJl2EscTdLudLv58uXHt&index=1 What Is Flash Memory] |

| − | + | *[https://numato.com/blog/differences-between-fpga-and-asics/ FPGA Vs ASIC: Differences Between Them And Which One To Use?] | |

| − | |||

| − | * [https:// | ||

| + | ;Encontro 5 (8 ago): | ||

| + | * [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 3 e 4 | ||

| + | *Exemplo de um Circuito para cálculo da '''distância de Hamming'''. | ||

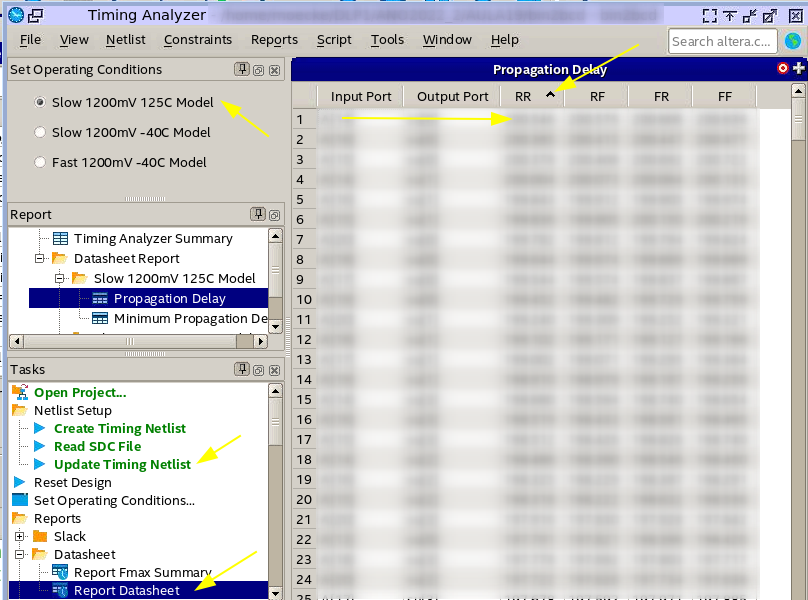

| + | :*[[Medição de tempos de propagação em circuitos combinacionais]] | ||

| + | :* Os alunos devem utilizar a nuvem para realizar a atividade. | ||

| + | :*[https://wiki.sj.ifsc.edu.br/index.php/Medi%C3%A7%C3%A3o_de_tempos_de_propaga%C3%A7%C3%A3o_em_circuitos_combinacionais#Inserindo_restri.C3.A7.C3.B5es_de_atraso_m.C3.A1ximo_para_o_compilador Inserindo restrições de atraso máximo para o compilador] | ||

| + | :* Objetivos: Copiar e colar o código no Quartus; diferença entre analise e síntese e compilação; observar o RTL (usar UNGROUP); simulação funcional e simulação temporal; observar os atrasos de propagação na simulação temporal. | ||

| + | ;PARA CONHECER MAIS: | ||

| + | * Ler pag. 413 a 431 de <ref name="PEDRONI2010a"> PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657 </ref> ou pag. 495 a 501 de de <ref name="PEDRONI2010b"> PEDRONI, Volnei A. '''Circuit Design and Simulation with VHDL'''; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 </ref>. | ||

| + | * [https://en.wikipedia.org/wiki/Field-programmable_gate_array#History FPGA History] | ||

| + | * [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Design_and_programming FPGA Design and programming] | ||

| + | * [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Basic_process_technology_types FPGA Basic process technology types] | ||

| + | * [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Major_manufacturers FPGA Major manufacturers] | ||

| + | * Assistir [https://www.coursera.org/lecture/intro-fpga-design-embedded-systems/1-many-types-of-fpgas-EWo0n Many types of FPGAs] Coursera | ||

| + | * O que é um Schmitt trigger? | ||

| + | :*[https://youtu.be/d-7Oyd8o8hE?t=93 Um pouco de lab] - lab até o minuto 5:20, depois um exemplo com AMPOP | ||

| + | :*[https://howtomechatronics.com/how-it-works/electrical-engineering/schmitt-trigger/ como funciona] | ||

| + | * O que é a JTAG? | ||

| + | :*[https://www.corelis.com/educationdownload/JTAG-Tutorial.pdf Como funciona para testes e programação] - In-System-Programming pag.7 | ||

;Notícias recentes do mundo dos DLPs: | ;Notícias recentes do mundo dos DLPs: | ||

| − | |||

*[https://newsroom.intel.com/press-kits/intel-acquisition-of-altera/#:~:text=Intel%20and%20Altera%20announced%20on,transaction%20closed%20December%2028%2C%202015. Intel Acquisiton of Altera] | *[https://newsroom.intel.com/press-kits/intel-acquisition-of-altera/#:~:text=Intel%20and%20Altera%20announced%20on,transaction%20closed%20December%2028%2C%202015. Intel Acquisiton of Altera] | ||

<i> | <i> | ||

| Linha 123: | Linha 143: | ||

</i> | </i> | ||

| − | <!-- | + | <!-- |

| − | * [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo | + | |

| + | ;Encontro 6 (28 fev.): | ||

| + | * [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 3 | ||

*Exemplo de um Circuito para cálculo da '''distância de Hamming'''. | *Exemplo de um Circuito para cálculo da '''distância de Hamming'''. | ||

:*[[Medição de tempos de propagação em circuitos combinacionais]] | :*[[Medição de tempos de propagação em circuitos combinacionais]] | ||

| − | |||

| − | |||

:* Os alunos devem utilizar a nuvem para realizar a atividade. | :* Os alunos devem utilizar a nuvem para realizar a atividade. | ||

:* O professor estará disponível através do chat da UC e pelo link de meet disponibilizado no chat.[https://wiki.sj.ifsc.edu.br/index.php/Medi%C3%A7%C3%A3o_de_tempos_de_propaga%C3%A7%C3%A3o_em_circuitos_combinacionais#Inserindo_restri.C3.A7.C3.B5es_de_atraso_m.C3.A1ximo_para_o_compilador Inserindo restrições de atraso máximo para o compilador] | :* O professor estará disponível através do chat da UC e pelo link de meet disponibilizado no chat.[https://wiki.sj.ifsc.edu.br/index.php/Medi%C3%A7%C3%A3o_de_tempos_de_propaga%C3%A7%C3%A3o_em_circuitos_combinacionais#Inserindo_restri.C3.A7.C3.B5es_de_atraso_m.C3.A1ximo_para_o_compilador Inserindo restrições de atraso máximo para o compilador] | ||

| Linha 135: | Linha 155: | ||

--> | --> | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | + | ||

===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== | ===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== | ||

| − | * | + | * 10 ENCONTROS |

{{collapse top| expand = true | Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS}} | {{collapse top| expand = true | Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS}} | ||

| − | ;Encontro | + | ;Encontro 6 (11 ago.) |

* Introdução ao VHDL e ambiente EDA - QUARTUS | * Introdução ao VHDL e ambiente EDA - QUARTUS | ||

* Estrutura do código VHDL | * Estrutura do código VHDL | ||

| Linha 193: | Linha 213: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | ;Encontro | + | ;Encontro 8 (7 mar.) |

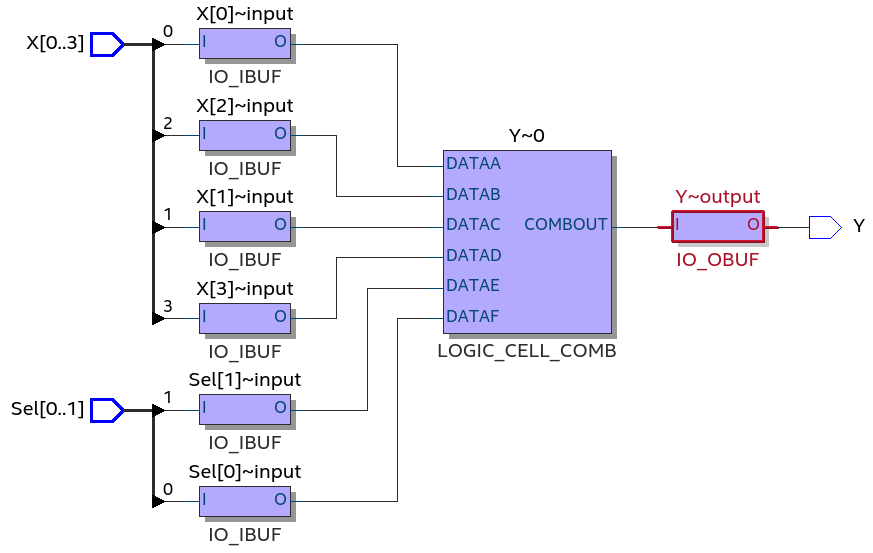

| − | Exemplo | + | * Exemplo - Descrição de um multiplexador de 4 entradas |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

entity mux_novo is | entity mux_novo is | ||

| Linha 263: | Linha 283: | ||

{{fig|2.3|Código RTL do mux 4x1 v_WITH_SELECT| RTL_mux4x1v3.png| 200 px |}} | {{fig|2.3|Código RTL do mux 4x1 v_WITH_SELECT| RTL_mux4x1v3.png| 200 px |}} | ||

:'''OBS''': [https://en.wikipedia.org/wiki/Register-transfer_level Register Transfer-Level] (RTL) é uma abstração na qual o circuito é descrito em termos de fluxo de sinais entre os registradores presentes no hardware e as operações combinacionais realizadas com esses dados. | :'''OBS''': [https://en.wikipedia.org/wiki/Register-transfer_level Register Transfer-Level] (RTL) é uma abstração na qual o circuito é descrito em termos de fluxo de sinais entre os registradores presentes no hardware e as operações combinacionais realizadas com esses dados. | ||

| − | |||

* Note a que ao verificar o Technology Map Viewer, nos 3 primeiros casos serão usados os mesmos elementos lógicos. | * Note a que ao verificar o Technology Map Viewer, nos 3 primeiros casos serão usados os mesmos elementos lógicos. | ||

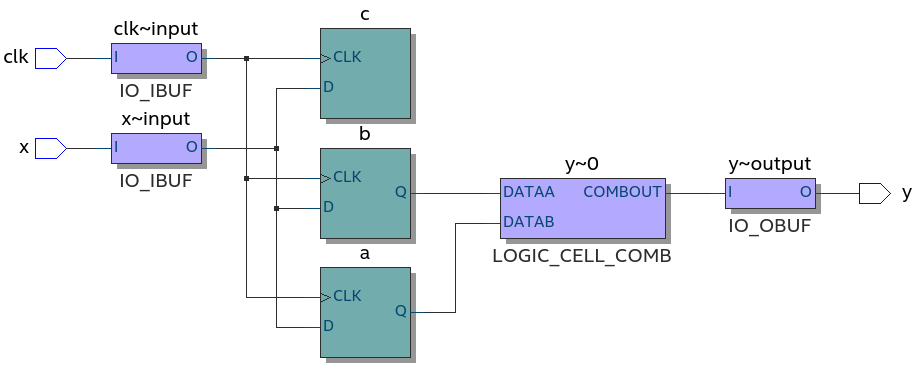

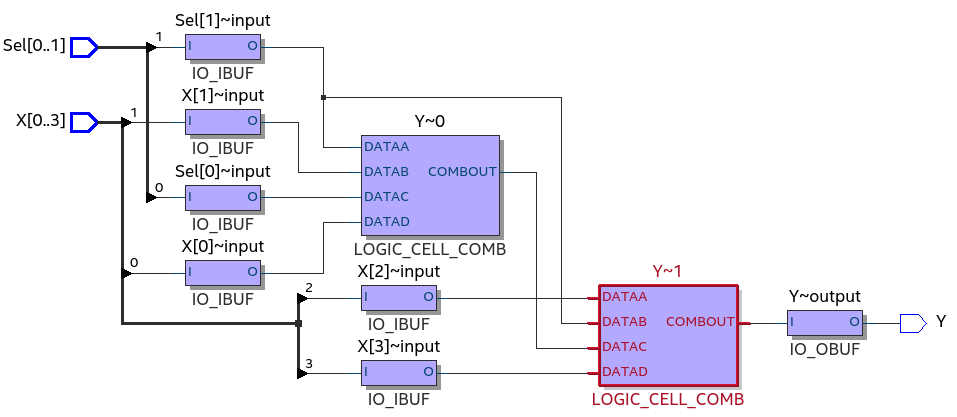

{{fig|2.4|Technology Map do mux 4x1 para a família Cyclone | TM_mux4x1.png| 400 px |}} | {{fig|2.4|Technology Map do mux 4x1 para a família Cyclone | TM_mux4x1.png| 400 px |}} | ||

| − | |||

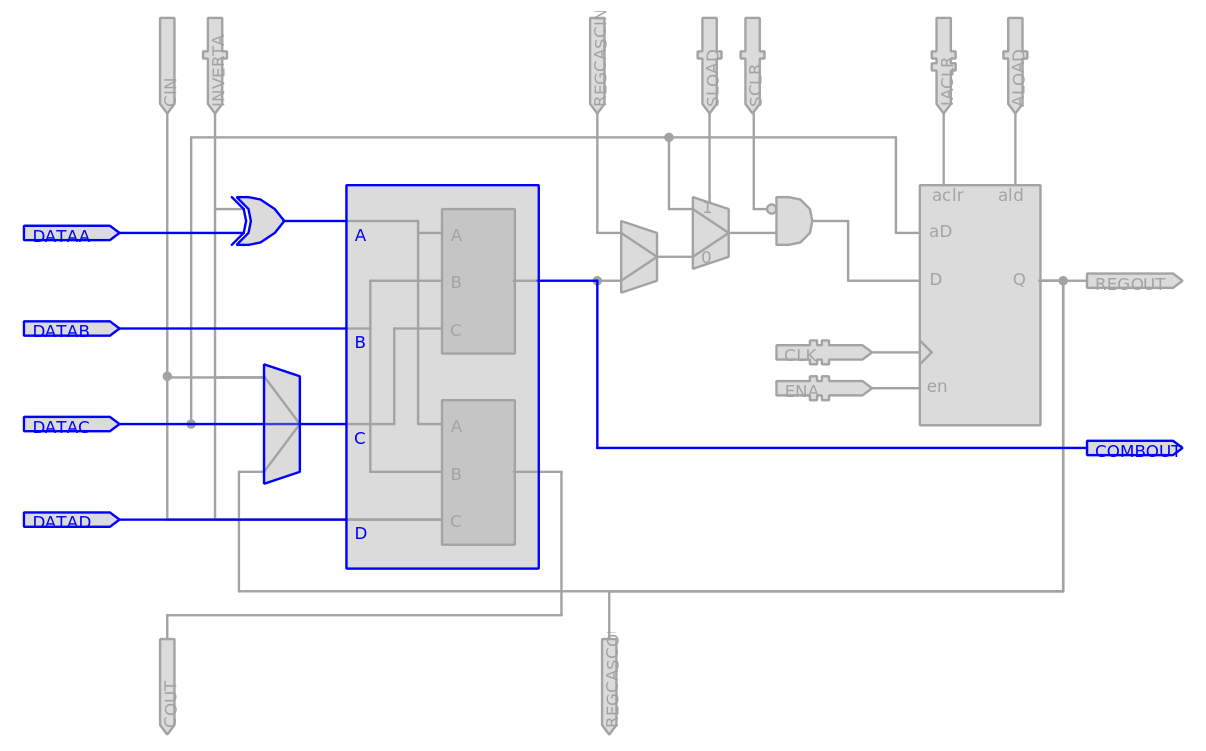

* Note que o elemento lógico acima possui uma LUT (LookUp Table) que basicamente implementa o circuito combinacional através de uma tabela de consulta (Tabela Verdade), a qual pode ser visualizada clicando com o botão Direito do Mouse e selecionando Properties, juntamente com Mapa de Karnaugh e seu Circuito Lógico representado por portas. Todas as representações são equivalentes. | * Note que o elemento lógico acima possui uma LUT (LookUp Table) que basicamente implementa o circuito combinacional através de uma tabela de consulta (Tabela Verdade), a qual pode ser visualizada clicando com o botão Direito do Mouse e selecionando Properties, juntamente com Mapa de Karnaugh e seu Circuito Lógico representado por portas. Todas as representações são equivalentes. | ||

| Linha 278: | Linha 296: | ||

{{fig|2.5|Technology Map do mux 4x1 para a família Stratix III | TM_mux4x1_S3.png| 400 px |}} | {{fig|2.5|Technology Map do mux 4x1 para a família Stratix III | TM_mux4x1_S3.png| 400 px |}} | ||

| − | |||

| − | |||

| + | ;Encontro 7 (15 ago.) | ||

| − | |||

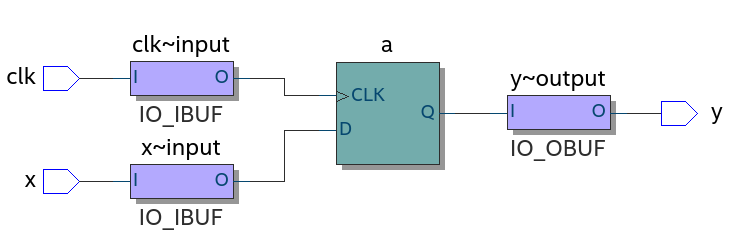

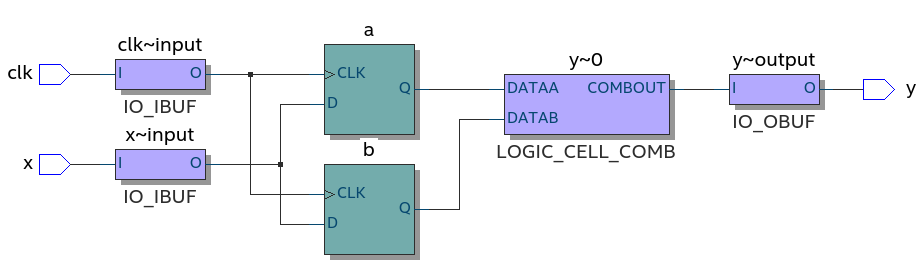

* Exemplo 2.2 (VHDL) - programação de um flip-flop | * Exemplo 2.2 (VHDL) - programação de um flip-flop | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 326: | Linha 342: | ||

:*[[Palavras reservadas do VHDL]] | :*[[Palavras reservadas do VHDL]] | ||

:*[http://g2384.github.io/work/VHDLformatter.html VHDL Beautifier, Formatter] - para formatar automaticamente um código VHDL. | :*[http://g2384.github.io/work/VHDLformatter.html VHDL Beautifier, Formatter] - para formatar automaticamente um código VHDL. | ||

| − | |||

| − | ;Encontro | + | ;Encontro 8 (18 ago.) |

| − | |||

| − | |||

| − | |||

| − | * | + | *[[Simulação Funcional usando o ModelSim]] |

| − | + | *Funcionamento do ModelSim: GUI, caracteristicas, testbench | |

| + | *Prática do Modelsim com bin2bcd | ||

| + | *Faça a simulação inserindo os valores 64, 99, 09, 00, 01, 109, 190. | ||

| + | *Perceba que com 7 bits na entrada, o número 190 não é representado corretamente, pois necessita de 8 bits. | ||

| + | *Perceba que a conversão para BCD do número 109 não é correta, pois o algoritmo implementado só preve a separação de dezena e unidade, e portanto não trata a centena. | ||

| − | + | ;Encontro 9 (22 ago.) | |

| − | + | * [[Simulação Funcional usando o ModelSim]] - completar passos 11 e 12. | |

| − | + | * Uso das bibliotecas no VHDL. | |

| − | + | :*Library '''std''' | |

| − | + | ::O Package '''standard''': é parte do VHDL desde a primeira versão (1987). Ela contem definição de tipos de dados (BIT, INTEGER, BOOLEAN, CHARACTER, etc.) e seus operadores logicos, aritméticos, de comparação e shift. | |

| − | + | ::O Package textio fornece os recurso para o tratamento de textos e arquivos, que podem ser utilizados na simulação. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | * Uso das bibliotecas no VHDL. | ||

| − | :*Library '''std''' | ||

| − | ::O Package '''standard''': é parte do VHDL desde a primeira versão (1987). Ela contem definição de tipos de dados (BIT, INTEGER, BOOLEAN, CHARACTER, etc.) e seus operadores logicos, aritméticos, de comparação e shift. | ||

| − | ::O Package textio fornece os recurso para o tratamento de textos e arquivos, que podem ser utilizados na simulação. | ||

*Como declarar e usar os pacotes da biblioteca '''std'''. | *Como declarar e usar os pacotes da biblioteca '''std'''. | ||

:: Note que esses pacotes são implicitamente carregados não precisando ser declarados. Ambos pacotes foram expandidos no VHDL 2008. | :: Note que esses pacotes são implicitamente carregados não precisando ser declarados. Ambos pacotes foram expandidos no VHDL 2008. | ||

| Linha 367: | Linha 366: | ||

use std.textio.all; | use std.textio.all; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | *Onde estão os arquivos dessa biblioteca na versão Quartus | + | *Onde estão os arquivos dessa biblioteca na versão Quartus instalada nos computadores do IFSC e na IFSC_CLOUD? |

| − | ls /opt/ | + | ls /opt/intelFPGA/20.1/quartus/libraries/vhdl/std |

:*Library '''ieee''' | :*Library '''ieee''' | ||

| Linha 397: | Linha 396: | ||

*Onde estão os arquivos dessa biblioteca na versão Quartus II versão 13.0sp1 instalada nos computadores do IFSC e na IFSC_CLOUD? | *Onde estão os arquivos dessa biblioteca na versão Quartus II versão 13.0sp1 instalada nos computadores do IFSC e na IFSC_CLOUD? | ||

::Os pacotes padrão: | ::Os pacotes padrão: | ||

| − | + | /opt/intelFPGA/20.1/quartus/libraries/vhdl/ieee | |

::Os pacotes não padrão: | ::Os pacotes não padrão: | ||

| − | + | /opt/intelFPGA/20.1/quartus/libraries/vhdl/mentor/arithmetic (Mentor Graphics) | |

| − | + | /opt/intelFPGA/20.1/quartus/libraries/vhdl/synopsys/ieee (Synopsys) | |

*Os arquivos dessa biblioteca do padrão (versão 2008) estão apenas disponíveis a partir do Quartus II versão 16.0 instalado na IFSC_CLOUD? | *Os arquivos dessa biblioteca do padrão (versão 2008) estão apenas disponíveis a partir do Quartus II versão 16.0 instalado na IFSC_CLOUD? | ||

ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008 | ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008 | ||

| − | + | * Exemplo 2.3 (VHDL e Modelsim) - programação de um circuito somador com registrador | |

| − | + | : Realizar a simulação funcional do circuito | |

| − | + | : Observar o "Technology Map" e o "RTL" do circuito | |

| − | |||

| − | |||

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

LIBRARY ieee; | LIBRARY ieee; | ||

| Linha 438: | Linha 434: | ||

END ARCHITECTURE; | END ARCHITECTURE; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | :: Acrescente saídas para o sinal '''sum''' e para o sinal '''comp''', de modo a poder observar estes sinais no simulador | + | :: Acrescente saídas para o sinal '''sum''' e para o sinal '''comp''', de modo a poder observar estes sinais no simulador Modelsim e realize nova simulação funcional. |

{{fig|2.10|Código RTL do Exemplo 2.3| RTL_Ex2_3_Pedronib.png| 400 px |}} | {{fig|2.10|Código RTL do Exemplo 2.3| RTL_Ex2_3_Pedronib.png| 400 px |}} | ||

| − | + | ;Encontro 10 (23 ago.) | |

| − | + | *Exemplo de um '''contador''' em VHDL. [https://en.wikipedia.org/wiki/VHDL#Example:_a_counter COUNTER] na página de VHDL da Wikipedia. | |

| − | + | <syntaxhighlight lang=vhdl> | |

| − | + | library IEEE; | |

| − | + | use IEEE.std_logic_1164.all; | |

| − | + | use IEEE.numeric_std.all; -- for the unsigned type | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | entity COUNTER is | |

| − | + | generic ( | |

| − | + | WIDTH : in natural := 32); | |

| − | + | port ( | |

| − | ; | + | RST : in std_logic; |

| − | + | CLK : in std_logic; | |

| − | + | LOAD : in std_logic; | |

| − | + | DATA : in std_logic_vector(WIDTH-1 downto 0); | |

| − | + | Q : out std_logic_vector(WIDTH-1 downto 0)); | |

| − | + | end entity COUNTER; | |

| − | + | ||

| + | architecture RTL of COUNTER is | ||

| + | |||

| + | begin | ||

| + | |||

| + | process(all) is | ||

| + | begin | ||

| + | if RST then | ||

| + | Q <= (others => '0'); | ||

| + | elsif rising_edge(CLK) then | ||

| + | if LOAD='1' then | ||

| + | Q <= DATA; | ||

| + | else | ||

| + | Q <= std_logic_vector(unsigned(Q) + 1); | ||

| + | end if; | ||

| + | end if; | ||

| + | end process; | ||

| − | + | end architecture RTL; | |

| − | |||

| − | |||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | |||

| − | |||

| − | :* | + | :*[[Restringir a frequencia máxima de clock no Quartus II]] |

| − | + | :* Objetivos: Copiar e colar o código no Quartus; diferença entre analise e síntese e compilação; observar o RTL (usar UNGROUP); simulação funcional e simulação temporal (considerando o tempo de propagação). Em função da dificuldade na realização da simulação temporal com o Modelsim, será utilizado excepcionalmente o QSIM para este fim. | |

| − | |||

| − | |||

| − | |||

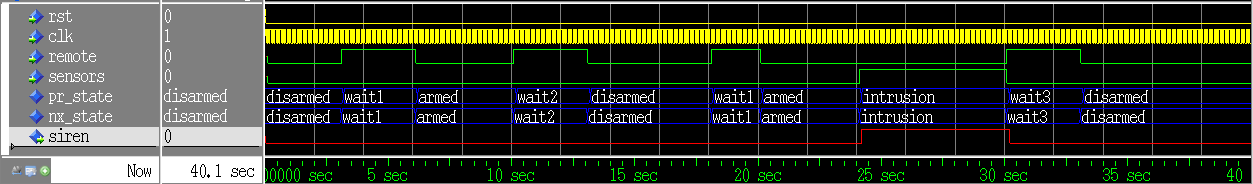

| − | + | *Ao realizar as simulações funcional e temporal do circuito '''Flip-Flop4''' ou do '''Counter''', será possível perceber que enquanto na simulação funcional, as mudanças ocorrem instantaneamente, na temporal, todos os tempos de propagação em vias e nos elementos lógicos são considerados. OBserve atentamente nas duas figuras a seguir as diferenças. | |

| − | |||

| − | |||

| − | |||

| − | + | {{fig|2.6|Simulação funcional com QSIM de 4 FF - 100ns| SIM1_4FF.png| 800 px |}} | |

| − | |||

| − | |||

| − | + | {{fig|2.7|Simulação Temporal com QSIM de 4 FF - 100ns| SIM2_4FF.png| 800 px |}} | |

| − | |||

| − | : | + | :Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existem atrasos variáveos de cerca de ~6ns nestas mudanças. |

| − | |||

| − | |||

| − | |||

| − | : | + | ''IMPORTANTE:'' Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possível verificar se o circuito atende as restrições de tempo. |

| − | |||

| − | |||

| − | * | + | * Para definir as restrições de tempo do clock por exemplo, pode ser adicionado um arquivo .sdc ao projeto definindo a frequência do clock esperada através da seguinte linha: |

| − | |||

| − | + | create_clock -name CLK50MHz -period 50MHz [get_ports {*}] | |

| − | |||

| − | + | *Ver pag. 3 a 24 de <ref name="PEDRONI2010b"> PEDRONI, Volnei A. '''Circuit Design and Simulation with VHDL'''; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 </ref> | |

| − | |||

| − | + | ;Encontro 11 e 12 (25 e 29 ago.) | |

| − | + | :* utilizar o código do '''contador''' em VHDL. [https://en.wikipedia.org/wiki/VHDL#Example:_a_counter COUNTER] na página de VHDL da Wikipedia. | |

| − | + | :* Definir a pinagem das chaves e leds conforme o kit a ser utilizado. | |

| − | + | :* Perceber o problema do repique das chaves. | |

| − | + | ::Ver [[Dicas de como eliminar o repique das chaves mecânicas]] | |

| + | :: Ler sobre o problema do repique das chaves mecânicas [https://my.eng.utah.edu/~cs5780/debouncing.pdf A Guide to Debouncing] | ||

| + | *Realizar [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE3_-_Programa.C3.A7.C3.A3o_do_kit_Mercurio_IV AE3 - Programação do kit Mercurio IV]. | ||

| + | *Medir o repique da chave e a solução com osciloscópio. | ||

| + | {{collapse bottom}} | ||

| − | + | ===Unidade 3 - Tipos de Dados e Operadores em VHDL=== | |

| + | * 10 ENCONTROS | ||

| + | {{collapse top | expand=true | Unidade 3 - Tipos de Dados e Operadores em VHDL}} | ||

| + | ;Encontro 13 (1 set.) | ||

| + | *Comentários no código (duplo traço --) | ||

| + | -- Isso eh uma linha de comentario | ||

| + | y <= a * b ; --o sinal y recebe o resultado da multiplicacao a x b | ||

| + | *Representação de caracteres, strings e números em VHDL. No circuito, os caracteres são representados através de bits de acordo com a [https://www.lookuptables.com/text/ascii-table tabela ASCII] básica (00 a 7F). A definição dessa tabela é feita o pacote '''[[standard.vhd]]''' da biblioteca '''std'''. | ||

| + | :*Caracteres (entre aspas simples) | ||

| + | caracter: 'A' 'x' '#' (com aspas simples) | ||

| + | :*Palavras (entre aspas duplas), é definida no VHDL como um vetor de caracteres. | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | type string is array (positive range <>) of character; | |

| − | + | </syntaxhighlight> | |

| + | |||

| + | string: "IFSC" "teste" "teste123" | ||

| − | + | :*Números em geral | |

| + | elemento ("bit") único: '0' '1' 'Z' (entre aspas simples) | ||

| + | vetor de elementos ("bits"): "0110" "101001Z" (entre aspas duplas) | ||

| + | vetor de 1 elemento ("bit"): "0" "1" (entre aspas duplas) | ||

| + | inteiros: 5 1101 1102 (sem aspas) | ||

| + | |||

| + | :*Números binários: | ||

| + | 0 -> '0' | ||

| + | 7 (em base 2) -> "0111" ou b"0111" ou B"0111" | ||

| + | 1023 (em base 2) -> "001111111111" ou b"1111111111" ou B"1111111111" | ||

| + | |||

| + | :*Números octais: | ||

| + | 44 (em base 8) -> 5*8^1 + 4*8^0 -> O"54" ou o"54" | ||

| + | 1023 (em base 8)-> 1*8^3 + 7*8^2 + 7*8^1 + 7*8^0 -> o"1777" 8#1777# | ||

| − | - | + | :*Números Hexadecimais: |

| − | + | 1023 (em base 16) -> 3*16^2 + 15*16^1 + 15*16^0 = X"3FF" ou x"3FF" 16#3FF# | |

| − | -- | + | :*Números decimais: |

| + | 1023 -> 1023 ou 1_023 | ||

| + | 1000 -> 1000 ou 1_000 ou 1E3 ou 10#1000# | ||

| + | ::Cuidado ao usar o "_" pois algumas ferramentas não o reconhecem. | ||

| − | + | :*Números em outras bases (de 2 a 16) | |

| − | + | 85 (em base 5) -> (3*5^2 + 2*5^1 + 0*5^0) -> 5#320# | |

| − | + | 1539 (em base 3) -> (2*3^2+0*3^1+1*3^0)*3^4 -> 3#201#E4 | |

| − | |||

| − | |||

| − | + | *Tipos de dados em VHDL. | |

| + | :*Objetos de VHDL: '''CONSTANT''', '''SIGNAL''', '''VARIABLE''', '''FILE'''. | ||

| + | O objeto '''CONSTANT''' pode ser declarado na parte declarativa da ENTITY, ARCHITECTURE, PACKAGE, PACKAGE_BODY, BLOCK, GENERATE, PROCESS, FUNCTION e PROCEDURE. | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | |||

| − | |||

| − | -- Variable sem valor default. | + | constant <constant_name> : <type> := <constant_value>; |

| − | variable <name> : <type>; | + | |

| + | -- Declarações comuns de constantes | ||

| + | |||

| + | constant GND : std_logic := '0'; | ||

| + | constant VCC : std_logic := '1'; | ||

| + | constant SSD_0 : std_logic_vector(0 to 6) := "1111110"; | ||

| + | constant MAX : natural := 44; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | O objeto '''SIGNAL''' pode ser declarado na parte declarativa da ENTITY, ARCHITECTURE, PACKAGE, BLOCK, GENERATE. Os sinais não podem ser declarados no código sequencial (PROCESS, FUNCTION e PROCEDURE), mas podem ser usados. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- Signal sem valor default | ||

| + | -- Para atribuir um valor a um signal use "<=" como operador. | ||

| + | |||

| + | signal <name> : <type>; | ||

| + | |||

| + | -- Signal com valor default | ||

| + | signal <name> : <type> := <default_value>; | ||

| + | |||

| + | -- Declarações comuns de signals | ||

| + | |||

| + | signal <name> : std_logic; | ||

| + | signal <name> : std_logic_vector(<msb_index> downto <lsb_index>); | ||

| + | signal <name> : integer; | ||

| + | signal <name> : integer range <low> to <high>; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | O objeto '''VARIABLE''' (variável) só pode ser declarada e usada dentro do escopo no código sequencial (PROCESS, FUNCTION e PROCEDURE). | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- Variables devem ser declarada em process ou subprogramas. | ||

| + | -- Para atribuir um valor a um variable use ":=" como operador. | ||

| + | |||

| + | -- Variable sem valor default. | ||

| + | variable <name> : <type>; | ||

-- Variable com valor default. | -- Variable com valor default. | ||

| Linha 603: | Linha 655: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| + | |||

| + | ;Encontro 14 (5 set.) | ||

A biblioteca [[Std logic 1164.vhd]] define os tipos STD_(U)LOGIG, STD_(U)LOGIG_VECTOR. | A biblioteca [[Std logic 1164.vhd]] define os tipos STD_(U)LOGIG, STD_(U)LOGIG_VECTOR. | ||

| Linha 650: | Linha 704: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | |||

| − | |||

A biblioteca [[Numeric std.vhd]] define os tipos UNSIGNED e SIGNED. | A biblioteca [[Numeric std.vhd]] define os tipos UNSIGNED e SIGNED. | ||

| Linha 735: | Linha 787: | ||

* Tipos de dados predefinidos: FIXED e FLOAT (apenas conhecer) | * Tipos de dados predefinidos: FIXED e FLOAT (apenas conhecer) | ||

| − | |||

| − | |||

| − | |||

* '''Desafio 1''' - Fazer um circuito que detecte se existe alguma vaga vazia em um lote de 9 vagas. A entrada '''x(n)''' está baixo '0' se a vaga está vazia, e alto '1' se tem carro. A saída '''y''' estará alta '1' sempre que houver uma ou mais vagas vazias, e em baixo '0' se não houver nenhuma vaga. | * '''Desafio 1''' - Fazer um circuito que detecte se existe alguma vaga vazia em um lote de 9 vagas. A entrada '''x(n)''' está baixo '0' se a vaga está vazia, e alto '1' se tem carro. A saída '''y''' estará alta '1' sempre que houver uma ou mais vagas vazias, e em baixo '0' se não houver nenhuma vaga. | ||

| Linha 748: | Linha 797: | ||

{{fig|3.2| Simulação do contador de vagas | cntvagas9.png | 800 px |}} | {{fig|3.2| Simulação do contador de vagas | cntvagas9.png | 800 px |}} | ||

| + | ;Encontro 15 (6 set.) | ||

| − | |||

| − | |||

| − | |||

| − | |||

* Exemplo 3.1 Buffer Tri-state | * Exemplo 3.1 Buffer Tri-state | ||

:*Ver como funciona em [http://bibl.ica.jku.at/dc/build/html/basiccircuits/basiccircuits.html#figure-1] | :*Ver como funciona em [http://bibl.ica.jku.at/dc/build/html/basiccircuits/basiccircuits.html#figure-1] | ||

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 781: | Linha 826: | ||

::* Analise se seria possível modificar as portas para o tipo '''bit'''. | ::* Analise se seria possível modificar as portas para o tipo '''bit'''. | ||

:: '''Importante''': O terceiro estado 'Z' só pode ser usado em saídas, e a sua realização nos FPGAs só ocorre nos nós de I/O. | :: '''Importante''': O terceiro estado 'Z' só pode ser usado em saídas, e a sua realização nos FPGAs só ocorre nos nós de I/O. | ||

| + | ;Curiosidade: Existem circuitos comerciais que implementam essa função three-state [https://www.ti.com/lit/ds/symlink/sn74lvc16244a-q1.pdf?ts=1681232207751&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FSN74LVC16244A-Q1 16 buffers], [https://www.ti.com/lit/ds/symlink/sn74lv244a-ep.pdf?ts=1681237777688&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FSN74LV244A-EP 8 buffers], [https://www.ti.com/lit/ds/symlink/sn74auc1g126.pdf?ts=1681222704977&ref_url=https%253A%252F%252Fwww.google.com%252F 1 buffer]. Porque não utilizar um CPLD ou FPGA em seu lugar? | ||

| + | ;Encontro 16 (12 set.) | ||

:* Exemplo 3.2 Circuito com Saida "don't care" | :* Exemplo 3.2 Circuito com Saida "don't care" | ||

| Linha 806: | Linha 853: | ||

* '''Desafio 3''' - Fazer um circuito que detecte se existe alguma vaga vazia em um lote de 9 vagas. A entrada '''x(n)''' está baixo '0' se a vaga está vazia, e alto '1' se tem carro. A saída '''y''' estará alta '1' sempre que houver uma ou mais vagas vazias, e em baixo '0' se não houver nenhuma vaga. Inspirado na descrição VHDL acima, tente resolver esse problema usando ''don't care''. | * '''Desafio 3''' - Fazer um circuito que detecte se existe alguma vaga vazia em um lote de 9 vagas. A entrada '''x(n)''' está baixo '0' se a vaga está vazia, e alto '1' se tem carro. A saída '''y''' estará alta '1' sempre que houver uma ou mais vagas vazias, e em baixo '0' se não houver nenhuma vaga. Inspirado na descrição VHDL acima, tente resolver esse problema usando ''don't care''. | ||

| − | |||

:'''Importante''': O ''don't care'' não funciona como se espera para uma entrada, por isso, use ''don't care'' apenas para saídas. | :'''Importante''': O ''don't care'' não funciona como se espera para uma entrada, por isso, use ''don't care'' apenas para saídas. | ||

| Linha 867: | Linha 913: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| + | |||

<center> | <center> | ||

{{Mensagem | {{Mensagem | ||

| Linha 877: | Linha 924: | ||

|background colour=#F5FFFA}} | |background colour=#F5FFFA}} | ||

</center> | </center> | ||

| + | |||

:: Ver pag. 39 a 54 de <ref name="PEDRONI2010b"/> | :: Ver pag. 39 a 54 de <ref name="PEDRONI2010b"/> | ||

| − | ;Encontro | + | ;Encontro 17 (15 set.) |

*Operadores em VHDL. | *Operadores em VHDL. | ||

:* Operadores predefinidos: Atribuição, Lógicos, Aritméticos, Comparação, Deslocamento, Concatenação, "Matching". | :* Operadores predefinidos: Atribuição, Lógicos, Aritméticos, Comparação, Deslocamento, Concatenação, "Matching". | ||

| Linha 960: | Linha 1 008: | ||

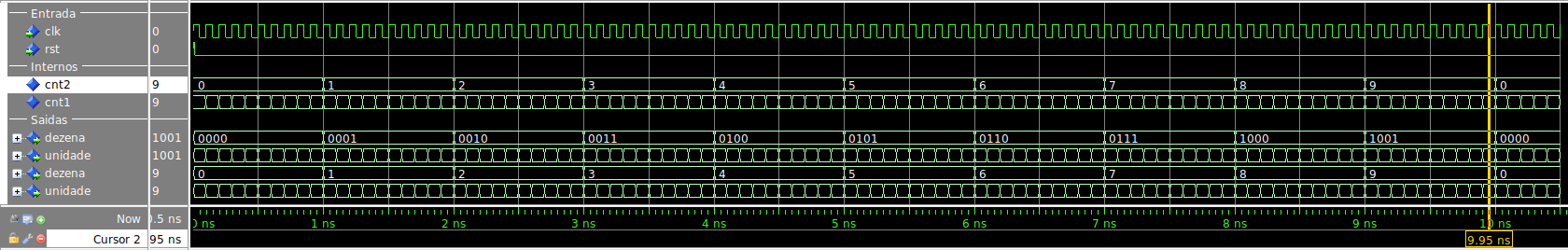

{{fig|3.3| Simulação do conversor de Binário para BCD com 2 digitos | bin2bcdDU_modelsim.png | 1000 px |}} | {{fig|3.3| Simulação do conversor de Binário para BCD com 2 digitos | bin2bcdDU_modelsim.png | 1000 px |}} | ||

| − | |||

| + | ;Encontro 18 (19 set.) | ||

;Operadores lógicos: | ;Operadores lógicos: | ||

São suportados nos tipos de dados: BIT, BIT_VECTOR, BOOLEAN, STD_(U)LOGIC, STD_(U)LOGIC_VECTOR, SIGNED e UNSIGNED. Com VHDL 2008 também suportado para BOOLEAN_VECTOR, UFIXED, SFIXED e FLOAT. | São suportados nos tipos de dados: BIT, BIT_VECTOR, BOOLEAN, STD_(U)LOGIC, STD_(U)LOGIC_VECTOR, SIGNED e UNSIGNED. Com VHDL 2008 também suportado para BOOLEAN_VECTOR, UFIXED, SFIXED e FLOAT. | ||

| Linha 982: | Linha 1 030: | ||

:*SRL (''Shift Right Logic'') - Deslocamento a direita lógico (preenchimento com '0's das posições a esquerda. | :*SRL (''Shift Right Logic'') - Deslocamento a direita lógico (preenchimento com '0's das posições a esquerda. | ||

:*SLA (''Shift Left Arithmetic'') - Deslocamento a esquerda aritmético (posições liberadas da direita mantém o bit lsb) | :*SLA (''Shift Left Arithmetic'') - Deslocamento a esquerda aritmético (posições liberadas da direita mantém o bit lsb) | ||

| − | :*SRA (''Shift Right Arithmetic'') - Deslocamento a | + | :*SRA (''Shift Right Arithmetic'') - Deslocamento a direita aritmético (posições liberadas da esquerda mantém o bit msb) |

:*ROL (''Rotate Left'') - Deslocamento circular a esquerda ( o bit que sai na esquerda é retornado na direita) | :*ROL (''Rotate Left'') - Deslocamento circular a esquerda ( o bit que sai na esquerda é retornado na direita) | ||

:*ROR (''Rotate Right'') - Deslocamento circular a direita ( o bit que sai na direita é retornado na esquerda) | :*ROR (''Rotate Right'') - Deslocamento circular a direita ( o bit que sai na direita é retornado na esquerda) | ||

| Linha 1 049: | Linha 1 097: | ||

</i> | </i> | ||

| + | ;Encontro 20 (20 set.) | ||

:* '''ATTRIBUTE keep''' [https://www.intel.com/content/www/us/en/programmable/quartushelp/current/index.htm#hdl/vhdl/vhdl_file_dir_keep.htm] | :* '''ATTRIBUTE keep''' [https://www.intel.com/content/www/us/en/programmable/quartushelp/current/index.htm#hdl/vhdl/vhdl_file_dir_keep.htm] | ||

O atributo de síntese KEEP, sinaliza ao processo de "Analysis & Synthesis" para manter intacto um determinado signal ou componente. | O atributo de síntese KEEP, sinaliza ao processo de "Analysis & Synthesis" para manter intacto um determinado signal ou componente. | ||

| Linha 1 118: | Linha 1 167: | ||

: Ver pag. 91 a 111 de <ref name="PEDRONI2010b"/> | : Ver pag. 91 a 111 de <ref name="PEDRONI2010b"/> | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | |||

| − | |||

* Atributos predefinidos são definidos no padrão [https://ieeexplore-ieee-org.ez130.periodicos.capes.gov.br/stamp/stamp.jsp?tp=&arnumber=8938196 1076-2019 - IEEE Standard for VHDL Language Reference Manual]. Esse documento pode ser acesso via o portal Periódicos Capes acesso CAFE. | * Atributos predefinidos são definidos no padrão [https://ieeexplore-ieee-org.ez130.periodicos.capes.gov.br/stamp/stamp.jsp?tp=&arnumber=8938196 1076-2019 - IEEE Standard for VHDL Language Reference Manual]. Esse documento pode ser acesso via o portal Periódicos Capes acesso CAFE. | ||

| Linha 1 158: | Linha 1 205: | ||

E'SIMPLE_NAME - The simple name, character literal, or operator symbol of the named entity | E'SIMPLE_NAME - The simple name, character literal, or operator symbol of the named entity | ||

| + | ;Encontro 21 (22 set.) | ||

* Atributos definidos pelo usuário; | * Atributos definidos pelo usuário; | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 1 164: | Linha 1 212: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | * Tipos definidos pelo usuário: | |

| − | + | :* Escalares (Inteiros e Enumerados) | |

| − | + | :* Tipos de Array 1D x 1D, 2D , 1D x 1D x 1D, 3D. Ver : [[Array em VHDL]] | |

| Linha 1 217: | Linha 1 265: | ||

('0', '1', '1', '1')); -- 7 | ('0', '1', '1', '1')); -- 7 | ||

begin | begin | ||

| − | + | -- slice1 <= table(row)(column); | |

| − | + | -- slice2 <= table(row)(1 to 2); | |

| − | + | -- slice3 <= table(row)); | |

| − | + | -- slice4 <= table(1 TO 3)(column); | |

| − | + | -- slice4 <= table(1)(column) & table(2)(column) & table(3)(column); | |

| − | + | -- gen : for i in 1 to 3 generate | |

| − | + | -- slice4(i) <= table(i)(column); | |

| − | + | -- end generate; | |

end architecture; | end architecture; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| Linha 1 235: | Linha 1 283: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| + | |||

| + | ;Encontro 22 (29 set.) | ||

{{collapse top| bg=lightyellow | Exemplo 3.7: Array de bits 2D }} | {{collapse top| bg=lightyellow | Exemplo 3.7: Array de bits 2D }} | ||

O código abaixo cria um '''array''' de bits e utiliza as entradas "row" e "column" para fazer a leitura dos dados em uma tabela declarada como '''constant'''. | O código abaixo cria um '''array''' de bits e utiliza as entradas "row" e "column" para fazer a leitura dos dados em uma tabela declarada como '''constant'''. | ||

| Linha 1 258: | Linha 1 308: | ||

--slice1 <= table(row, column); | --slice1 <= table(row, column); | ||

--slice2 <= table(row, 1 TO 2); | --slice2 <= table(row, 1 TO 2); | ||

| − | --slice3 <= table(row | + | --slice3 <= table(row); |

--slice4 <= table(1 TO 3, column); | --slice4 <= table(1 TO 3, column); | ||

| − | --slice4 <= table(1, column) & table(2, column) & | + | --slice4 <= table(1, column) & table(2, column) & table(3, column) |

--gen : for i in 1 to 3 generate | --gen : for i in 1 to 3 generate | ||

-- slice4(i) <= table(i, column); | -- slice4(i) <= table(i, column); | ||

| Linha 1 316: | Linha 1 366: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | |||

Como usar ARRAYs em portas?: | Como usar ARRAYs em portas?: | ||

* Declaração do TYPE em PACKAGE | * Declaração do TYPE em PACKAGE | ||

| Linha 1 466: | Linha 1 515: | ||

;Sobrecarga de operadores: | ;Sobrecarga de operadores: | ||

| + | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 1 490: | Linha 1 540: | ||

;Desafio 5: Completar o contador de vagos usando um numero inteiro (1 para vaga, 0 para ocupado) nas entradas no lugar dos bits. | ;Desafio 5: Completar o contador de vagos usando um numero inteiro (1 para vaga, 0 para ocupado) nas entradas no lugar dos bits. | ||

| − | ;Encontro | + | <!-- |

| − | + | ;Encontro 25 (25 abr.) | |

| − | ;Encontro | + | ;Encontro 26 (26 abr.) |

| − | |||

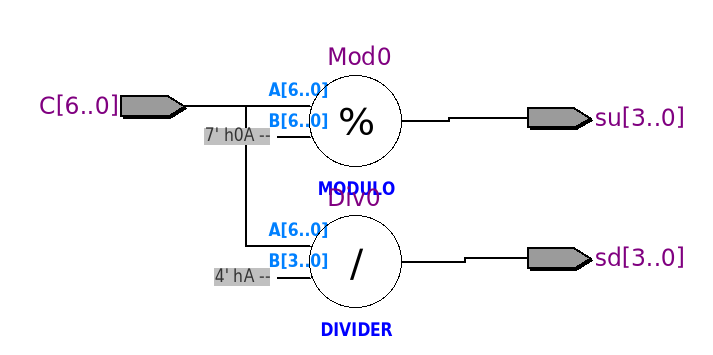

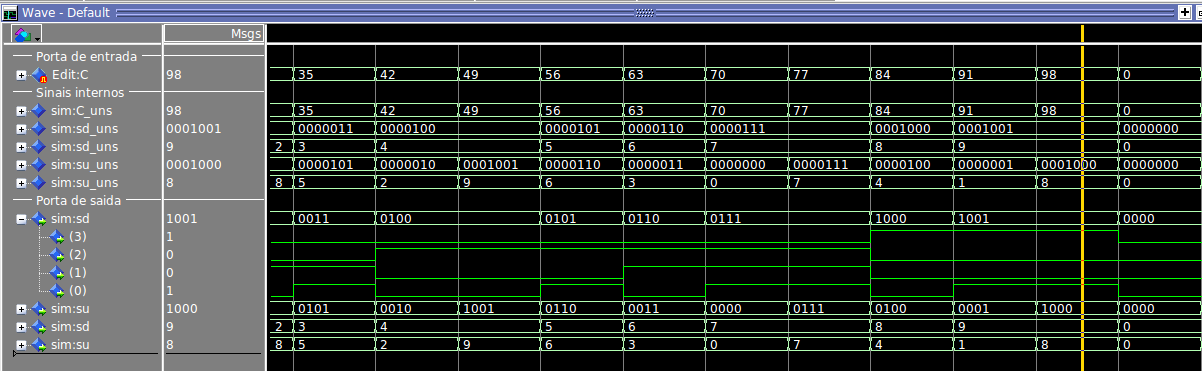

* A implementação de circuitos aritméticos com operadores deve seguir as seguintes recomendações: | * A implementação de circuitos aritméticos com operadores deve seguir as seguintes recomendações: | ||

:* Para o uso dos operadores o mais adequado é utilizar o padrão industrial '''STD_LOGIC_VECTOR'''. Internamente os valores das portas devem ser convertidos ou para valores '''INTEGER''' ou para '''UNSIGNED'''/'''SIGNED'''. para tal é necessário utilizar o pacote '''numeric_std''' da biblioteca '''ieee'''. | :* Para o uso dos operadores o mais adequado é utilizar o padrão industrial '''STD_LOGIC_VECTOR'''. Internamente os valores das portas devem ser convertidos ou para valores '''INTEGER''' ou para '''UNSIGNED'''/'''SIGNED'''. para tal é necessário utilizar o pacote '''numeric_std''' da biblioteca '''ieee'''. | ||

| Linha 1 611: | Linha 1 660: | ||

:*[[Uso do WaveDrom para gerar diagramas de tempo]] | :*[[Uso do WaveDrom para gerar diagramas de tempo]] | ||

| + | |||

| + | *[https://ieeexplore-ieee-org.ez130.periodicos.capes.gov.br/stamp/stamp.jsp?tp=&arnumber=8938196 IEEE Std 1076‐2019 IEEE Standard for VHDL Language: Reference Manual] - acesse via Periódicos Capes /Cafe | ||

--> | --> | ||

| − | |||

{{collapse bottom}} | {{collapse bottom}} | ||

===Unidade 4 - Código Concorrente=== | ===Unidade 4 - Código Concorrente=== | ||

| − | * | + | * 4 ENCONTROS |

{{collapse top| expand=true | Unidade 4 - Código Concorrente}} | {{collapse top| expand=true | Unidade 4 - Código Concorrente}} | ||

| − | + | ||

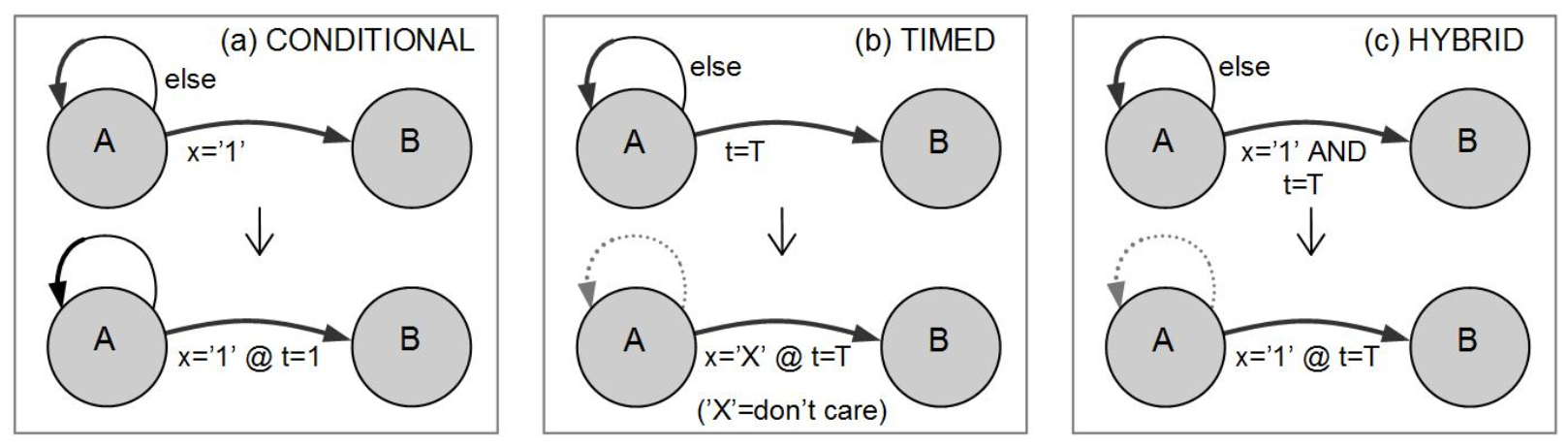

| − | ;Encontro | + | ;Encontro 24 (3 out.) |

*Código Concorrente. | *Código Concorrente. | ||

:* Uso de Operadores | :* Uso de Operadores | ||

| Linha 1 735: | Linha 1 785: | ||

::Ver pag. 121 a 127 de <ref name="PEDRONI2010b"/> | ::Ver pag. 121 a 127 de <ref name="PEDRONI2010b"/> | ||

| − | + | ;Encontro 25 (4 out.) | |

:* Uso da instrução FOR-GENERATE | :* Uso da instrução FOR-GENERATE | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 1 779: | Linha 1 829: | ||

architecture ifsc_v1 of vector_adder is | architecture ifsc_v1 of vector_adder is | ||

| − | signal soma_sig : | + | signal soma_sig : unsigned(3 downto 0); |

begin | begin | ||

| − | soma_sig <= | + | soma_sig <= unsigned(a(0)) + unsigned(a(1)) + unsigned(a(2)) + unsigned(a(3)); |

soma <= std_logic_vector(soma_sig); | soma <= std_logic_vector(soma_sig); | ||

end architecture; | end architecture; | ||

| Linha 1 789: | Linha 1 839: | ||

begin | begin | ||

| − | |||

end architecture; | end architecture; | ||

| Linha 1 805: | Linha 1 854: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | ;Encontro | + | ;Encontro 26 (6 out.) |

* Conhecer o [[Código Gray]] | * Conhecer o [[Código Gray]] | ||

| Linha 1 858: | Linha 1 907: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | ;Encontro | + | |

| + | ;Encontro 27 (10 out.) | ||

| + | |||

Outros exemplos a serem estudados: | Outros exemplos a serem estudados: | ||

* Porta AND e NAND generica (uso do FOR GENERATE) | * Porta AND e NAND generica (uso do FOR GENERATE) | ||

* Detector de paridade | * Detector de paridade | ||

| − | |||

| − | |||

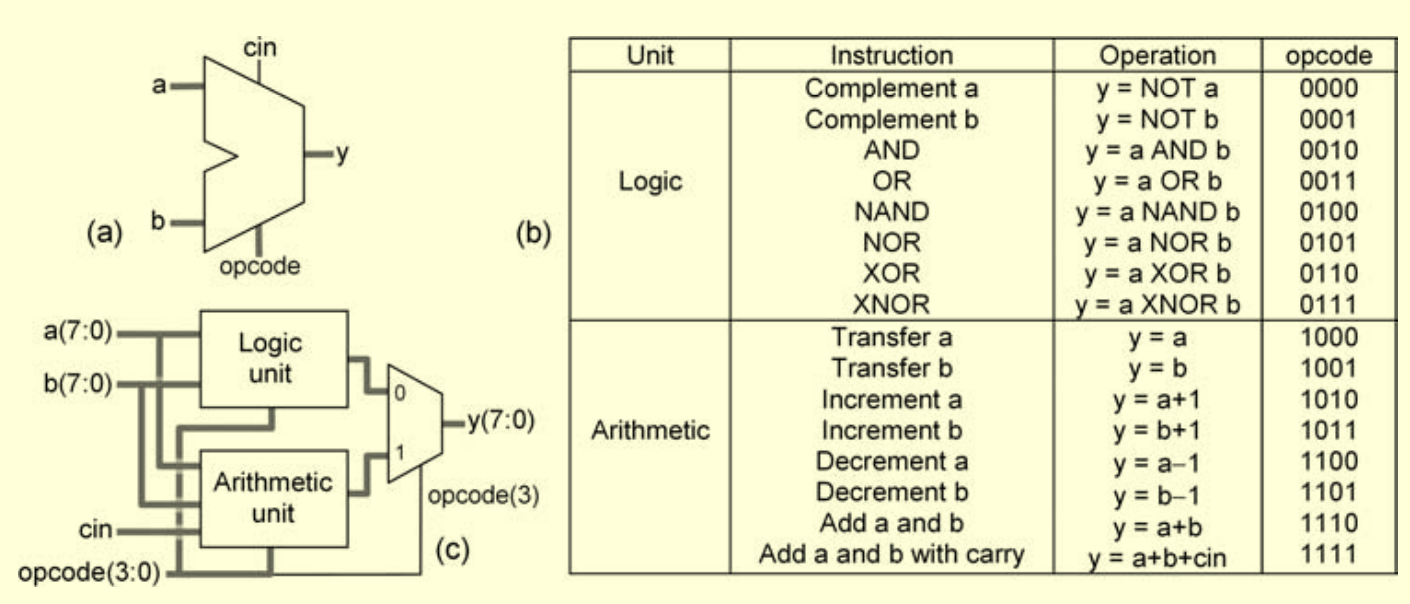

*Unidade de Aritmética UA). | *Unidade de Aritmética UA). | ||

:*Escreva o código VHDL que implemente a ALU mostrada no diagrama abaixo. Use operações do tipo SIGNED. As entradas '''a''' e '''b''' e saída '''y''' ter o número de bits definido através de GENERIC, e ser do tipo STD_LOGIC_VECTOR. Faça simulação funcional para os diferentes OPCODE. | :*Escreva o código VHDL que implemente a ALU mostrada no diagrama abaixo. Use operações do tipo SIGNED. As entradas '''a''' e '''b''' e saída '''y''' ter o número de bits definido através de GENERIC, e ser do tipo STD_LOGIC_VECTOR. Faça simulação funcional para os diferentes OPCODE. | ||

| Linha 1 892: | Linha 1 941: | ||

{{fig|3.9| Unidade de Lógica e Aritmética | Alu_pedroni.png | 600 px | pag. 127 <ref name="PEDRONI2010b"/>}} | {{fig|3.9| Unidade de Lógica e Aritmética | Alu_pedroni.png | 600 px | pag. 127 <ref name="PEDRONI2010b"/>}} | ||

| − | + | *Ver pag. 127 a 134 de <ref name="PEDRONI2010b"/> | |

| − | + | ;Encontro 28 (17 out.): Aula de exercícios | |

| − | + | * Lista de Exercícios: ver no Moodle [https://moodle.ifsc.edu.br/mod/wiki/view.php?id=56759 Estudos livres sem entrega de documentação (EL)] | |

| + | |||

{{collapse bottom}} | {{collapse bottom}} | ||

===Unidade 5 - Código Sequencial=== | ===Unidade 5 - Código Sequencial=== | ||

| − | * | + | * 7 ENCONTROS |

{{collapse top| expand=true| Unidade 5 - Código Sequencial}} | {{collapse top| expand=true| Unidade 5 - Código Sequencial}} | ||

| − | + | ;Encontro 29 (18 out.) | |

| − | ;Encontro | ||

*Código Sequencial. | *Código Sequencial. | ||

:*Diferenças entre código concorrente e sequencial <=> circuitos combinacional e sequencial | :*Diferenças entre código concorrente e sequencial <=> circuitos combinacional e sequencial | ||

| Linha 1 948: | Linha 1 997: | ||

end if; | end if; | ||

end process; | end process; | ||

| − | + | </syntaxhighlight> | |

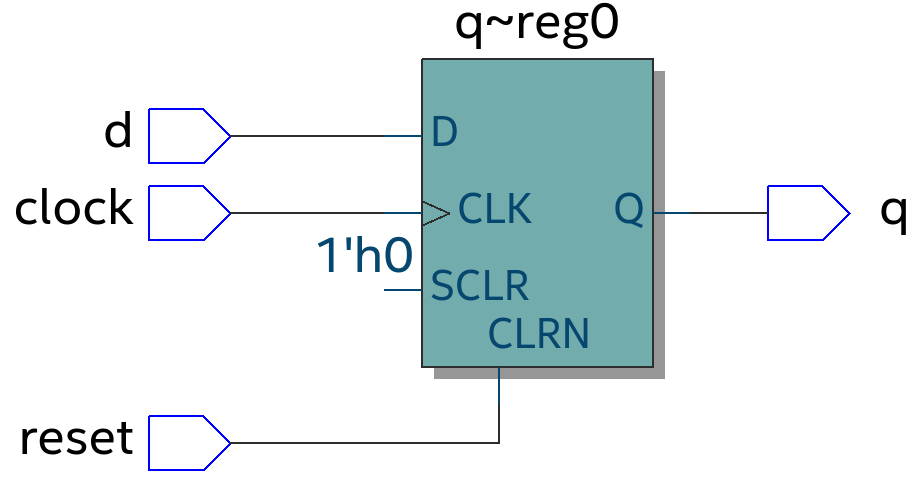

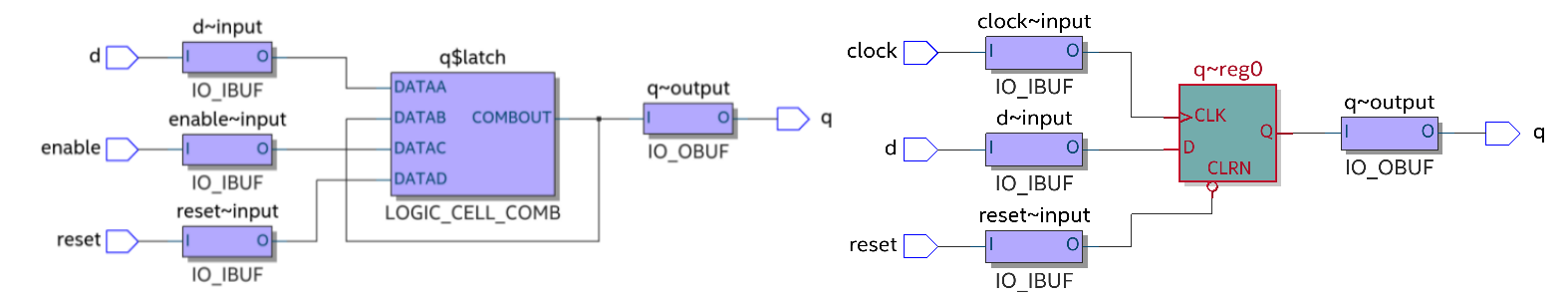

| + | {{fig|5.1|RTL de Flip-flop D de borda de subida, com reset assíncrono| FF_D_RST.png| 400 px | }} | ||

| + | <syntaxhighlight lang=vhdl> | ||

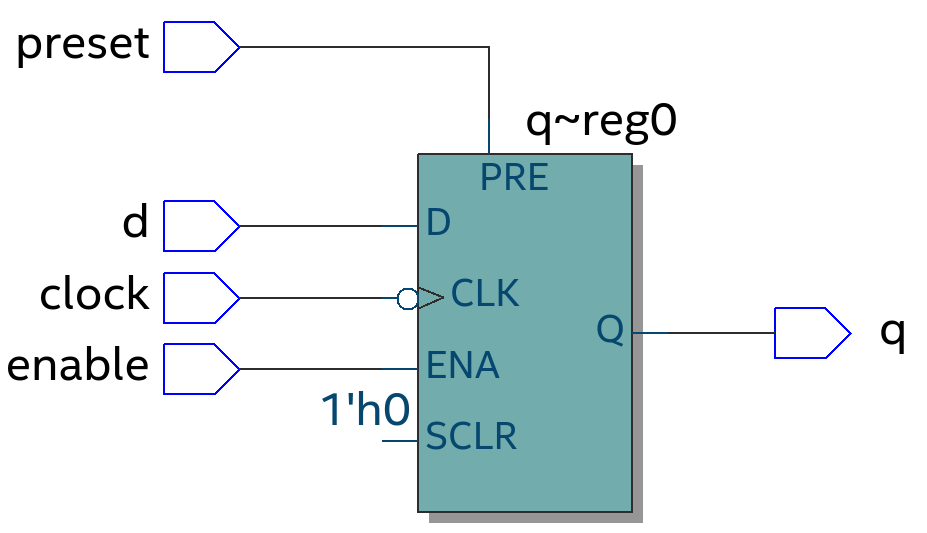

--Flip Flop tipo D com preset assincrono e sinal de enable, sensivel a borda de descida. | --Flip Flop tipo D com preset assincrono e sinal de enable, sensivel a borda de descida. | ||

process (clock, preset) | process (clock, preset) | ||

| Linha 1 961: | Linha 2 012: | ||

end process; | end process; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | {{fig|5.2|RTL de Flip-flop D de borda de descida, com preset assíncrono e enable| FF_D_PRST.png| 400 px | }} | |

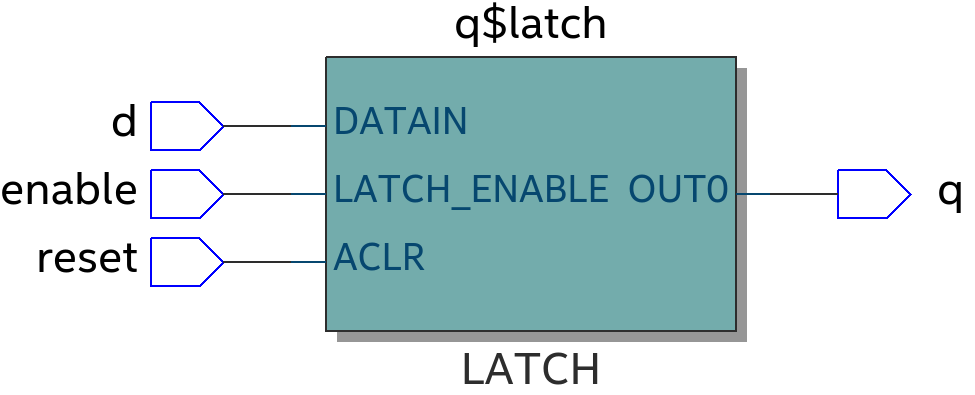

::* Comparar com Latch (sem clk'event). | ::* Comparar com Latch (sem clk'event). | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 1 974: | Linha 2 025: | ||

end process; | end process; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

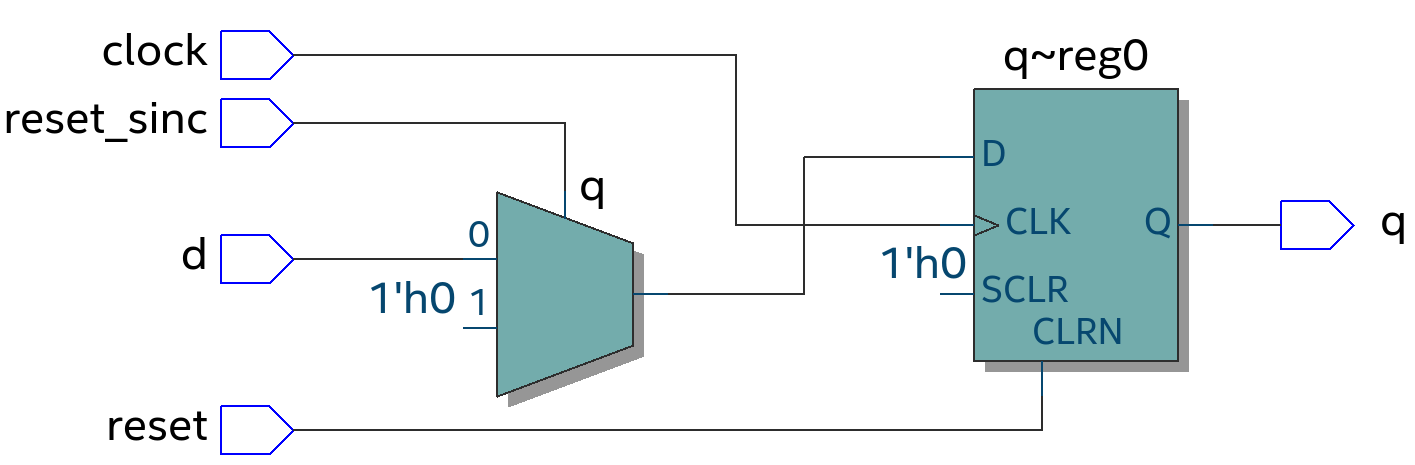

| + | {{fig|5.3|RTL de Latch D de com reset assíncrono e enable ativo alto| LATCH_D_RST.png| 400 px | }} | ||

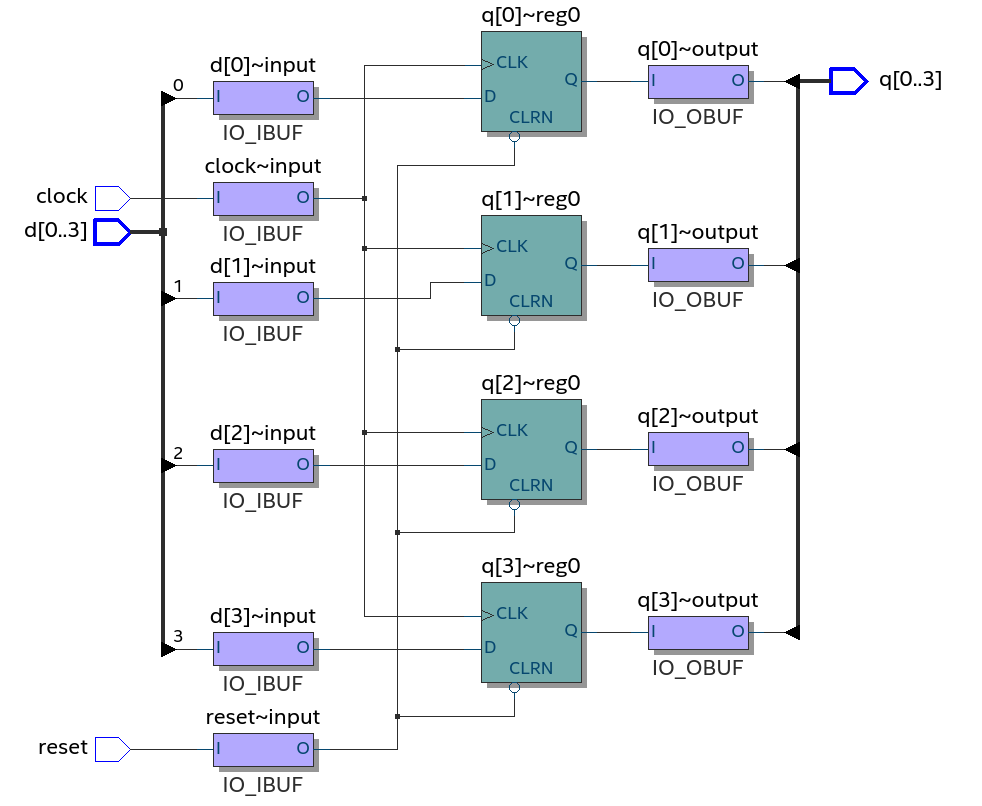

| + | * Na figura abaixo, note que o Latch é implementado utilizando a LUT do elemento lógico do FPGA, enquanto que o Flip-flop utiliza o componente já disponível neste elemento lógico. | ||

| + | *[[Evite os latches no projeto]] | ||

| + | |||

| + | {{fig|5.4|Comparação do ''Technology Map'' de um Latch_D (esquerda) com FF_D (direita)| FF_D_LATCH_D.png| 800 px | }} | ||

| + | |||

:*Ver pag. 151 a 156 de <ref name="PEDRONI2010b"/> | :*Ver pag. 151 a 156 de <ref name="PEDRONI2010b"/> | ||

| − | + | :*[[Especificando o valor de Power-Up do flip-flop D]] | |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

-- Flip Flop tipo D com reset síncrono sensível a borda de subida. | -- Flip Flop tipo D com reset síncrono sensível a borda de subida. | ||

| Linha 1 989: | Linha 2 046: | ||

end if; | end if; | ||

end process; | end process; | ||

| + | </syntaxhighlight> | ||

| + | {{fig|5.5|RTL do Flip-flop D com reset assíncrono e reset síncrono| FF_D_RST_SINC_ASINC.png| 400 px | }} | ||

| + | *[[Como evitar o uso da lógica combinacional no reset síncrono]] | ||

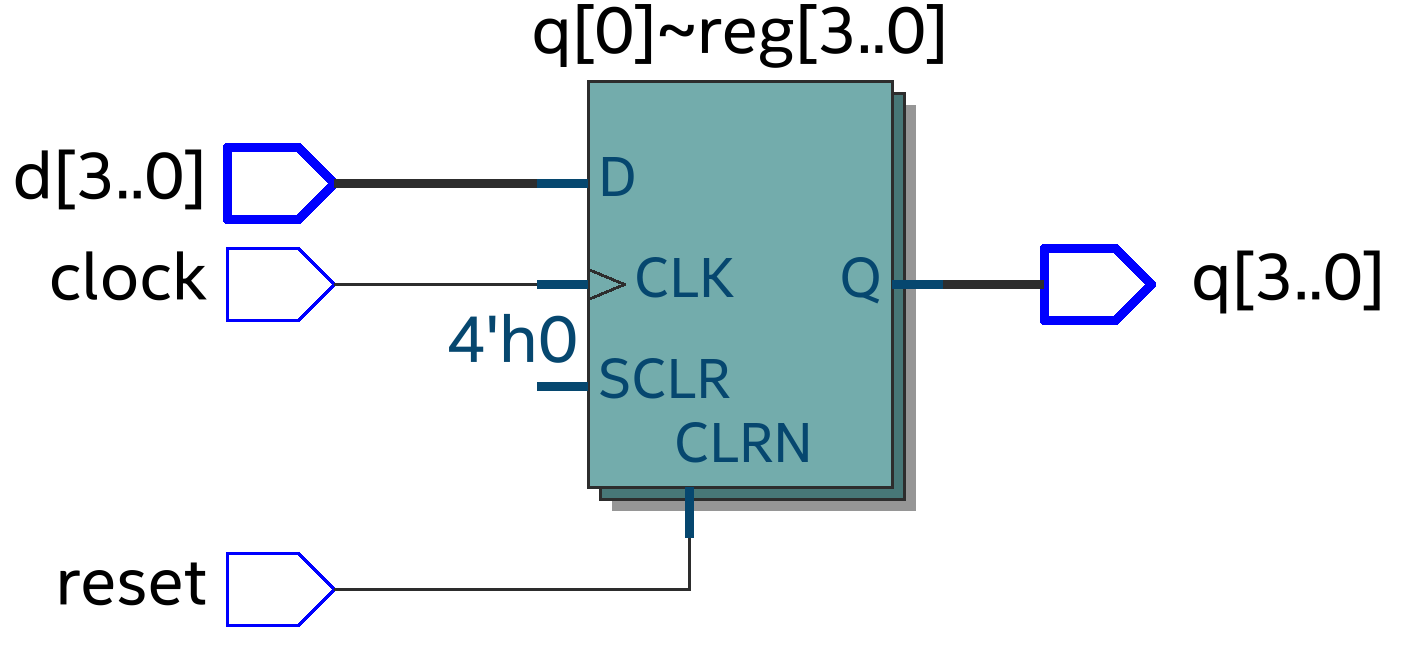

| − | + | *Exercício: Implemente um registrador com N FF_D no lugar de um único FF_D. | |

| − | * | + | {{fig|5.6|RTL do Registrador (de 4 bits) com reset assíncrono| REG_RST.png| 400 px | }} |

| + | {{fig|5.7|Techonogy Map do Registrador (de 4 bits) com reset assíncrono| TM_REG_RST.png| 400 px | }} | ||

| + | * Faça a simulação funcional do DFFs e do Latch | ||

| − | |||

| − | |||

| + | ;Encontro 21 (20 out.) | ||

* Contador crescente 0-N (baseado no Ex.6.2), com N = 2^Mbits-1 (1 3 7 15) | * Contador crescente 0-N (baseado no Ex.6.2), com N = 2^Mbits-1 (1 3 7 15) | ||

:* Com ''overflow'' no valor máximo | :* Com ''overflow'' no valor máximo | ||

* Contador crescente 0-N (baseado no Ex.6.2), com N =/= 2^Mbits (5, 10) | * Contador crescente 0-N (baseado no Ex.6.2), com N =/= 2^Mbits (5, 10) | ||

| − | |||

:* Com ''overflow'' no valor máximo | :* Com ''overflow'' no valor máximo | ||

| + | |||

| + | ;Encontro 33 (31 out.) | ||

* Converter os contadores para modo decrescente 0-N | * Converter os contadores para modo decrescente 0-N | ||

| − | |||

:* Com ''underflow'' no valor máximo | :* Com ''underflow'' no valor máximo | ||

| − | + | * Modificar os contadores para pararem no valor máximo(crescentes) e mínimo(decresces). | |

| − | |||

| − | |||

| + | * '''DESAFIO''': Faça um contador que conte de 0 a N, mas que seja crescente ou decrescente controlado por uma entrada DIR. | ||

| + | :* Se DIR = '1' a contagem é crescente se DIR = '0' a contagem é decrescente. | ||

| + | :* Ao atingir o valor máximo (ou mínimo) o contador deverá fazer overflow para o valor 0 (ou N). | ||

| − | ;Encontro | + | |

| − | Instruções do tipo '''LOOP''': LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT | + | ;Encontro 34 (1 nov.) |

| + | |||

| + | Instruções do tipo '''LOOP''': LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT | ||

*Instrução '''LOOP''' incondicional: | *Instrução '''LOOP''' incondicional: | ||

| Linha 2 112: | Linha 2 176: | ||

*Ver pag. 161 a 164 de <ref name="PEDRONI2010b"/> | *Ver pag. 161 a 164 de <ref name="PEDRONI2010b"/> | ||

| + | ;Encontro 35 e 36 (7 e 9 nov.) | ||

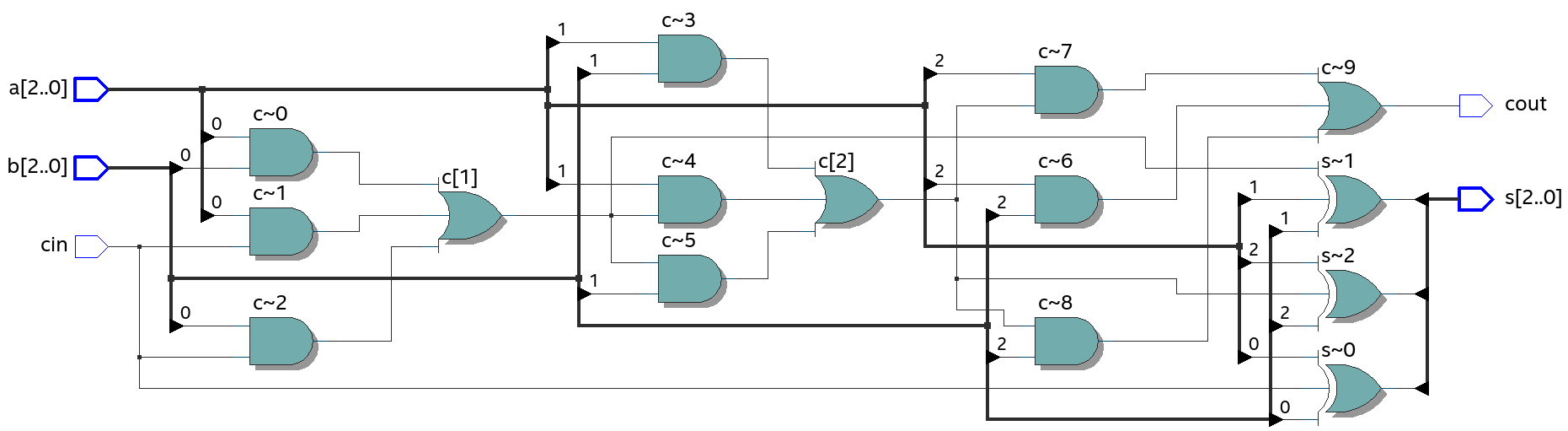

* Carry-Ripple Adder (FOR-LOOP) (Ex 6.4) - apenas analisar. | * Carry-Ripple Adder (FOR-LOOP) (Ex 6.4) - apenas analisar. | ||

:* Um somador do tipo carry ripple utiliza o bloco básico '''full adder''' para construir somadores de qualquer número de bits. Os bits carry são adicionados aos blocos posteriores, produzindo um hardware combinário. | :* Um somador do tipo carry ripple utiliza o bloco básico '''full adder''' para construir somadores de qualquer número de bits. Os bits carry são adicionados aos blocos posteriores, produzindo um hardware combinário. | ||

| Linha 2 118: | Linha 2 183: | ||

::<math> c_{k+1} = a_k . b_k + a_k . c_k + b_k . c_k </math> | ::<math> c_{k+1} = a_k . b_k + a_k . c_k + b_k . c_k </math> | ||

:: onde <math> c_{k+1} </math> é o '''carry out''', <math> c_{k} </math> é o '''carry in''' | :: onde <math> c_{k+1} </math> é o '''carry out''', <math> c_{k} </math> é o '''carry in''' | ||

| + | |||

| + | Esse somador pode ser implementado tanto com código sequencial como com código concorrente. Note que no primeiro caso o bit de '''carry''' se definido como '''variable''' pode ser reaproveitado. No segundo caso é necessário criar um vetor completo para conectar os '''carry_out''' de um estágio ao '''carry_in''' do próximo. | ||

| + | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| + | library ieee; | ||

| + | use ieee.std_logic_1164.all; | ||

| + | |||

entity carry_ripple_adder is | entity carry_ripple_adder is | ||

| − | generic (N : integer := | + | generic (N : integer := 3); |

port ( | port ( | ||

a, b : std_logic_vector (N-1 downto 0); | a, b : std_logic_vector (N-1 downto 0); | ||

| − | cin : std_logic | + | cin : std_logic; |

| − | s : out std_logic_vector (N downto 0); | + | s : out std_logic_vector (N-1 downto 0); |

| − | cout : out std_logic | + | cout : out std_logic |

); | ); | ||

end entity; | end entity; | ||

| − | architecture | + | architecture estrutural_sequencial_v1 of carry_ripple_adder is |

begin | begin | ||

-- Uso de um codigo sequencial para geracao de um circuito combinacional | -- Uso de um codigo sequencial para geracao de um circuito combinacional | ||

| − | process (a, b, cin) | + | process (a, b, cin) is |

| − | + | variable c : std_logic; | |

begin | begin | ||

| − | c | + | c := cin; |

| − | for i in 0 to N - 1 loop | + | for i in 0 to N-1 loop |

| − | + | s(i) <= a(i) xor b(i) xor c; | |

| − | + | c := (a(i) and b(i)) or (a(i) and c) or (b(i) and c); | |

| − | s(i) <= a(i) xor b(i) xor c | ||

| − | |||

| − | c | ||

end loop; | end loop; | ||

| − | cout <= c | + | cout <= c; |

end process; | end process; | ||

| + | end architecture; | ||

| + | |||

| + | architecture estrutural_concorrente_v1 of carry_ripple_adder is | ||

| + | signal c : std_logic_vector(N downto 0); | ||

| + | begin | ||

| + | -- Uso de um codigo concorrente para geracao de um circuito combinacional | ||

| + | c(0) <= cin; | ||

| + | l1: for i in 0 to N-1 generate | ||

| + | s(i) <= a(i) xor b(i) xor c(i); | ||

| + | c(i+1) <= (a(i) and b(i)) or (a(i) and c(i)) or (b(i) and c(i)); | ||

| + | end generate; | ||

| + | cout <= c(N); | ||

end architecture; | end architecture; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | {{fig|5.1|RTL do carry_ripple_adder de 3 bits | RTL_carry_ripple_adder3.png| 800 px |}} | |

| + | |||

*Instrução '''WAIT''': WAIT UNTIL, WAIT FOR (simulação apenas), WAIT ON (não implementada no Quartus II). | *Instrução '''WAIT''': WAIT UNTIL, WAIT FOR (simulação apenas), WAIT ON (não implementada no Quartus II). | ||

| Linha 2 160: | Linha 2 241: | ||

:Algumas instruções de '''WAIT''' serão utilizadas na criação de '''TestBench''' em VHDL para a simulação com o '''MODELSIM'''. | :Algumas instruções de '''WAIT''' serão utilizadas na criação de '''TestBench''' em VHDL para a simulação com o '''MODELSIM'''. | ||

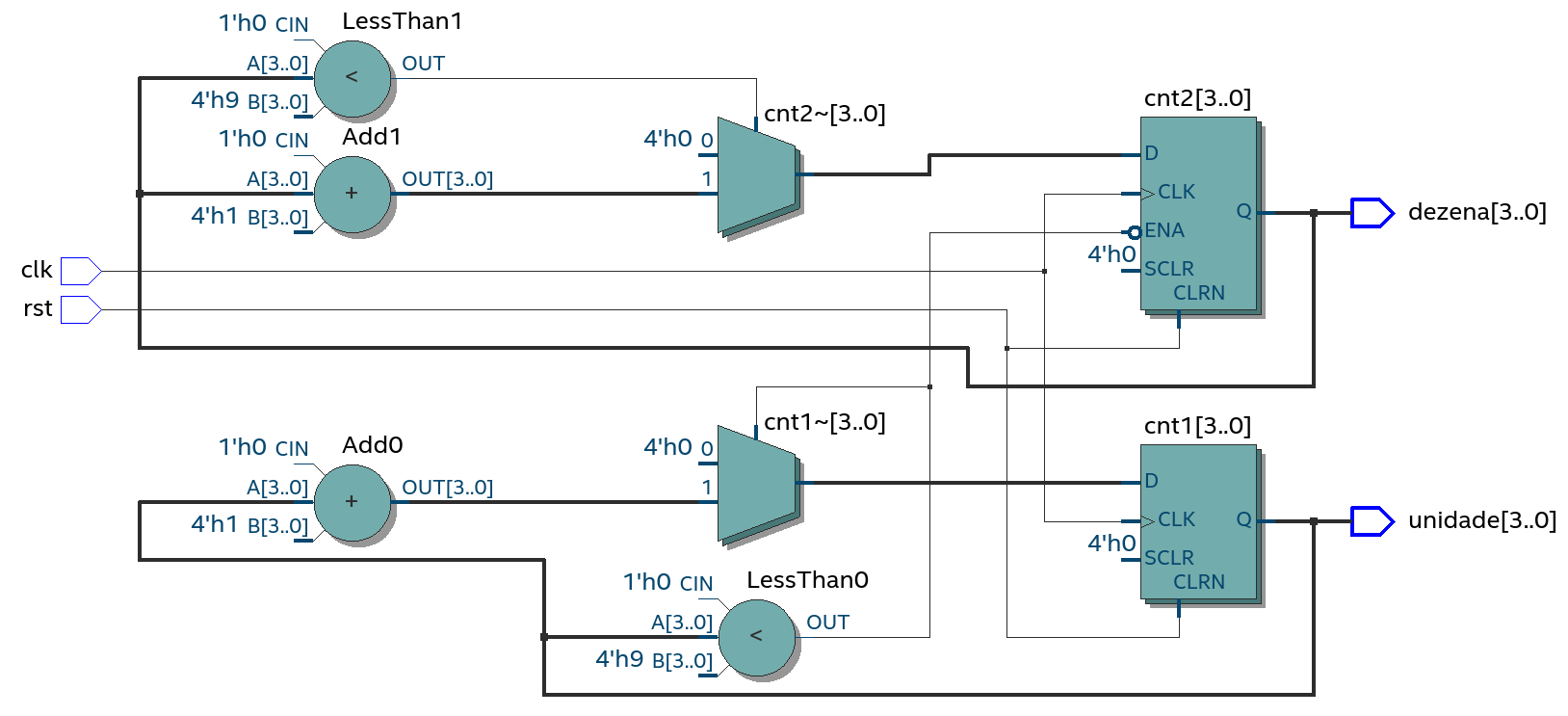

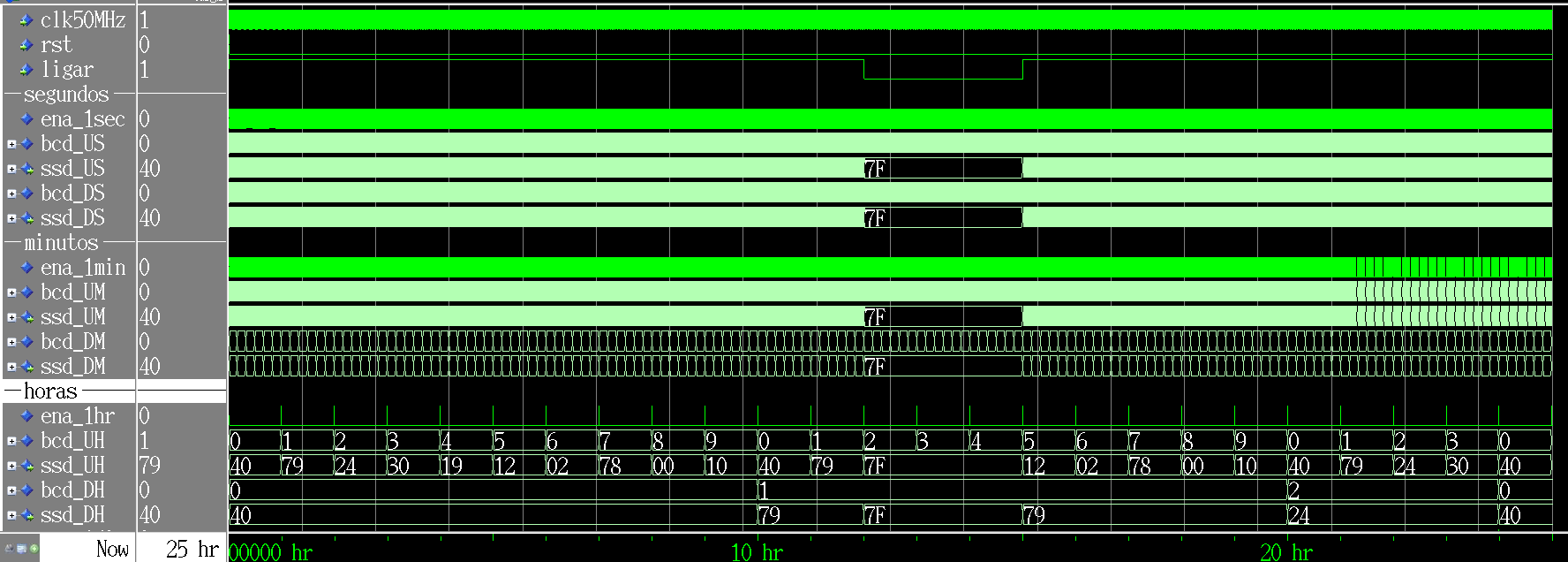

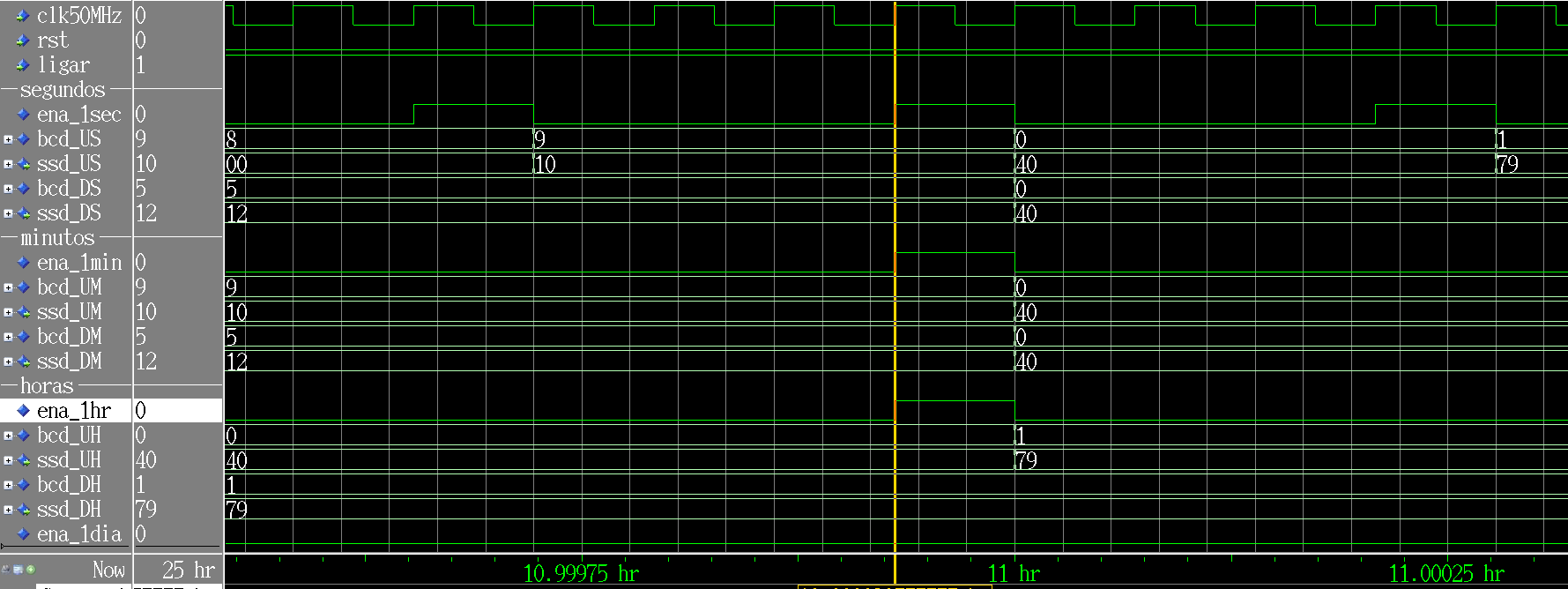

| + | * Projetar um contador em BCD entre 0 e 99 ('''countBCD_DU.vhd'''), com entrada de clock, reset e saidas unidade(0 a 9) e dezena (0 a 9). Projete o contador para parar em qualquer valor de DU onde D é a dezena e U é a unidade. | ||

| − | |||

:* versão 1 - contagem crescente. | :* versão 1 - contagem crescente. | ||

| + | {{fig|5.2|RTL do contador BCD 00 a 99 | RTL_countBCD00-99.png| 800 px |}} | ||

| + | {{fig|5.3|Simulação do contador BCD 00 a 99 | MODELSIM_countBCD00-99.png| 800 px |}} | ||

| + | |||

| + | * Projetar um divisor de clock que dado um clock de entrada de f Hz, produza na saída um sinal de clock de f/N onde N é um número inteiro ('''div_clk_N''') | ||

| + | |||

| + | *Projetar um conversor de BCD para SSD - display de sete segmentos ('''BCD2SSD.vhd'''). O circuito deve ter uma entrada que permite escolher se o display é do tipo anodo comum ou catodo comum. | ||

| + | |||

| + | <!-- | ||

| + | |||

:* versão 2 - contagem decrescente. | :* versão 2 - contagem decrescente. | ||

:* versão 3 - contagem crescente ou decrescente controlado por uma entrada DIR. Se DIR = '0' a contagem é crescente se DIR = '1' a contagem é decrescente. | :* versão 3 - contagem crescente ou decrescente controlado por uma entrada DIR. Se DIR = '0' a contagem é crescente se DIR = '1' a contagem é decrescente. | ||

| + | {{fig|5.4|RTL do contador bidirecional BCD 00 a 99 | RTL_bicountBCD00-99.png| 800 px |}} | ||

| + | {{fig|5.5|Simulação do contador bidirecional BCD 00 a 99| MODELSIM_bicountBCD00-99.png| 800 px |}} | ||

| + | |||

:* versão 4 - contagem crescente de 0 a 59 ou de 0 a 23. Essa versão será usado no relógio. | :* versão 4 - contagem crescente de 0 a 59 ou de 0 a 23. Essa versão será usado no relógio. | ||

| Linha 2 170: | Linha 2 263: | ||

::Antes de implementar a versão 3 verifique no RTL das versões 1 e 2 as diferenças, e pense nas possibilidades de reutilização do hardware. O que é comum entre elas e o que precisa ser acrescentado na versão 3. | ::Antes de implementar a versão 3 verifique no RTL das versões 1 e 2 as diferenças, e pense nas possibilidades de reutilização do hardware. O que é comum entre elas e o que precisa ser acrescentado na versão 3. | ||

::Tente obter uma versão com o mínimo acréscimo em elementos lógicos. | ::Tente obter uma versão com o mínimo acréscimo em elementos lógicos. | ||

| − | |||

| − | |||

* Registrador de deslocamento (Ex.6.3) | * Registrador de deslocamento (Ex.6.3) | ||

| − | {{fig| | + | {{fig|5.6| RTL do registrador de deslocamento (Ex.6.3) | RTL_ShifRegRight.png | 400 px |}} |

| − | + | {{fig|5.7| Technology Map do registrador de deslocamento (Ex.6.3) | TM_ShifRegRight.png | 800 px |}} | |

:Versão 1 - Implementação com 4 FF D. | :Versão 1 - Implementação com 4 FF D. | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 2 232: | Linha 2 323: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | *Simule o Registrador de Deslocamento | + | *Simule o Registrador de Deslocamento visualizando os sinais internos para perceber o deslocamento. |

| − | |||

Aproveitando a versão 3 ou 2 do Shift Register da aula anterior, projete e faça a simulação dos dois circuitos indicados a seguir: | Aproveitando a versão 3 ou 2 do Shift Register da aula anterior, projete e faça a simulação dos dois circuitos indicados a seguir: | ||

| − | |||

* Embrião de um conversor serial para paralelo. | * Embrião de um conversor serial para paralelo. | ||

| Linha 2 294: | Linha 2 383: | ||

;Encontro 37 (5 jul.): | ;Encontro 37 (5 jul.): | ||

* Preparação para a aula de laboratório (AE5 - Relógio HH-MM-SS Implementação, simulação e testes de hardware) | * Preparação para a aula de laboratório (AE5 - Relógio HH-MM-SS Implementação, simulação e testes de hardware) | ||

| − | + | ||

;Aula 37 (02 mar): | ;Aula 37 (02 mar): | ||

* Preparação para a aula de laboratório [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom(2021.2)_-_Prof._Marcos_Moecke#AE11_-_Laborat.C3.B3rio_de_programa.C3.A7.C3.A3o_de_FPGA_-_Timer_00_a_99 AE11 - Laboratório de programação de FPGA - Timer 00 a 99] | * Preparação para a aula de laboratório [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom(2021.2)_-_Prof._Marcos_Moecke#AE11_-_Laborat.C3.B3rio_de_programa.C3.A7.C3.A3o_de_FPGA_-_Timer_00_a_99 AE11 - Laboratório de programação de FPGA - Timer 00 a 99] | ||

| Linha 2 366: | Linha 2 455: | ||

===Unidade 6 - Projeto a nível de Sistema=== | ===Unidade 6 - Projeto a nível de Sistema=== | ||

| − | * | + | * 3 ENCONTROS |

{{collapse top| expand=true | Unidade 6 - Projeto a nível de Sistema}} | {{collapse top| expand=true | Unidade 6 - Projeto a nível de Sistema}} | ||

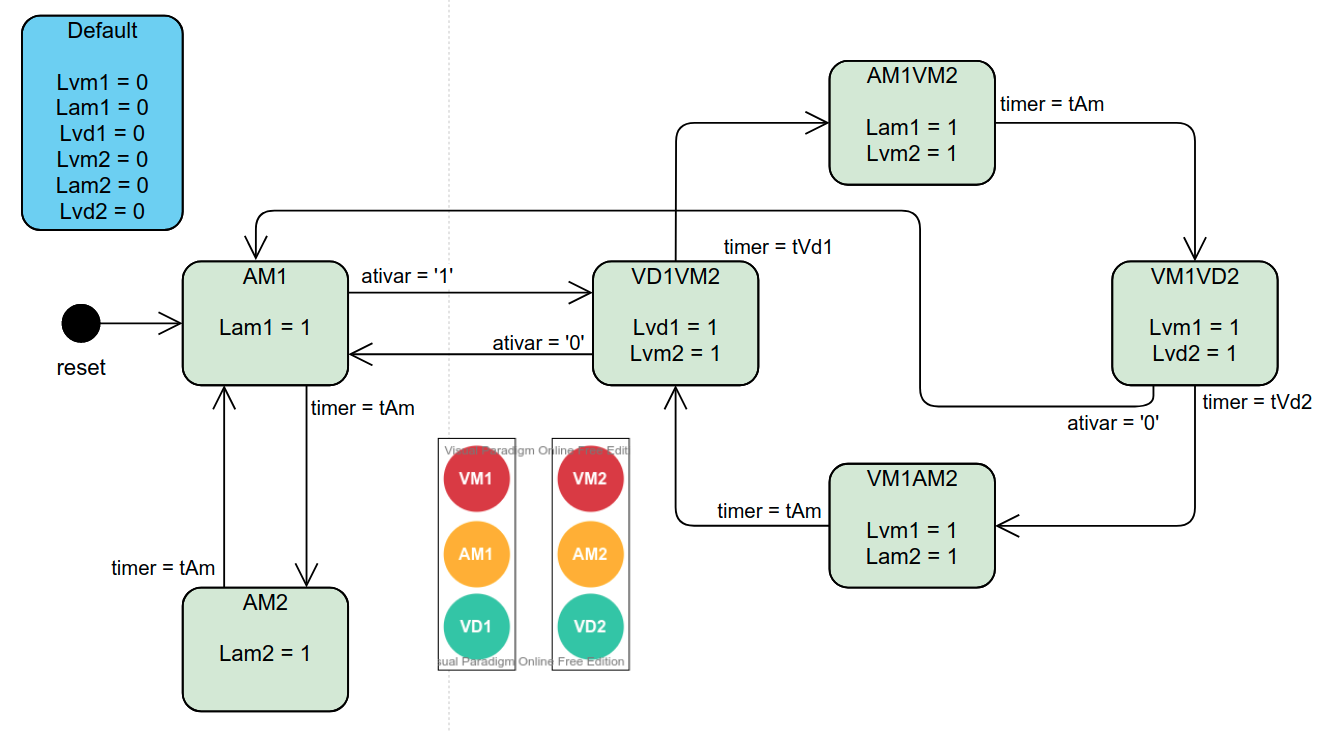

| − | ;Encontro | + | ;Encontro 37 (14 nov.) |

*Projeto a nível de Sistema. | *Projeto a nível de Sistema. | ||

:* O '''PACKAGE''' e '''PACKAGE BODY''': onde declarar e como usar. | :* O '''PACKAGE''' e '''PACKAGE BODY''': onde declarar e como usar. | ||

| Linha 2 376: | Linha 2 465: | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | entity | + | entity countBCD_DU is |

| − | generic ( | + | generic (max_D : natural := 9; max_U : natural := 9); |

port ( | port ( | ||

clk, rst : in std_logic; | clk, rst : in std_logic; | ||

| − | + | clk_out : out std_logic; | |

| + | bcd_D, bcd_U : out std_logic_vector(3 downto 0) | ||

); | ); | ||

end entity; | end entity; | ||

| Linha 2 387: | Linha 2 477: | ||

Será declarada como um COMPONENT | Será declarada como um COMPONENT | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | component | + | component countBCD_DU is |

| − | generic ( | + | generic (max_D : natural := 9; max_U : natural := 9); |

port ( | port ( | ||

clk, rst : in std_logic; | clk, rst : in std_logic; | ||

| − | + | clk_out : out std_logic; | |

| + | bcd_D, bcd_U : out std_logic_vector(3 downto 0) | ||

); | ); | ||

end component; | end component; | ||

| Linha 2 399: | Linha 2 490: | ||

* Mapeamento por posição e nominal. | * Mapeamento por posição e nominal. | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | comp1 : | + | comp1 : countBCD_DU |

| − | GENERIC MAP ( | + | GENERIC MAP (5, 9) |

| − | PORT MAP (clk,rst, bcd_dezena, bcd_unidade); | + | PORT MAP (clk,rst, clk1sec, bcd_dezena, bcd_unidade); |

</syntaxhighlight> | </syntaxhighlight> | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

comp1 : contador_bcd_00_99 | comp1 : contador_bcd_00_99 | ||

| − | GENERIC MAP ( | + | GENERIC MAP ( max_D => 5, max_U => 9) |

PORT MAP ( clk => clk, | PORT MAP ( clk => clk, | ||

rst => rst, | rst => rst, | ||

| − | + | clk_out => clk1sec, | |

| − | + | bcd_D => bcd_dezena, | |

| + | bcd_U => bcd_unidade); | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| Linha 2 418: | Linha 2 510: | ||

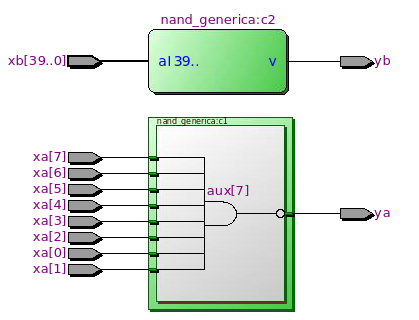

{{fig|5.1| RTL portas NAND genéricas | NAND8&NAND40.png | 400 px |}} | {{fig|5.1| RTL portas NAND genéricas | NAND8&NAND40.png | 400 px |}} | ||

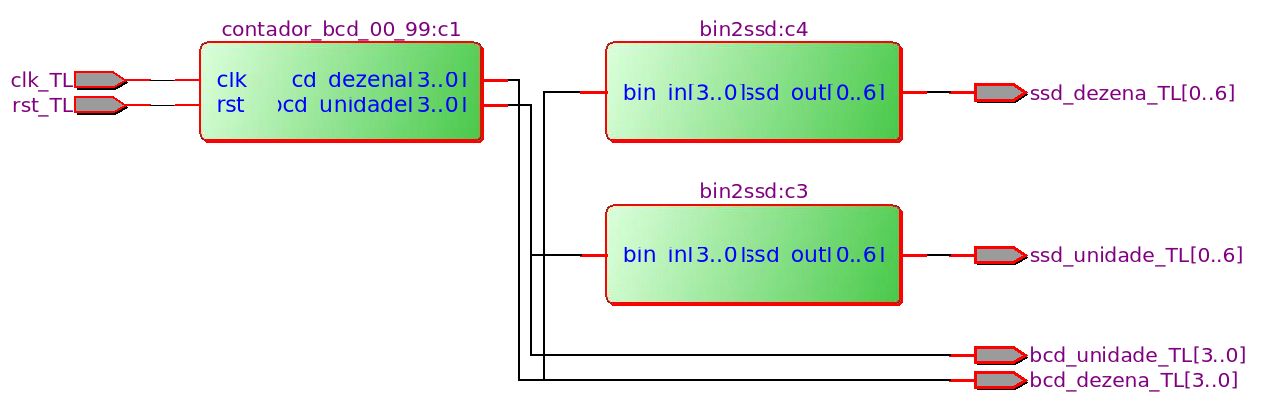

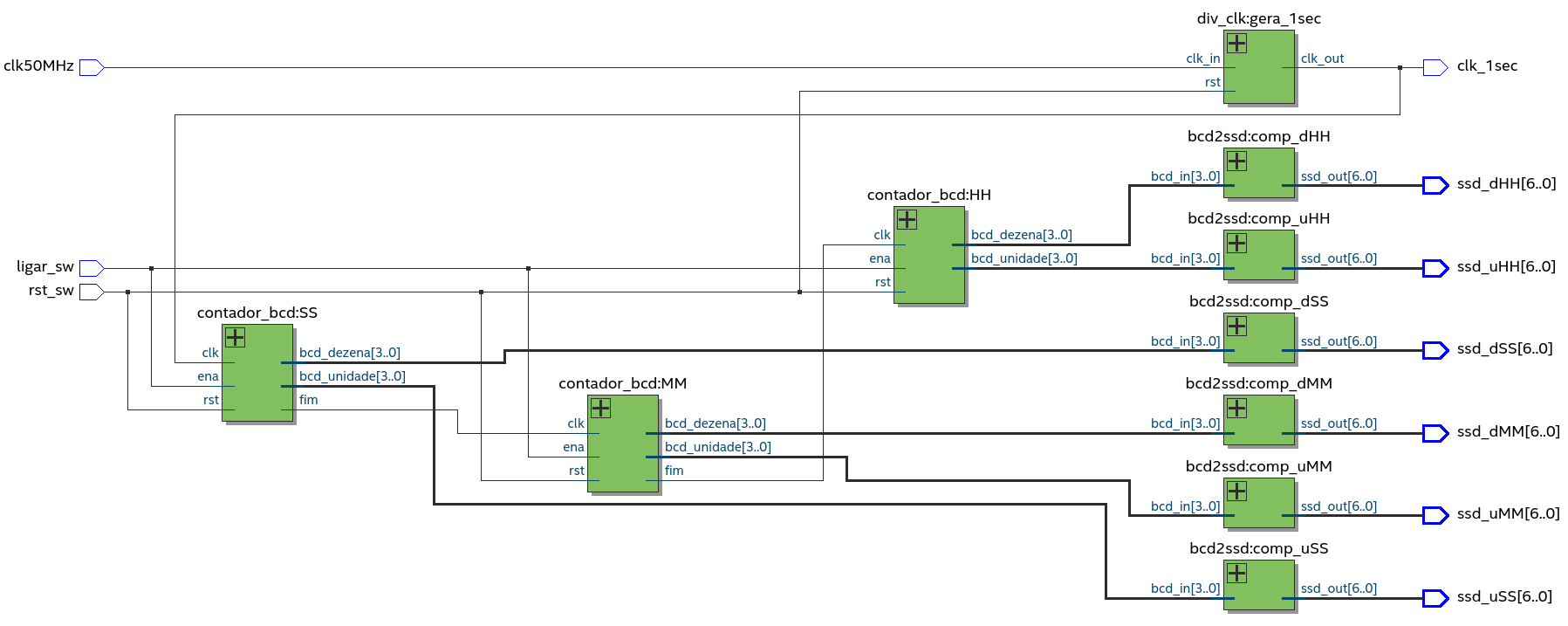

| − | * | + | * Construir o projeto do '''contador_ssd_00_99''' usando componentes projetados anteriormente |

{{fig|5.2| RTL do contador_ssd_00_99 usando componentes | contador_ssd_00_99_TL.png | 600 px |}} | {{fig|5.2| RTL do contador_ssd_00_99 usando componentes | contador_ssd_00_99_TL.png | 600 px |}} | ||

| + | ;Ver também: | ||

| + | *[[Display de 7 segmentos]] | ||

| − | |||

| − | |||

| − | ; Encontro | + | ;Encontro 38 (17 nov.) |

| + | *[https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE4_-_Laborat.C3.B3rio_de_programa.C3.A7.C3.A3o_de_FPGA_-_Rel.C3.B3gio_HHMMSS AE4 - Laboratório de programação de FPGA - Relógio HHMMSS] | ||

| + | |||

| + | ;Encontro 39 (20 nov.) | ||

* Instanciação de '''COMPONENT''' com '''GENERATE'''. | * Instanciação de '''COMPONENT''' com '''GENERATE'''. | ||

| Linha 2 437: | Linha 2 532: | ||

::* Ligação direta: ARCHITECTURE-ENTITY. | ::* Ligação direta: ARCHITECTURE-ENTITY. | ||

::* Ligação da instanciação dos componentes: COMPONENT-ENTITY(ARCHITECTURE). | ::* Ligação da instanciação dos componentes: COMPONENT-ENTITY(ARCHITECTURE). | ||

| − | |||

*FUNCTION e PROCEDURE (são chamados de subprogramas), e podem ser construídos em um PACKAGE, ENTITY, ARCHITECTURE, ou PROCESS. | *FUNCTION e PROCEDURE (são chamados de subprogramas), e podem ser construídos em um PACKAGE, ENTITY, ARCHITECTURE, ou PROCESS. | ||

| Linha 2 554: | Linha 2 648: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | |||

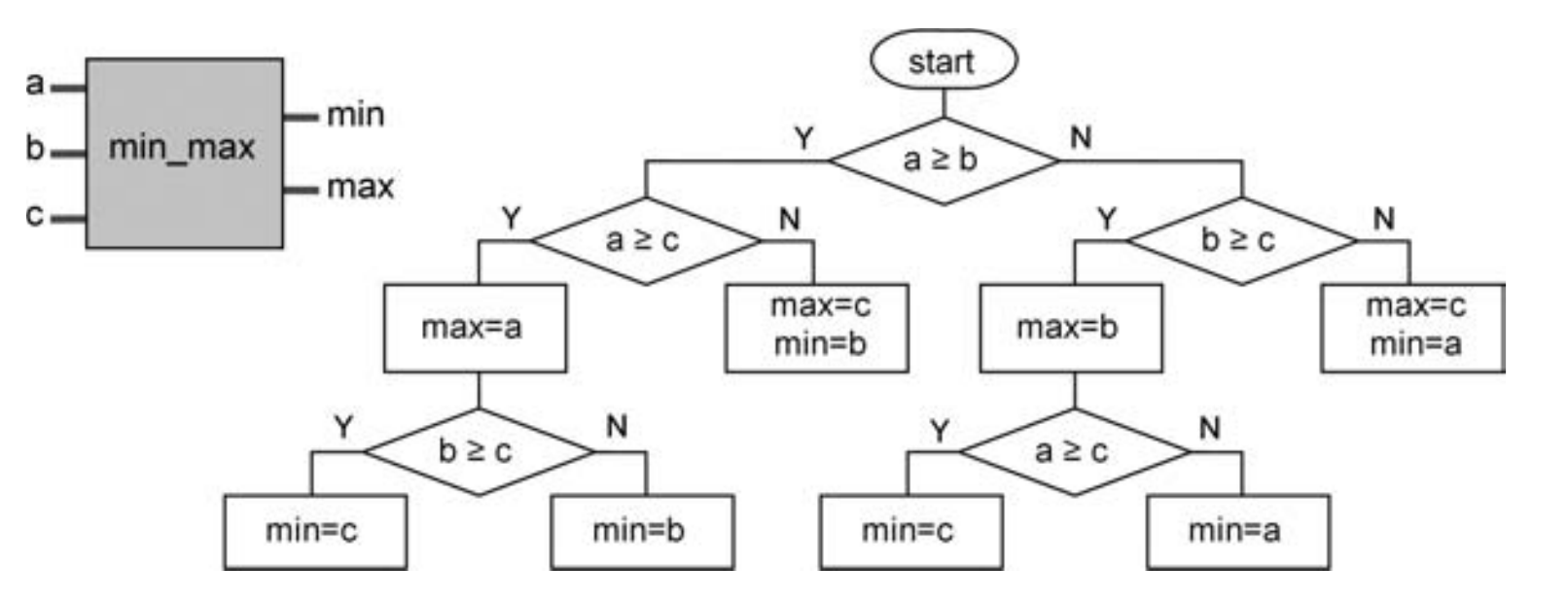

* Exemplo: min_max Ex.9.4 | * Exemplo: min_max Ex.9.4 | ||

{{fig|6.1|Fluxograma da PROCEDURE min_max| fluxogramMinMax.png| 600 px | pag. 232 de <ref name="PEDRONI2010b"/> }} | {{fig|6.1|Fluxograma da PROCEDURE min_max| fluxogramMinMax.png| 600 px | pag. 232 de <ref name="PEDRONI2010b"/> }} | ||

| Linha 2 629: | Linha 2 722: | ||

:*Exemplo: Detector de Paridade Ex. 8.3 | :*Exemplo: Detector de Paridade Ex. 8.3 | ||

:* Ver pag. 201 a 213 de <ref name="PEDRONI2010b"/> | :* Ver pag. 201 a 213 de <ref name="PEDRONI2010b"/> | ||

| − | |||

<!-- | <!-- | ||

; Encontro 41 e 42 (16 jul. Sábado): | ; Encontro 41 e 42 (16 jul. Sábado): | ||

*[https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE7_-_Laborat.C3.B3rio_de_programa.C3.A7.C3.A3o_de_FPGA_-_Timer_000_a_999_.28vers.C3.A3o_2.29 AE7 - Laboratório de programação de FPGA - Timer 000 a 999 (versão 2) ] | *[https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE7_-_Laborat.C3.B3rio_de_programa.C3.A7.C3.A3o_de_FPGA_-_Timer_000_a_999_.28vers.C3.A3o_2.29 AE7 - Laboratório de programação de FPGA - Timer 000 a 999 (versão 2) ] | ||

| − | |||

::* Exercícios: 9.1 a 9.4, 9.6 a 9.9 | ::* Exercícios: 9.1 a 9.4, 9.6 a 9.9 | ||

:* Ver pag. 213 a 239 de <ref name="PEDRONI2010b"/>) | :* Ver pag. 213 a 239 de <ref name="PEDRONI2010b"/>) | ||

| Linha 2 681: | Linha 2 772: | ||

===Unidade 7 - Maquinas de Estado Finitas=== | ===Unidade 7 - Maquinas de Estado Finitas=== | ||

| − | + | * 4 ENCONTROS | |

| − | {{collapse top| expand=true | Unidade 7 - Maquinas de Estado Finitas}} | + | {{collapse top | expand=true | Unidade 7 - Maquinas de Estado Finitas}} |

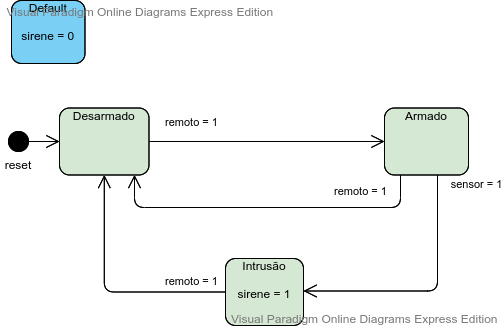

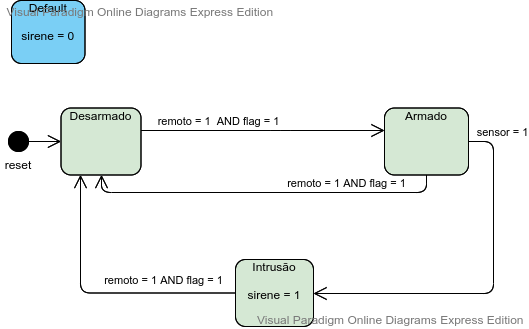

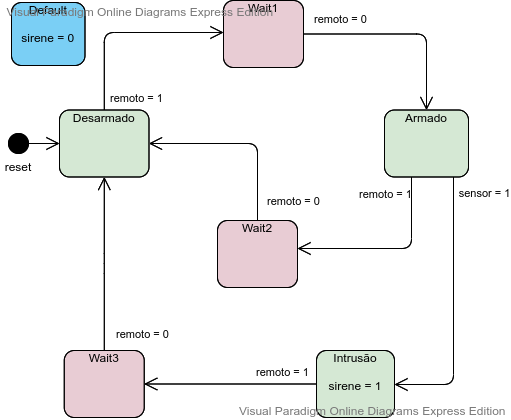

| − | + | ;Encontro 39 (24 nov.) | |

| − | ; Encontro | + | * O que é uma FSM - Finite State Machine |

| − | |||

| − | |||

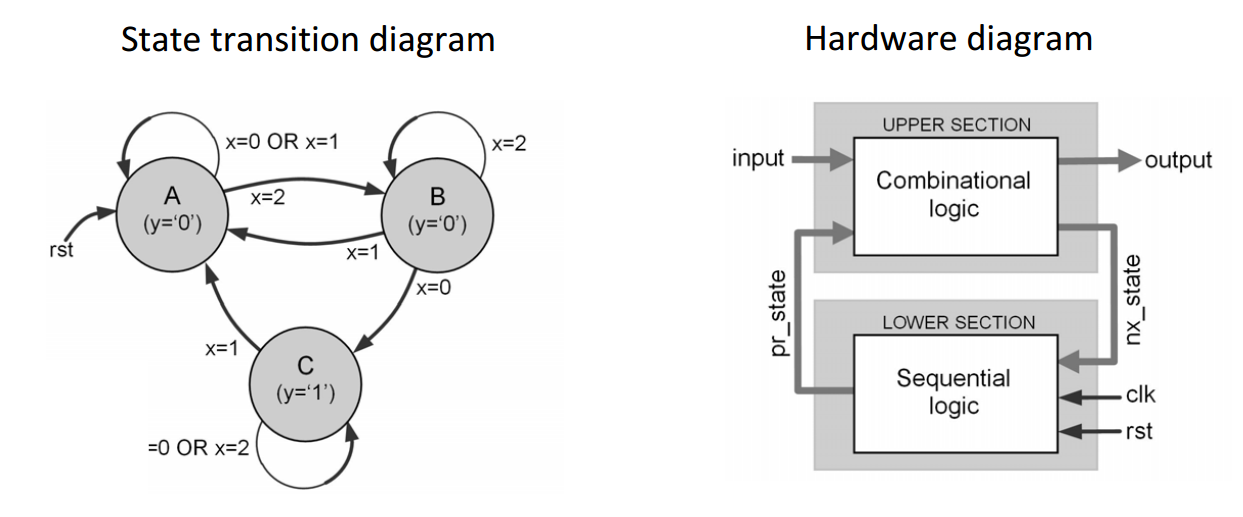

{{fig|7.1|Exemplo de diagrama de estados de uma FSM Fig11.1(a) e implementação em hardware da FSM Fig11.2(a)|Fig11_1_FSM.png|800 px|Figura 11.1 e 11.2 de <ref name="PEDRONI2010b"/>}} | {{fig|7.1|Exemplo de diagrama de estados de uma FSM Fig11.1(a) e implementação em hardware da FSM Fig11.2(a)|Fig11_1_FSM.png|800 px|Figura 11.1 e 11.2 de <ref name="PEDRONI2010b"/>}} | ||

| − | + | * Modelo básico em VHDL de FSM | |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

LIBRARY ieee; | LIBRARY ieee; | ||

| Linha 2 696: | Linha 2 785: | ||

PORT ( | PORT ( | ||

clk, rst : IN STD_LOGIC; | clk, rst : IN STD_LOGIC; | ||

| − | + | entradas : IN < data_type > ; | |

| − | + | saidas : OUT < data_type >); | |

END entity; | END entity; | ||

---------------------------------------------------------- | ---------------------------------------------------------- | ||

| Linha 2 712: | Linha 2 801: | ||

IF (rst = '1') THEN | IF (rst = '1') THEN | ||

pr_state <= A; | pr_state <= A; | ||

| − | ELSIF (clk | + | ELSIF rising_edge(clk) THEN |

| + | -- apenas na borda do "clk" ocorre a mudança de estado da FSM | ||

pr_state <= nx_state; | pr_state <= nx_state; | ||

END IF; | END IF; | ||

END PROCESS; | END PROCESS; | ||

------Logica Combinacional da FSM:------------ | ------Logica Combinacional da FSM:------------ | ||

| − | PROCESS (pr_state, | + | PROCESS (pr_state, entradas) |

BEGIN | BEGIN | ||

| − | + | ------Valores default das saidas------------ | |

| − | + | saidas <= < valor > ; | |

CASE pr_state IS | CASE pr_state IS | ||

WHEN A => | WHEN A => | ||

| − | + | -- é necessário um WHEN para definir as "saidas" durante cada estado | |

| − | IF ( | + | -- e analisar as "entradas" para definir o próximo estado |

| + | saidas <= < valor > ; -- apenas se diferente do valor default | ||

| + | IF (entradas = < valor >) THEN | ||

nx_state <= B; | nx_state <= B; | ||

... | ... | ||

| Linha 2 731: | Linha 2 823: | ||

END IF; | END IF; | ||

WHEN B => | WHEN B => | ||

| − | + | saidas <= < valor > ; -- apenas se diferente do valor default | |

| − | IF ( | + | -- dependendo das "entradas", pode ser que hajam mais de um estados de destino |

| + | IF (entradas = < valor >) THEN | ||

nx_state <= C; | nx_state <= C; | ||

| − | + | ELSIF (entradas = < valor >) THEN | |

| + | nx_state <= A; | ||

ELSE | ELSE | ||

nx_state <= B; | nx_state <= B; | ||

END IF; | END IF; | ||

| + | WHEN C => | ||

| + | saidas <= < valor > ; -- apenas se diferente do valor default | ||

| + | -- a passagem para outro estado pode não depender de nenhuma "entrada" | ||

| + | nx_state <= D; | ||

WHEN ... | WHEN ... | ||

| + | |||

| + | |||

END CASE; | END CASE; | ||

END PROCESS; | END PROCESS; | ||

------Seção de Saída (opcional):------- | ------Seção de Saída (opcional):------- | ||

| + | -- Essa seção visa garantir que a saida new_output esteja sincronizada com o clk. | ||

| + | -- Se isso não for importante, ela pode ser suprimida | ||

PROCESS (clk, rst) | PROCESS (clk, rst) | ||

BEGIN | BEGIN | ||

IF (rst = '1') THEN | IF (rst = '1') THEN | ||

| − | new_output <= < | + | new_output <= < valor > ; |

| − | ELSIF (clk | + | ELSIF rising_edge(clk) THEN --or falling_edge(clk) |

new_output <= output; | new_output <= output; | ||

END IF; | END IF; | ||

| Linha 2 752: | Linha 2 854: | ||

END architecture; | END architecture; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| + | ;Dica: Se ao discrever uma FSM, faltar algum estado, o Quartus dará erro durante a compilação. Para resolver temporariamente isso pode se usar antes de encerrar o case | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | WHEN others => | ||

| + | nx_state <= <initial_state>; | ||

| + | </syntaxhighlight> | ||

| + | |||

:* Usando o template acima descreva em VHDL a FSM indicada na Figura 11.1. | :* Usando o template acima descreva em VHDL a FSM indicada na Figura 11.1. | ||

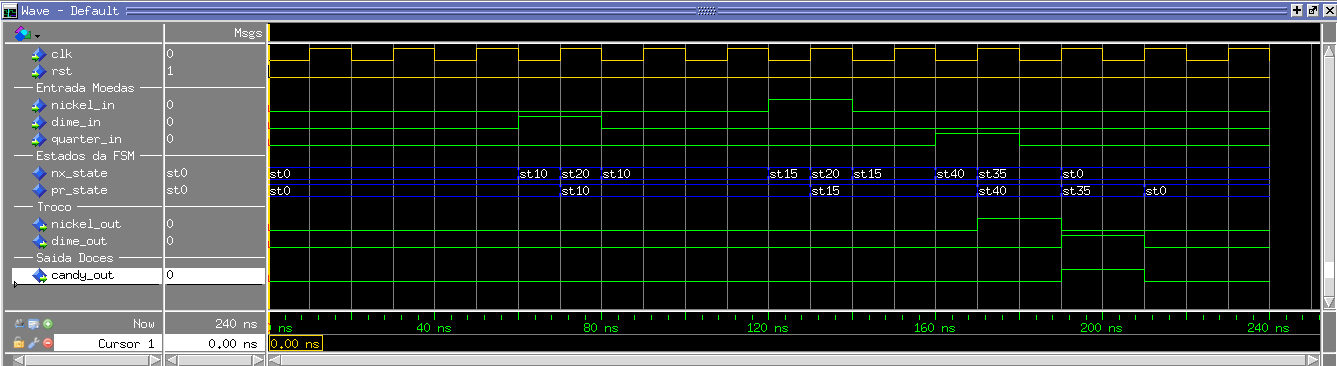

:* Faça a simulação da FSM com Modelsim utilizando um testbench em VHDL que faça a FSM seguir os estados | :* Faça a simulação da FSM com Modelsim utilizando um testbench em VHDL que faça a FSM seguir os estados | ||

| − | + | <center> | |

| + | <math> RST \to A \xrightarrow{\text{x=0}} A \xrightarrow{\text{x=1}} A \xrightarrow{\text{x=2}} B \xrightarrow{\text{x=2}} B \xrightarrow{\text{x=0}} C \xrightarrow{\text{x=0}} C \xrightarrow{\text{x=2}} C \xrightarrow{\text{x=1}} A \xrightarrow{\text{x=2}} B \xrightarrow{\text{x=1}} A </math> | ||

| + | </center> | ||

:: Ver pag. 277 a 280 de <ref name="PEDRONI2010b"/> | :: Ver pag. 277 a 280 de <ref name="PEDRONI2010b"/> | ||

| − | :: | + | :: Note que o uso da atribuição manual do '''enum_encoding''' pode faz com que o compilador do Quartus não reconheça a FSM, mas use logica regular para representar o sistema. |

| − | |||

| − | |||

| − | |||

| − | |||

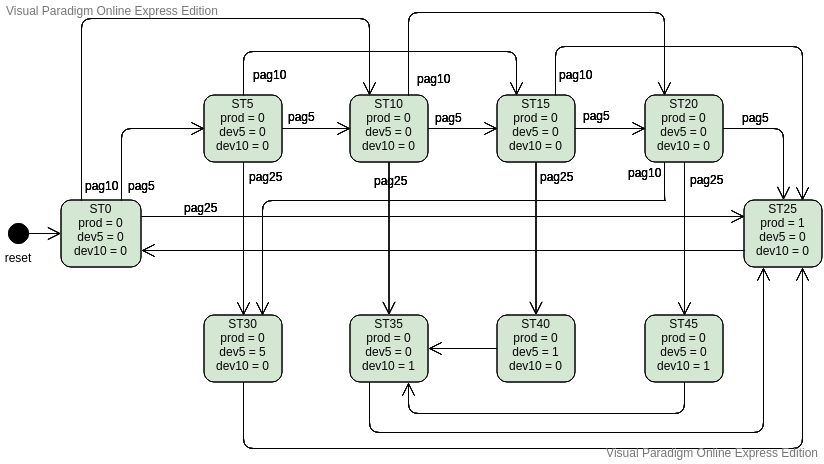

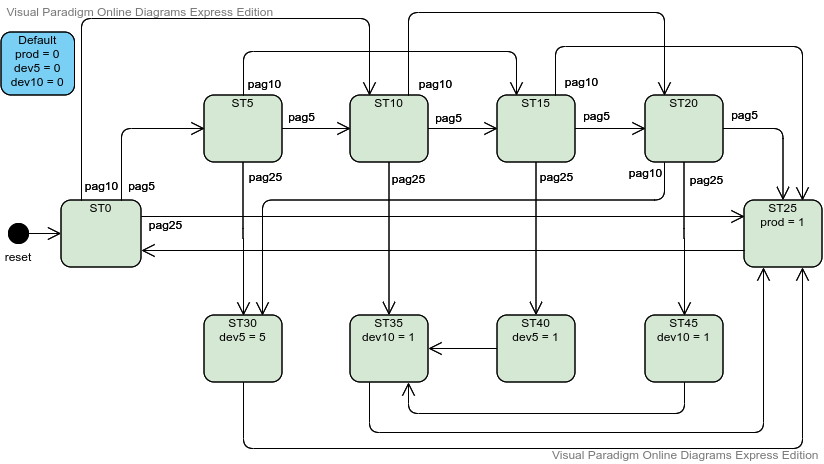

:* Máquina de vender doces | :* Máquina de vender doces | ||

::*Use o template da FSM para modelar o sistema mostrado na figurar a seguir. | ::*Use o template da FSM para modelar o sistema mostrado na figurar a seguir. | ||

| Linha 2 776: | Linha 2 882: | ||

:: '''Dica''': para desenhar a FSM recomendo utilizar um software on-line para tal finalidade. Por Ex. [https://online.visual-paradigm.com/pt/ Visual Paradigm]. | :: '''Dica''': para desenhar a FSM recomendo utilizar um software on-line para tal finalidade. Por Ex. [https://online.visual-paradigm.com/pt/ Visual Paradigm]. | ||

| − | |||