1 Registro on-line das aulas

1.1 Unidade 1 - Aula inicial, Introdução a disciplina

| Unidade 1 - Aula inicial, Introdução a disciplina

|

- Encontro 1 (12 ago.)

- A página da UC contém os materiais que não alteram entre semestre.

- Relação com as outras UCs do Eixo Sistemas Computacionais (Marrom). Ver grafo do curriculo

- ELD129002 - ELETRÔNICA DIGITAL I (ELD1): Sistema de numeração e códigos. Lógica booleana. Circuitos combinacionais. Circuitos aritméticos. Linguagem de descrição de hardware. Implementação e teste de circuitos digitais. Projeto de circuitos lógicos.

- ELD129003 - ELETRÔNICA DIGITAL II (ELD2): Dispositivos lógicos programáveis. Circuitos sequenciais. Metodologia síncrona. Projeto hierárquico e parametrizado. Máquinas de estados finita. Register Transfer Methodology. Teste de circuitos digitais. Implementação em FPGA. Introdução a Linguagem de Descrição de Hardware.

- AOC129004 - ARQUITETURA E ORGANIZAÇÃO DE COMPUTADORES (AOC): Introdução à Arquitetura Computadores. Linguagem Assembly. Linguagem de Máquina. Programação Assembly. Modos de Endereçamento. Processo de compilação e carga de um programa. Introdução à Organização de Computadores. Organização Monociclo e Multiciclo. Pipeline. Memória e Sistema de E/S.

- MIC129007 - MICROCONTROLADORES (MIC): Introdução a Microcontroladores e Aplicações. Arquitetura de um microcontrolador. Pilha e Subrotinas. Interrupção. Contadores e Temporizadores. Interface com Periféricos. Programação em alto nível (ex.: C, C++ e RUST) para Microcontroladores: Mapeamento de tipos e estruturas de alto nível para sistemas com recursos limitados. Projeto de hardware e firmware com microcontroladores.

- STE129008 - STE - SISTEMAS EMBARCADOS (STE): Conceitos em Sistemas Embarcados. Metodologia de Desenvolvimento de Sistemas Embarcados. Sistemas Operacionais para Sistemas Embarcados. Ferramentas de desenvolvimento e depuração. Barramentos e dispositivos de acesso a redes. Desenvolvimento de Projeto.

- Nesta página está o Registro diário dos encontros e avaliações.

- A entrega de atividades e avaliações será através da plataforma Moodle. A inscrição dos alunos é automática a partir do SIGAA.

- Para a comunicação entre professor-aluno, além dos avisos no SIGAA, utilizaremos o chat institucional. A princípio todos os alunos já estão previamente cadastrados pelo seu email institucional. Confiram enviando uma mensagem de apresentação.

- Utilizaremos durante as aulas algumas ferramentas computacionas como o site do Falstad para entender circuitos digitais e fazer simulações básicas.

- Também utilizaremos os softwares Quartus Light e ModelSim instalados nas maquinas do laboratório para praticar a parte de programação de hardware (descrição de hardware). Esses softwares também podem ser usados através da Nuvem do IFSC..

- LER PARA O PRÓXIMO ENCONTRO

|

1.2 Unidade 2 - Sistema de numeração e códigos

| Unidade 2 - Sistema de numeração e códigos

|

|

|

1.3 Unidade 3 - Funções, portas lógicas e álgebra booleana

| Unidade 3 - Funções, portas lógicas e álgebra booleana

|

|

|

1.4 Unidade 4 - Introdução a linguagem VHDL e Quartus/ModelSim

| Unidade 4 - Introdução a linguagem VHDL e Quartus/ModelSim

|

|

|

1.5 Unidade 5 - Circuitos lógicos combinacionais (com VHDL)

| Unidade 5 - Circuitos lógicos combinacionais (com VHDL)

|

|

|

1.6 Unidade 6 - Circuitos aritméticos (com VHDL)

| Unidade 6 - Circuitos aritméticos (com VHDL)

|

|

|

2 Avaliações

Durante o semestre serão realizadas 4 avaliações. As avaliações devem ser enviadas pela plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1a - (3 pontos) Sistema de Numeração e códigos : XX/2025

- A1b - (4 pontos) Expressões lógicas e mapa de Karnaugh : XX/2025

- A1c - (4 pontos) Circuitos lógicos, Introdução ao VHDL e revisão de A1a e A1b : XX/2025

- A2 - (10 pontos) Circuitos combinacionais e ariméticos : XX/2025

- R1 - Recuperação de A1: XX/2025

- R2 - Recuperação de A2: XX/2025

Folhas de consulta:

3 Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN.

A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN. Para os BÔNUS só serão considerados projetos entregues no prazo.

4.1 AE1 - Projeto de um conversor de binário para mostrador de 7 segmentos

| AE1 - Projeto de um conversor de binário para mostrador de 7 segmentos

|

- Objetivos

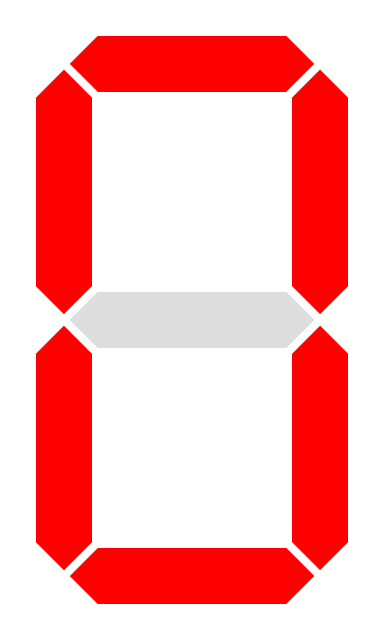

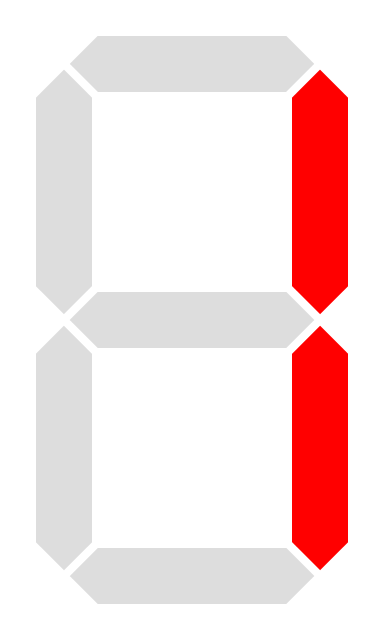

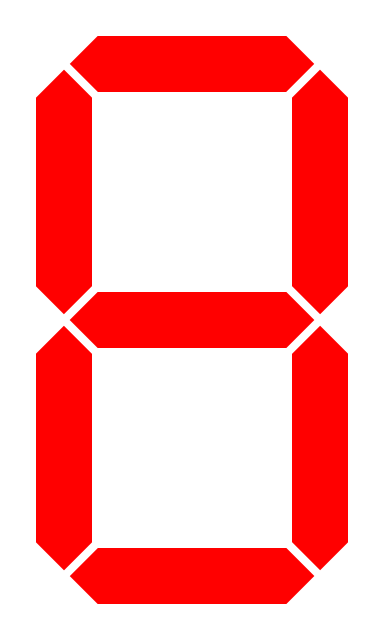

- Conhecer o mostrador (diplay) de 7 segmento

- Projetar um circuito digital que realize a conversão de uma entrada binária de 4 bits para uma saída de um mostrador de 7 segmentos, para o conjunto escolhido.

- Descrever o funcionamento de um circuito através de uma tabela verdade.

- Usar a técnica do mapa de Karnaugh para minimizar a função lógica de cada uma das saídas.

- Atividades

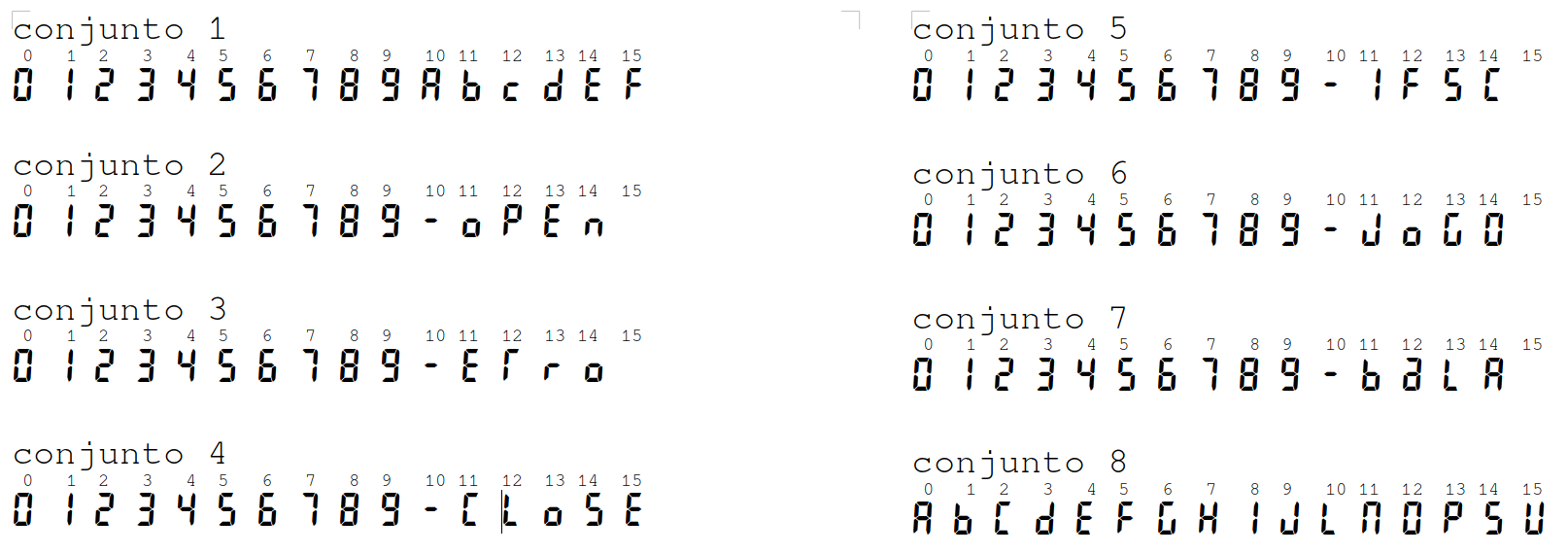

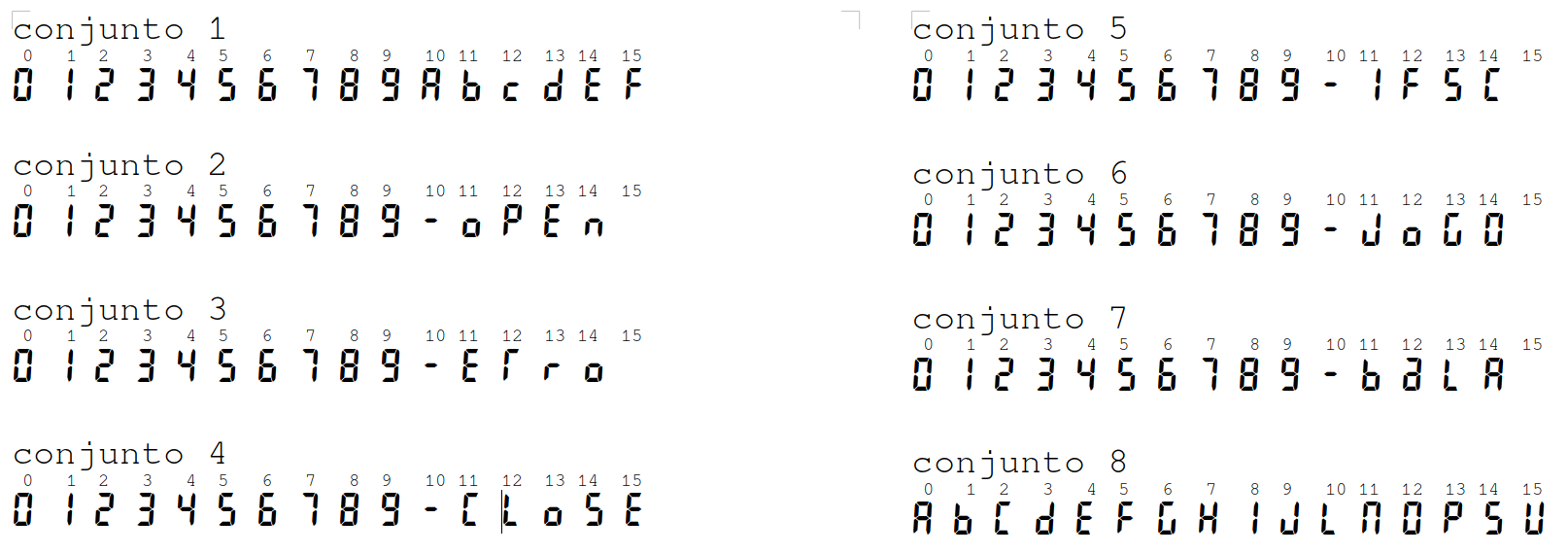

Figura AE1.1 - Conjuntos para mostrador de 7 segmentos

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Nesta atividade os estudantes devem projetar um conversor de binário para mostrador de 7 segmentos.

- Inicialmente considere que na entrada são possíveis apenas os valores 0, 1, 2, ... 8, 9. Apesar de uma entrada binária de 4 bits poder receber os valores 1010 (dez), 1011 (onze), ... 1111 (quinze), pode considerar que elas não acontecem por restrição dos dados de entrada. Por isso, cada estudante tem a liberdade de definir como o mostrador se comportará nesta situação.

| Digito

|

ABCD

|

ssd_a

|

ssd_b

|

ssd_c

|

ssd_d

|

ssd_e

|

ssd_f

|

ssd_g

|

Mostrador

|

| 0 |

0000 |

|

|

|

|

|

|

|

|

| 1 |

0001 |

|

|

|

|

|

|

|

|

| 2 |

0010 |

|

|

|

|

|

|

|

|

| 3 |

0011 |

|

|

|

|

|

|

|

|

| 4 |

0100 |

|

|

|

|

|

|

|

|

| 5 |

0101 |

|

|

|

|

|

|

|

|

| 6 |

0110 |

|

|

|

|

|

|

|

|

| 7 |

0111 |

|

|

|

|

|

|

|

|

| 8 |

1000 |

|

|

|

|

|

|

|

|

| 9 |

1001 |

|

|

|

|

|

|

|

|

| A |

1010 |

|

|

|

|

|

|

|

|

| B |

1011 |

|

|

|

|

|

|

|

|

| C |

1100 |

|

|

|

|

|

|

|

|

| D |

1101 |

|

|

|

|

|

|

|

|

| E |

1110 |

|

|

|

|

|

|

|

|

| F |

1111 |

|

|

|

|

|

|

|

|

- Em um novo projeto considere que os valores 1010 (dez), 1011 (onze), ... 1111 (quinze) mostram os segmentos acessos conforme figura acima.

- Entregas

- O projeto todo deverá se realizado manuscrito, devendo as folhas ter a identificação do nome completo do estudante e estar grampeadas.

- Devem ser feitos dois projetos, sendo que um deve usaro o don't care e outro usando todas as entradas conforme o conjunto escolhido.

- Compare o resultado final dos dois projetos. Deverão ser apresentados no mínimo:

- 1) A tabela verdade completa indicando para as entradas de 0 a 15 quais são os valores das saídas (segmentos) a, b, c, d, e, f, g.

- 2) Para cada saída mostre o mapa de Karnaugh e a indicação dos agrupamentos de bits obtidos, e o respectiva produto (implicante).

- 3) Para cada saída deve ser apresentada a expressão lógica minimizada e também o circuito lógico obtido.

- Os projetos serão depois implementados em hardware, quando você saberá se houve algum erro no seu projeto.

- A entrega será feita pessoalmente para o professor no prazo indicado no Moodle.

|

4.2 AE2 - Conhecendo os dispositivos lógicos programáveis

| AE2 - Conhecendo os dispositivos lógicos programáveis

|

- Objetivos

- Conhecer o Quartus Prime e as características dos dispositivos lógicos programáveis

- Analisar os tempos de propagação em um circuito combinacional

- Alterar configurações do compilador

- Fazer a simulação funcional de um circuito combinacional.

- Atividades

- PASSO 0: Abrindo o Quartus Prime na Nuvem do IFSC

- Ao escolher a família de FPGAS, escolha inicialmente um dispositivo da família Max II. Anote o código desse dispositivo.

- Capture as telas solicitadas e depois utilize-as no relatório da atividade.

- Anote o tempo utilizado para cada uma das etapas do processo de compilação.

- Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo.

- Anote algum erro (Error) ou alertas (Warnings) que o Quartus II indicar no painel de mensagens [Messages]

- Ao final salve o projeto em um arquivo QAR (sugestão PJ1.QAR)

- Observe as mudanças que ocorrem tanto no tipo de Elemento Lógico disponível, no Chip Planner, no Pin Planner, e no circuito dos pinos de I/O. Note que estes FPGAs também apresenta novos componentes, tais como: Memória, Multiplicadores, DSP, PLL, DLL, etc. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documente aqueles que encontrar.

- Compare os resultados obtidos nos procedimentos do PASSO 1 e PASSO 2.

- Ao escolher a família de FPGAS, escolha um dispositivo FPGA da família Cyclone IV E. Anote o código desse dispositivo.

- Se você está com o código da AE1 - Projeto de um conversor de binário para mostrador de 7 segmentos escrito, use este código no lugar do código do cálculo da distância de Hamming

- Capture as telas mostradas no roteiro e depois utilize-as no relatório da atividade.

- Anote o tempo máximo de propagação entre as entradas e saídas.

- Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo.

- Experimente modificar as configurações do compilador, conforme mostrado em Configurando o compilador. Se desejar mude a semente inicial trocando o valor de [Seed: 1]

- Experimente inserir diferentes restrições de atraso máximo para o compilador, e analise o resultado obtido.

- Anote algum erro (Error) ou alertas (Warnings) que o Quartus II indicar no painel de mensagens [Messages]

- Ao final salve o projeto em um arquivo QAR (sugestão PJ2.QAR)

- PASSO 4: Realize a simulação funcional de: Cálculo da distância de Hamming (hamming_distance.vhd) ou Circuito conversor de binário para BCD (bin2bcd.vhd)

- Siga as passos indicados em Simulação Funcional usando o ModelSim.

- Capture as telas que mostram o circuito funcionando e depois utilize-as no relatório da atividade.

- Anote algum erro (Error) ou alertas (Warnings) que o Modelsim indicar no painel de mensagens [Messages]

- Ao final salve o projeto em um arquivo QAR (sugestão PJ3.QAR)

- Entregas

- Envie um arquivo QAR contendo todos os arquivos necessário para compilar cada um dos projetos.

- Envie um relatório em PDF, incluindo as imagens capturadas (inclua um título para cada figura) e escreva para cada imagem um texto comentando o que representa. O relatório também deve ter a identificação (autor, título, data) uma breve introdução e uma conclusão. A descrição dos procedimentos feita na página wiki não precisa incluída no relatório.

- Use preferencialmente o Overleaf para gerar o relatório. Mas o uso de MS-Word, Libreoffice e Google Docs também é permitida.

- A entrega será feita através do Moodle da disciplina. Observe o prazo de entrega.

|

4.3 AE3 - Programação do kit Mercurio IV

| AE3 - Programação do kit Mercurio IV

|

- Objetivos

- Apreender como programar um FPGA usando um kit de desenvolvimento

- Baseado na AE1 - Projeto de um conversor de binário para mostrador de 7 segmentos, implementar o projeto em VHDL.

- Descrever um circuito que você projetou em VHDL, implentá-lo e testá-lo.

- Fazer as adaptações necessárias para que o circuito projetado funcione no kit escolhido

- Testar o circuito, e anotar os resultados.

- Procedimento de laboratório

- Passo 1 - Descrevendo o hardware e fazendo a Análise e Síntese

- Abra o projeto do conversor de binário para mostrador de 7 segmentos (já simulado em aula anterior)

- Fazer a análise e síntese e corrigir eventuais erros.

-- A bibliteca std e o pacote standard são autodeclarados, então as linhas abaixo podem ser comentadas com "--"

--library std;

--use std.standard.all;

entity BCD2SSD is

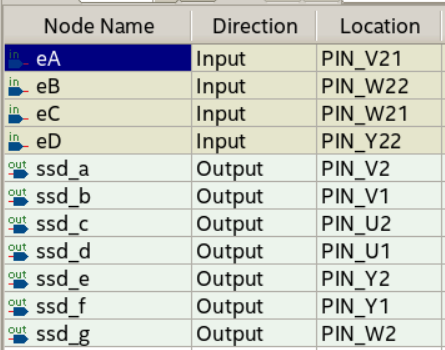

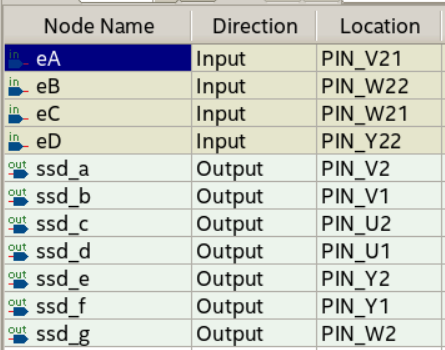

port (

-- Entradas ABCD do circuito

eA, eB, eC, eD: in bit;

-- Saidas para os leds do mostrador de 7 segmentos. Note que o nome a, b, .. g foi mudado para ssd_a, ssd_b, ... ssd_g pois o VHDL é insensível a caixa

ssd_a, ssd_b, ssd_c, ssd_d, ssd_e, ssd_f, ssd_g : out bit

);

end entity;

architecture ifsc_v1 of BCD2SSD is

begin

-- descreva a expressão lógica obtida para cada uma das saídas;

-- Por exemplo: se for a = A + C + (B'.D') + (B.D)

ssd_a <= eA or eC or (not eB and not eD) or (eB and eD);

ssd_g <= ;

end architecture;

- Passo 2 - Configurando o dispositivo e os pinos a serem utilizados

Veja os detalhes em Preparando para gravar o circuito lógico no FPGA. Após escolher o kit a ser usado no projeto, é necessário informar ao Quartus II a família e o dispositivo (device) que será utilizado

- para DE2-115 {Assignments > Device... > Device family (Family: [Cyclone IV E], Name filter: [EP4CE115F29C7] ) > [OK]}

- para MERCÚRIO IV {Assignments > Device... > Device family (Family: [Cyclone IV E], Name filter: [EP4CE30F23C7] ) > [OK]}

Após selecionar o dispositivo faça uma nova [Analysis and Synthesis].

Para evitar que saídas de circuitos da placa sejam ligadas ao terra através do FPGA, defina como alta impedância o estado dos pinos não utilizados no projeto.

- {Assignments > Device... > Device and Pin Options... > Category: Unused Pins > Reserve all unused pins: [As input tri-stated] > [OK] > [OK]}

Atribua os pinos conforme a necessidade do projeto.

- Uso do Pin Planner {Assignments > Pin Planner} no modo tabela. Digite o número do pino na coluna {Location}. Apenas posições válidas são aceitas.

| Signal

|

Name FPGA

|

Pin No. Description

|

I/O Standard

|

| SW[0] |

PIN_V21 |

Chave tipo Slide Switch 3 |

3.3V

|

| SW[1] |

PIN_W22 |

Chave tipo Slide Switch 2 |

3.3V

|

| SW[2] |

PIN_W21 |

Chave tipo Slide Switch 1 |

3.3V

|

| SW[3] |

PIN_Y22 |

Chave tipo Slide Switch 0 |

3.3V

|

- Configurar como entrada os seguintes pinos:

eA Y22

eB W21

eC W22

eD V21

- Observe a tabela com a pinagem dos display (mostrador de sete segmentos) disponíveis neste kit.

| Signal

|

Name FPGA

|

Pin No. Description

|

I/O Standard

|

| DISP0_D[0] |

PIN_V2 |

Segmento A - Display 0 |

3.3V

|

| DISP0_D[1] |

PIN_V1 |

Segmento B - Display 0 |

3.3V

|

| DISP0_D[2] |

PIN_U2 |

Segmento C - Display 0 |

3.3V

|

| DISP0_D[3] |

PIN_U1 |

Segmento D - Display 0 |

3.3V

|

| DISP0_D[4] |

PIN_Y2 |

Segmento E - Display 0 |

3.3V

|

| DISP0_D[5] |

PIN_Y1 |

Segmento F - Display 0 |

3.3V

|

| DISP0_D[6] |

PIN_W2 |

Segmento G - Display 0 |

3.3V

|

- Configure como saída do FPGA os seguintes pinos:

ssd_a V2

ssd_b V1

ssd_c U2

ssd_d U1

ssd_e Y2

ssd_f Y1

ssd_g W2

- A final do processo, o Pin Planner {Assignments > Pin Planner} deverá mostrar a correta pinagem conforme exemplificado na figura abaixo:

Uma vez completada a configuração e pinagem, execute o Fitter (Place & Route). Após a compilação a mensagem de warning "Critical Warning (XXXXX): No exact pin location assignment(s) for XX pins of XX total pins" não deverá mais ser mostrada. Caso seja mostrada verifique qual o pino que não foi configurado corretamente e corrija.

- Passo 3 - Programando o FPGA

Veja o procedimento de como deve ser feita a programação do FPGA em Programando o FPGA através da USB-Blaster

- Passo 4 - Testes de validação

- Realizar os seguintes testes, acionando as chaves A, B, C e D e observando o resultado no mstrador de sete segmentos:

- Carregar nas chaves os valores binários de 0 ("0000") a 9 ("1001") e observar se o valor mostrado é o desejado.

- Carregar nas chaves os valores binários de 10 ("1010") a 15 ("1111") e observar se o que é mostrado.

- Anote todos os resultados

| Digito

|

ABCD

|

ssd_a

|

ssd_b

|

ssd_c

|

ssd_d

|

ssd_e

|

ssd_f

|

ssd_g

|

Mostrador

|

| 0 |

0000 |

|

|

|

|

|

|

|

|

| 1 |

0001 |

|

|

|

|

|

|

|

|

| 2 |

0010 |

|

|

|

|

|

|

|

|

| 3 |

0011 |

|

|

|

|

|

|

|

|

| 4 |

0100 |

|

|

|

|

|

|

|

|

| 5 |

0101 |

|

|

|

|

|

|

|

|

| 6 |

0110 |

|

|

|

|

|

|

|

|

| 7 |

0111 |

|

|

|

|

|

|

|

|

| 8 |

1000 |

|

|

|

|

|

|

|

|

| 9 |

1001 |

|

|

|

|

|

|

|

|

| A |

1010 |

|

|

|

|

|

|

|

|

| B |

1011 |

|

|

|

|

|

|

|

|

| C |

1100 |

|

|

|

|

|

|

|

|

| D |

1101 |

|

|

|

|

|

|

|

|

| E |

1110 |

|

|

|

|

|

|

|

|

| F |

1111 |

|

|

|

|

|

|

|

|

- Relatório Técnico

- Documentar o experimento em um relatório técnico que contenha no mínimo:

- Identificação (título, disciplina, data, autores);

- Introdução;

- Descrição do procedimento realizado;

- Resultados obtidos (com imagens dos itens importantes) e análise dos resultados;

- Conclusão.

- Apêndice (se desejar pode ser disponibilizados vídeos do funcionamento do circuito no Passo 4

- O relatório deve também responder as questões levantadas e mostrar que os objetivos apresentados na introdução foram atendidos.

|

5 Referências Bibliográficas:

Curso de Engenharia de Telecomunicações