Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

(→ATUAL) |

(→ATUAL) |

||

| Linha 2 072: | Linha 2 072: | ||

* Porta paralela com N DFFs. | * Porta paralela com N DFFs. | ||

| − | |||

;Aula 30 (16 fev): | ;Aula 30 (16 fev): | ||

* Contador crescente 0-N (baseado no Ex.6.2), com N = 2^Mbits-1 (1 3 7 15) | * Contador crescente 0-N (baseado no Ex.6.2), com N = 2^Mbits-1 (1 3 7 15) | ||

| Linha 2 084: | Linha 2 083: | ||

:* Com parada no valor mínimo | :* Com parada no valor mínimo | ||

:* Com underflow no valor máximo | :* Com underflow no valor máximo | ||

| + | ====ATUAL==== | ||

| + | ;Aula 31 (17 fev): | ||

* Projetar um contador em BCD entre 0 e 99, com entrada de clock, reset e saidas unidade(0 a 9) e dezena (0 a 9). | * Projetar um contador em BCD entre 0 e 99, com entrada de clock, reset e saidas unidade(0 a 9) e dezena (0 a 9). | ||

:* versão 1 - contagem crescente. | :* versão 1 - contagem crescente. | ||

Edição das 10h14min de 17 de fevereiro de 2022

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 3 ENCONTROS

| Unidade 1 - Introdução a disciplina | ||||

|---|---|---|---|---|

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 5 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

Exemplo de descrição de um multiplexador de 4 entradas entity mux_novo is

port

(

-- Input ports

X: in bit_vector (3 downto 0);

S : in bit_vector (1 downto 0);

-- Output ports

Y : out bit

);

end entity mux_novo;

-- Implementação com lógica pura

architecture v_logica_pura of mux_novo is

begin

Y <= (X(0) and (not S(1)) and (not S(0))) or

(X(1) and (not S(1)) and (S(0))) or

(X(2) and (S(1)) and (not S(0))) or

(X(3) and (S(1)) and (S(0)));

end architecture Logica_pura;

-- Implementação com WHEN ELSE

architecture v_WHEN of mux_novo is

begin

Y <= X(0) when S = "00" else

X(1) when S = "01" else

X(2) when S = "10" else

X(3);

end architecture v_WHEN;

-- Implementação com WITH SELECT

architecture v_WITH_SELECT of mux_novo is

begin

with S select

Y <= X(0) when "00", -- note o uso da ,

X(1) when "01",

X(2) when "10",

X(3) when others; -- note o uso de others, para todos os demais valores.

-- Não pode ser substituido por "11" mesmo que o signal seja bit_vector.

end architecture v_WITH_SELECT;

-- Implementação com IF ELSE

architecture v_IF_ELSE of mux_novo is

begin

-- Uma arquitetura vazia como essa é denominada de STUB,

-- Pode ser utilizada em um projeto durante para conferir as conexões externas.

-- Posteriormente a arquitetura será descrita.

end architecture v_IF_ELSET;

-- Design Unit que associa a architecture com a entity

configuration cfg_ifsc of mux_novo is

-- for v_WITH_SELECT end for;

for v_WHEN end for;

end configuration;

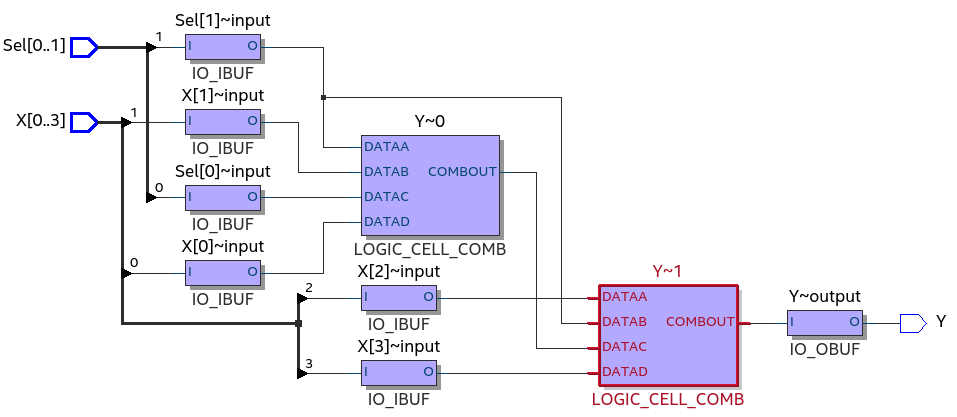

Figura 2.1 - Código RTL do mux 4x1 v_logica_pura  Figura 2.2 - Código RTL do mux 4x1 v_WHEN  Figura 2.3 - Código RTL do mux 4x1 v_WITH_SELECT

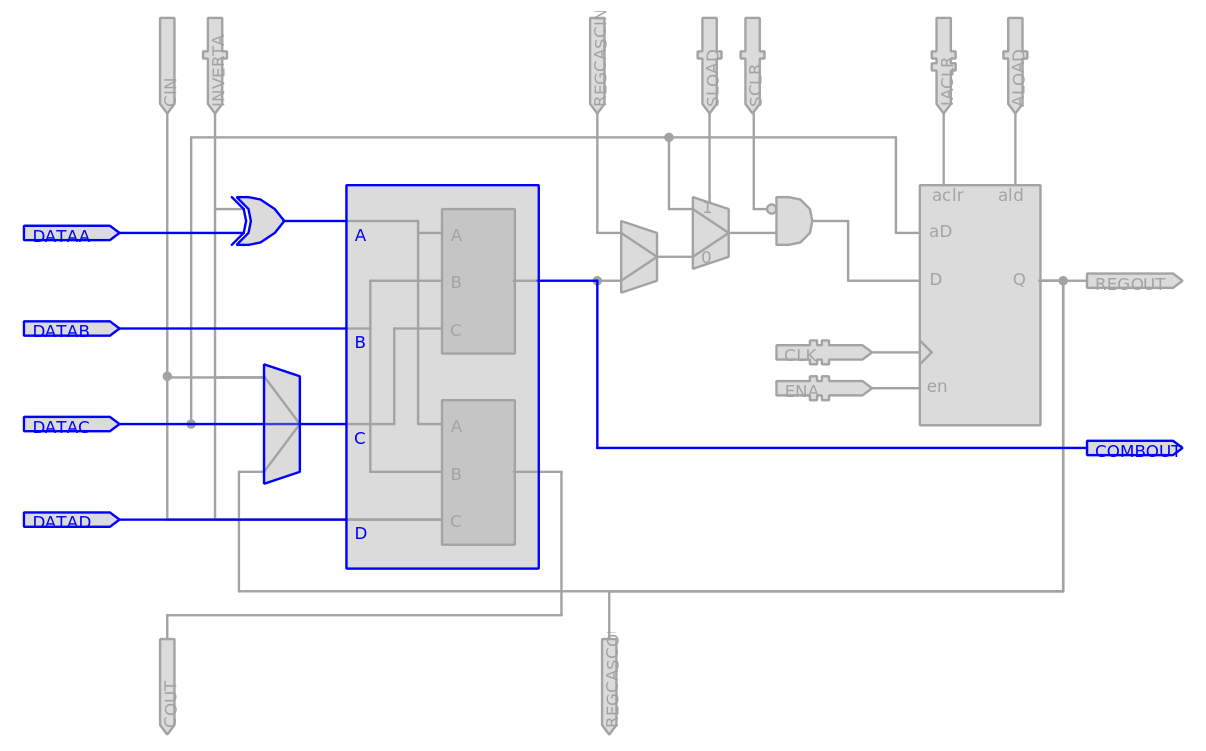

Figura 2.4 - Technology Map do mux 4x1 para a família Cyclone

Figura 2.5 - Elemento Lógico usado no mux 4x1 para a família Cyclone (node properties)

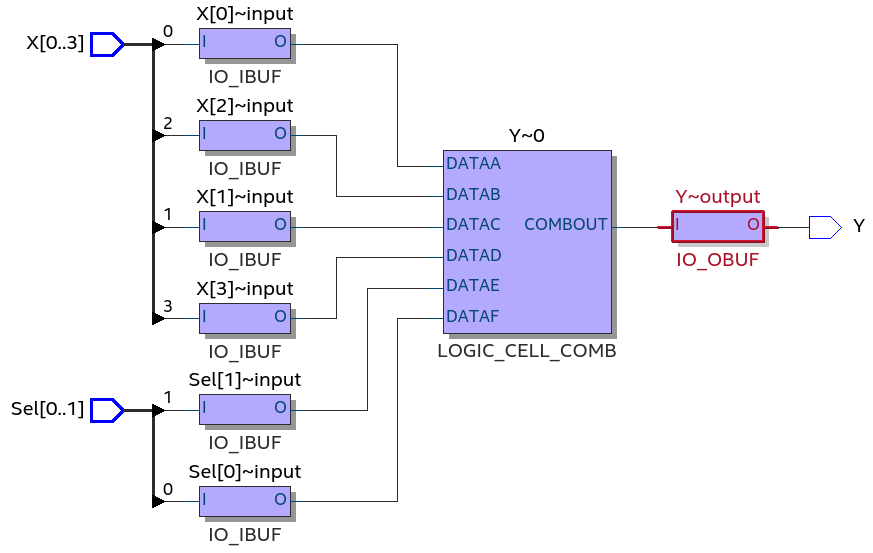

No entanto se utilizarmos um dispositivo FPGA da família Stratix III, que tem LUT tem 6 entradas, será necessário apenas 1 LE, conforme ilustrado a seguir. Figura 2.5 - Technology Map do mux 4x1 para a família Stratix III

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

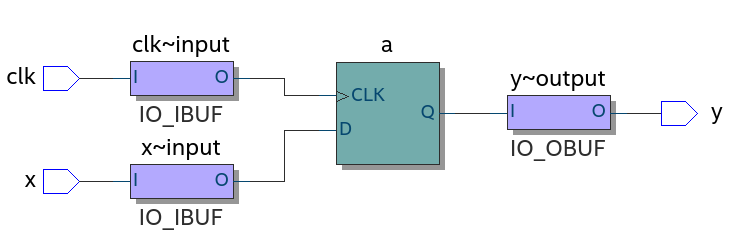

Figura 2.2 - Código RTL do Exemplo 2.2

Figura 2.3 - Technology Map do Exemplo 2.2

Figura 2.4 - Chip Planner do Exemplo 2.2

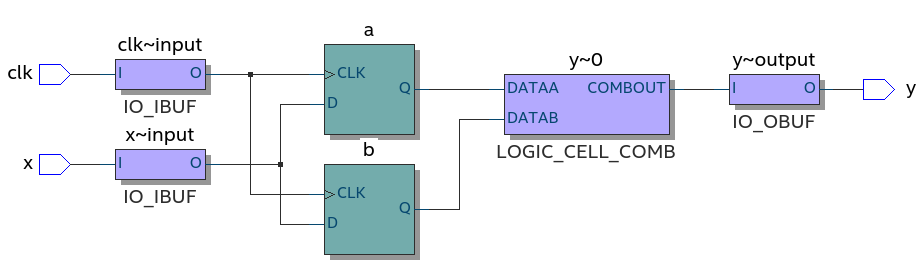

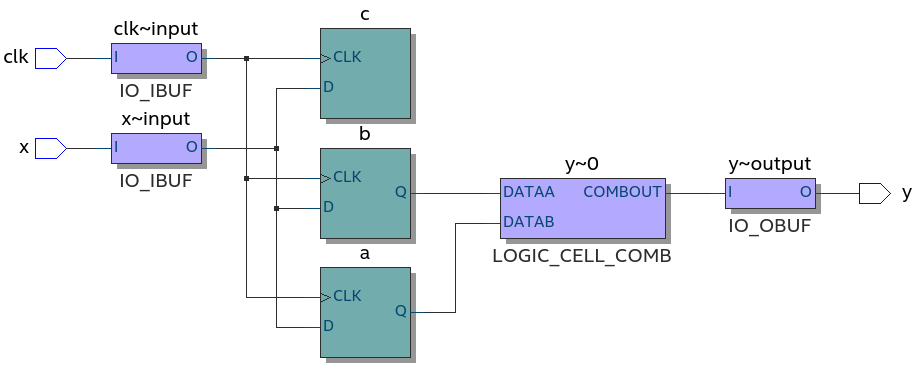

Figura 2.5 - RTL 4 FF

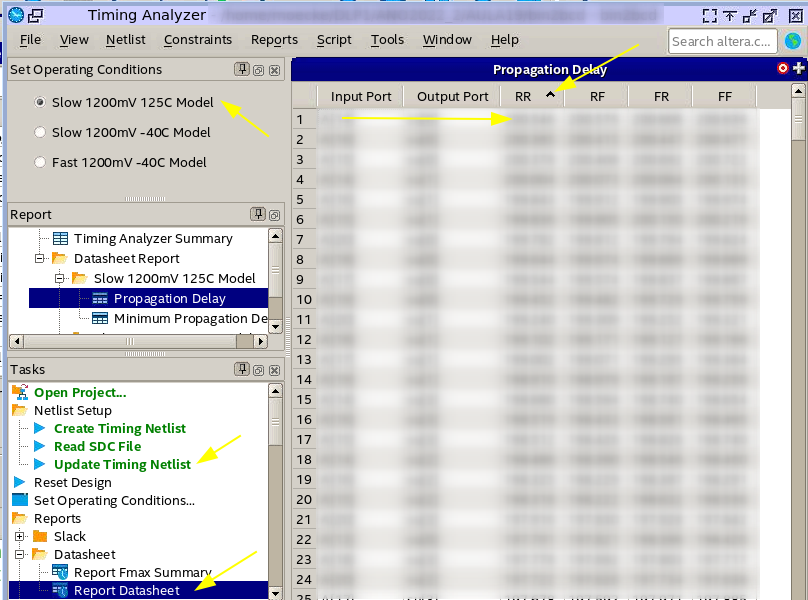

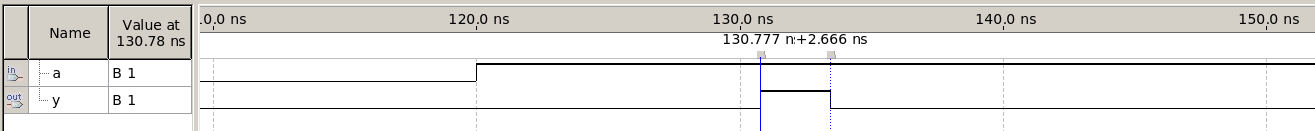

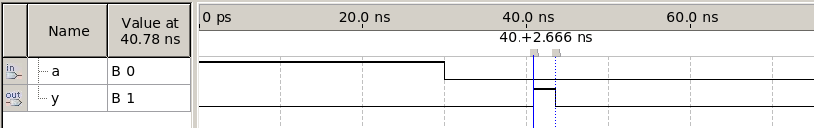

Figura 2.6 - Simulação Funcional de 4 FF 100ns  Figura 2.7 - Simulação Temporal de 4 FF 100ns  Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possível verificar se o circuito atende as restrições de tempo.

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/std

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/ieee

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/mentor/arithmetic (Mentor Graphics) ls /opt/altera/13.0sp1/quartus/libraries/vhdl/synopsys/ieee (Synopsys)

ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add_v1 IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END ENTITY;

ARCHITECTURE ifsc_v1 OF registered_comp_add_v1 IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END ARCHITECTURE;

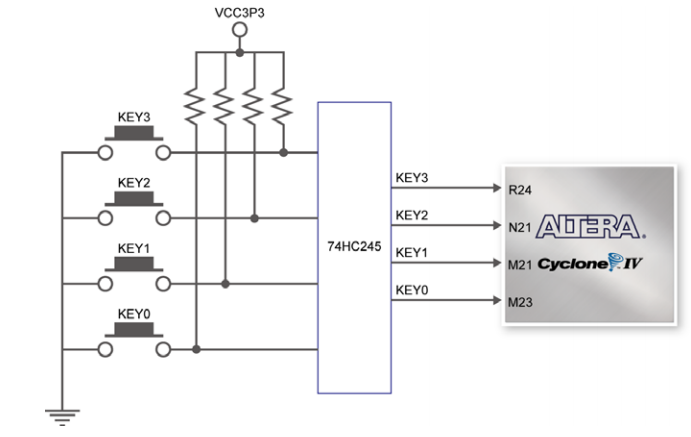

Figura 2.10 - Código RTL do Exemplo 2.3  Preparação para o Laboratório de programação de um contador. Problema do repique das chaves. Ver Dicas de como eliminar o repique das chaves mecânicas Ler sobre o problema do repique das chaves mecânicas A Guide to Debouncing

No dia 10 foram realizados os passos 1 a 2. Mas como houve um erro na definição da pinagem da chave usada para o clock, com isso, ao final do lab o circuito não funcionou. No dia 12 será refeito o circuito, testado novamente (Passo 3) e acrescentado o circuito de anti-repique sugerido |

Unidade 3 - Tipos de Dados e Operadores em VHDL

- 9 AULAS

| Unidade 3 - Tipos de Dados e Operadores em VHDL | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

-- Isso eh uma linha de comentario y <= a * b ; --o sinal y recebe o resultado da multiplicacao a x b

caracter: 'A' 'x' '#' (com aspas simples)

type string is array (positive range <>) of character;

string: "IFSC" "teste" "teste123"

elemento ("bit") único: '0' '1' 'Z' (entre aspas simples)

vetor de elementos ("bits"): "0110" "101001Z" (entre aspas duplas)

vetor de 1 elemento ("bit"): "0" "1" (entre aspas duplas)

inteiros: 5 1101 1102 (sem aspas)

0 -> '0' 7 (em base 2) -> "0111" ou b"0111" ou B"0111" 1023 (em base 2) -> "001111111111" ou b"1111111111" ou B"1111111111"

44 (em base 8) -> 5*8^1 + 4*8^0 -> O"54" ou o"54" 1023 (em base 8)-> 1*8^3 + 7*8^2 + 7*8^1 + 7*8^0 -> o"1777" 8#1777#

1023 (em base 16) -> 3*16^2 + 15*16^1 + 15*16^0 = X"3FF" ou x"3FF" 16#3FF#

1023 -> 1023 ou 1_023 1000 -> 1000 ou 1_000 ou 1E3

85 (em base 5) -> (3*5^2 + 2*5^1 + 0*5^0) -> 5#320# 1539 (em base 3) -> (2*3^2+0*3^1+1*3^0)*3^4 -> 3#201#E4

O objeto CONSTANT pode ser declarado na parte declarativa da ENTITY, ARCHITECTURE, PACKAGE, PACKAGE_BODY, BLOCK, GENERATE, PROCESS, FUNCTION e PROCEDURE. constant <constant_name> : <type> := <constant_value>;

-- Declarações comuns de constantes

constant GND : std_logic := '0';

constant VCC : std_logic := '1';

constant SSD_0 : std_logic_vector(0 to 6) := "1111110";

constant MAX : natural := 44;

O objeto SIGNAL pode ser declarado na parte declarativa da ENTITY, ARCHITECTURE, PACKAGE, BLOCK, GENERATE. Os sinais não podem ser declarados no código sequencial (PROCESS, FUNCTION e PROCEDURE), mas podem ser usados. -- Signal sem valor default

-- Para atribuir um valor a um signal use "<=" como operador.

signal <name> : <type>;

-- Signal com valor default

signal <name> : <type> := <default_value>;

-- Declarações comuns de signals

signal <name> : std_logic;

signal <name> : std_logic_vector(<msb_index> downto <lsb_index>);

signal <name> : integer;

signal <name> : integer range <low> to <high>;

O objeto VARIABLE (variável) só pode ser declarada e usada dentro do escopo no código sequencial (PROCESS, FUNCTION e PROCEDURE). -- Variables devem ser declarada em process ou subprogramas.

-- Para atribuir um valor a um variable use ":=" como operador.

-- Variable sem valor default.

variable <name> : <type>;

-- Variable com valor default.

variable <name> : <type> := <default_value>;

-- Declarações comuns de variables

variable <name> : std_logic;

variable <name> : std_logic_vector(<msb_index> downto <lsb_index>);

variable <name> : integer;

variable <name> : integer range <low> to <high>;

Exemplos de declaração de CONSTANT, SIGNAL, VARIABLE, inicializando o valor usando o agregados CONSTANT a: BIT_VECTOR(5 DOWNTO 0) := (OTHERS => '0'); -- "000000"

CONSTANT b: BIT_VECTOR(7 DOWNTO 0) := (7 => '0', OTHERS => '1'); -- "01111111"

CONSTANT c: BIT_VECTOR(7 DOWNTO 0) := (7 => '0', 6 DOWNTO 0 => '1'); -- "01111111"

CONSTANT d: BIT_VECTOR(7 DOWNTO 0) := "01111111";

SIGNAL e: STD_LOGIC_VECTOR(7 DOWNTO 0); -- Not initialized

SIGNAL f: STD_LOGIC_VECTOR(1 TO 8) := (2|3|8 => '1', 4 => 'Z', OTHERS => '0' ); -- "011Z0001"

VARIABLE g: BIT_VECTOR(1 TO 16); -- Not initialized

VARIABLE h: BIT_VECTOR(1 TO 16) := (1 TO 8 => '1', OTHERS => '0'); -- "1111111100000000"

A biblioteca standard.vhd define os tipos BIT, BIT_VECTOR, BOOLEAN, INTEGER, NATURAL, POSITIVE, CHARACTER, STRING. package standard is

type boolean is (false,true);

type bit is ('0', '1');

type severity_level is (note, warning, error, failure);

type integer is range -2147483647 to 2147483647;

type real is range -1.0E308 to 1.0E308;

type time is range -2147483648 to 2147483647

units

fs;

ps = 1000 fs;

ns = 1000 ps;

us = 1000 ns;

ms = 1000 us;

sec = 1000 ms;

min = 60 sec;

hr = 60 min;

end units;

subtype natural is integer range 0 to integer'high;

subtype positive is integer range 1 to integer'high;

type string is array (positive range <>) of character;

type bit_vector is array (natural range <>) of bit;

A biblioteca Std logic 1164.vhd define os tipos STD_(U)LOGIG, STD_(U)LOGIG_VECTOR. PACKAGE std_logic_1164 IS

TYPE std_ulogic IS ( 'U', -- Uninitialized

'X', -- Forcing Unknown

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak Unknown

'L', -- Weak 0

'H', -- Weak 1

'-' -- Don't care

);

TYPE std_ulogic_vector IS ARRAY ( NATURAL RANGE <> ) OF std_ulogic;

SUBTYPE std_logic IS resolved std_ulogic;

TYPE std_logic_vector IS ARRAY ( NATURAL RANGE <>) OF std_logic;

A biblioteca Std logic 1164.vhd ainda define algumas funções importantes como a rising_edge que determina se um sinal está na borda de subida (usado em sinais de clock). -------------------------------------------------------------------

-- conversion functions

-------------------------------------------------------------------

FUNCTION To_bit ( s : std_ulogic; xmap : BIT := '0') RETURN BIT;

FUNCTION To_bitvector ( s : std_logic_vector ; xmap : BIT := '0') RETURN BIT_VECTOR;

FUNCTION To_StdULogic ( b : BIT ) RETURN std_ulogic;

FUNCTION To_StdLogicVector ( b : BIT_VECTOR ) RETURN std_logic_vector;

-------------------------------------------------------------------

-- edge detection

-------------------------------------------------------------------

FUNCTION rising_edge (SIGNAL s : std_ulogic) RETURN BOOLEAN;

FUNCTION falling_edge (SIGNAL s : std_ulogic) RETURN BOOLEAN;

-------------------------------------------------------------------

-- edge detection

-------------------------------------------------------------------

FUNCTION rising_edge (SIGNAL s : std_ulogic) RETURN BOOLEAN IS

-- altera built_in builtin_rising_edge

BEGIN

RETURN (s'EVENT AND (To_X01(s) = '1') AND

(To_X01(s'LAST_VALUE) = '0'));

END;

A biblioteca Numeric std.vhd define os tipos UNSIGNED e SIGNED. package NUMERIC_STD is

type UNSIGNED is array (NATURAL range <>) of STD_LOGIC;

type SIGNED is array (NATURAL range <>) of STD_LOGIC;

A biblioteca Numeric std.vhd ainda define os operadores (abs, "+", "-", "*", "\", rem, mod, sll, slr, ror, rol), comparações ("=", '/=', ">", ">=", "<", "<=") e operadores lógicos (not, and, nand, or, nor, xor, xnor) para os tipos SIGNED e UNSIGNED. Além disso também define algumas funções muito utilizadas como: --============================================================================

-- RESIZE Functions

--============================================================================

function RESIZE (ARG: SIGNED; NEW_SIZE: NATURAL) return SIGNED;

function RESIZE (ARG: UNSIGNED; NEW_SIZE: NATURAL) return UNSIGNED;

--============================================================================

-- Conversion Functions

--============================================================================

function TO_INTEGER (ARG: UNSIGNED) return NATURAL;

function TO_INTEGER (ARG: SIGNED) return INTEGER;

function TO_UNSIGNED (ARG, SIZE: NATURAL) return UNSIGNED;

function TO_SIGNED (ARG: INTEGER; SIZE: NATURAL) return SIGNED;

Figura 3.1 - Simulação do indicador de vagas

Figura 3.2 - Simulação do contador de vagas

library ieee;

use ieee.std_logic_1164.all;

entity tri_state is

generic (N: NATURAL := 1);

port

(

input : in std_logic_vector(N-1 downto 0);

ena : in std_logic;

output : out std_logic_vector(N-1 downto 0);

);

end entity;

architecture tri_state of tri_state is

begin

output <= input when ena = '1' else "Z";

end architecture;

library ieee;

use ieee.std_logic_1164.all;

entity Ex3_2 is

port

(

x : in STD_LOGIC_VECTOR(1 downto 0);

y : out STD_LOGIC_VECTOR(1 downto 0)

);

end entity;

architecture un3 of Ex3_2 is

begin

y <= "00" when x = "00" else

"01" when x = "10" else

"10" when x = "01" else

"--";

end architecture;

x = "1----" -- não funciona em VHDL

std_match(x, "1----") -- funciona em VHDL

Ler e guardar a página sobre Aritmética com vetores em VDHL

Nesta aula, cada aluno deverá seguir o seguinte roteiro:

São suportados nos tipos de dados: BIT, BIT_VECTOR, BOOLEAN, STD_(U)LOGIC, STD_(U)LOGIC_VECTOR, SIGNED e UNSIGNED. Com VHDL 2008 também suportado para BOOLEAN_VECTOR, UFIXED, SFIXED e FLOAT. NOT AND NAND OR NOR XOR XNOR Apenas o operador NOT tem precedência sobre os demais y <= a AND b XOR c -- é equivalente a (a AND b) XOR c y <= NOT a AND b -- é equivalente a (NOT a) AND b. y <= a NAND b -- é equivalente a NOT (a AND b)

São suportados nos tipos de dados: INTEGER, NATURAL, POSITIVE, SIGNED e UNSIGNED. Com VHDL 2008 também suportado para UFIXED, SFIXED e FLOAT. soma (+) subtração (-) multiplicação (*) divisão (/) exponenciação (**) valor absoluto (ABS) resto (REM remainder) módulo (MOD) Não há restrições para síntese de circuitos com os operadores, exceto para "**" que necessita de expoente estático (a**5) ou base estática (5**a). O operador x/y é a divisão inteira com sinal.

O operador ABS x retorna o valor absoluto de x.

O operador x REM y retorna o resto de x/y com sinal de x. Esse operador realiza a operação x REM y = x - (x/y)*y.

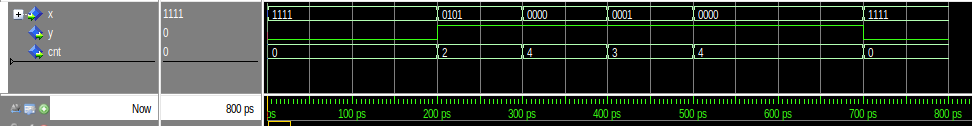

O operador x MOD y retorna o resto de x/y com sinal de y. Esse operador realiza a operação x MOD y = x REM y + a*y, onde a = 1 quando o sinal de x é diferente do sinal de y, e a = 0 se os sinais de x e y são iguais.

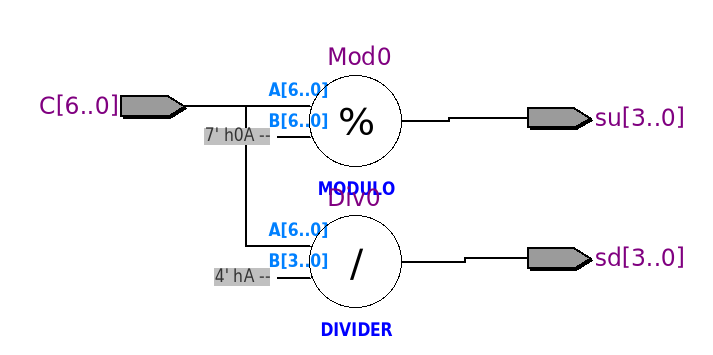

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity bin2bcd is

port

(

C : in std_logic_vector (6 downto 0);

sd, su : out std_logic_vector (3 downto 0)

);

end entity;

<!--

architecture ifsc_v1 of bin2bcd is

signal C_uns : unsigned (6 downto 0);

signal sd_uns, su_uns : unsigned (6 downto 0);

begin

sd <= std_logic_vector(resize(sd_uns, 4));

su <= std_logic_vector(resize(su_uns, 4));

sd_uns <= C_uns/10;

su_uns <= C_uns rem 10;

c_uns <= unsigned(c);

end architecture;

architecture ifsc_v2 of bin2bcd is

begin

-- Implemente o circuito usando a definição de REM que é: x REM y = x - (x/y)*y

end architecture;

configuration bin2bcd_cfg of bin2bcd is

--A instrução '''configuration''' associa a '''entity''' bin2bcd a '''architecture'''.

for ifsc_v1 end for;

--Para associar a '''entity''' bin2bcd a '''architecture''' ifsc_v2 comente a linha acima e descomente a linha abaixo.

-- for ifsc_v2 end for;

end configuration;

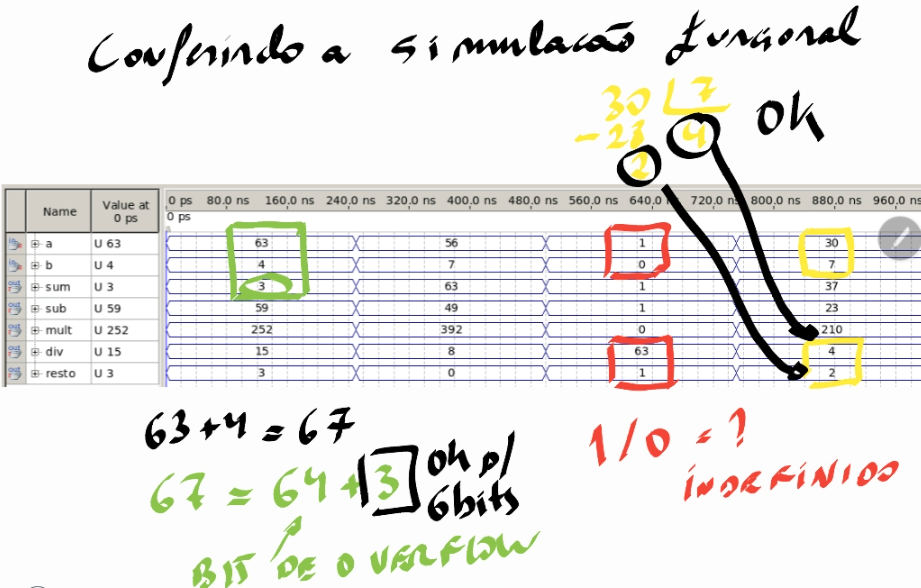

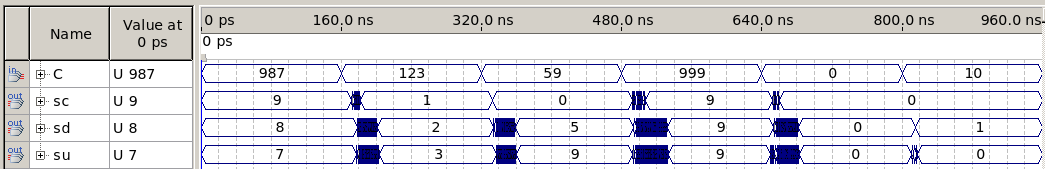

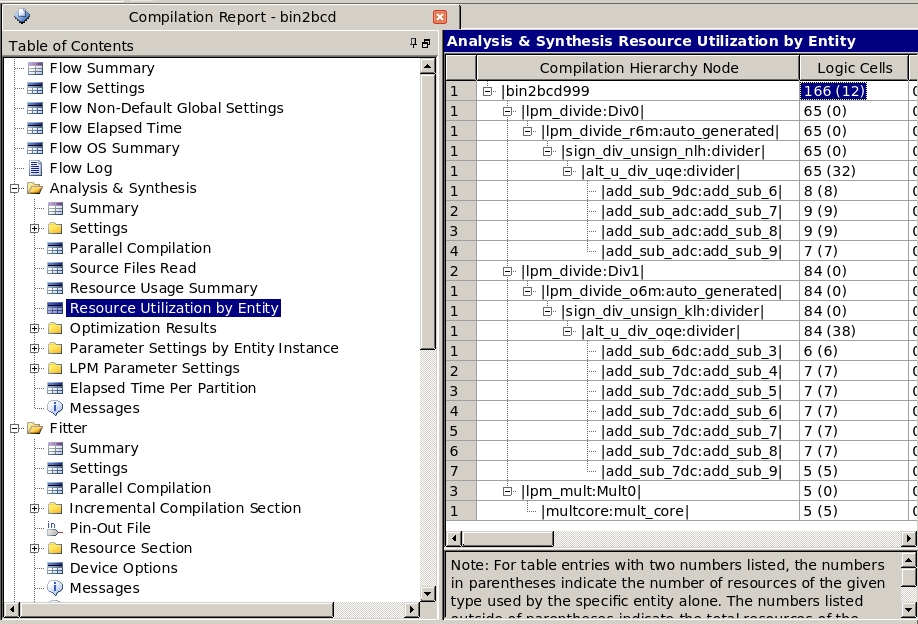

Figura 3.2 - RTL do conversor de Binário para BCD com 2 digitos  Figura 3.3 - Simulação do conversor de Binário para BCD com 2 digitos

signal a: bit_vector(7 downto 0) := "01100101"; y <= a SLL 2; -- y <= "10010100" (y <= a(5 downto 0) & "00";) y <= a SLA 2; -- y <= "10010111" (y <= a(5 downto 0) & a(0) & a(0);) y <= a ROR 2; -- y <= "01011001" (y <= a(1 downto 0) & a(7 downto 2);)

Igualdade (=) Diferença (/=) Menor que (<) Menor ou igual que (<=) Maior que (>) Maior ou igual que (>=)

Igualdade (?=) Diferença (?/=) Menor que (?<) Menor ou igual que (?<=) Maior que (?>) Maior ou igual que (?>=) Atributos em VHDL.

Em VHDL existem diversos atributos de sintese que controlam a forma como o processo de "Analysis & Synthesis" é realizado pelo Quartus II. Uma listagem completa pode ser encontrada em:

type fruit is (apple, orange, pear, mango);

attribute enum_encoding : string;

attribute enum_encoding of fruit : type is "11 01 10 00";

entity foo is

port (sel : in std_logic;

data : in std_logic_vector(3 downto 0);

o : out std_logic);

end foo;

architecture rtl of foo is

attribute chip_pin : string;

attribute chip_pin of sel : signal is "C4";

attribute chip_pin of data : signal is "D1, D2, D3, D4";

begin

-- Specify additional code

end architecture;

O uso desse atributo sobrepõe a atribuição dos pinos através da IDE do Quartus II, e por isso não é recomendável. O atributo de síntese chip_pin pode ser usado apenas em portas da entidade "top-level" do projeto. .

Atributos em VHDL.

O atributo de síntese KEEP, sinaliza ao processo de "Analysis & Synthesis" para manter intacto um determinado signal ou componente. signal a,b,c : std_logic;

attribute keep: boolean;

attribute keep of a,b,c: signal is true;

signal a,b,c : std_logic;

attribute preserve: boolean;

attribute preserve of a,b,c: signal is true;

signal reg1: std_logic;

attribute noprune: boolean;

attribute noprune of reg1: signal is true;

Para cada atributo existe uma descrição completa como mostrado a seguir. P'LEFT Kind: Value. Prefix: Any prefix P that is appropriate for an object with a scalar type or subtype T, or an alias thereof, or that denotes any scalar type or subtype T. Result type: Same type as T. Result: The left bound of T. A seguir estão listados alguns dos atributos mais utilizados.

P'LEFT - The left bound of T. P'RIGHT - The right bound of T. P'HIGH - The upper bound of T. P'LOW - The lower bound of T. P'ASCENDING - It is TRUE if T is defined with an ascending range; FALSE otherwise. P'LENGTH - maximum(0, T’POS(T’HIGH) – T’POS(T’LOW) + 1) P'RANGE - The range T'LEFT to T'RIGHT if the range of T is ascending, or the range T'LEFT downto T'RIGHT if the range of T is descending P'REVERSE_RANGE - The range T'RIGHT downto T'LEFT if the range of T is ascending, or the range T'RIGHT to T'LEFT if the range of T is descending T'POS(X) - The position number of the value of the parameter T'VAL(X) - The value whose position number is the universal_integer value corresponding to X.

A'LEFT [(N)] - Left bound of the Nth index range of A A'RIGHT [(N)] - Right bound of the Nth index range of A A'HIGH [(N)] - Upper bound of the Nth index range of A A'LOW [(N)] - Lower bound of the Nth index range of A. A'RANGE [(N)] - The range A'LEFT(N) to A'RIGHT(N) if the Nth index range of A is ascending, or the range A'LEFT(N) downto A'RIGHT(N) if the Nth index range of A is descending A'REVERSE_RANGE [(N)] - The range A'RIGHT(N) downto A'LEFT(N) if the Nth index range of A is ascending, or the range A'RIGHT(N) to A'LEFT(N) if the Nth index range of A is descending. A'LENGTH [(N)] - Number of values in the Nth index range A'ASCENDING [(N)] - TRUE if the Nth index range of A is defined with an ascending range; FALSE otherwise.

S'EVENT - A value that indicates whether an event has just occurred on signal S. S'LAST_VALUE - For a signal S, if an event has occurred on S in any simulation cycle, S'LAST_VALUE returns the value of S prior to the update of S in the last simulation cycle in which an event occurred; otherwise, S'LAST_VALUE returns the current value of S.

E'SIMPLE_NAME - The simple name, character literal, or operator symbol of the named entity

attribute attribute_name: attribute_type;

attribute attribute_name of entity_tag [signature]: entity_class is value;

A retirada de fatias (SLICES) dos ARRAYs só pode ser feita se o array foi definido com um vetor de vetores (1Dx1D ou 1Dx1Dx1D). Ainda assim é necessário respeitar a ordem dos índices do VETOR. No caso abaixo é ascendente (TO), e dentro dos limites (1 to 4). type a1Dx1D_bit is array (1 to 3) of BIT_VECTOR(1 to 4);

type a2D_bits is array (1 to 3, 1 to 4) of bit; type a3D_bits is array (1 to 3, 1 to 4, 1 to 2) of bit;

slice3 <= table(row, 1) & table(row, 2) & & table(row, 3) & & table(row, 4);

slice4 <= table(1, column) & table(2, column) & table(3, column);

gen1 : for j in 1 to 4 generate

slice3(j) <= table(row, j);

end generate;

gen2 : for i in 1 to 3 generate

slice4(i) <= table(i, column);

end generate;

-----Package:------------

-- File: my_pkg.vhd

-------------------------

package my_data_types is

type a1Dx1D_bit_vector is array (0 to 3) of BIT_VECTOR(7 downto 0);

end my_data_types;

-----Main code: --------

-- File: mux1Dx1D.vhd

-------------------------

use work.my_data_types.all;

entity mux1Dx1D is

port (

x : in a1Dx1D_bit_vector;

sel : integer range 0 to 3;

y : out BIT_VECTOR(7 downto 0)

);

end entity;

architecture pedroni of mux1Dx1D is

begin

y <= x(sel);

end architecture;

Ver pag. 60 a 73 de [2]

Enquanto que em um ARRAY todos os elementos devem ser obrigatoriamente do mesmo tipo, em um RECORD (Registro) os elementos podem ser de tipos diferentes. type memory_access is record

address : integer range 0 to 255;

block : integer range 0 to 3;

data : BIT_VECTOR(15 downto 0);

end record;

--Escrita no RECORD

constant endereco : memory_access := (34, 3, "010011110101011");

--Acesso ao RECORD

signal address_lido : integer range 0 to 255;

signal block_lido : integer range 0 to 3;

signal data_lido : bit_vector(15 downto 0);

address_lido <= endereco.address;

block_lido <= endereco.block;

data_lido <= endereco.data;

entity record_example is

port (

flag : out BIT_VECTOR(1 to 4);

sum : out natural range 0 to 15

);

end entity;

architecture record_example of record_example is

type pair is record

a, b : natural range 0 to 7;

end record;

type stack is array (1 to 4) of pair;

constant matrix : stack := ((1, 2), (3, 4), (5, 6), (7, 0));

begin

gen : for i in 1 to 4 generate

flag(i) <= '1' when matrix(i).a > matrix(i).b else '0';

end generate;

sum <= matrix(1).a + matrix(1).b;

end architecture;

A declaração de SUBTYPE é usada para restringir as declarações de TYPE. Abaixo estão alguns exemplos. subtype natural is integer range 0 to integer'HIGH;

subtype positive is integer range 1 to integer'HIGH;

subtype my_integer is integer range - 32 to 31;

A declaração ALIAS define um nome alternativo para uma entidade ou objeto. ALIAS new_name [: specifications] IS original_name [signature];

SIGNAL data_bus: STD_LOGIC_VECTOR(31 DOWNTO 0);

--bus1 is a new name for data_bus:

ALIAS bus1 IS data_bus;

--bus2 is a new name for data_bus, but with a modified range:

ALIAS bus2: STD_LOGIC_VECTOR(32 DOWNTO 1) IS data_bus;

--bus3 is another name for data_bus, with an ascending range:

ALIAS bus3: STD_LOGIC_VECTOR(1 TO 32) IS data_bus;

--upper_bus1 is a new name for the upper half of data_bus

ALIAS upper_bus1 IS data_bus(31 DOWNTO 16);

--upper_bus2 is a new name for the upper half of data_bus, but

--with a modified range:

ALIAS upper_bus2: STD_LOGIC_VECTOR(17 TO 32) IS data_bus(31 DOWNTO 16);

--lower_bus1 is a new name for the lower half of data_bus

ALIAS lower_bus1 IS data_bus(15 DOWNTO 0);

--lower_bus2 is a new name for the lower half of data_bus, but

--with a modified range:

ALIAS lower_bus2: STD_LOGIC_VECTOR(1 TO 16) IS data_bus(15 DOWNTO 0);

function ADD_UNSIGNED (L, R: UNSIGNED; C: STD_LOGIC) return UNSIGNED is

constant L_LEFT: INTEGER := L'LENGTH-1;

alias XL: UNSIGNED(L_LEFT downto 0) is L;

alias XR: UNSIGNED(L_LEFT downto 0) is R;

variable RESULT: UNSIGNED(L_LEFT downto 0);

variable CBIT: STD_LOGIC := C;

begin

for I in 0 to L_LEFT loop

RESULT(I) := CBIT xor XL(I) xor XR(I);

CBIT := (CBIT and XL(I)) or (CBIT and XR(I)) or (XL(I) and XR(I));

end loop;

return RESULT;

end ADD_UNSIGNED;

function "+" (a : integer; b : bit) return integer is

begin

if (b = '1') then return a + 1;

else

return a;

end if;

end "+";

function "+" (a : integer; b : std_logic) return integer is

begin

if (b = '1') then return a + 1;

else

return a;

end if;

end "+";

Figura 3.7 - Conversões entre tipos Integer, Unsigned, Signed, Std_logic_vector

a_UNS <= unsigned(a_SLV); a_SIG <= signed(a_SLV);

a_INT <= to_integer(a_UNS)); a_INT <= to_integer(a_SIG));

a_SLV <= std_logic_vector(a_UNS); a_SLV <= std_logic_vector(a_SIG);

a_UNS <= to_unsigned(a_INT,NBITS)); a_SIG <= to_signed(a_INT, NBITS));

function "+" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(MAX(L'LENGTH, R'LENGTH)-1 downto 0).

-- Result: Adds two UNSIGNED vectors that may be of different lengths.

function "-" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(MAX(L'LENGTH, R'LENGTH)-1 downto 0).

-- Result: Subtracts two UNSIGNED vectors that may be of different lengths.

function "*" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED((L'LENGTH+R'LENGTH-1) downto 0).

-- Result: Performs the multiplication operation on two UNSIGNED vectors

-- that may possibly be of different lengths.

function "/" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(L'LENGTH-1 downto 0)

-- Result: Divides an UNSIGNED vector, L, by another UNSIGNED vector, R.

-- NOTE: If second argument is zero for "/" operator, a severity level of ERROR is issued.

function "rem" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(R'LENGTH-1 downto 0)

-- Result: Computes "L rem R" where L and R are UNSIGNED vectors.

function "mod" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(R'LENGTH-1 downto 0)

-- Result: Computes "L mod R" where L and R are UNSIGNED vectors.

/opt/altera/13.0sp1/modelsim_ae/bin/vsim

cd /home/nome_usuario/nome_pasta/...

pwd ls

------------------------------------------------------

-- FILE : n_flip_flop.vhd

-- AUTOR: Marcos Moecke

-- DATA : 22 de dezembro de 2021

------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY n_flip_flop IS

GENERIC (N : NATURAL := 4);

PORT

(

clk : IN std_logic;

rst : IN std_logic;

d : IN std_logic_vector(N - 1 DOWNTO 0);

q : OUT std_logic_vector(N - 1 DOWNTO 0)

);

END;

ARCHITECTURE ifsc_v1 OF n_flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

q <= (OTHERS => '0');

ELSIF (clk'EVENT AND clk = '1') THEN

q <= d;

END IF;

END PROCESS;

END;

vlib work vcom -work work n_flip_flop.vhd

vsim work.n_flip_flop

Clique sobre os sinais na janela Objects e arraste-o até a janela Wave.

Selecione com o shift_clique_esquerdo do mouse os sinas d e q (barramentos de 4 bits) e em seguida clique_direito e selecione [radix > unsigned].

Use os comandos da janela de transcript para criar um arquivo tb_FF.do que permite repetir de forma automática o teste realizado. ################################

# FILE : tb_FF.do

# AUTOR: Marcos Moecke

# DATA : 14 de agosto de 2019

################################

|

Unidade 4 - Código Concorrente

- 4 AULAS

| Unidade 4 - Código Concorrente | ||

|---|---|---|

|

<optional_label>: <target> <=

<value> when <condition> else

<value> when <condition> else

<value> when <condition> else

...

<value>;

Warning (13012): Latch ... has unsafe behavior

<optional_label>: with <expression> select

<target> <=

<value> when <choices>,

<value> when <choices>,

<value> when <choices>,

...

<value> when others;

Error (10313): VHDL Case Statement error ...: Case Statement choices must cover all possible values of expression

configuration which_mux of mux4x1 is

-- for operators_only end for;

-- for operators_only_alias end for;

for with_WHEN end for;

-- for with_SELECT end for;

end configuration;

label: FOR identificador IN faixa GENERATE

[Parte_Declarativa

BEGIN]

Instruções_concorrentes

...

END GENERATE [label];

---------------------

-- FILE my_pkg.vhd --

---------------------

library ieee;

use ieee.std_logic_1164.all;

package my_pkg is

type a_slv is array(natural range <>) of std_logic_vector (3 downto 0);

end package;

---------------------------

-- FILE vector_adder.vhd --

---------------------------

library ieee work;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use work.my_pkg.all;

entity vector_adder is

generic (N : natural := 4);

port (

a : in a_slv (0 to N-1);

soma : out std_logic_vector (3 downto 0));

end entity;

-- Versão que realiza a soma diretamente, mas que precisa modificar o código de acordo com o número de entradas.

architecture ifsc_v1 of vector_adder is

signal soma_sig : signed(3 downto 0);

begin

soma_sig <= signed(a(0)) + signed(a(1)) + signed(a(2)) + signed(a(3));

soma <= std_logic_vector(soma_sig);

end architecture;

-- Versão que realiza a soma usando um FOR GENERATE

architecture ifsc_v2 of vector_adder is

begin

end architecture;

---------------------------

-- FILE vector_adder.vhd --

---------------------------

configuration ifsc_cfg of vector_adder is

-- for ifsc_v1 end for;

for ifsc_v2 end for;

end configuration;

-------------------------

-- File: bin2gray.vhd --

-------------------------

entity bin2gray is

generic (N : natural := 4 )

port

(

g : out std_logic_vector(____)

b : in std_logic_vector(____)

)

end entity

architecture ifsc_v1 of ____ is

begin

end architecture

architecture ifsc_v2 of ____ is

begin

end architecture

-------------------------

-- File: gray2bin.vhd --

-------------------------

entity gray2bin is

generic (N : natural := 4 )

port

(

g : in std_logic_vector(____)

b : out std_logic_vector(____)

)

end entity

architecture ifsc_v1 of ____ is

begin

end architecture

architecture ifsc_v2 of ____ is

begin

end architecture

----------------------

-- File: alu.vhd --

----------------------

entity alu is

generic (N : natural := 8);

port

(

a, b : in std_logic(? downto 0);

cin : in std_logic;

opcode : in std_logic(? downto 0);

y : out std_logic(? downto 0)

);

end entity;

architecture alu of alu is

begin

end architecture;

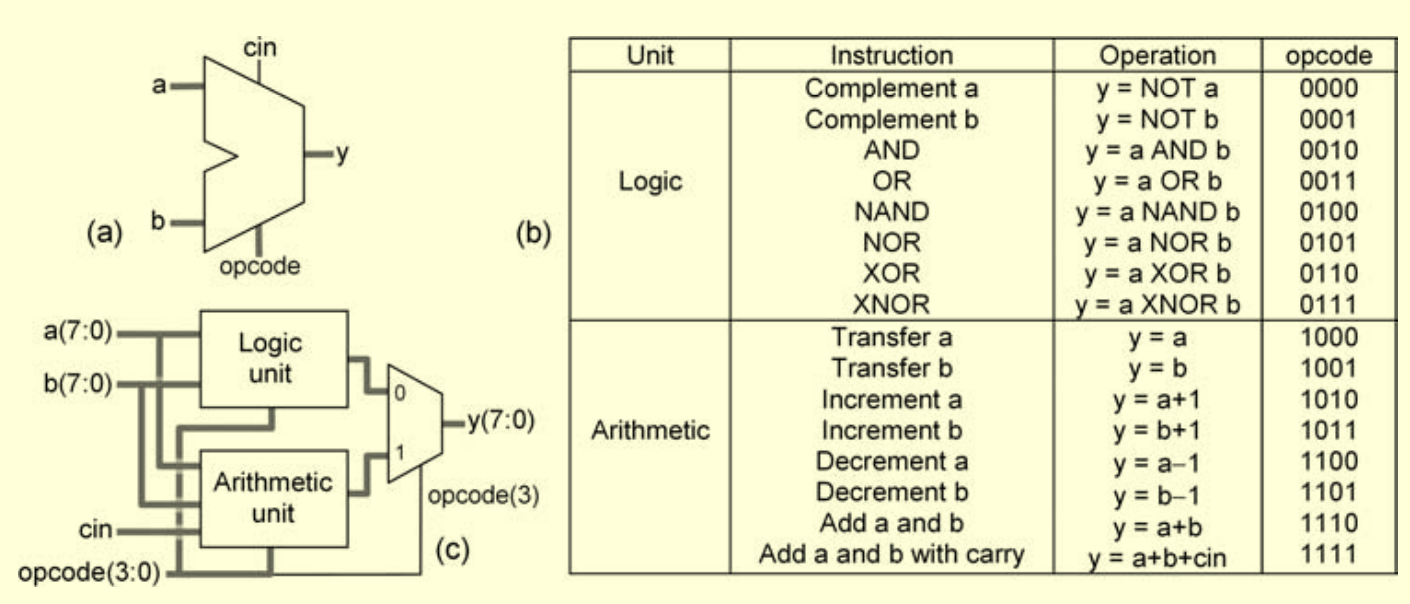

Figura 3.9 - Unidade de Lógica e Aritmética

Outros exemplos a serem estudados:

|

Unidade 5 - Código Sequencial

- 4 ENCONTROS

| Unidade 5 - Código Sequencial |

|---|

[rótulo:] PROCESS [(lista_de_sensibilidade)] [IS]

[parte_declarativa]

BEGIN

afirmação_sequencial;

afirmação_sequencial;

...

END PROCESS [rótulo];

[rótulo:] IF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSIF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSE

afirmação_sequencial;

afirmação_sequencial;

...

END IF [rótulo];

--Flip Flop tipo D com reset assincrono, sensivel a borda de subida.

process (clock,reset)

begin

if (reset = '1') then

q <= '0';

-- elsif (clock'event and clock = '1') then or

elsif (rising_edge(clock)) then

q <= d;

end if;

end process;

--Flip Flop tipo D com preset assincrono e sinal de enable, sensivel a borda de descida.

process (clock, preset)

begin

if (preset = '1') then

q <= '1';

elsif (falling_edge(clock)) then

if (enable = '1') then

q <= d;

end if;

end if;

end process;

--Latch tipo D com reset assincrono.

process (enable, reset, d)

begin

if (reset = '1') then

d <= '0';

elsif (enable='1')) then

q <= d;

end if;

end process;

-- Flip Flop tipo D com reset síncrono sensível a borda de subida.

-- Modifique a descrição para que o reset_ass seja assíncrono e reset_sinc seja síncrono.

-- Note que a função rising_edge(clock) é equivalente a (clock'event and clock'last_value = '0' and clock = '1'))

process (clock, reset)

begin

if (reset = '1') then

q <= '0';

elsif (clock'event and clock'last_value = '0' and clock = '1')) then

q <= d;

end if;

end process;

ATUAL

|

Avaliações

Nas avaliações A1 e A2 serão realizadas de forma presencial e vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

ATIVIDADE EXTRA-CLASSE (AE)

A soma das atividades Extra-classe será correspondente a 25% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle da disciplinas, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

AE1 - Palavras-cruzadas INTRODUÇÃO

| AE1 - Palavras-cruzadas INTRODUÇÃO |

|---|

|

AE2 - Conhecendo os dispositivos lógicos programáveis

| AE2 - Conhecendo os dispositivos lógicos programáveis |

|---|

|

AE3 - SNCT 2021 | 5G e Conectividade com IoT

| AE3 - SNCT 2021 |

|---|

| 5G e Conectividade com IoT |

|

Após assistir a palestra e debate do dia de hoje, seguem algumas perguntas que devem ser respondidas em um PDF.

|

AE4 - Programação do kit Mercurio IV

| AE4 - Programação do kit Mercurio IV |

|---|

entity counter is

generic (WIDTH : in natural := 4);

port (

RST : in std_logic;

CLK : in std_logic;

LOAD : in std_logic;

DATA : in std_logic_vector(WIDTH-1 downto 0);

R0 : out std_logic

Q : out std_logic_vector(WIDTH-1 downto 0));

end entity;

architecture ifsc_v1 of counter is

signal Q_aux : std_logic(WIDTH-1 downto 0);

begin

process(RST,CLK) is

begin

if RST = '1' then

Q_aux <= (others => '0');

elsif rising_edge(CLK) then

if LOAD= '1' then

Q_aux <= DATA;

else

Q_aux <= std_logic_vector(unsigned(Q_aux) + 1);

end if;

end if;

end process;

-- Adaptacao feita devido a matriz de leds acender com ZERO

Q <= not Q_aux;

-- Para acender um led eh necessario colocar ZERO na linha correspondente da matriz.

R0 <= '0';

end architecture;

CLK: PIN_Y17 ou PIN_V21 DATA[3]: PIN_H18 DATA[2]: PIN_H20 DATA[1]: PIN_K21 DATA[0]: PIN_J21 LOAD: PIN_Y22 Q[3]: PIN_J6 Q[2]: PIN_K8 Q[1]: PIN_J8 Q[0]: PIN_L8 RST: PIN_W21 R0: PIN_F10

-- insira na declaração das portas da entity a linha

LCD_BACKLIGHT: std_logic;

-- insira na architecture a linha

LCD_BACKLIGHT <= '0';

LCD_BACKLIGHT: PIN_V10

entity COUNTER_db is

...

CLK50MHz : in std_logic;

...

end entity

architecture ifsc_v2 of COUNTER_db is

...

signal CLK_db: std_logic := '0';

...

begin

-- debouncer de 10ms

process (CLK50MHz, CLK, RST, CLK_db) is

constant max_cnt: natural := 500000; -- 500000 10ms para clk 20ns

variable cnt_db : integer range 0 to max_cnt-1;

begin

if (RST = '1') then

cnt_db := 0;

CLK_db <= '0';

elsif ((CLK = '0') and (CLK_db = '0')) or

((CLK = '1') and (CLK_db = '1')) then

cnt_db := 0;

elsif (rising_edge(CLK50MHz)) then

if (cnt_db = max_cnt - 1) then

CLK_db <= not CLK_db;

else

cnt_db := cnt_db + 1;

end if;

end if;

end process;

...

-- Troque no process(RST,CLK) a entrada '''CLK''' do circuito anterior pela entrada '''CLK_db'''

CLK50MHz: PIN_T1

create_clock -name CLK50MHz -period 50MHz [get_ports -no_case {clk*}]

|

AE5 - Desafio das vagas de garagem

| AE5 - Desafio das vagas de garagem |

|---|

|

AE6 - Conversor de binário para BCD

AE7 - Estudo dos atributos de objetos e de síntese

AE8 - Estudo dos Arrays

| AE8 - Estudo dos Arrays |

|---|

entity array_1Dx1D_integer is

port (

row : in integer range 1 to 3;

slice : out integer range 0 to 15

);

end entity;

architecture teste of array_1Dx1D_integer is

type a1Dx1D_integer is array (1 to 3) of integer range 0 to 15;

constant table : a1Dx1D_integer := (15, 5, 7);

begin

slice <= table(row);

end architecture;

entity array_1Dx1D_bit is

port (

row : in integer range 1 to 3;

column : in integer range 0 to 4; --3 bits

slice1 : out bit;

slice2 : out bit_vector(1 to 2);

slice3 : out bit_vector(1 to 4);

slice4 : out bit_vector(1 to 3)

);

end entity;

architecture teste of array_1Dx1D_bit is

type a1Dx1D_bit is array (1 to 3) of bit_vector(1 to 4);

constant table : a1Dx1D_bit :=

(('1', '1', '1', '1'), --15

('0', '1', '0', '1'), -- 5

('0', '1', '1', '1')); -- 7

begin

--slice1 <= table(row)(column);

--slice2 <= table(row)(1 to 2);

--slice3 <= table(row)(1 to 4);

--slice4 <= table(1 TO 3)(column);

--slice4 <= table(1)(column) & table(2)(column) & table(3)(column);

--gen : for i in 1 to 3 generate

-- slice4(i) <= table(i)(column);

--end generate;

end architecture;

entity array_2D_bits is

port (

row : in integer range 0 to 3;

column : in integer range 0 to 4; --3 bits

slice1 : out bit;

slice2 : out BIT_VECTOR(1 to 2);

slice3 : out BIT_VECTOR(1 to 4);

slice4 : out BIT_VECTOR(1 to 3)

);

end entity;

architecture teste of array_2D_bits is

type a2D_bits is array (1 to 3, 1 to 4) of bit;

constant table : a2D_bits := (('0', '0', '0', '1'),

('1', '0', '0', '1'), ('1', '1', '0', '1')

);

begin

--slice1 <= table(row, column);

--slice2 <= table(row, 1 TO 2);

--slice3 <= table(row, 1 TO 4);

--slice4 <= table(1 TO 3, column);

--slice4 <= table(1, column) & table(2, column) & tabl

--gen : for i in 1 to 3 generate

-- slice4(i) <= table(i, column);

--end generate;

end architecture;

--Acessando uma linha de uma matriz

gen1 : for j in 1 to 4 generate

slice3(j) <= table(row, j);

end generate;

-- Acessando uma coluna de uma matriz

gen2 : for i in 1 to 3 generate

slice4(i) <= table(i, column);

end generate;

|

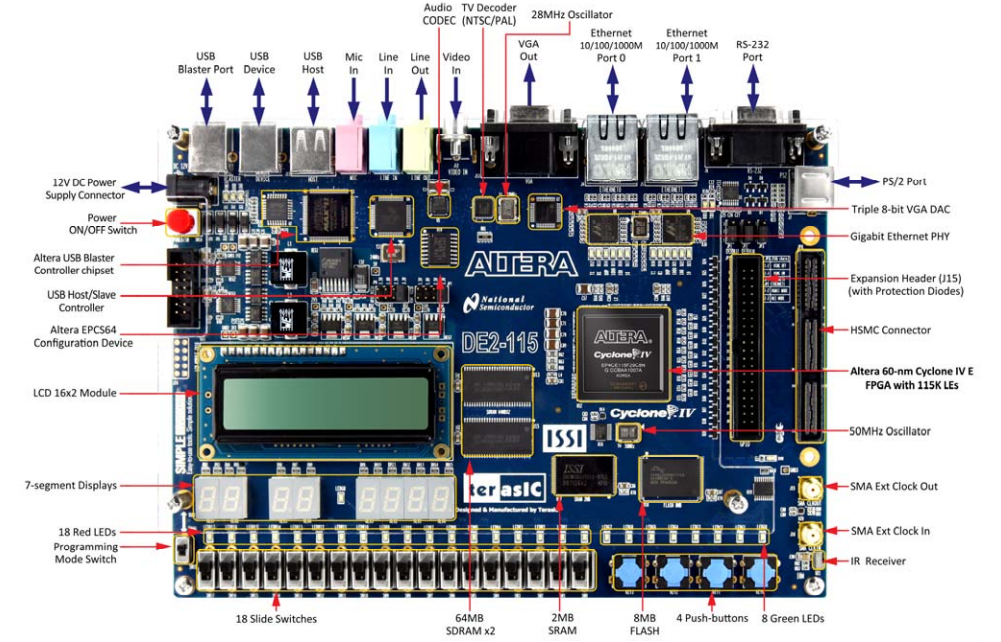

AE9 - Calculadora básica implementada no kit DE2-115

| AE9 - Calculadora básica implementada no kit DE2-115 |

|---|

|

AE10 - Simulação funcional com o ModelSim

| AE10 - Simulação funcional com o ModelSim |

|---|

PASSO 1 - Inciando o Modelsim e editando um arquivo VHDL:

/opt/altera/13.0sp1/modelsim_ae/bin/vsim

cd /home/nome_usuario/nome_pasta/.../AE10

pwd

ls

------------------------------------------------------

-- FILE : n_flip_flop.vhd

-- AUTOR: Marcos Moecke

-- DATA : 22 de dezembro de 2021

------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY n_flip_flop IS

GENERIC (N : NATURAL := 4);

PORT

(

clk : IN std_logic;

rst : IN std_logic;

d : IN std_logic_vector(N - 1 DOWNTO 0);

q : OUT std_logic_vector(N - 1 DOWNTO 0)

);

END;

ARCHITECTURE ifsc_v1 OF n_flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

q <= (OTHERS => '0');

ELSIF (clk'EVENT AND clk = '1') THEN

q <= d;

END IF;

END PROCESS;

END;

vlib work vcom -work work n_flip_flop.vhd

PASSO 2 - Simulação funcional com o Modelsim:

vsim work.n_flip_flop

wave create -pattern none -portmode in -language vhdl -range N 1 /n_flip_flop/d wave create -pattern none -portmode in -language vhdl /n_flip_flop/clk wave create -pattern none -portmode in -language vhdl /n_flip_flop/rst wave create -pattern none -portmode out -language vhdl -range 1 N /n_flip_flop/q Será aberta uma janela [Wave] na qual irão ser mostrados as 3 portas de entrada da Entity e a porta de saída. Clique sobre o sinal da porta de saída q e [Delete], pois esse sinal não será editado. Aproveite para arrastar com o mouse os sinais na janela Wave para ficarem na seguinte ordem: rst, clk, d.

Clique_direito sobre o sinal rst e selecione [Edit > Create/Modify Waveform] e escolha [Patterns = Constant], [Start Time = 0] [End Time = 3000] [Time Unit = ps] e clique em [Next], [Value = 0] e clique em [Finish]. Ou wave modify -driver freeze -pattern constant -value 0 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/rst Clique_direito sobre o sinal rst e selecione [Edit > Create/Modify Waveform] e escolha [Patterns = Constant], [Start Time = 20] [End Time = 30] [Time Unit = ps] e clique em [Next], [Value = 1] e clique em [Finish]. Ou wave modify -driver freeze -pattern constant -value 1 -starttime 20ps -endtime 30ps Edit:/n_flip_flop/rst

Clique_direito sobre o sinal clk e selecione [Edit > Create/Modify Waveform] e escolha [Patterns = Clock], [Start Time = 0] [End Time = 3000] [Time Unit = ps] e clique em [Next], [Initial Value = 1], [Clock Period = 100ps], [Duty Cycle = 50] e clique em [Finish]. Ou wave modify -driver freeze -pattern clock -initialvalue 1 -period 100ps -dutycycle 50 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/clk

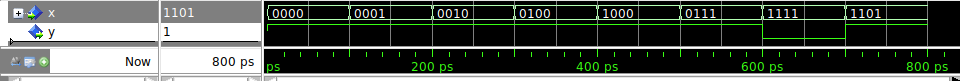

Clique_direito sobre o sinal d e selecione [Edit > Create/Modify Waveform] e escolha [Patterns = Counter], [Start Time = 0] [End Time = 1000] [Time Unit = ps] e clique em [Next], [Start Value = 0000], [End Value = 1111], [Time Period = 120ps], [Counter Type = Range], [Count Direction = Up], [Step Count = 1], [Repeat = Forever] e clique em [Finish]. Ou wave modify -driver freeze -pattern counter -startvalue 0000 -endvalue 1111 -type Range -direction Up -period 120ps -step 1 -repeat forever -range 4 1 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/d

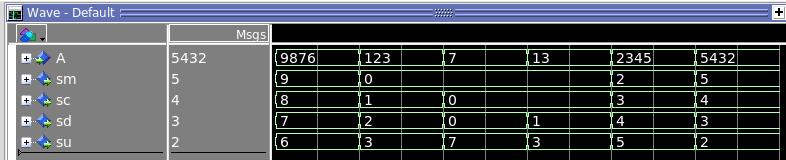

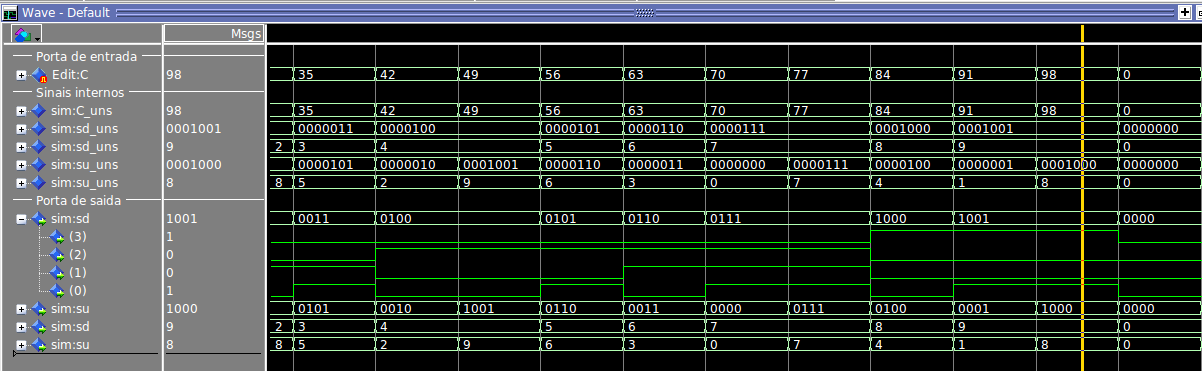

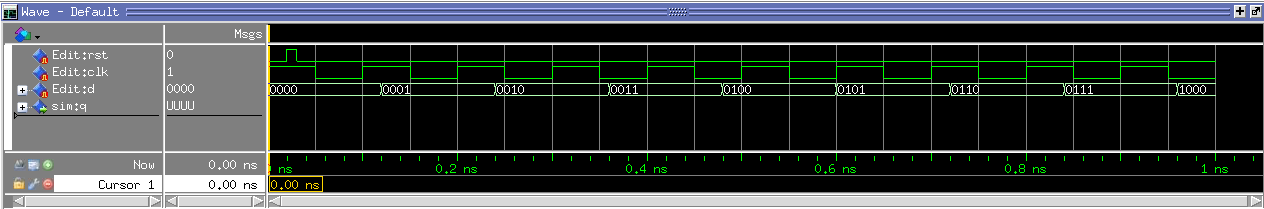

Clique sobre o sinal q na janela Objects e solte-o na janela Wave. Ao final desses passos a janela Wave deverá estar conforme mostrado abaixo: Figura AE10a - Edição do Waveform de 4 FF 1000ns no Modelsim

run -all

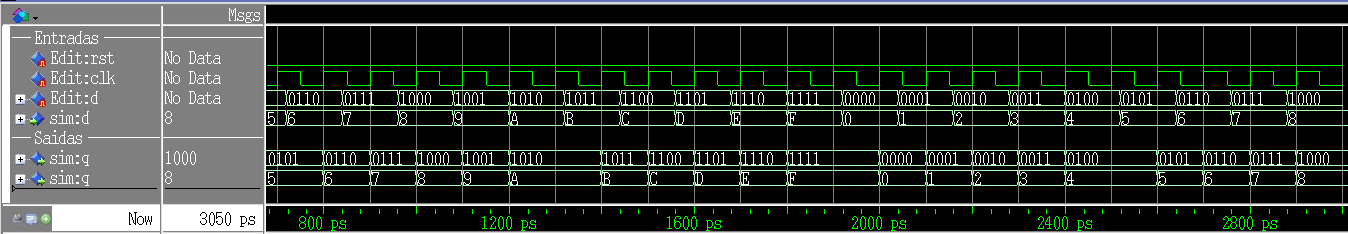

Selecione com o shift_clique_esquerdo do mouse os sinas d e q (barramentos de 4 bits) e em seguida clique_direito e selecione [radix > unsigned]. A janela Wave deverá estar conforme mostrado abaixo: Figura AE10b - Simulação funcional de 4 FF 1000ns no Modelsim

PASSO 3 - Criação de um arquivo de testbench:Use os comandos da janela de transcript para criar um arquivo tb_nFF.do que permite repetir de forma automática o teste realizado. ################################

# FILE : tb_FF_create1.do

# AUTOR: Marcos Moecke

# DATA : 14 de agosto de 2019

################################

#criacao da library work

vlib work

#compilacao da entity nome.vhd (nao necessita ser compilado no quartus II)

vcom -work work n_flip_flop.vhd

#simulacao na entity nome.vhd

vsim work.n_flip_flop

#inclusao de um divisor

add wave -noupdate -divider Entradas

#edicao do sinal rst

wave create -pattern none -portmode in -language vhdl /n_flip_flop/rst

wave modify -driver freeze -pattern constant -value 0 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/rst

wave modify -driver freeze -pattern constant -value 1 -starttime 20ps -endtime 30ps Edit:/n_flip_flop/rst

#edicao do sinal clock

wave create -pattern none -portmode in -language vhdl /n_flip_flop/clk

wave modify -driver freeze -pattern clock -initialvalue 1 -period 100ps -dutycycle 50 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/clk

#edicao do sinal d

wave create -pattern none -portmode in -language vhdl -range N 1 /n_flip_flop/d

wave modify -driver freeze -pattern counter -startvalue 0000 -endvalue 1111 -type Range -direction Up -period 120ps -step 1 -repeat forever -range 4 1 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/d

#inclusao do sinal de saida q (como UNSIGNED)

add wave -position end -radix hexadecimal sim:/n_flip_flop/d

#inclusao de um divisor

add wave -noupdate -divider Saidas

#inclusao do sinal de saida q (como BINARY)

add wave -position end sim:/n_flip_flop/q

#inclusao do sinal de saida q (como UNSIGNED)

add wave -position end -radix hexadecimal sim:/n_flip_flop/q

#Definir o zoom a ser mostrado na tela

WaveRestoreZoom {500 ps} {3000 ps}

#execucao da simulacao inteira

run -all

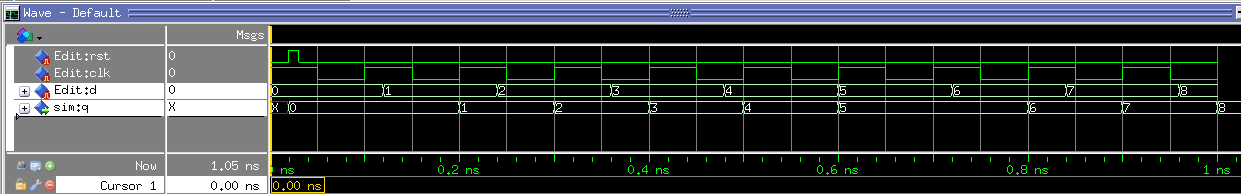

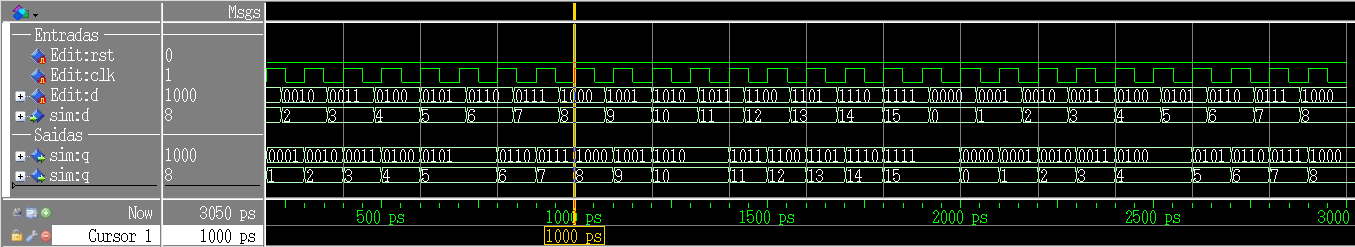

Figura AE10c - Simulação funcional no Modelsim  Se desejar reiniciar a simulação use o comando restart E em seguida execute a simulação pelo tempo que desejar run 1200 ps Uma segunda opção de criação do testbench é salvando o formato e criação do WAVE em um arquivo wave.do e executar esse script dentro do testbench. ###############################################

## FILE : wave.do

## AUTOR: Marcos Moecke

## DATA : 22 de dezembro de 2021

###############################################

onerror {resume}

quietly WaveActivateNextPane {} 0

add wave -noupdate -divider Entradas

wave clipboard store

wave create -pattern none -portmode in -language vhdl /n_flip_flop/rst

wave create -pattern none -portmode in -language vhdl /n_flip_flop/clk

wave create -pattern none -portmode in -language vhdl -range N 1 /n_flip_flop/d

wave modify -driver freeze -pattern constant -value 0 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/rst

wave modify -driver freeze -pattern constant -value 1 -starttime 20ps -endtime 30ps Edit:/n_flip_flop/rst

wave modify -driver freeze -pattern clock -initialvalue 1 -period 100ps -dutycycle 50 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/clk

wave modify -driver freeze -pattern counter -startvalue 0000 -endvalue 1111 -type Range -direction Up -period 120ps -step 1 -repeat forever -range 3 0 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/d

add wave -noupdate -radix unsigned /n_flip_flop/d

add wave -noupdate -divider Saidas

add wave -noupdate /n_flip_flop/q

add wave -noupdate -radix unsigned /n_flip_flop/q

TreeUpdate [SetDefaultTree]

WaveRestoreCursors {{Cursor 1} {1000 ps} 0}

quietly wave cursor active 1

configure wave -namecolwidth 150

configure wave -valuecolwidth 100

configure wave -justifyvalue left

configure wave -signalnamewidth 1

configure wave -snapdistance 10

configure wave -datasetprefix 0

configure wave -rowmargin 4

configure wave -childrowmargin 2

configure wave -gridoffset 0

configure wave -gridperiod 1

configure wave -griddelta 40

configure wave -timeline 0

configure wave -timelineunits ps

update

WaveRestoreZoom {0 ps} {3000 ps}

view wave

WaveCollapseAll -1

wave clipboard restore

###############################################

## FILE : tb_nFF_create2.do

## AUTOR: Marcos Moecke

## DATA : 22 de dezembro de 2021

###############################################

vlib work

vcom -reportprogress 300 -work work /home/moecke/DLP29006/ANO2021_2/AE10/n_flip_flop.vhd

vsim work.n_flip_flop

do wave.do

run -all

Figura AE10d - Simulação funcional no Modelsim  PASSO 4 - Simulação utilizando a interface gráfica com comandos force :

PASSO 5 - Conhecendo a integração do ModelSim com o Quartus II:

|

- ↑ 1,0 1,1 1,2 1,3 1,4 PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,00 2,01 2,02 2,03 2,04 2,05 2,06 2,07 2,08 2,09 2,10 2,11 2,12 2,13 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335