Mudanças entre as edições de "CIL-EngTel (página)"

| Linha 36: | Linha 36: | ||

===Circuitos Lógicos=== | ===Circuitos Lógicos=== | ||

*'''Buffer''' | *'''Buffer''' | ||

| − | :* 3-Estados - [http://www.ti.com/lit/ds/symlink/sn74ahc1g125.pdf 74AHC1G125] <small> <math> | + | :* 3-Estados - [http://www.ti.com/lit/ds/symlink/sn74ahc1g125.pdf 74AHC1G125] <small> <math> I_OL = 8 mA; I_OH = -8 mA </math></small> |

| − | :* 3-Estados e Driver - [http://www.ti.com/lit/ds/symlink/sn74ahc541.pdf 74AHC541] <small> <math> | + | :* 3-Estados e Driver - [http://www.ti.com/lit/ds/symlink/sn74ahc541.pdf 74AHC541] <small> <math> I_OL = 50 mA; I_OH = -50 mA </math></small> |

:* Dreno aberto - [http://www.ti.com/lit/ds/symlink/sn74lv07a.pdf 74LV07A] <small> The open-drain outputs require pullup resistors to perform correctly and can be connected to other open-drain outputs to implement active-low wired-OR or active-high wired-AND functions. </small> | :* Dreno aberto - [http://www.ti.com/lit/ds/symlink/sn74lv07a.pdf 74LV07A] <small> The open-drain outputs require pullup resistors to perform correctly and can be connected to other open-drain outputs to implement active-low wired-OR or active-high wired-AND functions. </small> | ||

:* Coletor aberto - [http://www.ti.com/lit/ds/symlink/sn7407.pdf 7407] | :* Coletor aberto - [http://www.ti.com/lit/ds/symlink/sn7407.pdf 7407] | ||

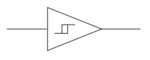

| + | [[Arquivo:Schmitt_trigger_symbol.svg |150 px]] | ||

| + | :*Schmitt trigger - [http://www.ti.com/lit/ds/symlink/sn74auc1g17.pdf SN74AUC1G17]<small> @<math> VCC = 2,3 V; V_T+ = 1,11 V; V_T- = 0,58 V </math></small> | ||

| + | ::*ver [https://en.wikipedia.org/wiki/Schmitt_trigger wikipedia] | ||

| + | ::*ver aplicações para esses circuitos [http://www.ti.com/lit/an/scea046/scea046.pdf] | ||

*'''Inversor''' - 6 Inversor - [http://www.ti.com/lit/ds/symlink/sn54als04b.pdf 74X04]; | *'''Inversor''' - 6 Inversor - [http://www.ti.com/lit/ds/symlink/sn54als04b.pdf 74X04]; | ||

*'''AND''' - 4 Porta AND2 - [http://www.ti.com/lit/ds/symlink/sn54als08.pdf 74X08], 3 Porta AND3 - [http://www.ti.com/lit/ds/symlink/sn54as11.pdf 74X11], 2 Porta AND4 - [http://www.ti.com/lit/ds/symlink/sn74als21a.pdf 74X21]. | *'''AND''' - 4 Porta AND2 - [http://www.ti.com/lit/ds/symlink/sn54als08.pdf 74X08], 3 Porta AND3 - [http://www.ti.com/lit/ds/symlink/sn54as11.pdf 74X11], 2 Porta AND4 - [http://www.ti.com/lit/ds/symlink/sn74als21a.pdf 74X21]. | ||

| Linha 47: | Linha 51: | ||

*'''XOR''' - 4 Porta XOR2 - [http://www.ti.com/lit/ds/symlink/sn74ls86a.pdf 74X86]; 4 Porta XOR2 - [http://www.ti.com/lit/ds/symlink/sn74ls386a.pdf 74X386]. | *'''XOR''' - 4 Porta XOR2 - [http://www.ti.com/lit/ds/symlink/sn74ls86a.pdf 74X86]; 4 Porta XOR2 - [http://www.ti.com/lit/ds/symlink/sn74ls386a.pdf 74X386]. | ||

*'''XNOR''' - 4 Porta XNOR2 - [http://www.ti.com/lit/ds/symlink/sn74ls266.pdf 74X266]. | *'''XNOR''' - 4 Porta XNOR2 - [http://www.ti.com/lit/ds/symlink/sn74ls266.pdf 74X266]. | ||

| − | |||

===Circuitos Lógicos Combinacionais=== | ===Circuitos Lógicos Combinacionais=== | ||

Edição das 09h21min de 27 de março de 2014

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

Carga horária, Ementas, Bibliografia, Professores

Plano de Ensino

Aulas

Software e equipamentos recomendados

Nas aulas de Circuitos Lógicos utilizaremos o Quartus II que é um EDA da ALTERA que possibilita a programação, sintese, teste e programação de dispositivos de lógica programável como os CPLDs e FPGAs. Além deste software utilizaremos também para a simulação o QSIM e o Modelsim-Altera.

Kits de desenvolvimento

- Nos links a seguir você pode consultar as informações sobre os kits Educacionais e de Desenvolvimento da ALTERA DE0-Nano,DE0, DE1, DE2-115.

- Outra opção é o uso do kit MERCURIO IV da MACNICA, que dispõe de um CYCLONE IV (EP4CE30F23). Procure no manual a pinagem dos dispositivos de entrada e saída do kit MERCURIO IV.

set_global_assignment -name FAMILY "Cyclone IV E" set_global_assignment -name DEVICE EP4CE30F23C7

- A instalação do cabo e driver USB para programação via JTAG de FPGA ALTERA deve ser feito uma vez na maquina onde será usado o programador da ALTERA (Embutido no Quartus II). Verificar o procedimento conforme o kit que você tem disponível em http://www.altera.com/download/drivers/dri-index.html.

- Para facilitar a alocação da pinagem, a Altera e a Macnica disponibilizam os arquivos de configuração .qsf para estes kits DE0_Nano.qsf, DE0.qsf, DE1.qsf, DE2_115.qsf, MERCURIO_IV.qsf.

Software Quartus II e QSIM

Procedimentos para instalação e uso estão descritos em Uso do Quartus II nos Labs do IFSC.

Configuração da USB para programação do FPGA

Para poder programar o FPGA é necessário configurar a USB-Blaster para ser utilizada através da USB. As instruções estão detalhadas em Configuração da USB para programação do FPGA via JTAG. O uso e programação do FPGA é detalhado em Programando o FPGA através da USB-Blaster.

Circuitos Integrados Comerciais

Para localizar os circuitos integrados comerciais existentes, consulte o Guia de produtos da Texas Instruments. Atualmente é muito comum o uso de circuitos integrados com uma única porta ou circuitos (ver Little Logic Guide). Nas listagens a seguir são mostrados as folhas de dados (Datasheet) de alguns circuitos comerciais, os quais também possuem uma implementação em VHDL disponível no software Quartus da ALTERA. O código 74X indica que o circuito pode estar disponível em diferentes famílias TTL e CMOS.

Um resumo das portas lógicas e demais circuitos da TI podem ser visualizados no guia de bolso. Os circuitos de 1 porta (páginas 79 a 84); de 2 portas (páginas 84 a 87); de 3 portas (páginas 87 e 88); e outros circuitos (páginas 161 a 288). Para a visualização da disponibilidade dos dispositivos lógicos nas diferentes famílias consulte a página 141 e 142.

Esta página [1] também apresenta uma rápida visualização da pinagem dos CIs mais antigos do tipo DIP.

Algumas informações muito úteis sobre as famílias lógicas, migração, níveis de tensão, encapsulamento podem ser vistas no [TI - Logic Guide http://www.ti.com/lit/sg/sdyu001z/sdyu001z.pdf].

Circuitos Lógicos

- Buffer

- 3-Estados - 74AHC1G125

- 3-Estados e Driver - 74AHC541

- Dreno aberto - 74LV07A The open-drain outputs require pullup resistors to perform correctly and can be connected to other open-drain outputs to implement active-low wired-OR or active-high wired-AND functions.

- Coletor aberto - 7407

- Schmitt trigger - SN74AUC1G17 @

- Inversor - 6 Inversor - 74X04;

- AND - 4 Porta AND2 - 74X08, 3 Porta AND3 - 74X11, 2 Porta AND4 - 74X21.

- NAND - 4 Porta NAND2 - 74X00, 3 Porta NAND3 - 74X10, 2 Porta NAND4 - 74X20; 1 Porta NAND8 - 74X30; 1 Porta NAND13 - 74X133.

- NOR - 4 Porta NOR2 - 74X02; 3 Porta NOR3 - 74X27; 2 Porta NOR5 - 74X260.

- OR - 4 Porta OR2 - 74X32.

- XOR - 4 Porta XOR2 - 74X86; 4 Porta XOR2 - 74X386.

- XNOR - 4 Porta XNOR2 - 74X266.

Circuitos Lógicos Combinacionais

- Decodificador/Demultiplexador 3 para 8 linhas - 74X138

- 2x Decodificador/Demultiplexador 2 para 4 linhas 74X139

- Decodificador/Driver BCD para Sete Segmentos - 74X47

- Decodificador/Demultiplexador 3 para 8 linhas com Latch - 74X137

- Multiplexador/Seletor de 8 para 1 - 74X151

- 2x Multiplexador/Seletor de 4 para 1 - 74X153

- 4x Multiplexador/Seletor de 2 para 1 - 74X157/158

- Decodificador BCD para 10 linhas decimais 74X42

- Codificador de Prioridade de 8 para código binário - 74X148

- Gerador de Paridade Par e Impar de 9 bits - 74X280

Circuitos Aritméticos Combinacionais

- Somador de 4 bits - 74X283

- Unidade de Lógica e Aritmética - 74X181.

- Look Ahead Carry Generator - 74X182

- Comparador BCD - 74X85

- Comparador de magnitude de 8 bits - 74X688

- Comparador de igualdade de 8 bits - 74X521

- Multiplicador binário de 4 bits por 4 bits - 74X284/285

Circuitos Sequenciais

- Registrador de deslocamento 74X164 8-bit Saída Paralela, 74X165, 74X166 8-bits Carga Parelela e saída serial, 74x194 4-Bit Bidirectional Universal Shift Registers, 74x299 8-Bit Universal Shift/Storage Registers With 3-State Outputs.

- Contador Assíncrono 74X90/92/93 - 74X90- Decada, 74X92 - Duzia, 74X93 - Binário 4 bits, 74X390 - 2x Decada,

- Contador Síncrono 74X161/163 - 74X161 - reset assíncrono, 74X163 - reset síncrono; 74X191, 74X193, 74X169 - Binario 4 bits, Up/Down

- Registradores com DFF 74X174 Hex D-type Flip-Flops With Clear, 74X273 Octal D-type Flip-Flops With Clear

Materiais de apoio as aulas

- Sistema de numeração binário

- Sistema de numeração hexadecimal

- Sistema de numeração octal

- Display de 7 segmentos

- A abstração Digital - MIT, Prof. Anant Agarwal

- Conhecendo o interior das portas lógicas - MIT, Prof. Anant Agarwal

- Tensões de entrada e saída nas familias lógicas

- A evolução do transistor MOS, [3]

- Atualmente estamos na tecnologia de 22nm, [4],já ingressando em 14 nm, [5]. No futuro qual será o tamanho do canal do GATE do transistor MOS [6]?

- O menor transistor 4nm. [7], [8]

Listas de Exercício

- Capítulo 4 (pag. 83 - 89). 4, 6-7, 10-19, 26-31.

Avaliações

- A1 - (18/03/2014)

- A2 - (29/04/2014)

- A3 - (29/04/2014)

- Projeto Final (apresentação 27/06/2014

- Recuperação (04/07/2014)

- Trabalhos e Listas de Exercícios

Aulas de Laboratório

- Uso do software Quartus e QSIM para ensino de Circuitos Lógicos

- Registrador de Deslocamento - BDF e QSIM

- Minimização de funções lógicas com mapa de Karnaugh

- Projetos Finais CIL29003

- Brainstorming de projetos CIL29003

Links auxiliares

- Sistema Binário do Egípcios

- Conversor de sistemas de numeração

- Conversores de número real para representação IEEE 754, [9], App para Iphone

- Voltage Translation Between 3.3-V, 2.5-V, 1.8-V, and 1.5-V Logic Standards, OLD - Texas Instruments.