Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

| Linha 1 856: | Linha 1 856: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| + | {{collapse top |bg=lightyellow | AE3 - SNCT 2021 | 5G e Conectividade com IoT}} | ||

===AE3 - SNCT 2021 | 5G e Conectividade com IoT=== | ===AE3 - SNCT 2021 | 5G e Conectividade com IoT=== | ||

| + | Após assistir a palestra e debate do dia de hoje, seguem algumas perguntas que devem ser respondidas em um PDF. | ||

| + | #Cite os palestrantes do evento de hoje. | ||

| + | #Dentro da parte inicial apresentada pelo ''Fabrício Sgambati'', qual foi a parte que mais te impressionou? Escreva umas 10 linhas sobre o tópico. | ||

| + | #Qual foi a tua avaliação sobre o evento de hoje? Comente o que achou. | ||

| + | #Qual dos palestrantes trouxe a informação que mais te interessou? Justifique. | ||

| + | {{collapse bottom}} | ||

{{collapse top |bg=lightyellow | AE4 - Programação do kit Mercurio IV}} | {{collapse top |bg=lightyellow | AE4 - Programação do kit Mercurio IV}} | ||

Edição das 11h10min de 2 de dezembro de 2021

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 3 ENCONTROS

| Unidade 1 - Introdução a disciplina | ||||

|---|---|---|---|---|

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 5 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

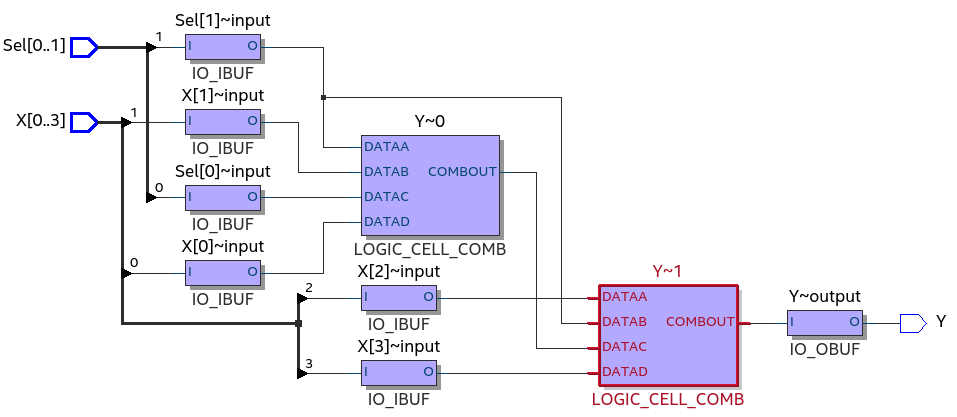

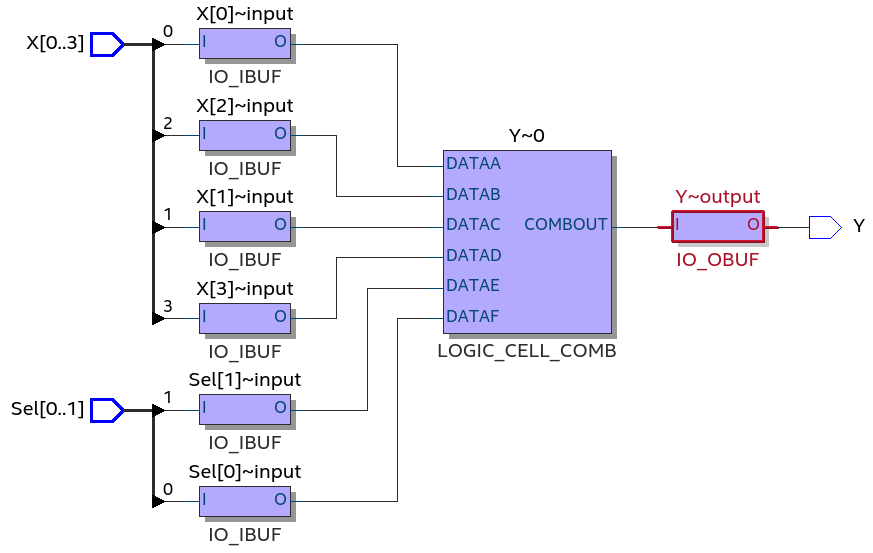

Exemplo de descrição de um multiplexador de 4 entradas entity mux_novo is

port

(

-- Input ports

X: in bit_vector (3 downto 0);

S : in bit_vector (1 downto 0);

-- Output ports

Y : out bit

);

end entity mux_novo;

-- Implementação com lógica pura

architecture v_logica_pura of mux_novo is

begin

Y <= (X(0) and (not S(1)) and (not S(0))) or

(X(1) and (not S(1)) and (S(0))) or

(X(2) and (S(1)) and (not S(0))) or

(X(3) and (S(1)) and (S(0)));

end architecture Logica_pura;

-- Implementação com WHEN ELSE

architecture v_WHEN of mux_novo is

begin

Y <= X(0) when S = "00" else

X(1) when S = "01" else

X(2) when S = "10" else

X(3);

end architecture v_WHEN;

-- Implementação com WITH SELECT

architecture v_WITH_SELECT of mux_novo is

begin

with S select

Y <= X(0) when "00", -- note o uso da ,

X(1) when "01",

X(2) when "10",

X(3) when others; -- note o uso de others, para todos os demais valores.

-- Não pode ser substituido por "11" mesmo que o signal seja bit_vector.

end architecture v_WITH_SELECT;

-- Implementação com IF ELSE

architecture v_IF_ELSE of mux_novo is

begin

-- Uma arquitetura vazia como essa é denominada de STUB,

-- Pode ser utilizada em um projeto durante para conferir as conexões externas.

-- Posteriormente a arquitetura será descrita.

end architecture v_IF_ELSET;

-- Design Unit que associa a architecture com a entity

configuration cfg_ifsc of mux_novo is

-- for v_WITH_SELECT end for;

for v_WHEN end for;

end configuration;

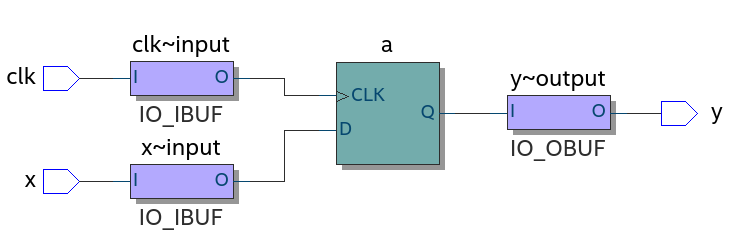

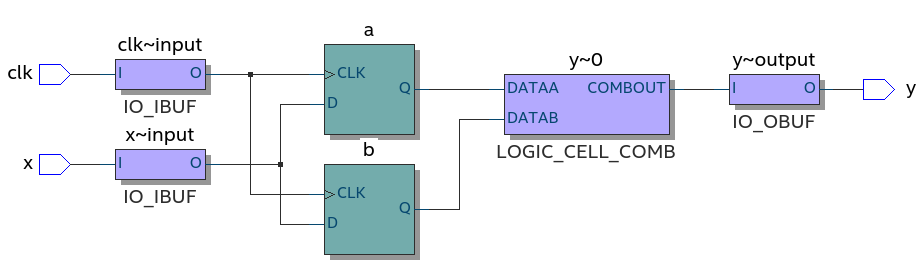

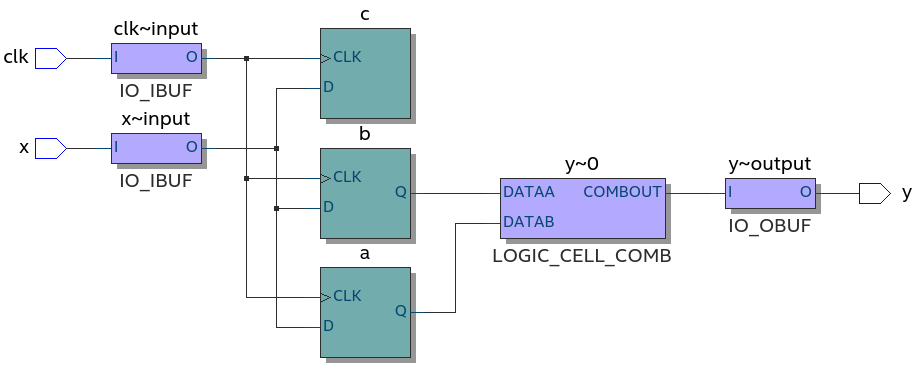

Figura 2.1 - Código RTL do mux 4x1 v_logica_pura  Figura 2.2 - Código RTL do mux 4x1 v_WHEN  Figura 2.3 - Código RTL do mux 4x1 v_WITH_SELECT

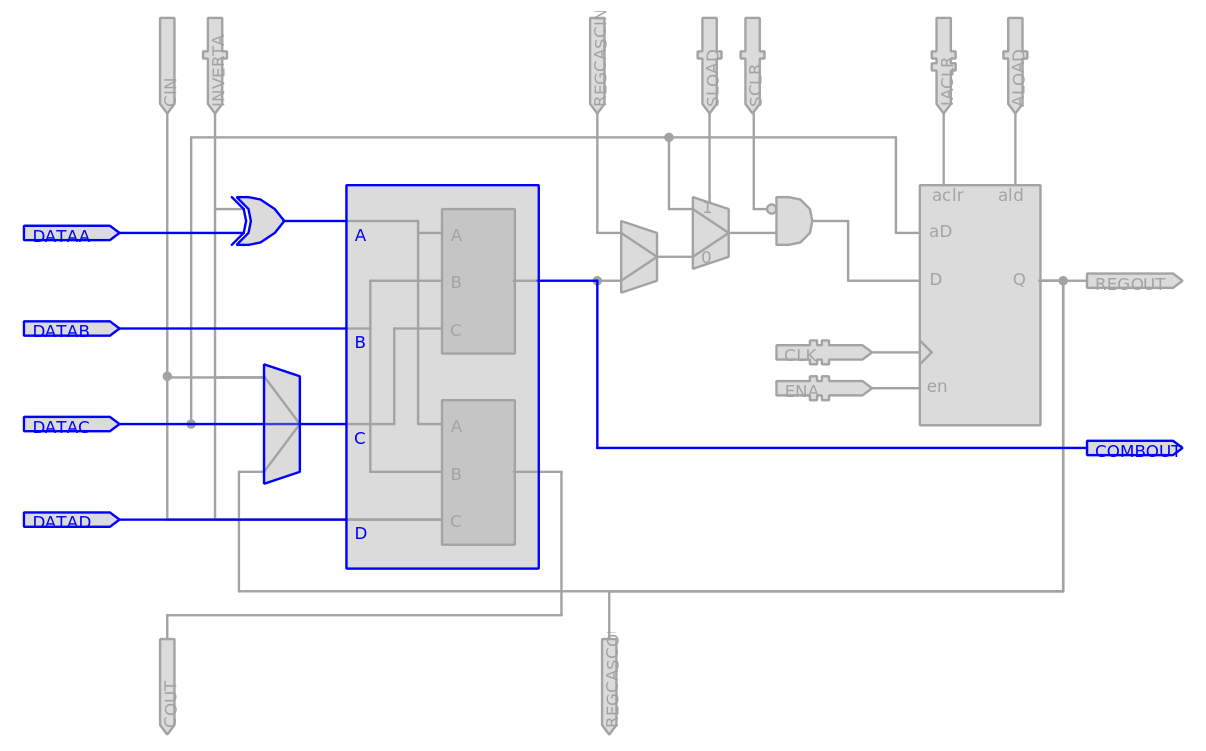

Figura 2.4 - Technology Map do mux 4x1 para a família Cyclone

Figura 2.5 - Elemento Lógico usado no mux 4x1 para a família Cyclone (node properties)

No entanto se utilizarmos um dispositivo FPGA da família Stratix III, que tem LUT tem 6 entradas, será necessário apenas 1 LE, conforme ilustrado a seguir. Figura 2.5 - Technology Map do mux 4x1 para a família Stratix III

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

Figura 2.2 - Código RTL do Exemplo 2.2

Figura 2.3 - Technology Map do Exemplo 2.2

Figura 2.4 - Chip Planner do Exemplo 2.2

Figura 2.5 - RTL 4 FF

Figura 2.6 - Simulação Funcional de 4 FF 100ns  Figura 2.7 - Simulação Temporal de 4 FF 100ns  Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possível verificar se o circuito atende as restrições de tempo.

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/std

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/ieee

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/mentor/arithmetic (Mentor Graphics) ls /opt/altera/13.0sp1/quartus/libraries/vhdl/synopsys/ieee (Synopsys)

ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add_v1 IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END ENTITY;

ARCHITECTURE ifsc_v1 OF registered_comp_add_v1 IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END ARCHITECTURE;

Figura 2.10 - Código RTL do Exemplo 2.3  Preparação para o Laboratório de programação de um contador. Problema do repique das chaves. Ver Dicas de como eliminar o repique das chaves mecânicas Ler sobre o problema do repique das chaves mecânicas A Guide to Debouncing

No dia 10 foram realizados os passos 1 a 2. Mas como houve um erro na definição da pinagem da chave usada para o clock, com isso, ao final do lab o circuito não funcionou. No dia 12 será refeito o circuito, testado novamente (Passo 3) e acrescentado o circuito de anti-repique sugerido

|

Unidade 3 - Tipos de Dados e Operadores em VHDL

- 9 AULAS

| Unidade 3 - Tipos de Dados e Operadores em VHDL | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

-- Isso eh uma linha de comentario y <= a * b ; --o sinal y recebe o resultado da multiplicacao a x b

caracter: 'A' 'x' '#' (com aspas simples)

type string is array (positive range <>) of character;

string: "IFSC" "teste" "teste123"

elemento ("bit") único: '0' '1' 'Z' (entre aspas simples)

vetor de elementos ("bits"): "0110" "101001Z" (entre aspas duplas)

vetor de 1 elemento ("bit"): "0" "1" (entre aspas duplas)

inteiros: 5 1101 1102 (sem aspas)

0 -> '0' 7 (em base 2) -> "0111" ou b"0111" ou B"0111" 1023 (em base 2) -> "001111111111" ou b"1111111111" ou B"1111111111"

44 (em base 8) -> 5*8^1 + 4*8^0 -> O"54" ou o"54" 1023 (em base 8)-> 1*8^3 + 7*8^2 + 7*8^1 + 7*8^0 -> o"1777" 8#1777#

1023 (em base 16) -> 3*16^2 + 15*16^1 + 15*16^0 = X"3FF" ou x"3FF" 16#3FF#

1023 -> 1023 ou 1_023 1000 -> 1000 ou 1_000 ou 1E3

85 (em base 5) -> (3*5^2 + 2*5^1 + 0*5^0) -> 5#320# 1539 (em base 3) -> (2*3^2+0*3^1+1*3^0)*3^4 -> 3#201#E4

O objeto CONSTANT pode ser declarado na parte declarativa da ENTITY, ARCHITECTURE, PACKAGE, PACKAGE_BODY, BLOCK, GENERATE, PROCESS, FUNCTION e PROCEDURE. constant <constant_name> : <type> := <constant_value>;

-- Declarações comuns de constantes

constant GND : std_logic := '0';

constant VCC : std_logic := '1';

constant SSD_0 : std_logic_vector(0 to 6) := "1111110";

constant MAX : natural := 44;

O objeto SIGNAL pode ser declarado na parte declarativa da ENTITY, ARCHITECTURE, PACKAGE, BLOCK, GENERATE. Os sinais não podem ser declarados no código sequencial (PROCESS, FUNCTION e PROCEDURE), mas podem ser usados. -- Signal sem valor default

-- Para atribuir um valor a um signal use "<=" como operador.

signal <name> : <type>;

-- Signal com valor default

signal <name> : <type> := <default_value>;

-- Declarações comuns de signals

signal <name> : std_logic;

signal <name> : std_logic_vector(<msb_index> downto <lsb_index>);

signal <name> : integer;

signal <name> : integer range <low> to <high>;

O objeto VARIABLE (variável) só pode ser declarada e usada dentro do escopo no código sequencial (PROCESS, FUNCTION e PROCEDURE). -- Variables devem ser declarada em process ou subprogramas.

-- Para atribuir um valor a um variable use ":=" como operador.

-- Variable sem valor default.

variable <name> : <type>;

-- Variable com valor default.

variable <name> : <type> := <default_value>;

-- Declarações comuns de variables

variable <name> : std_logic;

variable <name> : std_logic_vector(<msb_index> downto <lsb_index>);

variable <name> : integer;

variable <name> : integer range <low> to <high>;

Exemplos de declaração de CONSTANT, SIGNAL, VARIABLE, inicializando o valor usando o agregados CONSTANT a: BIT_VECTOR(5 DOWNTO 0) := (OTHERS => '0'); -- "000000"

CONSTANT b: BIT_VECTOR(7 DOWNTO 0) := (7 => '0', OTHERS => '1'); -- "01111111"

CONSTANT c: BIT_VECTOR(7 DOWNTO 0) := (7 => '0', 6 DOWNTO 0 => '1'); -- "01111111"

CONSTANT d: BIT_VECTOR(7 DOWNTO 0) := "01111111";

SIGNAL e: STD_LOGIC_VECTOR(7 DOWNTO 0); -- Not initialized

SIGNAL f: STD_LOGIC_VECTOR(1 TO 8) := (2|3|8 => '1', 4 => 'Z', OTHERS => '0' ); -- "011Z0001"

VARIABLE g: BIT_VECTOR(1 TO 16); -- Not initialized

VARIABLE h: BIT_VECTOR(1 TO 16) := (1 TO 8 => '1', OTHERS => '0'); -- "1111111100000000"

A biblioteca standard.vhd define os tipos BIT, BIT_VECTOR, BOOLEAN, INTEGER, NATURAL, POSITIVE, CHARACTER, STRING. package standard is

type boolean is (false,true);

type bit is ('0', '1');

type severity_level is (note, warning, error, failure);

type integer is range -2147483647 to 2147483647;

type real is range -1.0E308 to 1.0E308;

type time is range -2147483648 to 2147483647

units

fs;

ps = 1000 fs;

ns = 1000 ps;

us = 1000 ns;

ms = 1000 us;

sec = 1000 ms;

min = 60 sec;

hr = 60 min;

end units;

subtype natural is integer range 0 to integer'high;

subtype positive is integer range 1 to integer'high;

type string is array (positive range <>) of character;

type bit_vector is array (natural range <>) of bit;

A biblioteca Std logic 1164.vhd define os tipos STD_(U)LOGIG, STD_(U)LOGIG_VECTOR. PACKAGE std_logic_1164 IS

TYPE std_ulogic IS ( 'U', -- Uninitialized

'X', -- Forcing Unknown

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak Unknown

'L', -- Weak 0

'H', -- Weak 1

'-' -- Don't care

);

TYPE std_ulogic_vector IS ARRAY ( NATURAL RANGE <> ) OF std_ulogic;

SUBTYPE std_logic IS resolved std_ulogic;

TYPE std_logic_vector IS ARRAY ( NATURAL RANGE <>) OF std_logic;

A biblioteca Std logic 1164.vhd ainda define algumas funções importantes como a rising_edge que determina se um sinal está na borda de subida (usado em sinais de clock). -------------------------------------------------------------------

-- conversion functions

-------------------------------------------------------------------

FUNCTION To_bit ( s : std_ulogic; xmap : BIT := '0') RETURN BIT;

FUNCTION To_bitvector ( s : std_logic_vector ; xmap : BIT := '0') RETURN BIT_VECTOR;

FUNCTION To_StdULogic ( b : BIT ) RETURN std_ulogic;

FUNCTION To_StdLogicVector ( b : BIT_VECTOR ) RETURN std_logic_vector;

-------------------------------------------------------------------

-- edge detection

-------------------------------------------------------------------

FUNCTION rising_edge (SIGNAL s : std_ulogic) RETURN BOOLEAN;

FUNCTION falling_edge (SIGNAL s : std_ulogic) RETURN BOOLEAN;

-------------------------------------------------------------------

-- edge detection

-------------------------------------------------------------------

FUNCTION rising_edge (SIGNAL s : std_ulogic) RETURN BOOLEAN IS

-- altera built_in builtin_rising_edge

BEGIN

RETURN (s'EVENT AND (To_X01(s) = '1') AND

(To_X01(s'LAST_VALUE) = '0'));

END;

A biblioteca Numeric std.vhd define os tipos UNSIGNED e SIGNED. package NUMERIC_STD is

type UNSIGNED is array (NATURAL range <>) of STD_LOGIC;

type SIGNED is array (NATURAL range <>) of STD_LOGIC;

A biblioteca Numeric std.vhd ainda define os operadores (abs, "+", "-", "*", "\", rem, mod, sll, slr, ror, rol), comparações ("=", '/=', ">", ">=", "<", "<=") e operadores lógicos (not, and, nand, or, nor, xor, xnor) para os tipos SIGNED e UNSIGNED. Além disso também define algumas funções muito utilizadas como: --============================================================================

-- RESIZE Functions

--============================================================================

function RESIZE (ARG: SIGNED; NEW_SIZE: NATURAL) return SIGNED;

function RESIZE (ARG: UNSIGNED; NEW_SIZE: NATURAL) return UNSIGNED;

--============================================================================

-- Conversion Functions

--============================================================================

function TO_INTEGER (ARG: UNSIGNED) return NATURAL;

function TO_INTEGER (ARG: SIGNED) return INTEGER;

function TO_UNSIGNED (ARG, SIZE: NATURAL) return UNSIGNED;

function TO_SIGNED (ARG: INTEGER; SIZE: NATURAL) return SIGNED;

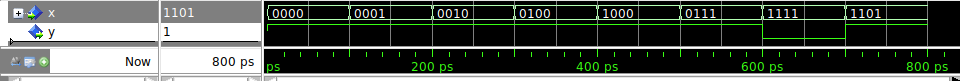

Figura 3.1 - Simulação do indicador de vagas

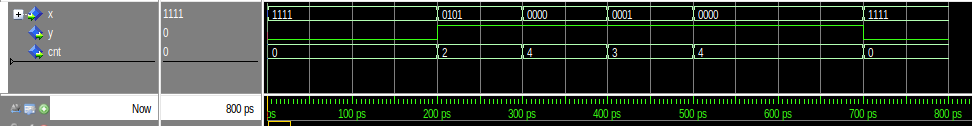

Figura 3.2 - Simulação do contador de vagas

library ieee;

use ieee.std_logic_1164.all;

entity tri_state is

generic (N: NATURAL := 1);

port

(

input : in std_logic_vector(N-1 downto 0);

ena : in std_logic;

output : out std_logic_vector(N-1 downto 0);

);

end entity;

architecture tri_state of tri_state is

begin

output <= input when ena = '1' else "Z";

end architecture;

library ieee;

use ieee.std_logic_1164.all;

entity Ex3_2 is

port

(

x : in STD_LOGIC_VECTOR(1 downto 0);

y : out STD_LOGIC_VECTOR(1 downto 0)

);

end entity;

architecture un3 of Ex3_2 is

begin

y <= "00" when x = "00" else

"01" when x = "10" else

"10" when x = "01" else

"--";

end architecture;

x = "1----" -- não funciona em VHDL

std_match(x, "1----") -- funciona em VHDL

Ler e guardar a página sobre Aritmética com vetores em VDHL

Nesta aula, cada aluno deverá seguir o seguinte roteiro:

São suportados nos tipos de dados: BIT, BIT_VECTOR, BOOLEAN, STD_(U)LOGIC, STD_(U)LOGIC_VECTOR, SIGNED e UNSIGNED. Com VHDL 2008 também suportado para BOOLEAN_VECTOR, UFIXED, SFIXED e FLOAT. NOT AND NAND OR NOR XOR XNOR Apenas o operador NOT tem precedência sobre os demais y <= a AND b XOR c -- é equivalente a (a AND b) XOR c y <= NOT a AND b -- é equivalente a (NOT a) AND b. y <= a NAND b -- é equivalente a NOT (a AND b)

São suportados nos tipos de dados: INTEGER, NATURAL, POSITIVE, SIGNED e UNSIGNED. Com VHDL 2008 também suportado para UFIXED, SFIXED e FLOAT. soma (+) subtração (-) multiplicação (*) divisão (/) exponenciação (**) valor absoluto (ABS) resto (REM remainder) módulo (MOD) Não há restrições para síntese de circuitos com os operadores, exceto para "**" que necessita de expoente estático (a**5) ou base estática (5**a). O operador x/y é a divisão inteira com sinal.

O operador ABS x retorna o valor absoluto de x.

O operador x REM y retorna o resto de x/y com sinal de x. Esse operador realiza a operação x REM y = x - (x/y)*y.

O operador x MOD y retorna o resto de x/y com sinal de y. Esse operador realiza a operação x MOD y = x REM y + a*y, onde a = 1 quando o sinal de x é diferente do sinal de y, e a = 0 se os sinais de x e y são iguais.

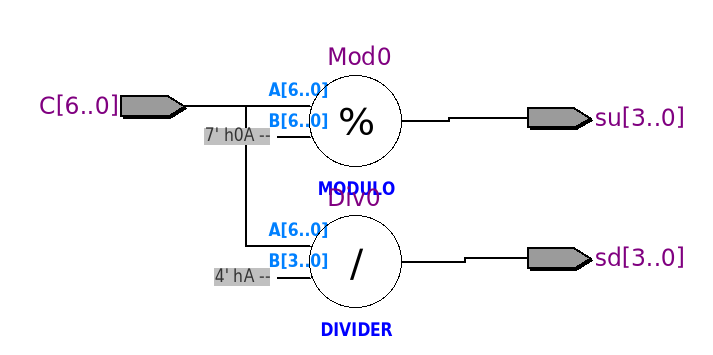

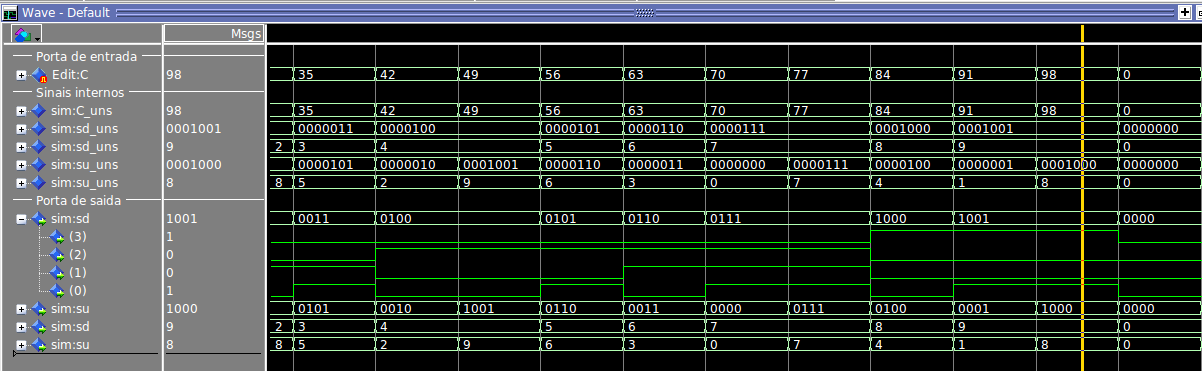

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity bin2bcd is

port

(

C : in std_logic_vector (6 downto 0);

sd, su : out std_logic_vector (3 downto 0)

);

end entity;

<!--

architecture ifsc_v1 of bin2bcd is

signal C_uns : unsigned (6 downto 0);

signal sd_uns, su_uns : unsigned (6 downto 0);

begin

sd <= std_logic_vector(resize(sd_uns, 4));

su <= std_logic_vector(resize(su_uns, 4));

sd_uns <= C_uns/10;

su_uns <= C_uns rem 10;

c_uns <= unsigned(c);

end architecture;

architecture ifsc_v2 of bin2bcd is

begin

-- Implemente o circuito usando a definição de REM que é: x REM y = x - (x/y)*y

end architecture;

configuration bin2bcd_cfg of bin2bcd is

--A instrução '''configuration''' associa a '''entity''' bin2bcd a '''architecture'''.

for ifsc_v1 end for;

--Para associar a '''entity''' bin2bcd a '''architecture''' ifsc_v2 comente a linha acima e descomente a linha abaixo.

-- for ifsc_v2 end for;

end configuration;

Figura 3.2 - RTL do conversor de Binário para BCD com 2 digitos  Figura 3.3 - Simulação do conversor de Binário para BCD com 2 digitos

signal a: bit_vector(7 downto 0) := "01100101"; y <= a SLL 2; -- y <= "10010100" (y <= a(5 downto 0) & "00";) y <= a SLA 2; -- y <= "10010111" (y <= a(5 downto 0) & a(0) & a(0);) y <= a ROR 2; -- y <= "01011001" (y <= a(1 downto 0) & a(7 downto 2);)

Igualdade (=) Diferença (/=) Menor que (<) Menor ou igual que (<=) Maior que (>) Maior ou igual que (>=)

Igualdade (?=) Diferença (?/=) Menor que (?<) Menor ou igual que (?<=) Maior que (?>) Maior ou igual que (?>=) Atributos em VHDL.

Em VHDL existem diversos atributos de sintese que controlam a forma como o processo de "Analysis & Synthesis" é realizado pelo Quartus II. Uma listagem completa pode ser encontrada em:

type fruit is (apple, orange, pear, mango);

attribute enum_encoding : string;

attribute enum_encoding of fruit : type is "11 01 10 00";

entity foo is

port (sel : in std_logic;

data : in std_logic_vector(3 downto 0);

o : out std_logic);

end foo;

architecture rtl of foo is

attribute chip_pin : string;

attribute chip_pin of sel : signal is "C4";

attribute chip_pin of data : signal is "D1, D2, D3, D4";

begin

-- Specify additional code

end architecture;

O uso desse atributo sobrepõe a atribuição dos pinos através da IDE do Quartus II, e por isso não é recomendável. O atributo de síntese chip_pin pode ser usado apenas em portas da entidade "top-level" do projeto. . ATUAL

Atributos em VHDL.

O atributo de síntese KEEP, sinaliza ao processo de "Analysis & Synthesis" para manter intacto um determinado signal ou componente. signal a,b,c : std_logic;

attribute keep: boolean;

attribute keep of a,b,c: signal is true;

signal a,b,c : std_logic;

attribute preserve: boolean;

attribute preserve of a,b,c: signal is true;

signal reg1: std_logic;

attribute noprune: boolean;

attribute noprune of reg1: signal is true;

Para cada atributo existe uma descrição completa como mostrado a seguir. P'LEFT Kind: Value. Prefix: Any prefix P that is appropriate for an object with a scalar type or subtype T, or an alias thereof, or that denotes any scalar type or subtype T. Result type: Same type as T. Result: The left bound of T. A seguir estão listados alguns dos atributos mais utilizados.

P'LEFT - The left bound of T. P'RIGHT - The right bound of T. P'HIGH - The upper bound of T. P'LOW - The lower bound of T. P'ASCENDING - It is TRUE if T is defined with an ascending range; FALSE otherwise. P'LENGTH - maximum(0, T’POS(T’HIGH) – T’POS(T’LOW) + 1) P'RANGE - The range T'LEFT to T'RIGHT if the range of T is ascending, or the range T'LEFT downto T'RIGHT if the range of T is descending P'REVERSE_RANGE - The range T'RIGHT downto T'LEFT if the range of T is ascending, or the range T'RIGHT to T'LEFT if the range of T is descending T'POS(X) - The position number of the value of the parameter T'VAL(X) - The value whose position number is the universal_integer value corresponding to X.

A'LEFT [(N)] - Left bound of the Nth index range of A A'RIGHT [(N)] - Right bound of the Nth index range of A A'HIGH [(N)] - Upper bound of the Nth index range of A A'LOW [(N)] - Lower bound of the Nth index range of A. A'RANGE [(N)] - The range A'LEFT(N) to A'RIGHT(N) if the Nth index range of A is ascending, or the range A'LEFT(N) downto A'RIGHT(N) if the Nth index range of A is descending A'REVERSE_RANGE [(N)] - The range A'RIGHT(N) downto A'LEFT(N) if the Nth index range of A is ascending, or the range A'RIGHT(N) to A'LEFT(N) if the Nth index range of A is descending. A'LENGTH [(N)] - Number of values in the Nth index range A'ASCENDING [(N)] - TRUE if the Nth index range of A is defined with an ascending range; FALSE otherwise.

S'EVENT - A value that indicates whether an event has just occurred on signal S. S'LAST_VALUE - For a signal S, if an event has occurred on S in any simulation cycle, S'LAST_VALUE returns the value of S prior to the update of S in the last simulation cycle in which an event occurred; otherwise, S'LAST_VALUE returns the current value of S.

E'SIMPLE_NAME - The simple name, character literal, or operator symbol of the named entity

attribute attribute_name: attribute_type;

attribute attribute_name of entity_tag [signature]: entity_class is value;

ATUAL

Avaliar a quantidade de elementos lógicos utilizadas para as diferentes versões conforme a tabela abaixo. Anote os dados de número de elementos logicos, guarde o RTL e Technology Map de cada versão. Após realizar as 8 versões, compare os resultados e documente em um relato simples, evitando duplicar as figuras que forem iguais. Analise os resultados escrevendo algum paragrafo de conclusão sobre este estudo.

Projetar um circuito gerador de pulsos que a cada transição de decida ou de subida do sinal de entrada A, gere um pulso na saída Y. Neste caso, haverá BÔNUS de 0,2 pontos na avaliação A1 para o aluno que obtiver o circuito que funcione com o menor número de elementos lógicos. Utilizem o menor dispositivo da família CYCLONE. Anote os dados de número de elementos lógicos, guarde o RTL e Technology Map do circuito. Também guarde a imagem da simulação que demonstre que o circuito funciona corretamente. Meça o tempo de duração do pulso na subida do sinal A e também na descida. Analise o resultado escrevendo um parágrafo de conclusão sobre este estudo, considerando as diferentes versões que tentou realizar. Para medir a duração dos pulsos use os cursores do simulador.

|

Avaliações

Nas avaliações A1 e A2 serão realizadas de forma presencial e vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

ATIVIDADE EXTRA-CLASSE (AE)

A soma das atividades Extra-classe será correspondente a 25% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle da disciplinas, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

| AE1 - Palavras-cruzadas INTRODUÇÃO |

|---|

AE1 - Palavras-cruzadas INTRODUÇÃO

|

| AE2 - Conhecendo os dispositivos lógicos programáveis |

|---|

AE2 - Conhecendo os dispositivos lógicos programáveis

|

| AE3 - SNCT 2021 |

|---|

| 5G e Conectividade com IoT |

AE3 - SNCT 2021 | 5G e Conectividade com IoTApós assistir a palestra e debate do dia de hoje, seguem algumas perguntas que devem ser respondidas em um PDF.

|

| AE4 - Programação do kit Mercurio IV |

|---|

AE4 - Programação do kit Mercurio IV

entity counter is

generic (WIDTH : in natural := 4);

port (

RST : in std_logic;

CLK : in std_logic;

LOAD : in std_logic;

DATA : in std_logic_vector(WIDTH-1 downto 0);

R0 : out std_logic

Q : out std_logic_vector(WIDTH-1 downto 0));

end entity;

architecture ifsc_v1 of counter is

signal Q_aux : std_logic(WIDTH-1 downto 0);

begin

process(RST,CLK) is

begin

if RST = '1' then

Q_aux <= (others => '0');

elsif rising_edge(CLK) then

if LOAD= '1' then

Q_aux <= DATA;

else

Q_aux <= std_logic_vector(unsigned(Q_aux) + 1);

end if;

end if;

end process;

-- Adaptacao feita devido a matriz de leds acender com ZERO

Q <= not Q_aux;

-- Para acender um led eh necessario colocar ZERO na linha correspondente da matriz.

R0 <= '0';

end architecture;

CLK: PIN_Y17 ou PIN_V21 DATA[3]: PIN_H18 DATA[2]: PIN_H20 DATA[1]: PIN_K21 DATA[0]: PIN_J21 LOAD: PIN_Y22 Q[3]: PIN_J6 Q[2]: PIN_K8 Q[1]: PIN_J8 Q[0]: PIN_L8 RST: PIN_W21 R0: PIN_F10

-- insira na declaração das portas da entity a linha

LCD_BACKLIGHT: std_logic;

-- insira na architecture a linha

LCD_BACKLIGHT <= '0';

LCD_BACKLIGHT: PIN_V10

entity COUNTER_db is

...

CLK50MHz : in std_logic;

...

end entity

architecture ifsc_v2 of COUNTER_db is

...

signal CLK_db: std_logic := '0';

...

begin

-- debouncer de 10ms

process (CLK50MHz, CLK, RST, CLK_db) is

constant max_cnt: natural := 500000; -- 500000 10ms para clk 20ns

variable cnt_db : integer range 0 to max_cnt-1;

begin

if (RST = '1') then

cnt_db := 0;

CLK_db <= '0';

elsif ((CLK = '0') and (CLK_db = '0')) or

((CLK = '1') and (CLK_db = '1')) then

cnt_db := 0;

elsif (rising_edge(CLK50MHz)) then

if (cnt_db = max_cnt - 1) then

CLK_db <= not CLK_db;

else

cnt_db := cnt_db + 1;

end if;

end if;

end process;

...

-- Troque no process(RST,CLK) a entrada '''CLK''' do circuito anterior pela entrada '''CLK_db'''

CLK50MHz: PIN_T1

create_clock -name CLK50MHz -period 50MHz [get_ports -no_case {clk*}]

|

| AE5 - Conversor de binário para BCD |

|---|

AE5 - Conversor de binário para BCD

Neste laboratório remoto, os alunos deverão implementar uma ou mais soluções do para um circuito conversor de binário para BCD (bin2bcd) com entrada binária variando de 0 a 999. Analise o tempo de propagação e área ocupada (número de elementos lógicos) e tente otimizar um ou os dois parâmetros. O aluno apresentar dois projetos como resultado sendo um para o menor tempo máximo de propagação e outro para menor área ocupada (número de elementos lógicos). Faça uma simulação que mostre que o circuito projetado funciona. Neste laboratório não é necessário fornecer as imagens RTL e Technology Map usadas para obter e melhorar os circuitos, nem a imagem da simulação que mostra que a versão entregue funciona. Mas no entanto o arquivo QAR entregue deve ser plenamente compilável e permitir após a Análise e Síntese e execução do arquivo de simulação VWF apresentar o resultado final. Se desejar você pode incluir os arquivos com as imagens de simulação e RTL de comprovação na entrega. Para fins de uniformização na comparação dos resultados utilizem o menor dispositivo da família CYCLONE (EP1C3T100A8).

|

| AE6 - Estudo dos atributos de objetos e de síntese | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

AE6 - Estudo dos atributos de objetos e de síntese

Neste laboratório remoto, os alunos deverão ser realizar as seguintes atividades:

Avaliar a quantidade de elementos lógicos utilizadas para as diferentes versões conforme a tabela abaixo. Anote os dados de número de elementos logicos, guarde o RTL e Technology Map de cada versão. Após realizar as 8 versões, compare os resultados e documente em um relato simples, evitando duplicar as figuras que forem iguais. Analise os resultados escrevendo algum paragrafo de conclusão sobre este estudo.

Projetar um circuito gerador de pulsos que a cada transição de decida ou de subida do sinal de entrada A, gere um pulso na saída Y. Neste caso, haverá BÔNUS de 0,2 pontos na avaliação A1 para o aluno que obtiver o circuito que funcione com o menor número de elementos lógicos. Para fins de uniformização na comparação dos resultados utilizem o menor dispositivo da família CYCLONE (EP1C3T100A8). Anote os dados de número de elementos lógicos, guarde o RTL e Technology Map do circuito. Também guarde a imagem da simulação que demonstre que o circuito funciona corretamente. Meça o tempo de duração do pulso na subida do sinal A e também na descida. Analise o resultado escrevendo um parágrafo de conclusão sobre este estudo, considerando as diferentes versões que tentou realizar. Para medir a duração dos pulsos use os cursores do simulador.

|