Mudanças entre as edições de "ELD129002-Engtelecom (Diário) - Prof. Marcos Moecke"

| (99 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 20: | Linha 20: | ||

;LER PARA O PRÓXIMO ENCONTRO: | ;LER PARA O PRÓXIMO ENCONTRO: | ||

| − | *Capítulo 1. Do Zero ao Um, seções 1.1 a 1.3 do livro [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf David Money Harris, B., & Harris Morgan Kaufman, S. L. (2013). Projeto Digital e Arquitetura de Computadores], diponibilizado gratuitamente pela www.imgtec.com. | + | *Capítulo 1. Do Zero ao Um, seções 1.1 a 1.3 do livro [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=27 David Money Harris, B., & Harris Morgan Kaufman, S. L. (2013). Projeto Digital e Arquitetura de Computadores], diponibilizado gratuitamente pela www.imgtec.com. |

{{collapse bottom}} | {{collapse bottom}} | ||

| Linha 26: | Linha 26: | ||

* 4 ENCONTROS | * 4 ENCONTROS | ||

{{collapse top | expand=true |Unidade 2 - Sistema de numeração e códigos}} | {{collapse top | expand=true |Unidade 2 - Sistema de numeração e códigos}} | ||

| − | + | ;Encontro 2 (20 fev) - Sistemas numéricos: | |

| − | ;Encontro 2 ( | ||

O ser humano precisa contar para determinar quantidades de coisas, com as quantidades ele pode fazer operações matemáticas e comparações. | O ser humano precisa contar para determinar quantidades de coisas, com as quantidades ele pode fazer operações matemáticas e comparações. | ||

*Os números permitem representar quantidades de forma simbólica. | *Os números permitem representar quantidades de forma simbólica. | ||

| Linha 61: | Linha 60: | ||

:*Exemplo: o número representado 111, corresponde a 1 quadra (2² = 4), 1 dupla (2¹ = 2) e 1 unidade (2⁰ = 1). | :*Exemplo: o número representado 111, corresponde a 1 quadra (2² = 4), 1 dupla (2¹ = 2) e 1 unidade (2⁰ = 1). | ||

:: <big> 1*2² + 1*2¹ + 1*2⁰ = 1*4 + 1*2 + 1*1 = 4 + 2 + 1 = 7 </big> | :: <big> 1*2² + 1*2¹ + 1*2⁰ = 1*4 + 1*2 + 1*1 = 4 + 2 + 1 = 7 </big> | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

*O que são bits, nibbles, bytes e word (palavra) de bits | *O que são bits, nibbles, bytes e word (palavra) de bits | ||

| Linha 104: | Linha 96: | ||

*Note no quadro acima: | *Note no quadro acima: | ||

:*o '''nibble''' corresponde ao grupo de 4 bits (meio byte) | :*o '''nibble''' corresponde ao grupo de 4 bits (meio byte) | ||

| − | :*o '''byte''' corresponde ao grupo de 8 bits | + | :*o '''byte''' corresponde ao grupo de 8 bits. Este grupo de 8 bits também é denominado de forma mais exata de '''octeto'''. |

:*a '''word''' corresponde ao grupo de 16 bits (as vezes 32 bits) | :*a '''word''' corresponde ao grupo de 16 bits (as vezes 32 bits) | ||

:*a '''double word''' corresponte ao grupo de 32 bits (as vezes 64 bits) | :*a '''double word''' corresponte ao grupo de 32 bits (as vezes 64 bits) | ||

| Linha 153: | Linha 145: | ||

|} | |} | ||

| − | Ler mais sobre [https://pt.wikipedia.org/wiki/Byte Byte] e os [https://pt.wikipedia.org/wiki/Prefixo_bin%C3%A1rio prefixos binários] na Wikipedia | + | ;PARA O PRÓXIMO ENCONTRO: |

| + | * Ler capítulo 1. Do Zero ao Um, seção 1.4 do livro [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=34 Projeto Digital e Arquitetura de Computadores], diponibilizado gratuitamente pela www.imgtec.com. | ||

| + | * Ver [https://moodle.ifsc.edu.br/pluginfile.php/311786/mod_resource/content/2/Sistemas%20num%C3%A9ricos.pdf Slides - Sistemas Numéricos] | ||

| + | * Ver mais sobre [https://pt.wikipedia.org/wiki/Byte Byte] ou [https://en.wikipedia.org/wiki/Byte Byte.en] e os [https://pt.wikipedia.org/wiki/Prefixo_bin%C3%A1rio prefixos binários] na Wikipedia | ||

| + | |||

| + | ;Encontro 3 (22 fev): | ||

| + | ;Conversão de bases entre sistemas numéricos: | ||

| + | *Conversão entre os sistemas de numeração '''decimal - binário - hexadecimal'''. | ||

| + | :*ver os [https://moodle.ifsc.edu.br/pluginfile.php/311786/mod_resource/content/2/Sistemas%20num%C3%A9ricos.pdf#page=15 slides - Sistemas Numéricos (conversão entre sistemas)] | ||

| + | |||

| + | *Regra geral de conversão de valor para qualquer sistema de numeração | ||

| + | :* Dividir o valor (número) pela base e obter o '''quociente''' e o '''resto'''. | ||

| + | :* Dividir sucessivas vezes o quociente anterior até obter um quociente nulo. | ||

| + | :* Os restos obtidos são os digitos que representam o valor (número) no novo sistema de numeração. | ||

| + | :* O primeiro resto obtido é o '''dígito menos significativo'''. | ||

| + | :* O último resto obtido é o '''dígito mais significativo'''. | ||

| + | |||

| + | *Regra geral de conversão de um sistema de numeração qualquer de base N para decimal | ||

| + | :* Verifique a posição do ponto decimal. | ||

| + | :* Os dígitos a esquerda do ponto decimal correspondem as posições 0, 1, 2, … . | ||

| + | :* Se houver dígitos a direita do ponto decimal, eles correspondem as posições -1, -2, -3, … . | ||

| + | :* A cada dígito é dado um peso correspondente ao valor da base elevada ao expoente N<sup>posição</sup>. | ||

| + | :* Multiplique os pesos pelos dígitos correspondentes. | ||

| + | :* O valor final (em decimal) é a soma dos valores obtidos. | ||

| + | {| class="wikitable" style="text-align:center;" | ||

| + | |- style="font-weight:bold;" | ||

| + | !style="width: 15%;" | posição | ||

| + | !style="width: 10%;" | k | ||

| + | !style="width: 7%;" | … | ||

| + | !style="width: 10%;" | 2 | ||

| + | !style="width: 10%;" | 1 | ||

| + | !style="width: 10%;" | 0 | ||

| + | !style="width: 3%;" | , | ||

| + | !style="width: 10%;" | -1 | ||

| + | !style="width: 10%;" | -2 | ||

| + | !style="width: 7%;" | … | ||

| + | !style="width: 10%;" | -l | ||

| + | |- | ||

| + | | style="font-weight:bold;" | dígito | ||

| + | | d<sub>k</sub> | ||

| + | | | ||

| + | | d<sub>2</sub> | ||

| + | | d<sub>1</sub> | ||

| + | | d<sub>0</sub> | ||

| + | | | ||

| + | | d<sub>-1</sub> | ||

| + | | d<sub>-2</sub> | ||

| + | | | ||

| + | | d<sub>-l</sub> | ||

| + | |- | ||

| + | | style="font-weight:bold;" | peso | ||

| + | | N<sup>k</sup> | ||

| + | | | ||

| + | | N<sup>2</sup> | ||

| + | | N<sup>1</sup> | ||

| + | | N<sup>0</sup> | ||

| + | | | ||

| + | | N<sup>-1</sup> | ||

| + | | N<sup>-2</sup> | ||

| + | | | ||

| + | | N<sup>-l</sup> | ||

| + | |- | ||

| + | | style="font-weight:bold;" | somar | ||

| + | | d<sub>k</sub> × N<sup>k</sup> | ||

| + | | | ||

| + | | d<sub>2</sub> × N<sup>2</sup> | ||

| + | | d<sub>1</sub> × N<sup>1</sup> | ||

| + | | d<sub>0</sub> × N<sup>0</sup> | ||

| + | | | ||

| + | | d<sub>-1</sub> × N<sup>-1</sup> | ||

| + | | d<sub>-2</sub> × N<sup>-2</sup> | ||

| + | | | ||

| + | | d<sub>-l</sub> × N<sup>-l</sup> | ||

| + | |- | ||

| + | | style="font-weight:bold;" | valor | ||

| + | | colspan="10" style="font-weight:bold;" | d<sub>k</sub> × N<sup>k</sup> + d<sub>2</sub> × N<sup>2</sup> + d<sub>1</sub> × N<sup>1</sup> + d<sub>0</sub> × N<sup>0</sup> + d<sub>-1</sub> × N<sup>-1</sup> + d<sub>-2</sub> × N<sup>-2</sup> + d<sub>-l</sub> × N<sup>-l</sup> | ||

| + | |} | ||

;Códigos numéricos binários: | ;Códigos numéricos binários: | ||

| − | *Número sem sinal (UNSIGNED) | + | *Número sem sinal ('''UNSIGNED''') |

:Neste caso apenas números inteiros naturais podem ser representados. | :Neste caso apenas números inteiros naturais podem ser representados. | ||

:Usando <math> N </math> bits é possível representar números inteiros no intervalo de <math> [0, 2^{N}-1] </math>. | :Usando <math> N </math> bits é possível representar números inteiros no intervalo de <math> [0, 2^{N}-1] </math>. | ||

| Linha 299: | Linha 367: | ||

|} | |} | ||

| − | *Número com sinal (Complemento de 2 ou SIGNED) | + | *Número com sinal (Complemento de 2 ou '''SIGNED''') |

:Neste caso o msb corresponde ao peso negativo, de modo que ao colocar 1 no msb o número inteiro passa a ser negativo, e se o msb for 0, o número será positivo. | :Neste caso o msb corresponde ao peso negativo, de modo que ao colocar 1 no msb o número inteiro passa a ser negativo, e se o msb for 0, o número será positivo. | ||

:Usando <math> N </math> bits é possível representar números inteiros no intervalo de <math> [-2^{N-1}, 2^{N-1}-1] </math>. Nesta representação existem apenas um zero. | :Usando <math> N </math> bits é possível representar números inteiros no intervalo de <math> [-2^{N-1}, 2^{N-1}-1] </math>. Nesta representação existem apenas um zero. | ||

| Linha 408: | Linha 476: | ||

| − | Comparação das representações | + | ;Comparação das representações: |

| + | O quadro abaixo mostra as representações em binário dos valores de +15 a -8 no sistema sem sinal ('''UNSIGNED'''), com signal-magnitude , com sinal em complemento de um , com sinal em complemento de dois ('''SIGNED'''). No quadro é importante notar que sempre os números negativos tem o msb = 1. Adicionalmente alguns sistemas possuem dois zeros (+0 e -0). No tipo SIGNED note que o valor máximo positivo será menor que o valor absoluto do mínimo negativo, por uma unidade. | ||

| + | |||

{| class="wikitable" style="text-align:center;" | {| class="wikitable" style="text-align:center;" | ||

|- style="font-weight:bold;" | |- style="font-weight:bold;" | ||

| Linha 578: | Linha 648: | ||

*Para obter o número negativo em complemento de um deve-se complementar (inverter) todos os bits do número binário positivo. | *Para obter o número negativo em complemento de um deve-se complementar (inverter) todos os bits do número binário positivo. | ||

*Para obter o número negativo em complemento de dois deve-se: a) obter o complemento de um (complementar (inverter) todos os bits do número binário positivo ); b) somar 1 ao resultado. | *Para obter o número negativo em complemento de dois deve-se: a) obter o complemento de um (complementar (inverter) todos os bits do número binário positivo ); b) somar 1 ao resultado. | ||

| − | *Para obter o número negativo em sinal-magnitude é necessário apenas adicionar um bit 1 a esquerda do | + | *Para obter o número negativo em sinal-magnitude é necessário apenas adicionar um bit 1 a esquerda do msb. |

*Note que em todos os casos a representação de números com sinal, sempre implica na necessidade de um bit a mais. | *Note que em todos os casos a representação de números com sinal, sempre implica na necessidade de um bit a mais. | ||

| − | 13 (decimal) = | + | 13 (decimal) = 1101 (binário sem sinal) |

| − | -13 (decimal) = | + | +13 (decimal) = '''0'''1101 (binário em sinal-magnitude) |

| − | -13 (decimal) = 10010 + | + | -13 (decimal) = '''1'''1101 (binário em sinal-magnitude) |

| − | -13 (decimal) = | + | +13 (decimal) = '''0'''1101 (binário em complemento de um) |

| + | -13 (decimal) = '''10010''' (binário em complemento de um) | ||

| + | +13 (decimal) = '''0'''1101 (binário em complemento de dois) | ||

| + | -13 (decimal) = '''10011''' = 10010 + 1 (binário em complemento de dois) | ||

| + | |||

| + | ;PARA O PRÓXIMO ENCONTRO: | ||

| + | * Iniciar a resolução dos [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=74 Exercícios 1.7 ao 1.49 Capítulo 1 - Projeto Digital e Arquitetura de Computadores] | ||

| + | |||

| + | ;Encontro 4 (27 fev): | ||

;Código ASCII: | ;Código ASCII: | ||

O código '''ASCII''' (''American Standard Code for Information Interchange''), é um padrão de codificação de caracteres para comunicação digital. Ele tem apenas 128 pontos de código, sendo 95 são caracteres imprimíveis e os demais são não imprimíveis (em azul no quadro abaixo), sendo usados para diversos controles de equipamentos eletrônicos. Atualmente esse código está sendo substituido pelos códigos '''UNICODE''', que tem milhões de pontos de código, mas nos UNICODE os primeiros 128 são iguais ao conjunto ASCII. | O código '''ASCII''' (''American Standard Code for Information Interchange''), é um padrão de codificação de caracteres para comunicação digital. Ele tem apenas 128 pontos de código, sendo 95 são caracteres imprimíveis e os demais são não imprimíveis (em azul no quadro abaixo), sendo usados para diversos controles de equipamentos eletrônicos. Atualmente esse código está sendo substituido pelos códigos '''UNICODE''', que tem milhões de pontos de código, mas nos UNICODE os primeiros 128 são iguais ao conjunto ASCII. | ||

| Linha 783: | Linha 861: | ||

*A letra "a" é representado pelo número hexadecimal 61, o que corresponde a 01100001 em binário | *A letra "a" é representado pelo número hexadecimal 61, o que corresponde a 01100001 em binário | ||

*O espaço "SP" é representado pelo número hexadecimal 20, o que corresponde a 00100000 em binário | *O espaço "SP" é representado pelo número hexadecimal 20, o que corresponde a 00100000 em binário | ||

| − | Descubra o que está escrito | + | |

| − | + | Descubra o que está escrito neste código binário onde cada 8 bits correspondem a um simbolo ASCII: | |

01000010 01101111 01101101 00100000 01100100 01101001 01100001 00100000 01110000 01100101 01110011 01110011 01101111 01000001 01001100 01001100 | 01000010 01101111 01101101 00100000 01100100 01101001 01100001 00100000 01110000 01100101 01110011 01110011 01101111 01000001 01001100 01001100 | ||

| − | |||

;Código UNICODE: | ;Código UNICODE: | ||

| Linha 796: | Linha 873: | ||

*O processo reverso pode ser feito usando [https://onlineutf8tools.com/convert-code-points-to-utf8 code points to utf8 converter] | *O processo reverso pode ser feito usando [https://onlineutf8tools.com/convert-code-points-to-utf8 code points to utf8 converter] | ||

| − | |||

| − | |||

*Outros códigos binários: | *Outros códigos binários: | ||

:* '''Gray''' - É um código em que dois valores consecutivos diferem em apenas um bit. Isso é útil para minimizar erros de leitura em sistemas eletrônicos, já que a transição entre estados ocorre com uma única mudança de bit, facilitando a detecção de erros. | :* '''Gray''' - É um código em que dois valores consecutivos diferem em apenas um bit. Isso é útil para minimizar erros de leitura em sistemas eletrônicos, já que a transição entre estados ocorre com uma única mudança de bit, facilitando a detecção de erros. | ||

| Linha 803: | Linha 878: | ||

::*Em código binário convencional o número adjacente a 0111 (7) é o 1000 (8), mudança em 4 bits. | ::*Em código binário convencional o número adjacente a 0111 (7) é o 1000 (8), mudança em 4 bits. | ||

::*Em código Gray o número adjacente a 0100 (7) é o 1100 (8), mudança de apenas 1 bit. | ::*Em código Gray o número adjacente a 0100 (7) é o 1100 (8), mudança de apenas 1 bit. | ||

| + | |||

:* '''One-hot''' - Neste código cada valor é representado por uma única posição ativa (ALTO) dentro do conjunto de bits, enquanto todas as outras posições estão inativas (BAIXO). Esse código é frequentemente usado em sistemas digitais para representar estados discretos, como em máquinas de estados finitos, e também na geração de sinais de seleção de múltiplos circuitos tais como memórias. A vantagem principal reside na simplicidade da detecção de um único estado ativo, evitando ambiguidades e permitindo uma implementação eficiente em hardware. | :* '''One-hot''' - Neste código cada valor é representado por uma única posição ativa (ALTO) dentro do conjunto de bits, enquanto todas as outras posições estão inativas (BAIXO). Esse código é frequentemente usado em sistemas digitais para representar estados discretos, como em máquinas de estados finitos, e também na geração de sinais de seleção de múltiplos circuitos tais como memórias. A vantagem principal reside na simplicidade da detecção de um único estado ativo, evitando ambiguidades e permitindo uma implementação eficiente em hardware. | ||

| + | |||

:* '''Johnson''' - Neste código é gerado deslocando-se sucessivamente todos os bits para a esquerda e colocando o bit complementar do msb como lsb. A codificação normalmente começa com todos bits "0". Devido a sua simplicidade, ele é utilizado para contadores utilizados em controle de sistemas digitais simples de alta velocidade. Por sempre ter apenas 1 bit de diferença entre números adjacentes, ele fornece boa proteção contra erros, mas necessita de mais bits para representar a mesma faixa de valores que um binário sequencial. | :* '''Johnson''' - Neste código é gerado deslocando-se sucessivamente todos os bits para a esquerda e colocando o bit complementar do msb como lsb. A codificação normalmente começa com todos bits "0". Devido a sua simplicidade, ele é utilizado para contadores utilizados em controle de sistemas digitais simples de alta velocidade. Por sempre ter apenas 1 bit de diferença entre números adjacentes, ele fornece boa proteção contra erros, mas necessita de mais bits para representar a mesma faixa de valores que um binário sequencial. | ||

| + | |||

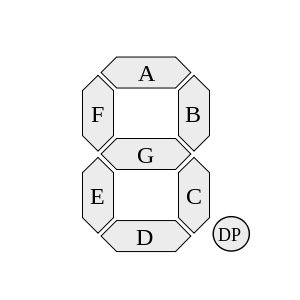

:* '''BCD''' (''Binary-coded decimal'') - Esse código basicamente consiste em representar cada digito decimal de 0 a 9 por um grupo de 4 bits (0 -> 0000, 1 -> 0001, ... 8 -> 1000 e 9 -> 1001). Ele é utilizado em mostradores de sete segmentos, onde cada um deles indica um dígito. | :* '''BCD''' (''Binary-coded decimal'') - Esse código basicamente consiste em representar cada digito decimal de 0 a 9 por um grupo de 4 bits (0 -> 0000, 1 -> 0001, ... 8 -> 1000 e 9 -> 1001). Ele é utilizado em mostradores de sete segmentos, onde cada um deles indica um dígito. | ||

| + | |||

<center> | <center> | ||

{| class="wikitable" style="text-align:center;" | {| class="wikitable" style="text-align:center;" | ||

| Linha 963: | Linha 1 042: | ||

|} | |} | ||

</center> | </center> | ||

| − | |||

| − | |||

| − | |||

;Extensão de bits de um número inteiro sem sinal: | ;Extensão de bits de um número inteiro sem sinal: | ||

| Linha 986: | Linha 1 062: | ||

Número estendido: 10001101 = (-13 em decimal), pois -(+8 + 4 + 1) = -13 | Número estendido: 10001101 = (-13 em decimal), pois -(+8 + 4 + 1) = -13 | ||

| − | ;Ponto Fixo: | + | ;Números binário fracionários em Ponto Fixo: |

| − | * | + | *A representaçaõ de '''Ponto Fixo''' é um número binário que permite representares números fracionários. Os valores são todos escalonados por um fator constante para transformar em um número inteiro. Assim, o número 5,25 pode ser escalonado por 2² => 5,25 x 4 = 21, e portanto 5,25 = 21 / 2². Assim, usando dois bits fracionarios, o número 5,25 pode ser escrito em binário como 10101, onde o separador fracionário esta em 101,01. |

*Usando <math> M </math> bits para representar um número de ponto fixo Q(M,F) com F bits fracionários, é possível representar números fracionários no intervalo de <math> [0, 2^{M-F}-2^{-F}] </math>. Neste caso a resolução (menor quantidade que se pode representar) é de <math> 2^{-F} </math> | *Usando <math> M </math> bits para representar um número de ponto fixo Q(M,F) com F bits fracionários, é possível representar números fracionários no intervalo de <math> [0, 2^{M-F}-2^{-F}] </math>. Neste caso a resolução (menor quantidade que se pode representar) é de <math> 2^{-F} </math> | ||

:Por exemplo usando Q(8,3) => <math> [0; 2^{5}-2^{-3}] = [ 0; 31,875] = [00000,000_2; 11111,111_2] </math>, e a resolução é de <math> 2^{-3} = 0,125 </math>. | :Por exemplo usando Q(8,3) => <math> [0; 2^{5}-2^{-3}] = [ 0; 31,875] = [00000,000_2; 11111,111_2] </math>, e a resolução é de <math> 2^{-3} = 0,125 </math>. | ||

| Linha 1 047: | Linha 1 123: | ||

*Note que que é possível obter rapidamente o valor de um número de ponto fixo, obtendo o valor do seu número inteiro correspondente, dividindo-o por 2<sup>-F</sup>. No exemplo acima, 10100111, corresponde ao inteiro 167, ou seja se o número é do tipo Q(8,3), o valor é de 167/2<sup>-F</sup> = 20,875. | *Note que que é possível obter rapidamente o valor de um número de ponto fixo, obtendo o valor do seu número inteiro correspondente, dividindo-o por 2<sup>-F</sup>. No exemplo acima, 10100111, corresponde ao inteiro 167, ou seja se o número é do tipo Q(8,3), o valor é de 167/2<sup>-F</sup> = 20,875. | ||

*Assim como nos números inteiros, é possível representar também números em ponto fixo negativos usando complemento de 2 ou sinal-magnitude. | *Assim como nos números inteiros, é possível representar também números em ponto fixo negativos usando complemento de 2 ou sinal-magnitude. | ||

| − | ;Ponto Flutuante (''floating point''): | + | |

| − | Os números de ponto flutuante são agrupados da esquerda para a direita:1) bit de sinal, 2) expoente e 3) mantissa. Para os formatos binários IEEE 754 (básico e estendido) que possuem implementações de hardware existentes, eles são distribuídos da seguinte forma: | + | ;PARA O PRÓXIMO ENCONTRO: |

| + | *Resolução dos [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=74 Exercícios 1.7 ao 1.49 Capítulo 1 - Projeto Digital e Arquitetura de Computadores] | ||

| + | *Ler Capítulo 2 - Representações Binárias em [http://biblioteca.ifsc.edu.br/index.asp?codigo_sophia=30631 Eletrônica digital moderna e VHDL / Volnei A. Pedroni; tradução de Arlete Simille Marques] | ||

| + | *Ver exercícios 2.2 a 2.13, 2.16 a 2.18, 2.21 a 2.26, 2.29 a 2.32, 2.39 a 2.41 de [http://biblioteca.ifsc.edu.br/index.asp?codigo_sophia=30631] | ||

| + | |||

| + | ;Encontro 5 (29 fev): | ||

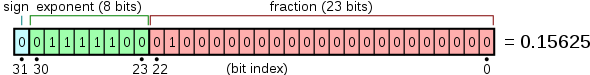

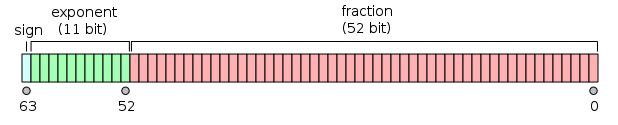

| + | ;Ponto Flutuante (''floating point''):Os números de ponto flutuante são agrupados da esquerda para a direita:1) bit de sinal, 2) expoente e 3) mantissa. Para os formatos binários IEEE 754 (básico e estendido) que possuem implementações de hardware existentes, eles são distribuídos da seguinte forma: | ||

{| class="wikitable" style="text-align:center; background-color:#F8F9FA; color:#202122;" | {| class="wikitable" style="text-align:center; background-color:#F8F9FA; color:#202122;" | ||

| Linha 1 057: | Linha 1 139: | ||

! Mantissa | ! Mantissa | ||

! Total<br />bits | ! Total<br />bits | ||

| − | ! style="background-color:#FFF; font-weight:normal;" | | + | ! style="background-color:#FFF; font-weight:normal;"| |

! Viés do <br />exponente | ! Viés do <br />exponente | ||

! Precisão <br />em bits | ! Precisão <br />em bits | ||

|- | |- | ||

| − | | Half-precision | + | | Half-precision |

| − | | style="vertical-align:middle;" | 1 | + | | style="vertical-align:middle;"|1 |

| − | | style="vertical-align:middle;" | 5 | + | | style="vertical-align:middle;"|5 |

| − | | style="vertical-align:middle;" | 10 | + | | style="vertical-align:middle;"|10 |

| − | | style="vertical-align:middle;" | 16 | + | | style="vertical-align:middle;"|16 |

| − | | style="vertical-align:middle; background-color:#FFF;" | | + | | style="vertical-align:middle; background-color:#FFF;"| |

| − | | style="vertical-align:middle;" | 15 | + | | style="vertical-align:middle;"|15 |

| − | | style="vertical-align:middle;" | 11 | + | | style="vertical-align:middle;"|11 |

|- | |- | ||

| Single-precision | | Single-precision | ||

| − | | style="vertical-align:middle;" | 1 | + | | style="vertical-align:middle;"|1 |

| − | | style="vertical-align:middle;" | 8 | + | | style="vertical-align:middle;"|8 |

| − | | style="vertical-align:middle;" | 23 | + | | style="vertical-align:middle;"|23 |

| − | | style="vertical-align:middle;" | 32 | + | | style="vertical-align:middle;"|32 |

| − | | style="vertical-align:middle; background-color:#FFF;" | | + | | style="vertical-align:middle; background-color:#FFF;"| |

| − | | style="vertical-align:middle;" | 127 | + | | style="vertical-align:middle;"|127 |

| − | | style="vertical-align:middle;" | 24 | + | | style="vertical-align:middle;"|24 |

|- | |- | ||

| Double-precision | | Double-precision | ||

| − | | style="vertical-align:middle;" | 1 | + | | style="vertical-align:middle;"|1 |

| − | | style="vertical-align:middle;" | 11 | + | | style="vertical-align:middle;"|11 |

| − | | style="vertical-align:middle;" | 52 | + | | style="vertical-align:middle;"|52 |

| − | | style="vertical-align:middle;" | 64 | + | | style="vertical-align:middle;"|64 |

| − | | style="vertical-align:middle; background-color:#FFF;" | | + | | style="vertical-align:middle; background-color:#FFF;"| |

| − | | style="vertical-align:middle;" | 1023 | + | | style="vertical-align:middle;"|1023 |

| − | | style="vertical-align:middle;" | 53 | + | | style="vertical-align:middle;"|53 |

|} | |} | ||

| Linha 1 097: | Linha 1 179: | ||

<center>[[Arquivo:PontoFlutuante64.png]]</center> | <center>[[Arquivo:PontoFlutuante64.png]]</center> | ||

| − | + | ;Como converter de decimal para floating point?: | |

| − | : | + | # Identifique quantos bits serão usados e obtenha o viés (veja na tabela acima) |

| − | + | # Converta o número decimal para binário ponto fixo: | |

| − | #Identifique | + | # Normalize a mantissa, movendo o ponto decimal para que haja apenas um um dígito à esquerda do ponto decimal. |

| − | #Obtenha o sinal do número a partir do ''msb'' (S = 0 => +; S = 1 => -) | + | # Determine o sinal, o expoente e a mantissa: 1) O número é positivo, então o bit de sinal é 0. 2) O expoente é o deslocamento necessário para normalizar a mantissa. 3) A mantissa é a parte fracionária normalizada. |

| − | #Obtenha o número correspondente ao | + | # Converta o expoente para binário com bias: Adicionamos o viés ao expoente para obter o valor final. |

| − | #Considerando o viés, calcule o | + | # Junte os bits na ordem: sinal, expoente e mantissa, e obtenha o número em IEEE 754 Floating Point |

| − | #Obtenha o valor da mantissa (M) e | + | |

| − | #O resultado em decimal é <math> (-)^S \times 1.M \times 2^{E-vies} </math> | + | '''Exemplo:''' Dado o número '''85,125''' converta para a representação floating point de 32 bits |

| − | Exemplo: Dado o número floating point de 32 bits = | + | '''P1:''' 32 bits, portanto o viés é 127. |

| − | + | '''P2:''' 85 em binário é 1010101. 0.125 em binário é 0.001. Portanto, 85,125 em binário é 1010101.001 | |

| − | + | '''P3:''' 1010101.001 => <span style="color:red;">1</span>.<span style="color:blue;">010101001</span> × 2^6 | |

| − | Expoente (8 bits): 10000001 = 129 - 127 = 2 | + | '''P4:''' O número é positivo, então o bit de sinal é 0. O expoente é o deslocamento necessário para normalizar a mantissa. No caso, 6. A mantissa é a parte fracionária normalizada, que é <span style="color:blue;">010101001</span>.(note que o <span style="color:red;">1</span> a esquerda do ponto decimal não será representado. |

| − | Mantissa: (23 bits): 11000000000000000000000 | + | '''P5:''' Expoente = 6 + 127 = 133 em binário é <span style="color:green;">10000101</span>. |

| − | Valor (24 bits): 1.11000000000000000000000 = 1,75 | + | '''P6:''' Sinal: 0, Expoente: <span style="color:green;">10000101</span>, Mantissa: <span style="color:blue;">010101001</span>00000000000000 (completar com zeros até 23 bits), portanto 0 10000101 <span style="color:blue;">010101001</span>00000000000000 |

| − | Resultado: (-) 1,75 x 2<sup>2</sup> = 7 | + | : FONTE: [https://www.wikihow.com/Convert-a-Number-from-Decimal-to-IEEE-754-Floating-Point-Representation How to Convert a Number from Decimal to IEEE 754 Floating Point Representation] |

| + | |||

| + | ;Como converter de floating point para decimal?: | ||

| + | # Identifique o número de bits e obtenha o número de bits do expoente e o viés (veja na tabela acima), | ||

| + | # Obtenha o sinal do número a partir do ''msb'' (S = 0 => +; S = 1 => -) | ||

| + | # Obtenha o número correspondente ao Expoente (E). | ||

| + | # Considerando o viés, calcule o expoente (e = E - viés) | ||

| + | # Obtenha o valor da mantissa (M) e | ||

| + | # Obtenha o valor decimal correspondente, acrescentando o 1 inteiro (se o numero estiver normalizado) antes da conversão | ||

| + | # O resultado em decimal é <math> (-)^S \times 1.M \times 2^{E-vies} </math> | ||

| + | '''Exemplo:''' Dado o número representado em floating point de 32 bits = 1<span style="color:green;">10000001</span><span style="color:blue;">11000000000000000000000</span> | ||

| + | '''P1:''' Expoente tem 8 bits => viés = 127 (2<sup>8-1</sup>-1) | ||

| + | '''P2:''' Sinal (msb): 1 => é um número negativo (-) | ||

| + | '''P3:''' Expoente (8 bits): <span style="color:green;">10000001</span> = 129 | ||

| + | '''P4:''' expoente (e = E - vies) 129 - 127 = 2 | ||

| + | '''P5:''' Mantissa: (23 bits): <span style="color:blue;">11000000000000000000000</span> | ||

| + | '''P6:''' Valor (24 bits):1.<span style="color:blue;">11000000000000000000000</span> = 1,75 | ||

| + | '''P7:''' Resultado: (-) 1,75 x 2<sup>2</sup> = -7 | ||

| − | + | ;Números sub_normais: | |

| − | Os números | + | Os números sub_normais são indicados pelo Expoente = 00000000. Esse Expoente será interpretado como 2<sup>-126</sup>. Eles, ao contrário dos números normalizados, não usam um "1" implícito no início da mantissa. Isso significa que a mantissa desses números começa com um "0" explícito antes da parte fracionária, permitindo representar valores muito pequenos que não podem ser normalizados devido à limitação dos bits do expoente. |

| + | Exemplos: | ||

| + | 0 00000000 00000000000000000000000 corresponde ao número +0 | ||

| + | 1 00000000 00000000000000000000000 corresponde ao número -0 | ||

| + | 0 00000000 10000000000000000000000 corresponde ao número 0,5 x 2<sup>-126</sup> = 5.877472E-39 | ||

| + | 1 00000000 00000000000000000000001 corresponde ao número -2<sup>-23</sup> x 2<sup>-126</sup> = -0.00000011920928955078125 x 2<sup>-126</sup> = -1.40129846432481707092373E-45 (2<sup>-149</sup> | ||

| − | + | ;Números especiais: | |

| − | + | * Infinito Positivo (Inf): Bit de sinal: 0 (positivo) Expoente: Todos os bits definidos como 1 (8 bits) | |

| − | |||

| − | |||

Mantissa: Todos os bits definidos como 0 (23 bits) | Mantissa: Todos os bits definidos como 0 (23 bits) | ||

Representação em 32 bits: 0 11111111 00000000000000000000000 | Representação em 32 bits: 0 11111111 00000000000000000000000 | ||

| − | + | * Infinito Negativo (-Inf): Bit de sinal: 1 (negativo) Expoente: Todos os bits definidos como 1 (8 bits) | |

| − | |||

| − | |||

| − | |||

Mantissa: Todos os bits definidos como 0 (23 bits) | Mantissa: Todos os bits definidos como 0 (23 bits) | ||

Representação em 32 bits: 1 11111111 00000000000000000000000 | Representação em 32 bits: 1 11111111 00000000000000000000000 | ||

| − | + | * NaN (''Not a Number''): Bit de sinal: Pode ser 0 ou 1 (geralmente usado para sinalizar erros ou operações indefinidas) Expoente: Todos os bits definidos como 1 (8 bits) | |

| − | |||

| − | |||

| − | |||

Mantissa: Pelo menos um bit não nulo (23 bits) | Mantissa: Pelo menos um bit não nulo (23 bits) | ||

Representação: x 11111111 yyyyyyyyyyyyyyyyyyyyyyy (onde "x" é o bit de sinal e "y" são bits da mantissa) | Representação: x 11111111 yyyyyyyyyyyyyyyyyyyyyyy (onde "x" é o bit de sinal e "y" são bits da mantissa) | ||

| − | + | ;Exemplos de conversores online: | |

| − | + | * [http://weitz.de/ieee/ IEEE 754 Calculator] 16-bits & 32-bits & 64-bits & 128-bits | |

| − | + | * [https://www.h-schmidt.net/FloatConverter/IEEE754.html IEEE-754 Floating Point Converter] 32-bitsVer [[Media: PontoFixoFlutuante.pdf| Ponto Fixo e Flutuante]] - prof. Odilson | |

| − | + | * Ver [https://en.wikipedia.org/wiki/Floating-point_arithmetic Floating-point arithmetic] - wikipedia | |

| − | + | * Ver [https://en.wikipedia.org/wiki/IEEE_754 IEEE 754] - wikipedia | |

| − | *Ver [https://en.wikipedia.org/wiki/Floating-point_arithmetic Floating-point arithmetic] - wikipedia | + | * Ler sobre os hardware de microprocessadores [https://en.wikipedia.org/wiki/History_of_computing_hardware_(1960s%E2%80%93present)#Microprocessors]. Para ver o número de bits de cada arquitetura, clique no link correspondente na tabela.{{collapse bottom}} |

| − | *Ver [https://en.wikipedia.org/wiki/IEEE_754 IEEE 754] - wikipedia | ||

| − | *Ler sobre os hardware de microprocessadores [https://en.wikipedia.org/wiki/History_of_computing_hardware_(1960s%E2%80%93present)#Microprocessors]. | ||

| − | |||

| − | {{collapse bottom}} | ||

===Unidade 3 - Funções, portas lógicas e álgebra booleana=== | ===Unidade 3 - Funções, portas lógicas e álgebra booleana=== | ||

* 10 ENCONTROS | * 10 ENCONTROS | ||

{{collapse top |expand=true | Unidade 3 - Funções, portas lógicas e álgebra booleana }} | {{collapse top |expand=true | Unidade 3 - Funções, portas lógicas e álgebra booleana }} | ||

| − | + | ;Encontro 6 (5 mar.) | |

| − | ;Encontro 6 | + | ;Funções e portas lógicas: |

| − | * | + | *[https://moodle.ifsc.edu.br/pluginfile.php/311787/mod_resource/content/1/Fun%C3%A7%C3%B5es%20%20e%20portas%20l%C3%B3gicas.pdf Funções e portas lógicas] |

| − | *Ler pag 49 a 69 de [https://moodle.ifsc.edu.br/pluginfile.php/ | + | ;PARA O PRÓXIMO ENCONTRO: |

| − | + | *Rever [https://moodle.ifsc.edu.br/pluginfile.php/311787/mod_resource/content/1/Fun%C3%A7%C3%B5es%20%20e%20portas%20l%C3%B3gicas.pdf Funções e portas lógicas] | |

| − | + | *Ler pag 49 a 69 de [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=49 Projeto Digital e Arquitetura de Computadores] | |

| − | |||

| − | |||

| − | * | + | ;Encontro 7 (7 mar.) |

| + | ;Funções e portas lógicas: | ||

| + | *[https://moodle.ifsc.edu.br/pluginfile.php/311787/mod_resource/content/1/Fun%C3%A7%C3%B5es%20%20e%20portas%20l%C3%B3gicas.pdf Funções e portas lógicas] | ||

| + | ;PARA O PRÓXIMO ENCONTRO: | ||

| + | *[[Como as portas lógicas são implementadas com transistores CMOS]] | ||

| − | |||

| − | |||

| − | |||

| − | ;Encontro | + | ;Encontro 8 (12 mar.) |

| − | * | + | *[https://moodle.ifsc.edu.br/pluginfile.php/311788/mod_resource/content/2/Algebra%20de%20Boole.pdf Álgebra de Boole] - slides |

| − | *Ler a seção '''2. | + | ;PARA O PRÓXIMO ENCONTRO: |

| − | * | + | *Rever slides 1 a 15 de [https://moodle.ifsc.edu.br/pluginfile.php/311788/mod_resource/content/2/Algebra%20de%20Boole.pdf Álgebra de Boole] |

| + | *Ler a seção '''2.3.ÁLGEBRA BOOLEANA''' nas pag 107 a 116 de [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=107 Projeto Digital e Arquitetura de Computadores] | ||

| + | *Ler a seção '''4-2 LEIS E REGRAS DA ÁLGEBRA BOOLEANA''' nas pag 201 a 206 de [https://app.minhabiblioteca.com.br/reader/books/9788577801077/pageid/200 FLOYD, Thomas. Sistemas digitais. Grupo A, 2011. E-book. ISBN 9788577801077] na [[Minha Biblioteca]] | ||

| − | ;Encontro | + | ;Encontro 9 (14 mar.) |

| − | * | + | *[https://moodle.ifsc.edu.br/pluginfile.php/311788/mod_resource/content/2/Algebra%20de%20Boole.pdf Álgebra de Boole] |

| − | * | + | ;Teoremas de De Morgan: |

| + | *O complemento do produto é igual a soma dos complementos: <math> \overline{X \cdot Y} = \overline{X} + \overline{Y} </math> | ||

| + | *O complemento da soma é igual ao produto dos complementos: <math> \overline{X+Y} = \overline{X} \cdot \overline{Y} </math> | ||

| − | + | Para provar os teoremas, podemos obter a tabela verdade de ambos lados de cada equação booleana. | |

| − | |||

| − | |||

| − | |||

| − | ; | + | {| class="wikitable" style="text-align:center;" |

| − | + | |- style="text-align:left;" | |

| − | + | ! colspan="2" | Entradas | |

| − | + | ! colspan="2" | Saídas | |

| − | + | |- style="font-weight:bold; background-color:#EAECF0; color:#202122;" | |

| − | + | | style="vertical-align:middle; width: 25%;" | X | |

| − | + | | style="vertical-align:middle; width: 25%;" | Y | |

| − | + | | style="font-weight:normal; width: 25%;" | <math> \overline{X \cdot Y} </math> | |

| − | -- | + | | style="font-weight:normal; width: 25%;" | <math> \overline{X} + \overline{Y} </math> |

| − | + | |- style="vertical-align:middle; | |

| + | | 0 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | |- | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | |} | ||

| − | === | + | {| class="wikitable" style="text-align:center;" |

| − | + | |- style="text-align:left;" | |

| − | {{ | + | ! colspan="2" | Entradas |

| − | < | + | ! colspan="2" | Saídas |

| − | + | |- style="font-weight:bold; background-color:#EAECF0; color:#202122;" | |

| − | + | | style="vertical-align:middle; width: 25%;" | X | |

| − | + | | style="vertical-align:middle; width: 25%;" | Y | |

| − | + | | style="font-weight:normal; width: 25%;" | <math> \overline{X + Y} </math> | |

| − | + | | style="font-weight:normal; width: 25%;" | <math> \overline{X} \cdot \overline{Y} </math> | |

| + | |- style="vertical-align:middle; | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | |- | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | |} | ||

| + | |||

| + | Ou utilizar os postulados e teoremas da algebra de boole. | ||

| + | Considerando que <math> \overline{X+Y} = \overline{X} \cdot \overline{Y} </math> seja verdade, então | ||

| + | :'''PASSO 1:''' pelo postulado do complemento <math> \overline{A} + A = 1 </math>, podemos afirmar que | ||

| + | ::<math>(X+Y) + (\overline{X}\cdot\overline{Y}) = 1 </math> | ||

| + | :'''PASSO 2:''' pelo teorema da distribuição <math> A + (B \cdot C) = (A + B) \cdot (A + C) </math>, podemos afirmar que | ||

| + | ::<math> (X + Y) + (\overline{X}\cdot\overline{Y})=(X + Y + \overline{X})\cdot(X + Y + \overline{Y}) </math> | ||

| + | :'''PASSO 3:''' pelo teorema da comutação <math> A + B = B + A </math>, podemos afirmar que | ||

| + | ::<math>(X + Y + \overline{X})\cdot(X + Y + \overline{Y}) = (Y + X + \overline{X})\cdot(X + Y + \overline{Y}) </math> | ||

| + | :'''PASSO 4:''' pelo postulado do complemento <math> A + \overline{A} = 1 </math>, podemos afirmar que | ||

| + | ::<math>(Y + X + \overline{X})\cdot(X + Y + \overline{Y}) = (Y + 1) \cdot (X + 1) </math> | ||

| + | :'''PASSO 5:''' pelo postulado do elemento absorvente <math> A + 1 = 1 </math>, podemos afirmar que | ||

| + | ::<math> (Y + 1) \cdot (X + 1) = 1 \cdot 1 </math> | ||

| + | :'''PASSO 6:''' pelo postulado da multiplicação (AND) <math> 1 \cdot 1 = 1 </math>, podemos afirmar que | ||

| + | ::<math> 1 \cdot 1 = 1 </math> | ||

| + | : Portanto a consideração inicial é verdadeira <math> \overline{X+Y} = \overline{X} \cdot \overline{Y} </math>. | ||

| + | |||

| + | :'''Nota:''' O teorema também pode ser provado usando o postulado do complemento <math> \overline{A} \cdot A = 0 </math>, pois neste caso, podemos afirmar que | ||

| + | ::<math>(X+Y) . (\overline{X}\cdot\overline{Y}) = 0 </math>. | ||

| + | :Tente desenvolver o restante da prova usando apenas os postulados e teoremas. | ||

| + | |||

| + | Os teoremas de De Morgam são validos para qualquer número (N) de entradas, podem ser escritos como: | ||

| + | : <math> \overline{X_1 \cdot X_2 \cdot ... \cdot X_N} = \overline{X_1} + \overline{X_2} + ... + \overline{X_N} </math> | ||

| + | : <math> \overline{X_1 + X_2 + ... + X_N} = \overline{X_1} \cdot \overline{X_2} \cdot ... \cdot \overline{X_N}</math> | ||

| − | ; | + | ;Exercícios: |

| − | + | Simplifique as expressões lógicas (''caso seja possível''). Indique os Postulados ou Teoremas utilizado em cada passo. Para simplificar as notações os códigos A1 a A5 e T1 a T12 ou T1' a T12' indicado na [https://moodle.ifsc.edu.br/pluginfile.php/372852/mod_resource/content/1/Folha%20de%20consulta%20-%20%C3%A1lgebra%20booleana.pdf Folha de consulta - álgebra booleana]. | |

| + | :a) ABC + A + BC | ||

| + | :b) A.B + A.B’ + A’.B | ||

| + | :c) X.Y + X.Y’ + X’.Y + X.Y | ||

| + | :d) X.Y + X.Z + Z.Y | ||

| + | :e) D.B’+D.(D.B+C.D’) | ||

| + | |||

| + | Ver também exemplos em 4-4 ANÁLISE BOOLEANA DE CIRCUITOS LÓGICOS [[https://app.minhabiblioteca.com.br/reader/books/9788577801077/pageid/206 FLOYD, Thomas. Sistemas digitais. Grupo A, 2011. E-book. ISBN 9788577801077] | ||

| − | * | + | ;PARA O PRÓXIMO ENCONTRO: |

| − | + | *Rever slides 16 até fim de [https://moodle.ifsc.edu.br/pluginfile.php/311788/mod_resource/content/2/Algebra%20de%20Boole.pdf Álgebra de Boole] | |

| − | + | *Ler a seção '''2.3.ÁLGEBRA BOOLEANA''' nas pag 107 a 116 de [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=107 Projeto Digital e Arquitetura de Computadores] | |

| − | + | *Ler a seção '''4-3 TEOREMAS DE DEMORGAN e 4-4 ANÁLISE BOOLEANA DE CIRCUITOS LÓGICOS ''' nas pag 207 a 216 de [https://app.minhabiblioteca.com.br/reader/books/9788577801077/pageid/206 FLOYD, Thomas. Sistemas digitais. Grupo A, 2011. E-book. ISBN 9788577801077] na [[Minha Biblioteca]] | |

| − | |||

| − | |||

| − | :* ''' | + | ;Encontro 10 (21 mar.) |

| − | + | *Expressão booleana - Tabela verdade - Circuito com portas lógicas: | |

| − | + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/311791/mod_resource/content/1/Portas%20-%20Tabela%20verdade%20-%20Express%C3%B5es.pdf Expressão booleana - Tabela verdade - Circuito com portas lógicas] | |

| − | + | *Ler a seção '''2.4. DA LÓGICA ÀS PORTAS e 2.5.LÓGICA COMBINATÓRIO MULTI-NÍVEL''' nas pag 90 a 95 de [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=116 Projeto Digital e Arquitetura de Computadores] | |

| − | + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/311790/mod_resource/content/1/Exercicios%20de%20algebra%20de%20boole.pdf Exercícios de álgebra de Boole] | |

| − | + | *Ler a seção '''2.3.4. A Verdade por Detrás de Tudo e 2.3.5. Simplificando Equações''' nas pag 87 a 90 de [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=113 Projeto Digital e Arquitetura de Computadores] | |

| − | + | ||

| − | + | ;Encontro 11 (26 mar.): | |

| − | + | *Expressão booleana - Tabela verdade - Circuito com portas lógicas: | |

| − | + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/311791/mod_resource/content/1/Portas%20-%20Tabela%20verdade%20-%20Express%C3%B5es.pdf Expressão booleana - Tabela verdade - Circuito com portas lógicas] | |

| − | + | *Ler a seção '''2.4. DA LÓGICA ÀS PORTAS e 2.5.LÓGICA COMBINATÓRIO MULTI-NÍVEL''' nas pag 90 a 95 de [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=116 Projeto Digital e Arquitetura de Computadores] | |

| − | + | *Avaliação A1b (50 minutos) | |

| − | |||

| − | |||

| − | [ | ||

| − | |||

| − | |||

| − | |||

| − | :* ''' | + | ;Encontro 12 (28 mar.) |

| − | + | *Simplificação de expressões lógicas - Mapas de Karnaugh-Veitch: | |

| − | + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/311792/mod_resource/content/2/Simplifica%C3%A7%C3%A3o%20de%20express%C3%B5es%20l%C3%B3gicas%20-%20Mapas%20de%20Karnaugh-Veitch.pdf Simplificação de expressões lógicas - Mapas de Karnaugh-Veitch] | |

| − | + | *Ler a seção '''2.7.MAPAS DE KARNAUGH''' nas pag 99 a 108 de [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=125 Projeto Digital e Arquitetura de Computadores] | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | * | + | ;Encontro 13 (2 abr.) |

| + | *Ler [https://en.wikipedia.org/wiki/Quine%E2%80%93McCluskey_algorithm#:~:text=The%20Quine%E2%80%93McCluskey%20algorithm%20is,to%20as%20the%20tabulation%20method Quine–McCluskey algorithm] | ||

| + | *Teste em [https://www.mathematik.uni-marburg.de/~thormae/lectures/ti1/code/qmc/ Quine–McCluskey algorithm] | ||

| + | *Ler [https://en.wikipedia.org/wiki/Espresso_heuristic_logic_minimizer Espresso heuristic logic minimizer] | ||

| + | *Ler [https://wiki.sj.ifsc.edu.br/index.php/Mapas_de_Karnaugh_2D_e_3D Mapas de Karnaugh 2D e 3D] | ||

| + | *K-Map online [https://www.docjava.com/cpe210/kmapExplorer.html docjava.com], [https://ictlab.kz/extra/Kmap/ ICT laboratory], [https://www.mathematik.uni-marburg.de/~thormae/lectures/ti1/code/karnaughmap/ uni-marburg.de] | ||

| − | + | ;Encontro 14 (4 abr.) | |

| − | + | *Simplificação de expressões lógicas - Mapas de Karnaugh-Veitch: | |

| − | + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/311792/mod_resource/content/2/Simplifica%C3%A7%C3%A3o%20de%20express%C3%B5es%20l%C3%B3gicas%20-%20Mapas%20de%20Karnaugh-Veitch.pdf Simplificação de expressões lógicas - Mapas de Karnaugh-Veitch] | |

| + | *Ler a seção '''2.7.MAPAS DE KARNAUGH''' nas pag 99 a 108 de [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=125 Projeto Digital e Arquitetura de Computadores] | ||

| − | |||

| − | |||

| − | |||

| − | + | ;Encontro 15 (9 abr.) - Projeto de circuitos combinacionais: | |

| − | + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/311789/mod_resource/content/1/Projeto%20de%20circuitos%20combinacionais.pdf Projeto de circuitos combinacionais] | |

| − | + | *Multiplexadores e Decodificadores: | |

| − | + | *Ler a seção '''2.8.BLOCOS COMBINATÓRIOS''' nas pag 109 a 114 [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=135 Projeto Digital e Arquitetura de Computadores] | |

| − | + | ||

| + | ;Encontro 16 (11 abr.) | ||

| + | *Exercícios 2.1, 2.2, 2.5-7, 2.13-18, 2.22-25, 2.28-29, 2.31-32, 2.34, 2.35, 2.36-37, 2.39-40 ver [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=151] | ||

| + | *Pergunta 2.2, 2.3, 2.4 ver [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=163] | ||

| + | |||

| + | ;Encontro 18 (23 abr.) - Avaliação A1c (6 pontos): | ||

| + | *Simplificação de expressões lógicas e mapa de Karnaugh | ||

| + | *Representação de circuitos lógicos - '''Diagrama de portas lógicos = Tabela Verdade = Expressão lógica''' | ||

| − | + | <!-- | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | *Consumo de energia de circuitos digitais. | |

| − | + | ::<math> P_{Estatica} = I_{DD} \times V_{DD} </math> | |

| − | + | ::<math> P_{Dinamica} = 1/2 \times C \times V_{DD}^2 \times f </math> | |

| − | + | ::<math> P_{Total} = P_{Estatica} + P_{Dinamica} </math> | |

| − | + | *Ler pag 69 a 70 de [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=69 Projeto Digital e Arquitetura de Computadores] | |

| − | * | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | ; | + | ;Encontro 11 (31 ago) - Exercícios de álgebra de Boole: |

| − | * | + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/252198/mod_resource/content/1/Exercicios%20de%20algebra%20de%20boole.pdf Exercícios de álgebra de Boole] |

| − | + | *Ler a seção '''2.3.4. A Verdade por Detrás de Tudo e 2.3.5. Simplificando Equações''' nas pag 87 a 90 de [https://moodle.ifsc.edu.br/pluginfile.php/159985/mod_resource/content/1/DDCA_portugues.pdf#page=113 Projeto Digital e Arquitetura de Computadores] | |

| − | ; | + | ;Encontro 12 (5 set) - Expressão booleana - Tabela verdade - Circuito com portas lógicas: |

| − | * | + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/254019/mod_resource/content/1/Portas%20-%20Tabela%20verdade%20-%20Express%C3%B5es.pdf Expressão booleana - Tabela verdade - Circuito com portas lógicas] |

| + | *Ler a seção '''2.4. DA LÓGICA ÀS PORTAS e 2.5.LÓGICA COMBINATÓRIO MULTI-NÍVEL''' nas pag 90 a 95 de [https://moodle.ifsc.edu.br/pluginfile.php/159985/mod_resource/content/1/DDCA_portugues.pdf#page=116 Projeto Digital e Arquitetura de Computadores] | ||

| + | *Avaliação A1b (55 minutos) | ||

| − | + | --> | |

| − | * | + | {{collapse bottom}} |

| + | |||

| + | ===Unidade 4 - Introdução a linguagem VHDL e Quartus/ModelSim=== | ||

| + | * 6 ENCONTROS | ||

| + | {{collapse top | expand=true |Unidade 4 - Introdução a linguagem VHDL e Quartus/ModelSim }} | ||

| − | |||

| − | |||

| + | ;Encontro 17 (18 abr.) - Linguagem VHDL: | ||

| + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/311793/mod_resource/content/2/Introdu%C3%A7%C3%A3o%20a%20linguagem%20de%20descri%C3%A7%C3%A3o%20de%20hardware.pdf Introdução a linguagem de descrição de hardware (DHL)] | ||

| − | ;Encontro | + | ;Encontro 19 (25 abr.) - Linguagem VHDL: |

| − | * | + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/311793/mod_resource/content/2/Introdu%C3%A7%C3%A3o%20a%20linguagem%20de%20descri%C3%A7%C3%A3o%20de%20hardware.pdf Introdução a linguagem de descrição de hardware (DHL)] |

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | * Estrutura do código VHDL | |

| − | * | + | :* Declaração das bibliotecas e pacotes '''LIBRARY''' / '''PACKAGE''' |

| − | + | <syntaxhighlight lang=vhdl> | |

| − | + | library library_name; | |

| − | + | use library_name.package_name.all; | |

| − | + | </syntaxhighlight> | |

| − | |||

| − | |||

| − | + | :* '''ENTITY''' | |

| − | * | ||

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | entity entity_name is | |

| − | + | [generic ( | |

| − | + | cons_name1: const_type const_value; | |

| − | entity | + | cons_name2: const_type const_value; |

| − | + | ... | |

| − | + | cons_nameN: const_type const_value);] | |

| − | + | [port ( | |

| − | + | signal_name1: mode signal_type; | |

| − | + | signal_name2: mode signal_type; | |

| − | + | ... | |

| − | + | signal_nameN: mode signal_type);] | |

| − | + | [declarative_part] | |

| − | begin | + | [begin |

| − | + | statement_part] | |

| − | end | + | end [entity] [entity_name]; |

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | :* '''ARCHITECTURE''' | |

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | - | + | architecture arch_name of entity_name is |

| − | + | [declarative_part] | |

| − | + | begin | |

| − | entity | + | statement_part |

| − | port | + | end [architecture] [arch_name]; |

| − | + | </syntaxhighlight> | |

| − | + | ||

| − | + | * Exemplo - Declaração de uma porta NAND em VHDL | |

| − | + | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | library std; | ||

| + | use std.standard.all; | ||

| + | |||

| + | entity nand_gate is | ||

| + | port (a, b: in bit; x: out bit); | ||

end entity; | end entity; | ||

| − | + | ||

| − | architecture | + | architecture nome_arch of nand_gate is |

begin | begin | ||

| − | + | x <= a nand b; | |

end architecture; | end architecture; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | *Uso do ambiente EDA - QUARTUS Prime para programação em VHDL. | |

| − | + | ;PASSO 0: | |

| − | + | [[Acesso ao IFSC-CLOUD (NUVEM) | Acesse a nuvem do IFSC]] usando um terminal via ssh: | |

| − | + | USER=LOGIN_SIGAA | |

| − | + | ssh $USER@quartus.sj.ifsc.edu.br -XC | |

| − | + | Insira a senha do SIGAA | |

| − | + | LOGIN_SIGAA@quartus.sj.ifsc.edu.br's password: | |

| − | |||

| − | |||

| − | |||

| − | + | ;PASSO 1: | |

| − | + | Abra o Quartus Prime digitando no terminal | |

| − | + | quartus20.1.sh | |

| − | + | Em seguida abra um arquivo para inserir o código VHDL. No menu superior selecione '''[File > New > Design Files: VHDL File]''' e '''[OK]''' | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| + | ;PASSO 2: | ||

| + | *Copie o código VHDL acima para o espaço de edição e salve o arquivo com o nome da '''entity''': ''nand_gate.vhd'', em um pasta exclusiva para este projeto. | ||

| + | *Ao ser perguntado se deseja criar um novo projeto, responda [Yes]. Os próximos passos podem ser realizados da seguinte forma: | ||

| + | :*Na tela '''Introduction''' [Next >] | ||

| + | :*Na tela '''Directory, Name, Top-Level Entity''' | ||

| + | ::*Note onde o projeto será salvo. | ||

| + | /home/USER/PASTA_DO_PROJETO/ | ||

| + | ::*Note o nome do projeto. Se quiser pode mudá-lo | ||

| + | nand_gate | ||

| + | ::*Note o nome da '''top-level design entity''' | ||

| + | nand_gate | ||

| + | ::*Em seguida [Next >] | ||

| + | :*Na tela '''Project Type''' [Next >] | ||

| + | :*Na tela '''Add Files''' [Next >], pois seu arquivo já está na lista dos arquivos. | ||

| + | :*Na tela '''Family, Device & Board Settings''', escolha a Family = ['''Cyclone IV E'''] e o Device = ['''EP4CE6E22A7'''] e [Next >] | ||

| + | :*Na tela '''EDA Tool Setting''' [Next >] | ||

| + | :*Note na tela Summary os dados do projeto e clique [Finish] | ||

| + | |||

| + | ;PASSO 3: | ||

| + | Realize a '''Analysis & Synthesis''' ['''Processing > Start > Start Analysis & Synthesis'''], ou use um dos botões que o professor mostrou em aula. | ||

| + | :*Note o '''Compilation Report''' | ||

| − | + | ;PASSO 4: | |

| − | + | *Use o [[RTL Viewer]] para ver a descrição RTL do circuito. Selecione '''[Tools > Netlist Vieweres > RTL Viewer]'''. | |

| − | + | *Use o [[Technology Map Viewer]] para ver a como o circuito foi mapeado para os elementos lógicos disponíveis no dispositivo FPGA selecionado. Selecione '''[Tools > Netlist Vieweres > Technology Map Viewer]'''. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | * | ||

| − | * | ||

| − | |||

| − | |||

| + | ;PASSO 5: | ||

| + | *Modifique a descrição do circuito para implementar o circuito da função Y = (A.B)' + C.D'B', salve o projeto Ckt2.vhd e de o mesmo nome para a entity. | ||

| − | * | + | ;PARA O PRÓXIMO ENCONTRO |

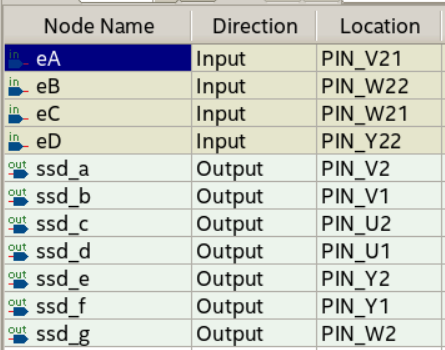

| − | + | *Escreva em VHDL o circuito do [https://wiki.sj.ifsc.edu.br/index.php/ELD129002-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE1_-_Projeto_de_um_conversor_de_bin.C3.A1rio_para_mostrador_de_7_segmentos AE1 - Projeto de um conversor de binário para mostrador de 7 segmentos] | |

| + | :*Use como modelo: | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | ------ | + | -- A bibliteca std e o pacote standard são autodeclarados, então as linhas abaixo podem ser comentadas com "--" |

| − | -- | + | --library std; |

| − | + | --use std.standard.all; | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | entity BCD2SSD is | |

| − | + | port ( | |

| + | -- Entradas ABCD do circuito | ||

| + | A, B, C, D: in bit; | ||

| + | -- Saidas para os leds do mostrador de 7 segmentos. Note que o nome a, b, .. g foi mudado para ssd_a, ssd_b, ... ssd_g pois o VHDL é insensível a caixa | ||

| + | ssd_a, ssd_b, ssd_c, ssd_d, ssd_e, ssd_f, ssd_g : out bit | ||

| + | ); | ||

| + | end entity; | ||

| − | + | architecture ifsc_v1 of BCD2SSD is | |

| − | |||

begin | begin | ||

| + | -- descreva a expressão lógica obtida para cada uma das saídas; | ||

| + | -- Por exemplo: se for a = A + C + (B'.D') + (B.D) | ||

| + | ssd_a <= A or C or (not B and not D) or (B and D); | ||

| − | end architecture | + | ssd_g <= ; |

| + | end architecture; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | ;Encontro | + | *Ler [https://pt.wikipedia.org/wiki/VHDL VHDL] na Wikipedia. |

| − | + | *Guardar [[Folha de consulta de VHDL]] | |

| − | + | ||

| − | *''' | + | ;Encontro 20 (30 abr.) [https://wiki.sj.ifsc.edu.br/index.php/ELD129002-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis AE2 - Conhecendo os dispositivos lógicos programáveis] |

| − | + | ||

| − | + | ====ATUAL==== | |

| − | + | ;Encontro 21 (2 mai.) [https://wiki.sj.ifsc.edu.br/index.php/ELD129002-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis AE2 - Conhecendo os dispositivos lógicos programáveis]: | |

| − | + | :*(Continuação) | |

| − | + | ;Encontro 22 (7 mai.) AE3: | |

| − | + | [[Preparando para gravar o circuito lógico no FPGA]] | |

| − | + | ||

| − | + | <!-- | |

| − | + | ;Encontro 18 (18 abr.) - Avaliação A1c (6 pontos): | |

| − | + | *Simplificação de expressões lógicas e mapa de Karnaugh | |

| − | + | *Representação de circuitos lógicos - '''Diagrama de portas lógicos = Tabela Verdade = Expressão lógica''' | |

| − | + | ||

| − | + | ;Encontro 18 (28 set) - Linguagem VHDL (cont): | |

| − | + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/262427/mod_resource/content/1/Introdu%C3%A7%C3%A3o%20a%20linguagem%20de%20descri%C3%A7%C3%A3o%20de%20hardware.pdf Introdução a linguagem de descrição de hardware (DHL)] | |

| − | | | + | |

| − | | | + | |

| − | + | ;Encontro 19 (3 out.) - Simulador ModelSim: | |

| − | + | *Abra o circuito que foi salvo na aula anterior. Após abrir o Quartus, clique em [File > Open Project] e selecione a pasta onde salvou o projeto. Depois clique sobre o arquivo '''nand_gate.qpf'''. Note que abrir um projeto é diferente de abrir um arquivo, pois todos os arquivos de configuração estão associados a esse .qpf. | |

| − | + | ||

| − | + | ;Encontro 20 (5 out.): | |

| − | + | *Avaliação A1c - Simplificação de expressões lógicas: | |

| − | + | ||

| − | | | + | |

| − | + | ;Encontro 21 (10 out.): | |

| − | + | *Escreva o código VHDL e faça a simulação para o circuito correspondente a expressão lógica: | |

| − | + | Y = AB + AC' | |

| − | + | Z = A'BC + C' | |

| − | + | --> | |

| − | + | {{collapse bottom}} | |

| − | + | ||

| − | + | ===Unidade 5 - Circuitos lógicos combinacionais (com VHDL)=== | |

| − | + | * 12 ENCONTROS | |

| − | + | {{collapse top | expand=true |Unidade 5 - Circuitos lógicos combinacionais (com VHDL)}} | |

| − | + | <!-- | |

| − | + | ;Encontro 22, 23 (17 e 20 out.) | |

| − | + | *[[Preparando para gravar o circuito lógico no FPGA]] | |

| − | + | * Configurar uma porta nand no kit. | |

| − | + | *[[Laboratório - Projeto e implementação de um conversor BCD para SSD | AE1 - Atividade de Laboratório 1 ]] | |

| − | + | ||

| − | + | ;Encontro 24 (24 out.) | |

| − | + | * Conhecer o [[Código Gray]] | |

| − | + | * Implementação de conversor Binário para Gray (bin2gray) | |

| − | + | <syntaxhighlight lang=vhdl> | |

| − | + | ------------------------- | |

| − | + | -- File: bin2gray_v1.vhd -- | |

| − | + | ------------------------- | |

| − | + | entity bin2gray_v1 is | |

| − | + | port | |

| − | + | ( | |

| − | </ | + | b0, b1, b2, b3 : in bit; |

| + | g0, g1, g2, g3 : in bit | ||

| + | ); | ||

| + | end entity; | ||

| + | --Exemplo implementando o circuito diretamente com as portas lógicas | ||

| + | architecture ifsc_v1 of ____ is | ||

| + | begin | ||

| + | |||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| − | + | Como o circuito de um conversor bin2gray, possui uma certa quantidade de bits de entrada e a mesma quantidade de saída, não é adequado descrever esse circuito utilizando o tipo '''bit'''. O VHDL dispõe do tipo '''bit_vector'''; de vetores para descrever esse tipo de entrada e saída. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | ------------------------- | ||

| + | -- File: bin2gray_v2.vhd -- | ||

| + | ------------------------- | ||

| + | entity bin2gray_v2 is | ||

| + | port | ||

| + | ( | ||

| + | b : in bit_vector(3 downto 0); | ||

| + | g : out bit_vector(3 downto 0) | ||

| + | ); | ||

| + | end entity; | ||

| + | --Exemplo implementando o circuito diretamente com as portas lógicas | ||

| + | architecture ifsc_v2 of ____ is | ||

| + | begin | ||

| − | + | end architecture; | |

| + | </syntaxhighlight> | ||

| + | Caso se deseje aumentar o número de bits da entrada, na abordagem acima é necessário aumentar o número de operações ou exclusivo, e para cada quantidade de bits é necessário ter uma nova descrição. Usando corretamente a instrução '''generic''', e a instrução '''for generate''', é possível escrever um código único (genérico) para qualquer numero de bits. | ||

| + | * O GENERIC permite parametrizar um circuito, definindo os valores que se deseja alterar em um circuito em diferentes soluções. Um exemplo comum é alterar o número de bits das entradas e saídas do circuito. Essa instrução é declarada na ENTITY, antes da declaração das PORT. | ||

| − | + | <syntaxhighlight lang=vhdl> | |

| − | + | [generic ( | |

| − | + | cons_name1: const_type const_value; | |

| − | + | cons_name2: const_type const_value; | |

| − | < | + | ... |

| − | + | cons_nameN: const_type const_value);] | |

| − | + | </syntaxhighlight> | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | </ | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| + | * Uso da instrução FOR-GENERATE | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | label: FOR identificador IN faixa GENERATE | ||

| + | [Parte_Declarativa | ||

| + | BEGIN] | ||

| + | Instruções_concorrentes | ||

| + | ... | ||

| + | END GENERATE [label]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | ------------------------- | ||

| + | -- File: bin2gray_v3.vhd -- | ||

| + | ------------------------- | ||

| + | entity bin2gray_v3 is | ||

| + | generic (N : natural := 4 ); | ||

| + | port | ||

| + | ( | ||

| + | b : in bit_vector(N-1 downto 0); | ||

| + | g : out bit_vector(N-1 downto 0) | ||

| + | ); | ||

| + | end entity; | ||

| + | architecture ifsc_v3 of ____ is | ||

| + | begin | ||

| + | |||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | * Após cada implementação analise o diagrama RTL e verifique se as 3 soluções apresentadas resultam no mesmo circuito. | ||

| + | * Efetua a simulação com o Modelsim para verificar se as entradas em código binário sequêncial de "0000" até "1111" resultam corretamente nas saídas em [[Código Gray]]. | ||

| + | * Verifique se a versão bin2gray_v3 pode ser alterada para 10 bits e continua gerando o circuito correto. | ||

| + | * Descubra quantas portas ou exclusivo seriam necessárias para o caso de N bits. | ||

| + | |||

| + | |||

| + | * DESAFIO: Implementação de conversor Gray para Binário (gray2bin) | ||

| + | Considerando o que aprendeu com as duas versões do conversor '''bin2gray''', descreva o circuito do conversor '''gray2bin'''. | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | entity | + | ------------------------- |

| + | -- File: gray2bin.vhd -- | ||

| + | ------------------------- | ||

| + | entity gray2bin is | ||

| + | generic (N : natural := 4 ) | ||

port | port | ||

( | ( | ||

| − | + | g : in std_logic_vector(____) | |

| − | + | b : out std_logic_vector(____) | |

| − | + | ) | |

| − | + | end entity | |

| − | |||

| − | ) | ||

| − | end entity | ||

| − | + | architecture ifsc_v1 of ____ is | |

| − | architecture | + | begin |

| + | end architecture | ||

| + | architecture ifsc_v2 of ____ is | ||

begin | begin | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | end architecture | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | * | + | ;Encontro 25 e 26 (26 e 31 out.) |

| − | + | * Conhecer o multiplexador digital. | |

| − | + | Um multiplexador digital de N entradas e 1 saída, frequentemente abreviado como MUX N:1, é um circuito digital muito utilizado para rotear sinais digitais Ele desempenha a função de selecionar uma das entradas para ser encaminhada para a saída com base em um sinal de seleção (ou controle). | |

| − | * | + | *'''MUX2:1''' |

| − | + | A tabela verdade que descreve um MUX2:1 é mostrada abaixo: | |

| − | + | <center> | |

| − | < | + | {| class="wikitable" style="text-align:center;" |

| − | -- | + | |- style="font-weight:bold;" |

| − | + | ! X1 | |

| − | + | ! X0 | |

| − | + | ! Sel | |

| − | + | ! style="background-color:#c0c0c0;" | Y | |

| − | + | |- | |

| − | + | | 0 | |

| − | + | | 0 | |

| − | + | | 0 | |

| − | + | | style="background-color:#c0c0c0;" | 0 | |

| − | + | |- | |

| − | + | | 0 | |

| − | + | | 0 | |

| − | + | | 1 | |

| − | + | | style="background-color:#c0c0c0;" | 0 | |

| − | + | |- | |

| − | + | | 0 | |

| − | + | | 1 | |

| − | + | | 0 | |

| − | + | | style="background-color:#c0c0c0;" | 1 | |

| − | + | |- | |

| − | </ | + | | 0 |

| − | + | | 1 | |

| − | + | | 1 | |

| − | + | | style="background-color:#c0c0c0;" | 0 | |

| − | + | |- | |

| − | + | | 1 | |

| − | + | | 0 | |

| + | | 0 | ||

| + | | style="background-color:#c0c0c0;" | 0 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | style="background-color:#c0c0c0;" | 1 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | style="background-color:#c0c0c0;" | 1 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | style="background-color:#c0c0c0;" | 1 | ||

| + | |} | ||

| + | </center> | ||

| + | |||

| + | O MUX2:1 também pode ser representado de forma resumida por: | ||

| + | <center> | ||

| + | {| class="wikitable" style="text-align:center;" | ||

| + | |- style="font-weight:bold;" | ||

| + | ! X1 | ||

| + | ! X0 | ||

| + | ! Sel | ||

| + | ! style="background-color:#c0c0c0;" | Y | ||

| + | |- | ||

| + | | - | ||

| + | | X0 | ||

| + | | 0 | ||

| + | | style="background-color:#c0c0c0;" | X0 | ||

| + | |- | ||

| + | | X1 | ||

| + | | - | ||

| + | | 1 | ||

| + | | style="background-color:#c0c0c0;" | X1 | ||

| + | |} | ||

| + | </center> | ||

| + | Onde o X0 e X1 na entrada podem assumir os valores 0 ou 1, e o simbolo "-" corresponde ao ''don't care'' (em VDHL) | ||

| + | |||

| + | A função booleana que descreve a operação de um MUX 2:1 pode ser representada da seguinte forma: | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | <math> Y = \overline{Sel} . X0 + Sel . X1 </math> | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | Onde Y é a saída; Sel é o sinal de seleção; X0 e X1 são as entradas. | |

| − | * | + | *'''MUX4:1''' |

| − | + | O MUX4:1 pode ser representado de forma resumida pela tabela verdade: | |

| − | |||

| − | |||

| − | |||

| − | + | <center> | |

| − | { | + | {| class="wikitable" style="text-align:center;" |

| − | + | |- style="font-weight:bold;" | |

| − | + | ! colspan="4" | Entradas | |

| − | + | ! colspan="2" | Seleção | |

| − | + | ! Saída | |

| − | + | |- style="font-weight:bold;" | |

| − | + | | X3 | |

| − | + | | X2 | |

| − | + | | X1 | |

| − | + | | X0 | |

| − | + | | Sel1 | |

| − | + | | Sel0 | |

| − | + | | style="background-color:#c0c0c0;" | Y | |

| − | + | |- | |

| − | + | | - | |

| − | + | | - | |

| − | + | | - | |

| − | + | | X0 | |

| − | + | | 0 | |

| − | + | | 0 | |

| − | + | | style="background-color:#c0c0c0;" | X0 | |

| − | + | |- | |

| − | + | | - | |

| − | + | | - | |

| − | + | | X1 | |

| − | : | + | | - |

| + | | 0 | ||

| + | | 1 | ||

| + | | style="background-color:#c0c0c0;" | X1 | ||

| + | |- | ||

| + | | - | ||

| + | | X2 | ||

| + | | - | ||

| + | | - | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | style="background-color:#c0c0c0;" | X2 | ||

| + | |- | ||

| + | | X3 | ||

| + | | - | ||

| + | | - | ||

| + | | - | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | style="background-color:#c0c0c0;" | X3 | ||

| + | |} | ||

| + | </center> | ||

| + | A função booleana que descreve a operação de um MUX 4:1 pode ser representada da seguinte forma: | ||

| + | |||

| + | |||

| + | <math> Y = X0 . \overline{Sel1} . \overline{Sel0} + X1 . \overline{Sel1} . Sel0 + X2 . Sel1 . \overline{Sel0} + X3 . Sel1 . Sel0 </math> | ||

| − | + | Dada a função booleana do MUX4:1 é simples para descreve-lo em VHDL utilizando apenas operadores lógicos. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | <syntaxhighlight lang=vhdl> | |

| − | + | entity mux4x1 is | |

| − | + | port | |

| − | + | ( | |

| − | + | -- Input ports | |

| − | : | + | X: in bit_vector (3 downto 0); |

| − | + | Sel : in bit_vector (1 downto 0); | |

| + | -- Output ports | ||

| + | Y : out bit | ||

| + | ); | ||

| + | end entity; | ||

| − | + | -- Implementação com lógica pura | |

| − | + | architecture v_logica_pura of mux4x1 is | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | begin | |

| − | + | Y <= (X(0) and (not Sel(1)) and (not Sel(0))) or | |

| − | + | ... | |

| − | + | end architecture; | |

| − | + | </syntaxhighlight> | |

| − | : | + | No entanto, o MUX4:1 também pode ser descrito utilizando a instrução '''WHEN-ELSE''' |

| − | + | <syntaxhighlight lang=vhdl> | |

| − | + | <optional_label>: <target> <= | |

| − | + | <value> when <condition> else | |

| + | <value> when <condition> else | ||

| + | <value> when <condition> else | ||

| + | ... | ||

| + | <value>; | ||

| + | </syntaxhighlight> | ||

| − | + | *Importante: O último ELSE deve cobrir todos os demais valores para evitar a criação de LATCHES. | |

| − | + | Warning (13012): Latch ... has unsafe behavior | |

| − | |||

| − | + | * No QuartusII existe um template pronto para ser utilizado em: '''[Edit > Insert Template > Language templates = VHDL (+) > Constructs (+) > Concurrent Statemens (+) > Conditional Signal Assignment]''' | |

| − | |||

| − | : | + | No caso do MUX4:1 ele poderia ser descrito como: |

| − | + | <syntaxhighlight lang=vhdl> | |

| − | + | -- Implementação com WHEN ELSE | |

| − | + | architecture v_WHEN_ELSE of mux4x1 is | |

| − | + | begin | |

| − | + | Y <= X(0) when Sel = "00" else | |

| − | + | X(1) when Sel = "01" else | |

| + | X(2) when Sel = "10" else | ||

| + | X(3); | ||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| − | + | Outra forma de descrever o MUX4:1 seria utilizando a instrução '''WITH-SELECT''' | |

| − | : | ||

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| + | <optional_label>: with <expression> select | ||

| + | <target> <= | ||

| + | <value> when <choices>, | ||

| + | <value> when <choices>, | ||

| + | <value> when <choices>, | ||

| + | ... | ||

| + | <value> when others; | ||

| + | </syntaxhighlight> | ||

| − | + | *Importante: Para cobrir todas as demais possibilidades deve ser utilizado o WHEN OTHERS evitando novamente a criação de LATCHES, ou erros de análise. | |

| − | + | Error (10313): VHDL Case Statement error ...: Case Statement choices must cover all possible values of expression | |

| − | + | * No QuartusII existe um template pronto para ser utilizado em: '''[Edit > Insert Template > Language templates = VHDL (+) > Constructs (+) > Concurrent Statemens (+) > Selected Signal Assignment]'''. '''Mas ATENÇÃO, faltam as virgulas após cada escolha'''. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | -- | + | -- Implementação com WITH SELECT |

| − | + | architecture v_WITH_SELECT of mux4x1 is | |

| − | signal < | + | begin |

| + | with Sel select | ||

| + | Y <= X(0) when "00", -- note o uso da , | ||

| + | X(1) when "01", | ||

| + | X(2) when "10", | ||

| + | X(3) when others; -- note o uso de others, para todos os demais valores. | ||

| + | -- Não pode ser substituido por "11" mesmo que o signal seja bit_vector. | ||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| − | - | + | * Note que para associar uma entre várias arquiteturas com a sua ENTITY pode-se utilizar a instrução CONFIGURATION. No exemplo abaixo a ARCHITECTURE que está descomentada é a que será associada a ENTITY mux4x1. |

| − | + | * Caso não se use a instrução CONFIGURATION, a última ARCHITECTURE será associada a ENTITY. | |

| + | * Apesar de apenas uma das ARCHITECTUREs ser associada, todas elas devem estar sintaticamente corretas, pois passarão pelo processo de ANÁLISE E SINTESE. | ||

| − | -- | + | <syntaxhighlight lang=vhdl> |

| − | + | -- Design Unit que associa a architecture com a entity | |

| − | + | configuration cfg_ifsc of mux4x1 is | |

| − | + | for v_logica_pura end for; | |

| − | + | -- for v_WHEN_ELSE end for; | |

| − | + | -- for v_WITH_SELECT end for; | |

| + | end configuration; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | * Faça a análise e sintese do mux4x1, associando a architecture v_logica_pura, depois v_WITH_SELECT, depois v_WHEN e por último v_IF_ELSE. | |

| + | * Note a diferença entre os RTL Viewer obtidos para cada architecture. | ||

| + | {{fig|2.1|Código RTL do mux4x1 v_logica_pura| RTL_mux4x1v1.png| 300 px |}} | ||

| + | {{fig|2.2|Código RTL do mux4x1 v_WHEN_ELSE| RTL_mux4x1v2.png| 400 px |}} | ||

| + | {{fig|2.3|Código RTL do mux4x1 v_WITH_SELECT| RTL_mux4x1v3.png| 200 px |}} | ||

| + | :'''OBS''': [https://en.wikipedia.org/wiki/Register-transfer_level Register Transfer-Level] (RTL) é uma abstração na qual o circuito é descrito em termos de fluxo de sinais entre os registradores presentes no hardware e as operações combinacionais realizadas com esses dados. | ||