Mudanças entre as edições de "Usuário:Kamila.r"

| (178 revisões intermediárias por 5 usuários não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

| − | + | __NOTOC__ | |

| + | #[[Modernização das aulas de Laboratório de Circuitos Lógicos | Publicação: Modernização das aulas de Laboratório de Circuitos Lógicos - 2013]]. | ||

| + | #[[Modernização das aulas de laboratório de circuítos lógicos: fase implementação | Publicação: Modernização das aulas de laboratório de circuitos lógicos: fase implementação - 2014]]. | ||

| + | #[[Projeto MALCIL - Sugestão de experimentos | Sugestão de Experimentos]]. | ||

| + | #[[Estudo de Circuitos Aritméticos e Implementação em Dispositivos Lógicos Programáveis]] | ||

| + | #[[G9:TCC_de_Kamila_Rose_da_Silva | TCC - Estudo de Unidades de Aritmética implementadas com DLP ]] | ||

| − | = | + | <!-- |

| − | ; | + | *Aplicação inviabilizada pela lentidão do Quartus via cloud: |

| + | **Aplicação do uso de decodificadores de endereço: Montar circuito que simula o barramento de uma CPU (TOCCI); | ||

| + | **Definição do roteiro sobre Flip-Flops: | ||

| + | #Começar com dlatch (criar: pg 278 PEDRONI); | ||

| + | #dff,tff,tffe,jkff,srff; | ||

| + | #testar set/reset | ||

| + | #Mostrar tabela verdade | ||

| + | --> | ||

| + | |||

| + | {{Collapse top | Mestrado}} | ||

| + | *http://ppgeel.posgrad.ufsc.br/form/ (Marcos) | ||

| + | *http://www.feec.unicamp.br/ (Rubem) | ||

| + | *http://pgeas.ufsc.br/linhas-de-pesquisa/ (Odilson, Eraldo) | ||

| + | *http://www.lisha.ufsc.br/HomePage (Roberto de Matos e Arliones) | ||

| + | *http://www.cienciasemfronteiras.gov.br/web/csf/mestrado-profissional2 | ||

| + | *http://www.fulbright.org.br/content/view/211/59/ | ||

| + | |||

| + | {{Collapse bottom}} | ||

| + | |||

| + | {{Collapse top | 2014: Implementação}} | ||

| + | |||

| + | =Semanário do Bolsista 2014: Implementação= | ||

| + | <!-- | ||

| + | --> | ||

| + | ;Horários 1° semestre: | ||

| + | *(4h) SEG 15:30 às 19:30 | ||

| + | *(4h) TER 7:30 às 9:40 - 17:30 às 19:20 | ||

| + | *(4h) QUA 7:30 às 9:40 - 17:30 às 19:20 | ||

| + | *(4h) QUI 9:30 às 11:40 - 17:30 às 19:20 | ||

| + | *(4h) SEX 7:30 às 9:40 - 17:30 às 19:20 | ||

| + | |||

| + | ;Horários 2° semestre: | ||

| + | *(4h) SEG 13:30 às 15:40 - 17:30 às 19:20 | ||

| + | *(2h) TER 7:30 às 9:30 | ||

| + | *(6h) QUA 9:30 às 11:30 - 13:30 às 17:30 | ||

| + | *(2h) QUI 7:30 às 9:30 | ||

| + | *(6h) SEX 7:30 às 9:40 - 15:30 às 19:20 | ||

| + | |||

| + | ==Abril== | ||

| + | ;Semana 01: 01-04 Abril: | ||

*Definição dos passos iniciais do trabalho | *Definição dos passos iniciais do trabalho | ||

*Leitura dos Manuais do Protolab | *Leitura dos Manuais do Protolab | ||

*Sondagem junto aos professores sobre o tipo de experimentos utilizados em Eletrônica Digital | *Sondagem junto aos professores sobre o tipo de experimentos utilizados em Eletrônica Digital | ||

| + | *Formatação da máquina linux e transferência dos arquivos Kamila e Lacip | ||

| + | *Estudo dos manuais com experimentos | ||

| + | *Download do software QuartusII V13 | ||

| + | *Definição de proposta: fazer um formulário para os professores da área de circuitos lógicos indicando os circuitos disponíveis no Manual 8810 para que eles possam selecionar por grau de importância e/ou necessidade quais os mais utilizados e que deveriam ser propostos também no Quartus | ||

| + | ;Semana 02: 07-11 Abril: | ||

| + | *Solicitado ao suporte a instalação da nova versão do Quartus | ||

| + | *Elaboração do questionário dos professores | ||

| + | *Em conversa com a professora Elen e o professor Eduardo, ambos recomendaram que os roteiros a serem desenvolvidos deveriam partir dos circuitos mais simples, com algumas portas lógicas, para melhor entendimento do funcionamento delas e uma interação inicial mais simples com o software | ||

| + | ;Semana 03: 14-17 Abril: | ||

| + | *Término do formulário dos professores | ||

| + | *Estudo das biografias do TOKHEIM | ||

| + | *Software Quartus V13 foi instalado | ||

| + | *Testes com a nova versão | ||

| + | *Desenvolvimento de uma relação de experimentos para propor aos professores da área de CIL | ||

| + | ;Semana 04: 22-30 Abril: | ||

| + | *[https://docs.google.com/forms/d/1lAhQjeiGx9_5bnVuJKbJxzH8BDb9Ejtj1ITuqTJWb28/viewform Fomulário Professores fase: Implementação] | ||

| + | *Seleção e estudos dos experimentos: | ||

| + | |||

| + | # Portas AND > Módulo 8810 | ||

| + | # Portas OR, NOT e NOR > Módulo 8810 | ||

| + | # Porta NAND e teorema de De Morgan > Módulo 8810 | ||

| + | # Programar o FPGA > Módulo 8810 | ||

| + | # Sistema de numeração binário > | ||

| + | # Decodificador de 3 para 8, 1 para 2, 2 para 3 (binário para one-hot) > | ||

| + | # Multiplexadores/Demultiplexadores > Módulo 8810 | ||

| + | # Tipos de Flip-Flops e Latch > TOKEIM | ||

| + | # Contador UP/DOWN > TOKEIM | ||

| + | # Contadores comerciais > TOKEIM | ||

| + | # Registrador de deslocamento > TOKEIM | ||

| + | # Comparador de magnitude > Módulo 8810 | ||

| + | # Somador/Subtrator/Complemento de 2; (4 e 8 bits) > Módulo 8810 | ||

| + | #Projeto de circuito para detectar Overflow > Módulo 8810 | ||

| + | # Multiplicador > | ||

| + | #(...) | ||

| + | |||

| + | ==Maio== | ||

| + | ;Semana 05: 05-09 Maio: | ||

| + | *Definir os objetivos de cada experimento mencionado na lista: | ||

| + | |||

| + | ; Porta AND: | ||

| + | * Utilizar o '''diagrama esquemático''' do Quartus II para inserir um circuito; | ||

| + | * Gerar formas de onda para entrada de simulação usando o QSIM; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Compreender o funcionamento da porta AND; | ||

| + | * Entender a tabela verdade de circuitos lógicos; | ||

| + | * Obter as imagens e dados para a confecção de relatório técnico; | ||

| + | |||

| + | ; Portas OR, NOT e NOR: | ||

| + | * Utilizar o '''diagrama esquemático''' do Quartus II para inserir um circuito; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - '''diagrama temporal''' (uso de cursores para medições); | ||

| + | * Compreender o funcionamento das porta OR, NOT e NOR; | ||

| + | * Entender a tabela verdade de circuitos lógicos; | ||

| + | |||

| + | ; Porta NAND e teorema de De Morgan: | ||

| + | * Utilizar o '''diagrama esquemático''' do Quartus II para inserir um circuito; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Compreender o funcionamento da porta NAND; | ||

| + | * Utilizar portas NAND para a implementação de portas OR, NOR, NOT e AND; | ||

| + | * Entender a equivalência de circuitos; | ||

| + | |||

| + | ; Programar o FPGA: | ||

| + | * Utilizar o '''diagrama esquemático''' do Quartus II para inserir um circuito; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Compreender o funcionamento das portas XOR e XNOR; | ||

| + | * Definir a pinagem de saída; | ||

| + | * Programar o FPGA para implementar um comparador de palavras (ou gerador de paridade); DE2-115 | ||

| + | * Entender o preenchimento da tabela verdade seguindo o resultado apresentado pelo circuito; | ||

| + | |||

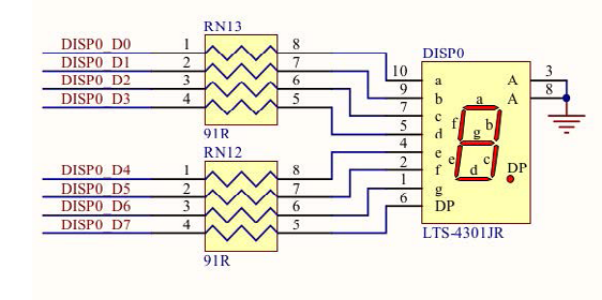

| + | ; Sistema de numeração binário: | ||

| + | * Compreender o funcionamento do display de sete segmentos; | ||

| + | * Compreender o funcionamento do codificador binário para sete segmentos; | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Fazer a simulação funcional do circuito com o QSIM; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DE2-115 | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Decodificador de 3 para 8, 1 para 2, 2 para 4 (binário para one-hot): | ||

| + | * Compreender o funcionamento do decodificador 3 para 8; [http://www.ti.com/lit/ds/symlink/sn54als138a.pdf 74X138] | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Fazer a simulação funcional do circuito com o QSIM; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DE0-NANO | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Multiplexadores/Demultiplexadores: | ||

| + | * Multiplexador/Seletor de 8 para 1; [http://www.ti.com/lit/ds/symlink/sn54als151.pdf 74X151] | ||

| + | * 2x Multiplexador/Seletor de 4 para 1; [http://www.ti.com/lit/ds/symlink/sn54als153.pdf 74X153] | ||

| + | * 4x Multiplexador/Seletor de 2 para 1; [http://www.ti.com/lit/ds/symlink/sn54als158.pdf 74X157/158] | ||

| + | * XXXXXXXXXXXX | ||

| + | |||

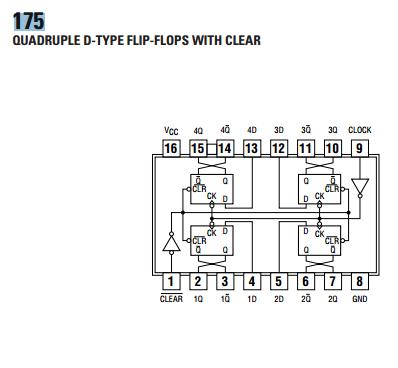

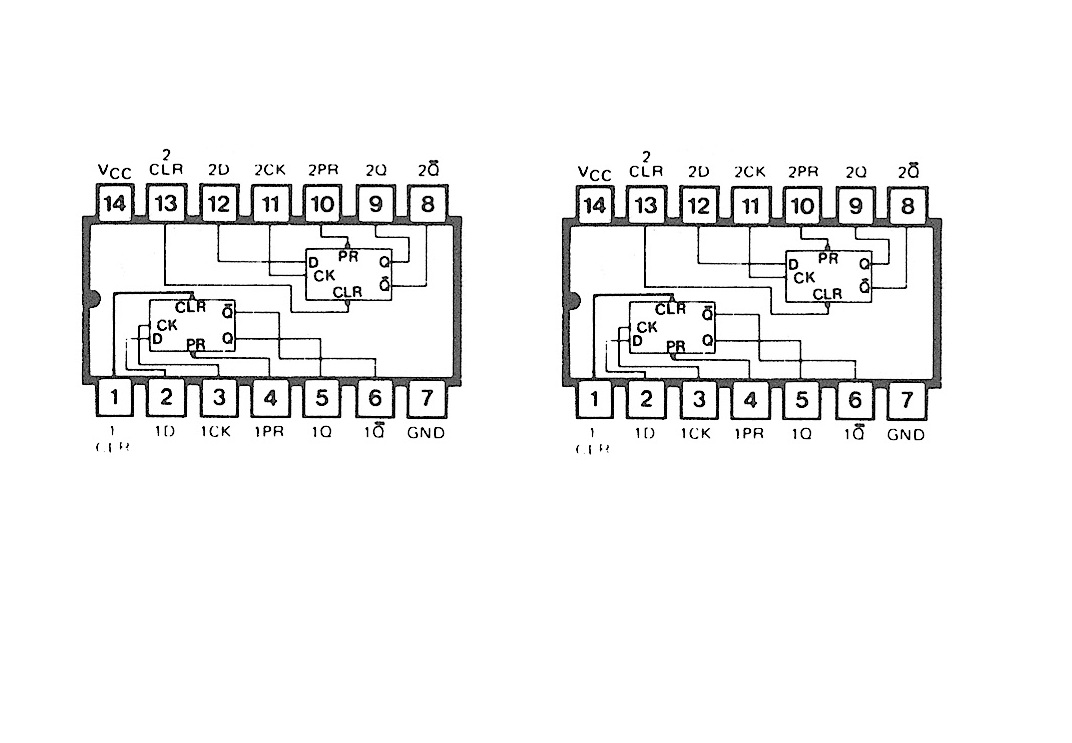

| + | ; Tipos de Flip-Flops e Latch: | ||

| + | * Compreender o funcionamento de Flip-Flops D, RS, JK e Latch RS e D; | ||

| + | * Compreender e observar o funcionando do CLOCK nos circutos; | ||

| + | * Fazer a simulação funcional dos circuito com o QSIM; | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DEO-NANO | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Contador UP/DOWN: | ||

| + | * Inserir diagrama esquemático de um circuito lógico com o Quartus II (circuito discreto); | ||

| + | * Fazer a simulação funcional de um circuito com o QSIM; | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Fazer a simulação temporal do circuito com o QSIM; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DE0-NANO | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Contadores comerciais: (74XX) | ||

| + | * Inserir diagrama esquemático de um circuito lógico com o Quartus II; | ||

| + | * Fazer a simulação funcional de um circuito com o QSIM; | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Fazer a simulação temporal do circuito com o QSIM; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DE2-115 | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Registrador de deslocamento: | ||

| + | * Inserir diagrama esquemático de um circuito lógico com o Quartus II; | ||

| + | * Fazer a simulação funcional de um circuito com o QSIM; | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Fazer a simulação temporal de um circuito com o QSIM; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DEO-NANO | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Comparador de magnitude: | ||

| + | * Utilizar o diagrama esquemático do Quartus II para inserir um circuito; | ||

| + | * Gerar formas de onda para entrada de simulação usando o QSIM; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Compreender o funcionamento do comparador de magnitude na forma de CI; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DE0-NANO | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Somador/Subtrator/Complemento de 2; (4 e 8 bits): | ||

| + | * Compreender o funcionamento dos circuitos aritméticos somador, subtrator e complemento de 2; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Analisar os resultados obtidos para entender e associar os tipos de operações realizados; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DE0-NANO | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Projeto de circuito para detectar Erros; | ||

| + | * Projetar circuito para detectar Erro em operações com números binários; | ||

| + | * Detectar a ocorrência de Erros; | ||

| + | * Entender funcionamento do Mapa de Karnaugh; | ||

| + | |||

| + | ; Multiplicador discreto: | ||

| + | * Compreender o funcionamento Multiplicador discreto; | ||

| + | * Construção de um projeto hierárquico; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Multiplicador: | ||

| + | * Compreender o funcionamento multiplicador binário de 4 bits por 4 bits; [http://www.ti.com/lit/ds/symlink/sn74284.pdf 74X284/285] | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Fazer a simulação temporal do circuito com o QSIM; | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ;Semana 06: 12-16 Maio: | ||

| + | * Término das escolhas dos circuitos e das definições dos objetivos dos mesmos; | ||

| + | * Edição do formulário dos Professores: fase implementação; | ||

| + | * Criação de um link na wiki para a descrição de todos os experimentos selecionados, incluindo objetivos e CIs que serão utilizados; | ||

| + | * Incluir o link no formulário; | ||

| + | * [[Projeto MALCIL - Sugestão de experimentos]] | ||

| + | |||

| + | ;Semana 07: 19-23 Maio: | ||

| + | |||

| + | *Início das implementações e documentação dos roteiros. | ||

| + | |||

| + | *'''Links Importantes:''' [ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE2-115/DE2_115.qsf Pinagem DE2-115] [ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE0-Nano/DE0_Nano.qsf Pinagem DE0-NANO] | ||

| + | |||

| + | ;Semana 08: 26-30 Maio: | ||

| + | |||

| + | *Implementações dos experimentos: 1/2/3/... | ||

| + | *Roteiro 1 -OK (Falta: Inserir Tabela Verdade) | ||

| + | |||

| + | ==Junho== | ||

| + | ;Semana 09: 02-06 Junho: | ||

| + | *Editar o experimento do roteiro 1; | ||

| + | *Implementar o .vwf e disponibilizar o doc no roteiro pelo Dropbox; | ||

| + | *Continuar implementando os experimentos propostos; | ||

| + | |||

| + | ;Semana 10: 09-13 Junho: | ||

| + | *Construção do Roteiro 2; | ||

| + | *Implementação do experimento 3/4; | ||

| + | <code>Dúvidas: | ||

| + | - Sobre o exp4, foi definido um circuito com apenas portas XNOR; | ||

| + | - Definir circuito para exp3 | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ;Semana 11: 16-18 Junho: | ||

| + | *Fazer resumo estendido sobre a pesquisa de 2013 durante a semana; | ||

| + | *Após término do resumo, dar início a confecção do banner; | ||

| + | |||

| + | |||

| + | ;Semana 12: 24-27 Junho: | ||

| + | *Implementação do Exp3 e estudos sobre o tema; | ||

| + | *Formulação roteiro 3; | ||

| + | *Término artigo SEPEI; | ||

| + | |||

| + | ==Julho== | ||

| + | ;Semana 13: 30-04 Julho: | ||

| + | *Continuando implementação dos experimentos e roteiros; | ||

| + | *Revisão do roteiro do contador para ajudar a Prof Elen em aula de laboratório com alunos do Integrado dia 07/07; | ||

| + | |||

| + | ;Semana 14: 07-11 Julho: | ||

| + | |||

| + | *Auxilar aula de laboratório CIL (Roteiro contador); | ||

| + | *Implementação experimento 4; | ||

| + | *Finalizar roteiros 3; | ||

| + | |||

| + | ;Semana 15 e 16: 14-25 Julho: | ||

| + | *Experimentos 4,5,9,10 e 11; | ||

| + | |||

| + | ==Agosto== | ||

| + | ;Semana 16 e 17: 30 Julho - 08 Agosto: | ||

| + | *Roteiros 4,5,9,10 e 11; | ||

| + | Obs:Quartus com problema na programação do kit | ||

| + | *Experimento 4: | ||

| + | <code> | ||

| + | #============================================================ | ||

| + | # SW | ||

| + | #============================================================ | ||

| + | set_location_assignment PIN_AB28 -to SW[0] | ||

| + | set_location_assignment PIN_AC28 -to SW[1] | ||

| + | set_location_assignment PIN_AC27 -to SW[2] | ||

| + | set_location_assignment PIN_AD27 -to SW[3] | ||

| + | set_location_assignment PIN_AB27 -to SW[4] | ||

| + | set_location_assignment PIN_AC26 -to SW[5] | ||

| + | set_location_assignment PIN_AD26 -to SW[6] | ||

| + | set_location_assignment PIN_AB26 -to SW[7] | ||

| + | #============================================================ | ||

| + | # LED | ||

| + | #============================================================ | ||

| + | set_location_assignment PIN_E21 -to LEDG[0] | ||

| + | set_location_assignment PIN_E22 -to LEDG[1] | ||

| + | set_location_assignment PIN_E25 -to LEDG[2] | ||

| + | set_location_assignment PIN_E24 -to LEDG[3] | ||

| + | set_location_assignment PIN_H21 -to LEDG[4] | ||

| + | </syntaxhighlight> | ||

| + | *DE0-NANO: family='''Cyclone IV''' device='''EP4CE22F17C6N''' | ||

| + | *DE2-115: family='''Cyclone IV''' device='''EP4CE115F29C7N''' | ||

| + | ;Semana 18: 11-15 Agosto: | ||

| + | *Elaboração do banner para o SEPEI; | ||

| + | ;IMPORTANTE: | ||

| + | Erro encontrado no arquivo de pinagem da DE2-115: Os pinos correspondentes aos leds vermelhos(LED1 e LED2) estão invertidos | ||

| + | #LED1- PIN_F19 | ||

| + | #LED2- PIN_E19 | ||

| + | *Print: ordem dos pinos invertida | ||

| + | [[Imagem:erroArq.png]] | ||

| + | *Fazer um experimento de contador assíncrono crescente para colocar as imagens no banner(sem pinagem e sem display 7-seg). Para uma simples explicação. | ||

| + | |||

| + | ;Semana 19: 18-22 Agosto: | ||

| + | *Roteiro 5; | ||

| + | *Finalização do banner SEPEI; | ||

| + | *Estudar PEDRONI e Módulo 8810 para definir quais implementações que ainda não foram feitas(Exp6, 7, 8, 12, 13, 14, 15 e 16); | ||

| + | |||

| + | ;Semana 20: 25-29 Agosto: | ||

| + | *Experimento 12; | ||

| + | *Estudos sobre exp 15 e 16; | ||

| + | *Novo roteiro do cont assíncrono crescente atualizado para Quartus v.13 (Apresentação para os Profs); | ||

| + | [[Contador Assíncrono Crescente - Roteiro para implementação e simulação com QUARTUS II(v.13), QSIM e kit DE2-115]] | ||

| + | |||

| + | ==Setembro== | ||

| + | ;Semana 21: 01-05 Setembro: | ||

| + | *Semana SEPEI; | ||

| + | ;Semana 22: 08-12 Setembro: | ||

| + | *Tutorial sobre Quartus para profs da área; | ||

| + | *Editar Contador assíncrono crescente e o Experimento1 com os primeiros passos para inclusão do diagrama esquemático no QuartusI; | ||

| + | *Nomear cada experimento para incluir na listagem do banner pra MCC; | ||

| + | *Elaboração do banner pra MCC; | ||

| + | Rascunho da listagem dos nomes dos experimentos: | ||

| + | # Introdução à ferramenta de ensino Quartus II; | ||

| + | # Simulação de portas do tipo OR, NOT e NOR; | ||

| + | # Aplicação do Teorema de De Morgan; | ||

| + | # Programação no FPGA; | ||

| + | # Introdução à sistema de numeração binário; | ||

| + | # Implementação de Decodificadores; | ||

| + | # Implementação de Multiplexadores; | ||

| + | # Introdução à tipos de Flip-Flops; | ||

| + | # Contadores assíncronos crescente e decrescente (Discretos); | ||

| + | # Contador assíncrono crescente (Comercial); | ||

| + | # Registador de deslocamento; | ||

| + | # Comparador de magnitude; | ||

| + | # Aritmética binária(Somador/Subtrator/Complemento de 2); | ||

| + | # Projeto de circuito para detectar Erros e aplicação do Mapa de Karnaugh; | ||

| + | # Multiplicador (discreto); | ||

| + | # Multiplicador; | ||

| + | |||

| + | ;Semana 22: 15-19 Setembro: | ||

| + | *Implementação dos experimentos que envolvem circuitos aritméticos no Quartus. | ||

| + | *Elaboração do mini curso Quartus para a MCC; | ||

| + | |||

| + | ;Semana 23: 22-26 Setembro: | ||

| + | *Implementação do experimento e roteiro do Comparador de magnitude; | ||

| + | *Roteiro sobre circuitos aritméticos; | ||

| + | |||

| + | ==Outubro== | ||

| + | ;Semana 24: 06-10 Outubro: | ||

| + | *'''Programação para o mês de Outubro: Terminar todos os experimentos e roteiros.''' | ||

| + | ;Semana 25: 13-17 Outubro: | ||

| + | *MCC; | ||

| + | ;Semana 26 e 27: 20 - 31 Outubro: | ||

| + | *Implementação do roteiro Multiplicador (Comercial); | ||

| + | *Implementação do experimento e roteiro Multiplicador (Discreto); | ||

| + | *Implementação do experimento Multiplexadores; | ||

| + | |||

| + | Exemplo tabela verdade: | ||

| + | *Preencha a tabela verdade: | ||

| + | |||

| + | {| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

| + | ! colspan="6" style="background: #efefef;" | Entradas | ||

| + | ! colspan="1" style="background: #ffdead;" | Saídas | ||

| + | |- | ||

| + | !width="30"| A | ||

| + | !width="30"| B | ||

| + | !width="30"| C | ||

| + | !width="30"| D | ||

| + | !width="30"| Sel0 | ||

| + | !width="30"| Sel1 | ||

| + | !width="50"| y | ||

| + | |- | ||

| + | | || || || || 0 || 0 || | | ||

| + | |- | ||

| + | | || || || || 0 || 1 || | | ||

| + | |- | ||

| + | | || || || || 1 || 0 || | | ||

| + | |- | ||

| + | | || || || || 1 || 1 || | | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | |||

| + | ==Novembro== | ||

| + | |||

| + | ;Semana 28: 03 - 07 Novembro: | ||

| + | *Estudar o experimento do Decod de endereços. Obs.: Não esquecer do exemplo de aplicação no roteiro; | ||

| + | *Iniciando a documentação do relatório técnico final; | ||

| + | |||

| + | ;Semana 29: 10 - 14 Novembro: | ||

| + | *Término do roteiro de Circuitos aritméticos; | ||

| + | *Desenvolvimento do relatório técnico. | ||

| + | |||

| + | ;Semana 30: 17 - 21 Novembro: | ||

| + | *Implementação e roteiro Decod endereços; | ||

| + | *Estudar mapa de Karnaugh; | ||

| + | *Obs.: Faltando terminar os Resultados do relatório técnico; | ||

| + | |||

| + | ;Semana 31: 24 - 28 Novembro: | ||

| + | *Término do relatório final; | ||

| + | *Definição do roteiro sobre Flip-Flops: | ||

| + | #Começar com dlatch (criar: pg 278 PEDRONI); | ||

| + | #dff,tff,tffe,jkff,srff; | ||

| + | #testar set/reset | ||

| + | #Mostrar tabela verdade | ||

| + | #Simulação temporal; | ||

| + | *Implementar 3 mini-roteiros: | ||

| + | # Como incluir .bdf em um projeto e uso do top-level (Como trocar a família do FPGA); - OK | ||

| + | # Simulação funcional (como criar formas de onda); - OK | ||

| + | # Simulação temporal (como criar formas de onda); - OK | ||

| + | |||

| + | *Reimplementar decodificador 7-seg discreto a partir do Mapa de Karnaugh; - OK | ||

| + | *Implementar Somador comercial no lugar do projeto de detecção de erros (fazer simulação temporal e propor a comparação com discreto -- qual é mais rápido?); - OK | ||

| + | *Aplicação do uso de decodificadores de endereço: Montar circuito que simula o barramento de uma CPU (TOCCI); | ||

| + | *"Assinar" projetos; | ||

| + | |||

| + | {{Collapse bottom}} | ||

{{Collapse top | 2013: Pesquisa}} | {{Collapse top | 2013: Pesquisa}} | ||

| + | |||

=Diário do Bolsista 2013: Pesquisa= | =Diário do Bolsista 2013: Pesquisa= | ||

;07mai2013: | ;07mai2013: | ||

| Linha 596: | Linha 1 004: | ||

*Realizar testes com o Quartus com 2 alunos. | *Realizar testes com o Quartus com 2 alunos. | ||

*Relatório Técnico. | *Relatório Técnico. | ||

| + | {{Collapse bottom}} | ||

| + | {{Collapse top | Roteiros - Contadores Assíncronos Crescente}} | ||

| + | |||

| + | * [[Contador Assíncrono Crescente - Roteiro para montagem na matriz de contatos real]] | ||

| + | * [[Contador Assíncrono Crescente - Roteiro para simulação no MULTISIM e montagem na matriz de contatos virtual]] | ||

| + | * [[Contador Assíncrono Crescente - Roteiro para implementação e simulação com QUARTUS II, QSIM e kit DE2-115]] | ||

| + | * [http://wiki.sj.ifsc.edu.br/index.php/Contador_Ass%C3%ADncrono_Crescente_-_Roteiro_para_implementa%C3%A7%C3%A3o_e_simula%C3%A7%C3%A3o_com_QUARTUS_II%28v.13%29,_QSIM_e_kit_DE2-115 Contador Assíncrono Crescente - Roteiro para implementação e simulação com QUARTUS II, QSIM e kit DE2-115 V.13 ] | ||

| + | |||

{{Collapse bottom}} | {{Collapse bottom}} | ||

| − | + | {{Collapse top |Métodos de pesquisa e aplicação }} | |

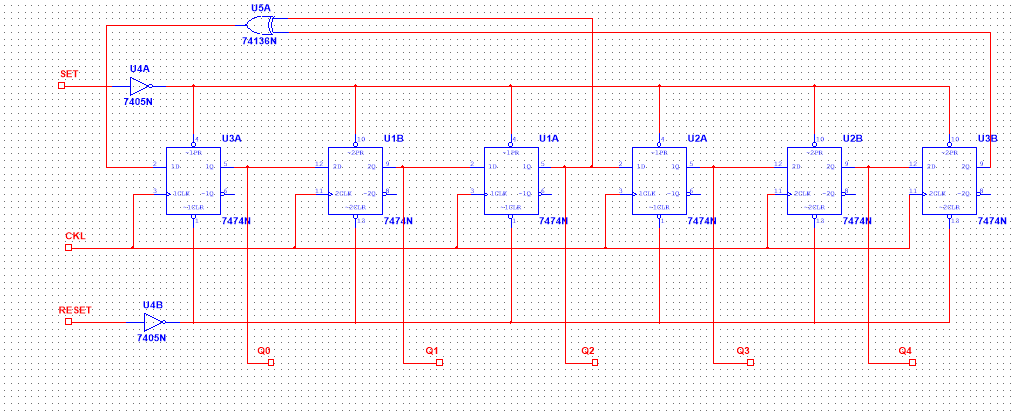

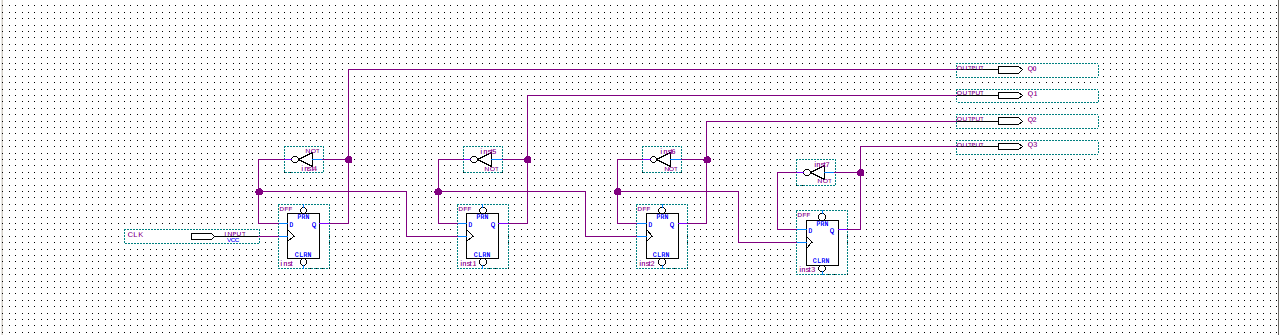

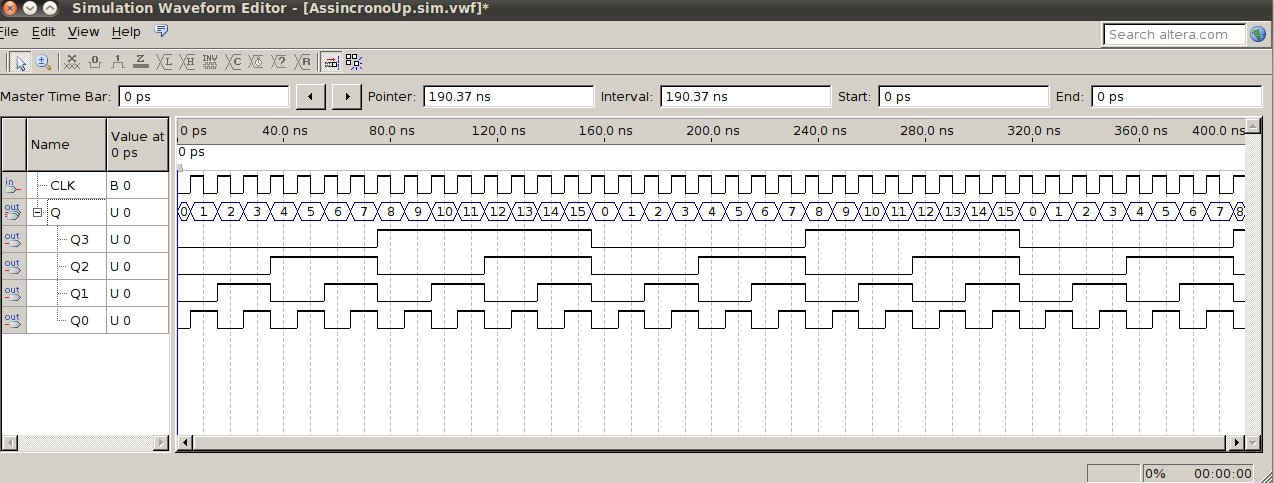

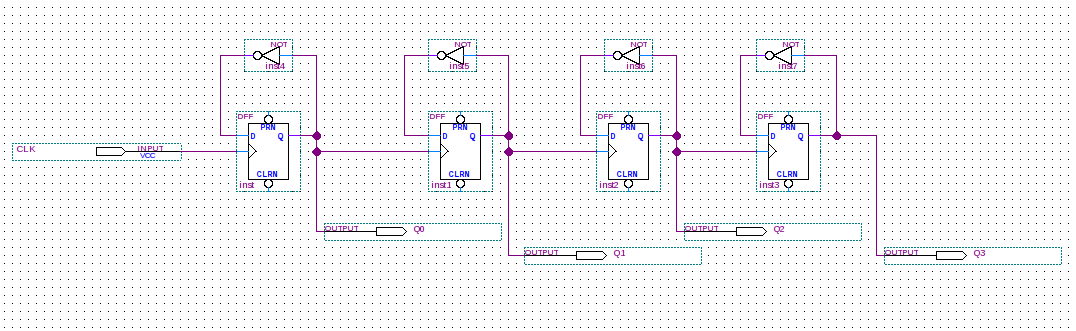

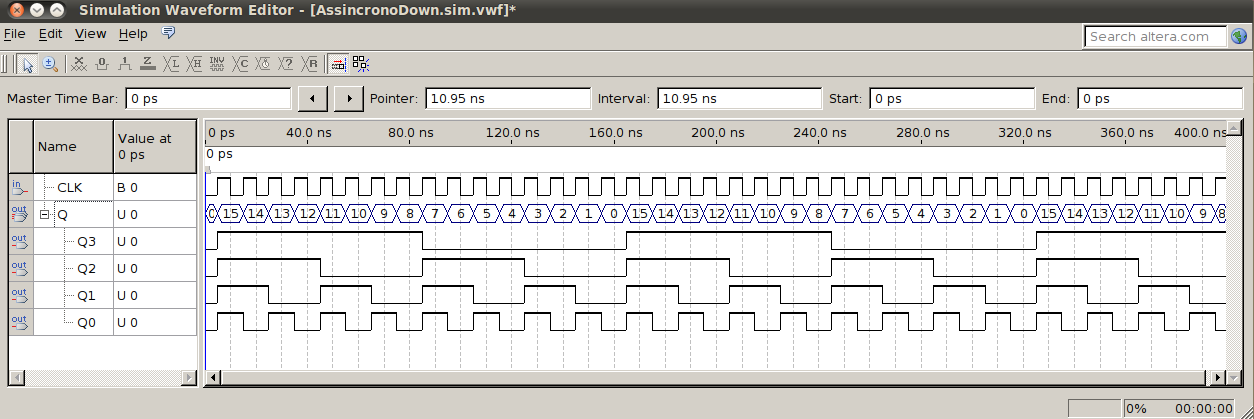

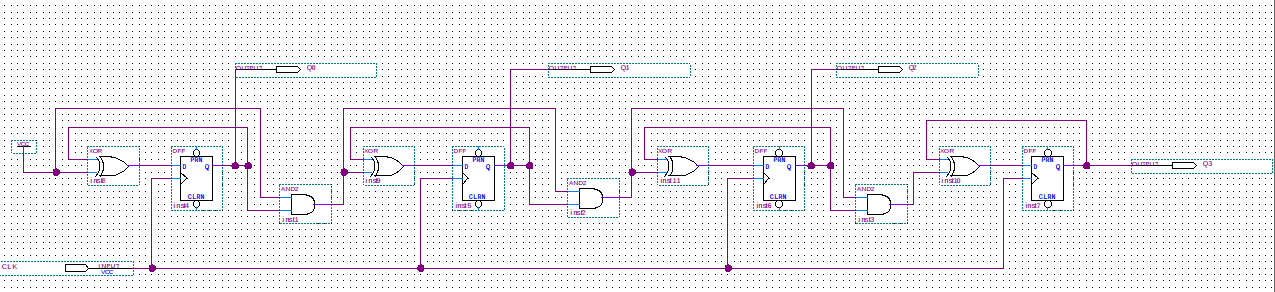

<big>'''Contador Assíncrono Crescente:'''</big> | <big>'''Contador Assíncrono Crescente:'''</big> | ||

| Linha 605: | Linha 1 021: | ||

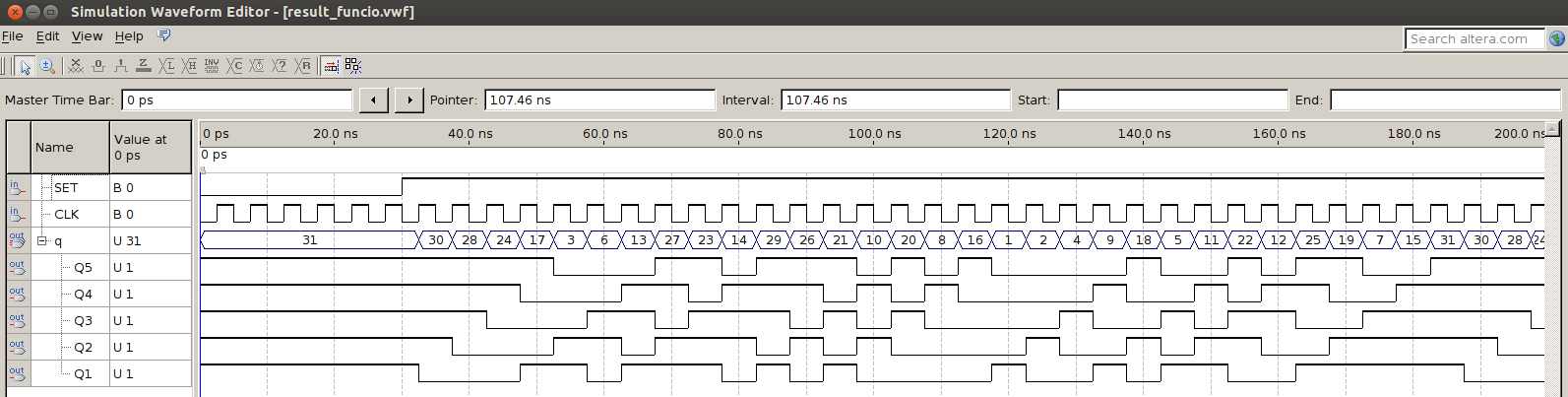

*'''QSim Funcional:''' | *'''QSim Funcional:''' | ||

[[Imagem:Kamila401.png|800px]] | [[Imagem:Kamila401.png|800px]] | ||

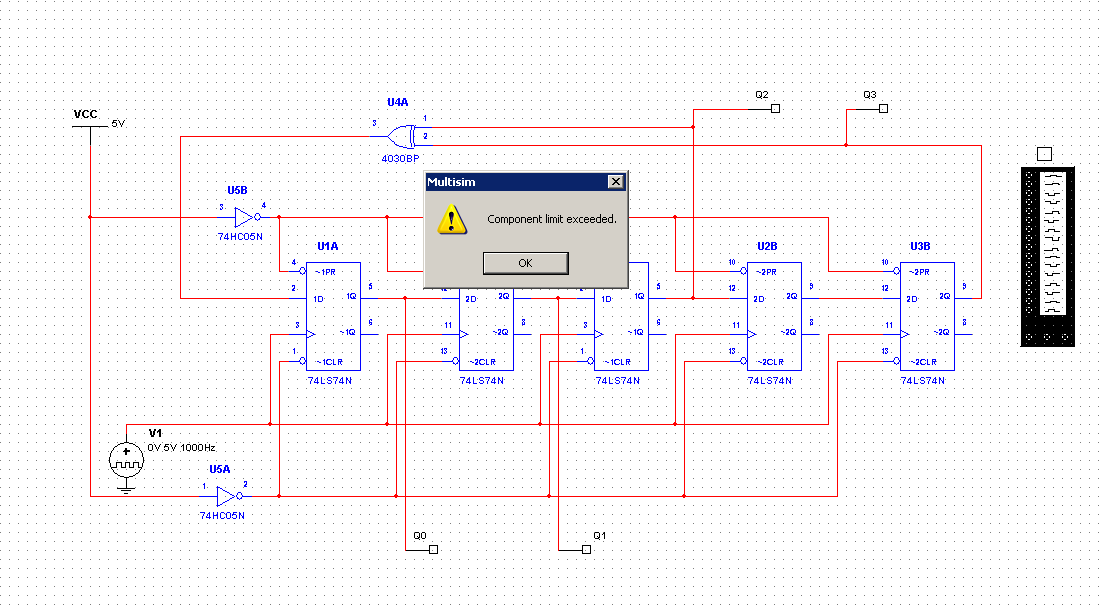

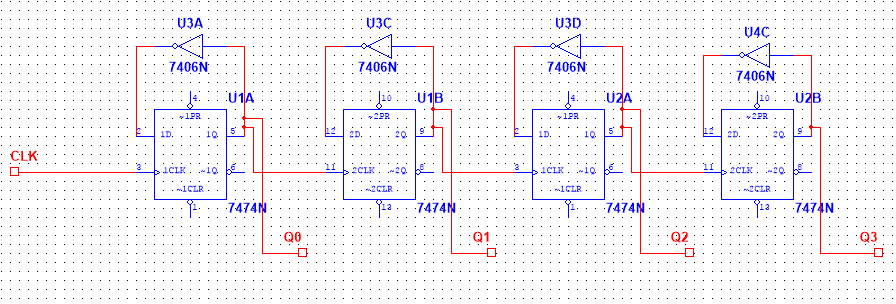

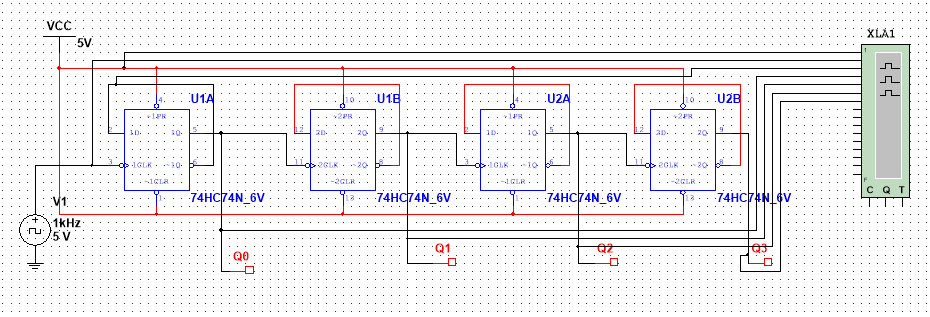

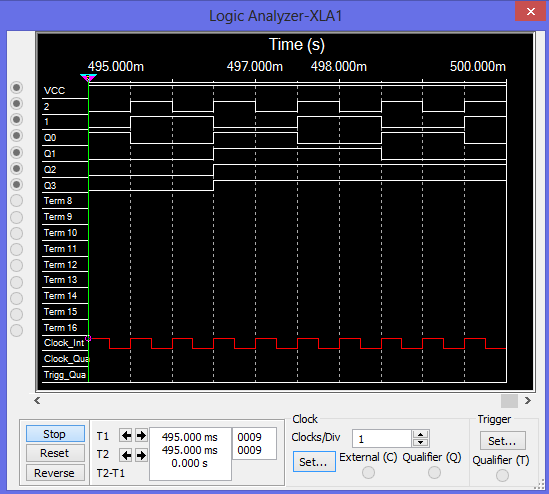

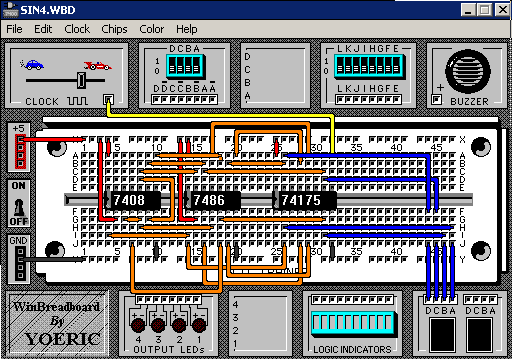

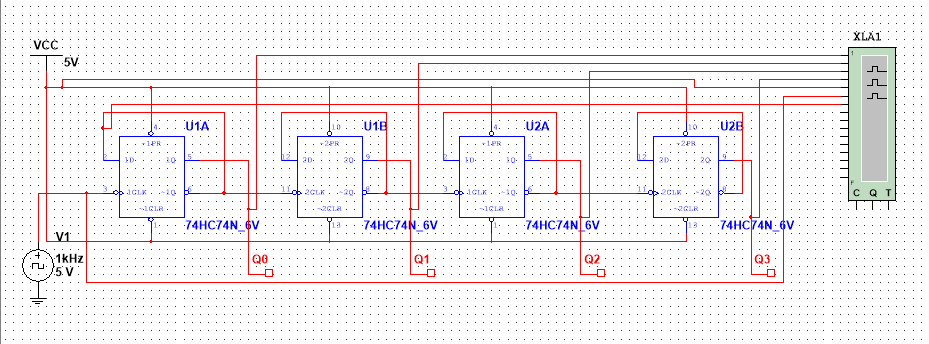

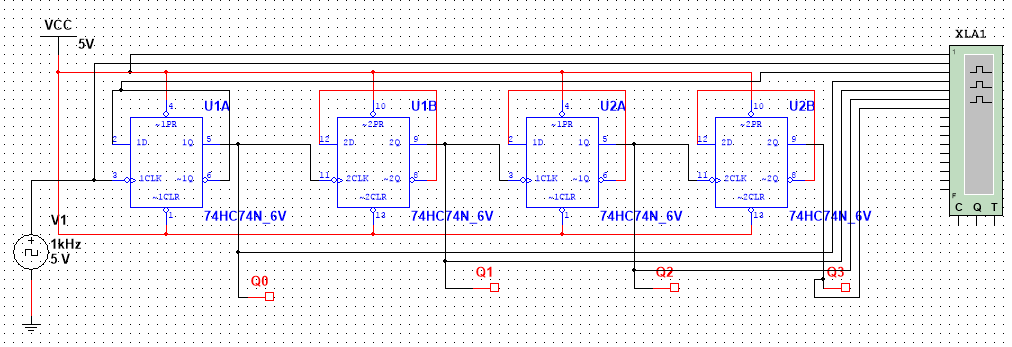

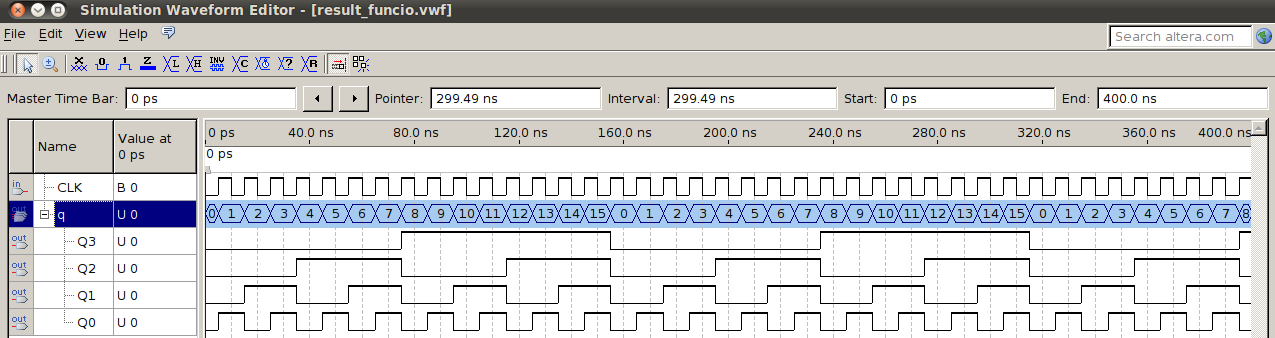

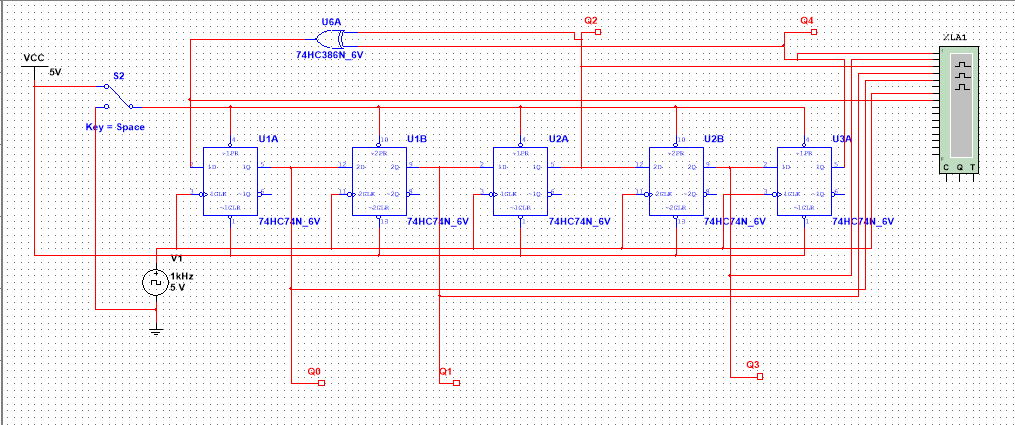

| − | *''' | + | *'''Multisim:''' |

[[Imagem:Kamila41.png|800px]] | [[Imagem:Kamila41.png|800px]] | ||

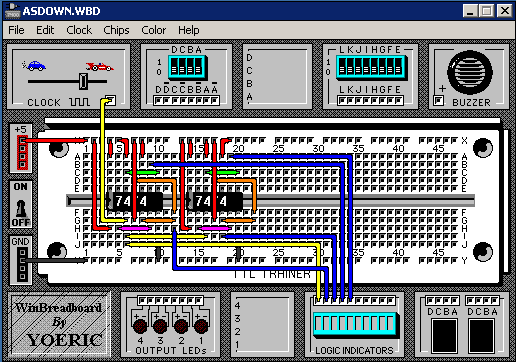

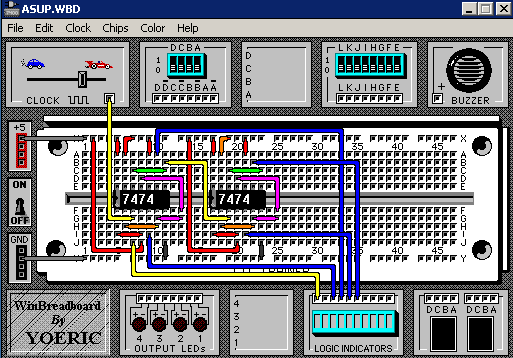

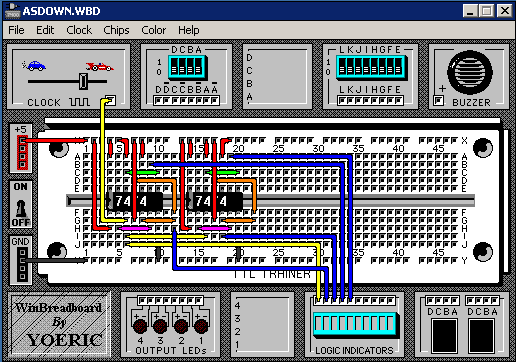

*'''Protoboard virtual:''' | *'''Protoboard virtual:''' | ||

| Linha 617: | Linha 1 033: | ||

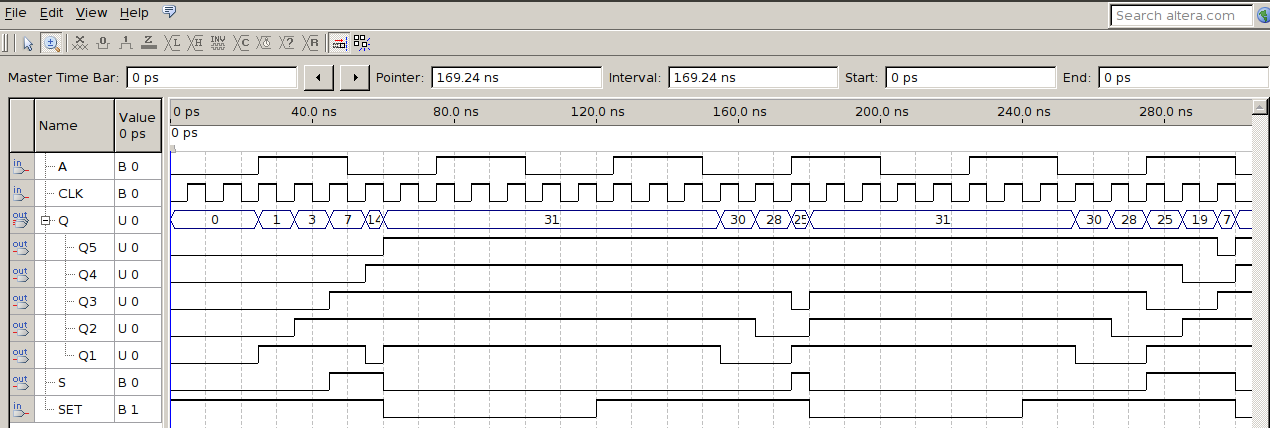

*'''QSim funcional:''' | *'''QSim funcional:''' | ||

[[Imagem:Kamila403.png|800px]] | [[Imagem:Kamila403.png|800px]] | ||

| − | *''' | + | *'''Multisim:''' |

[[Imagem:Kamila44.png|800px]] | [[Imagem:Kamila44.png|800px]] | ||

*'''Protoboard virtual:''' | *'''Protoboard virtual:''' | ||

| Linha 625: | Linha 1 041: | ||

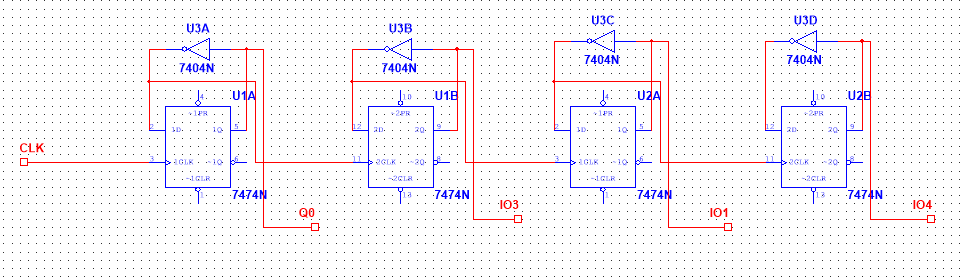

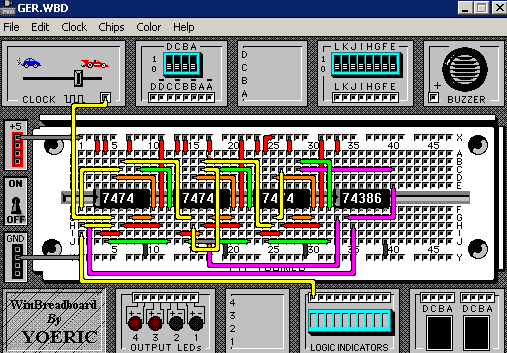

<big>'''Contador Síncrono:'''</big> | <big>'''Contador Síncrono:'''</big> | ||

| − | |||

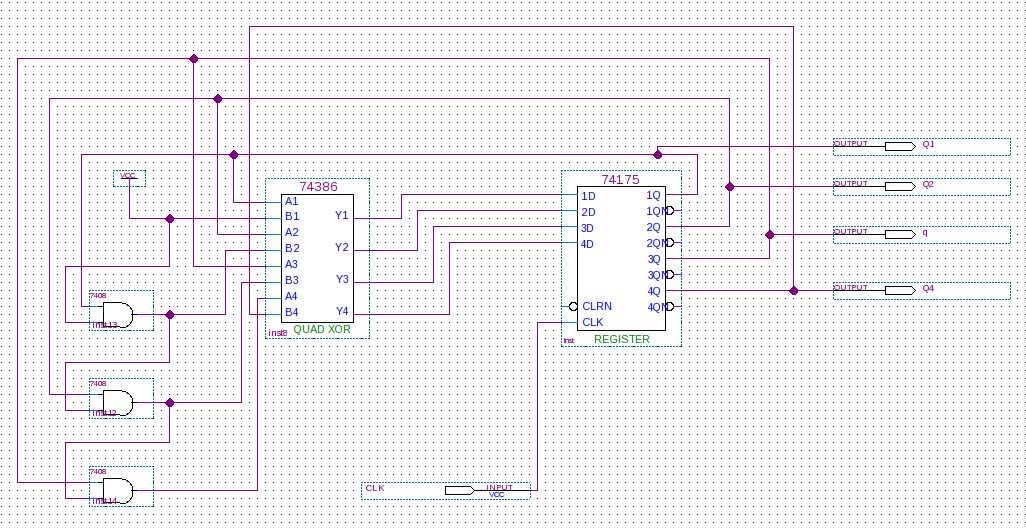

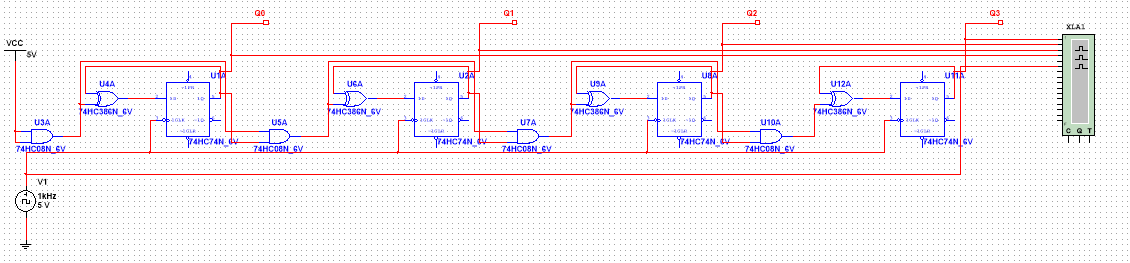

*'''Quartus:''' | *'''Quartus:''' | ||

[[Imagem:Kamila800.png|900px]] | [[Imagem:Kamila800.png|900px]] | ||

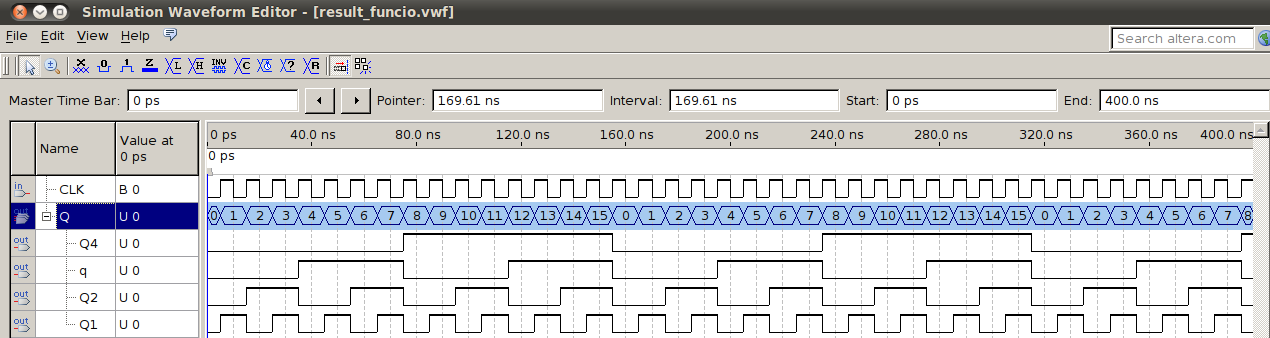

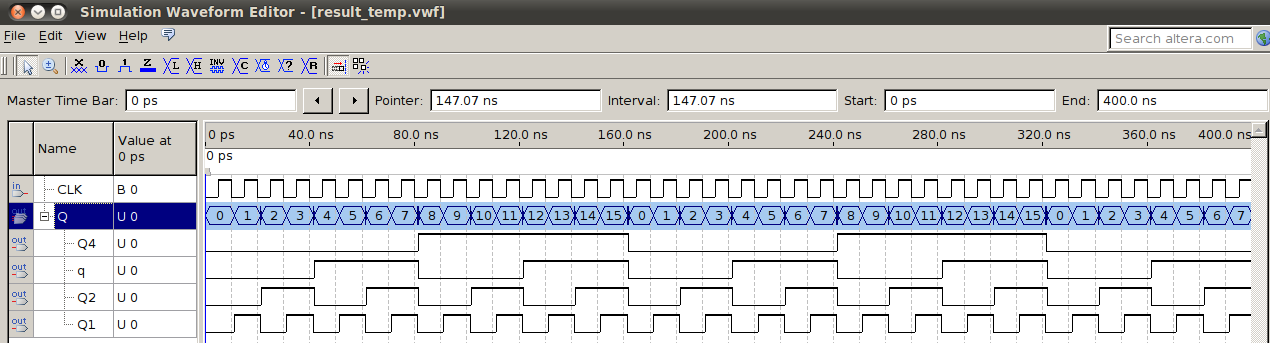

*'''QSim funcional:''' | *'''QSim funcional:''' | ||

[[Imagem:Kamila801.png|800px]] | [[Imagem:Kamila801.png|800px]] | ||

| − | *''' | + | *'''Multisim:''' |

[[Imagem:Kamila47.png|900px]] | [[Imagem:Kamila47.png|900px]] | ||

*'''Protoboard virtual:''' | *'''Protoboard virtual:''' | ||

| Linha 642: | Linha 1 057: | ||

*'''QSim funcional:''' | *'''QSim funcional:''' | ||

[[Imagem:Kamila580.png|800px]] | [[Imagem:Kamila580.png|800px]] | ||

| − | *''' | + | *'''Multisim:''' |

[[Imagem:Kamila50.png|800px]] | [[Imagem:Kamila50.png|800px]] | ||

*'''Protoboard virtual:''' | *'''Protoboard virtual:''' | ||

Edição atual tal como às 01h33min de 9 de maio de 2015

- Publicação: Modernização das aulas de Laboratório de Circuitos Lógicos - 2013.

- Publicação: Modernização das aulas de laboratório de circuitos lógicos: fase implementação - 2014.

- Sugestão de Experimentos.

- Estudo de Circuitos Aritméticos e Implementação em Dispositivos Lógicos Programáveis

- TCC - Estudo de Unidades de Aritmética implementadas com DLP

| Mestrado |

|---|

|

| 2014: Implementação | ||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Semanário do Bolsista 2014: Implementação

Abril

Maio

Junho

| ||||||||||||||||||||||||||||||||||||||||||

| 2013: Pesquisa |

|---|

Diário do Bolsista 2013: Pesquisa

Obs.:O clock é ligado a saída (Q'), apresentei essa solução já que não encontrei uma porta(dff, etc) que houvesse duas saídas Q e Q'

Apostila de Eletrônica Digital Marcos Moecke

|

| Métodos de pesquisa e aplicação |

|---|

|

Contador Assíncrono Crescente:

Contador Assíncrono Decrescente:

Contador assíncrono decrescente Contador Síncrono:

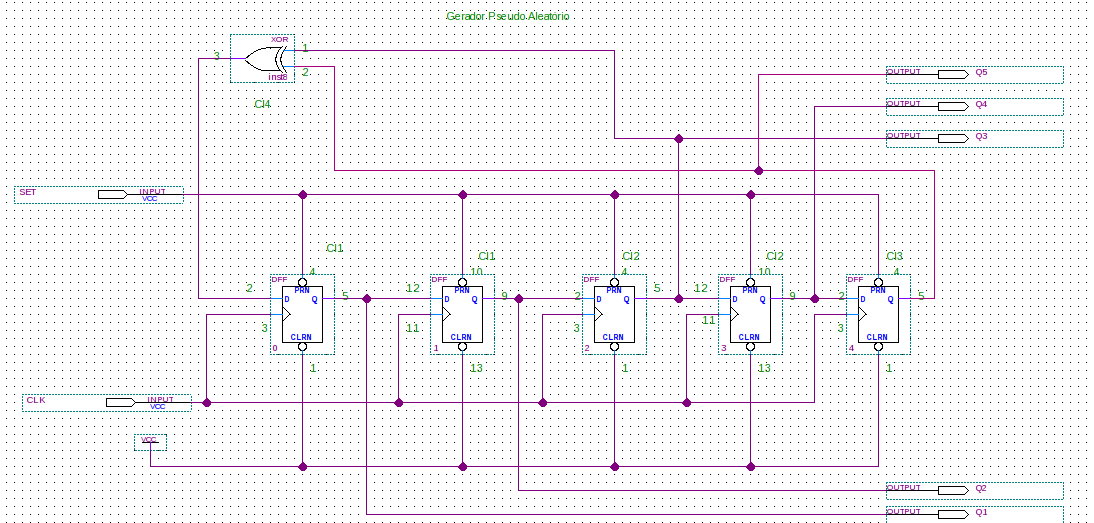

Gerador de Sequência Pseudoaleatória:

XXXX |