Mudanças entre as edições de "Usuário:Kamila.r"

| (268 revisões intermediárias por 5 usuários não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

| − | + | __NOTOC__ | |

| + | #[[Modernização das aulas de Laboratório de Circuitos Lógicos | Publicação: Modernização das aulas de Laboratório de Circuitos Lógicos - 2013]]. | ||

| + | #[[Modernização das aulas de laboratório de circuítos lógicos: fase implementação | Publicação: Modernização das aulas de laboratório de circuitos lógicos: fase implementação - 2014]]. | ||

| + | #[[Projeto MALCIL - Sugestão de experimentos | Sugestão de Experimentos]]. | ||

| + | #[[Estudo de Circuitos Aritméticos e Implementação em Dispositivos Lógicos Programáveis]] | ||

| + | #[[G9:TCC_de_Kamila_Rose_da_Silva | TCC - Estudo de Unidades de Aritmética implementadas com DLP ]] | ||

| − | + | <!-- | |

| + | *Aplicação inviabilizada pela lentidão do Quartus via cloud: | ||

| + | **Aplicação do uso de decodificadores de endereço: Montar circuito que simula o barramento de uma CPU (TOCCI); | ||

| + | **Definição do roteiro sobre Flip-Flops: | ||

| + | #Começar com dlatch (criar: pg 278 PEDRONI); | ||

| + | #dff,tff,tffe,jkff,srff; | ||

| + | #testar set/reset | ||

| + | #Mostrar tabela verdade | ||

| + | --> | ||

| − | + | {{Collapse top | Mestrado}} | |

| + | *http://ppgeel.posgrad.ufsc.br/form/ (Marcos) | ||

| + | *http://www.feec.unicamp.br/ (Rubem) | ||

| + | *http://pgeas.ufsc.br/linhas-de-pesquisa/ (Odilson, Eraldo) | ||

| + | *http://www.lisha.ufsc.br/HomePage (Roberto de Matos e Arliones) | ||

| + | *http://www.cienciasemfronteiras.gov.br/web/csf/mestrado-profissional2 | ||

| + | *http://www.fulbright.org.br/content/view/211/59/ | ||

| − | + | {{Collapse bottom}} | |

| − | |||

| − | |||

| − | |||

| − | ;07mai2013 | + | {{Collapse top | 2014: Implementação}} |

| + | |||

| + | =Semanário do Bolsista 2014: Implementação= | ||

| + | <!-- | ||

| + | --> | ||

| + | ;Horários 1° semestre: | ||

| + | *(4h) SEG 15:30 às 19:30 | ||

| + | *(4h) TER 7:30 às 9:40 - 17:30 às 19:20 | ||

| + | *(4h) QUA 7:30 às 9:40 - 17:30 às 19:20 | ||

| + | *(4h) QUI 9:30 às 11:40 - 17:30 às 19:20 | ||

| + | *(4h) SEX 7:30 às 9:40 - 17:30 às 19:20 | ||

| + | |||

| + | ;Horários 2° semestre: | ||

| + | *(4h) SEG 13:30 às 15:40 - 17:30 às 19:20 | ||

| + | *(2h) TER 7:30 às 9:30 | ||

| + | *(6h) QUA 9:30 às 11:30 - 13:30 às 17:30 | ||

| + | *(2h) QUI 7:30 às 9:30 | ||

| + | *(6h) SEX 7:30 às 9:40 - 15:30 às 19:20 | ||

| + | |||

| + | ==Abril== | ||

| + | ;Semana 01: 01-04 Abril: | ||

| + | *Definição dos passos iniciais do trabalho | ||

| + | *Leitura dos Manuais do Protolab | ||

| + | *Sondagem junto aos professores sobre o tipo de experimentos utilizados em Eletrônica Digital | ||

| + | *Formatação da máquina linux e transferência dos arquivos Kamila e Lacip | ||

| + | *Estudo dos manuais com experimentos | ||

| + | *Download do software QuartusII V13 | ||

| + | *Definição de proposta: fazer um formulário para os professores da área de circuitos lógicos indicando os circuitos disponíveis no Manual 8810 para que eles possam selecionar por grau de importância e/ou necessidade quais os mais utilizados e que deveriam ser propostos também no Quartus | ||

| + | ;Semana 02: 07-11 Abril: | ||

| + | *Solicitado ao suporte a instalação da nova versão do Quartus | ||

| + | *Elaboração do questionário dos professores | ||

| + | *Em conversa com a professora Elen e o professor Eduardo, ambos recomendaram que os roteiros a serem desenvolvidos deveriam partir dos circuitos mais simples, com algumas portas lógicas, para melhor entendimento do funcionamento delas e uma interação inicial mais simples com o software | ||

| + | ;Semana 03: 14-17 Abril: | ||

| + | *Término do formulário dos professores | ||

| + | *Estudo das biografias do TOKHEIM | ||

| + | *Software Quartus V13 foi instalado | ||

| + | *Testes com a nova versão | ||

| + | *Desenvolvimento de uma relação de experimentos para propor aos professores da área de CIL | ||

| + | ;Semana 04: 22-30 Abril: | ||

| + | *[https://docs.google.com/forms/d/1lAhQjeiGx9_5bnVuJKbJxzH8BDb9Ejtj1ITuqTJWb28/viewform Fomulário Professores fase: Implementação] | ||

| + | *Seleção e estudos dos experimentos: | ||

| + | |||

| + | # Portas AND > Módulo 8810 | ||

| + | # Portas OR, NOT e NOR > Módulo 8810 | ||

| + | # Porta NAND e teorema de De Morgan > Módulo 8810 | ||

| + | # Programar o FPGA > Módulo 8810 | ||

| + | # Sistema de numeração binário > | ||

| + | # Decodificador de 3 para 8, 1 para 2, 2 para 3 (binário para one-hot) > | ||

| + | # Multiplexadores/Demultiplexadores > Módulo 8810 | ||

| + | # Tipos de Flip-Flops e Latch > TOKEIM | ||

| + | # Contador UP/DOWN > TOKEIM | ||

| + | # Contadores comerciais > TOKEIM | ||

| + | # Registrador de deslocamento > TOKEIM | ||

| + | # Comparador de magnitude > Módulo 8810 | ||

| + | # Somador/Subtrator/Complemento de 2; (4 e 8 bits) > Módulo 8810 | ||

| + | #Projeto de circuito para detectar Overflow > Módulo 8810 | ||

| + | # Multiplicador > | ||

| + | #(...) | ||

| + | |||

| + | ==Maio== | ||

| + | ;Semana 05: 05-09 Maio: | ||

| + | *Definir os objetivos de cada experimento mencionado na lista: | ||

| + | |||

| + | ; Porta AND: | ||

| + | * Utilizar o '''diagrama esquemático''' do Quartus II para inserir um circuito; | ||

| + | * Gerar formas de onda para entrada de simulação usando o QSIM; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Compreender o funcionamento da porta AND; | ||

| + | * Entender a tabela verdade de circuitos lógicos; | ||

| + | * Obter as imagens e dados para a confecção de relatório técnico; | ||

| + | |||

| + | ; Portas OR, NOT e NOR: | ||

| + | * Utilizar o '''diagrama esquemático''' do Quartus II para inserir um circuito; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - '''diagrama temporal''' (uso de cursores para medições); | ||

| + | * Compreender o funcionamento das porta OR, NOT e NOR; | ||

| + | * Entender a tabela verdade de circuitos lógicos; | ||

| + | |||

| + | ; Porta NAND e teorema de De Morgan: | ||

| + | * Utilizar o '''diagrama esquemático''' do Quartus II para inserir um circuito; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Compreender o funcionamento da porta NAND; | ||

| + | * Utilizar portas NAND para a implementação de portas OR, NOR, NOT e AND; | ||

| + | * Entender a equivalência de circuitos; | ||

| + | |||

| + | ; Programar o FPGA: | ||

| + | * Utilizar o '''diagrama esquemático''' do Quartus II para inserir um circuito; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Compreender o funcionamento das portas XOR e XNOR; | ||

| + | * Definir a pinagem de saída; | ||

| + | * Programar o FPGA para implementar um comparador de palavras (ou gerador de paridade); DE2-115 | ||

| + | * Entender o preenchimento da tabela verdade seguindo o resultado apresentado pelo circuito; | ||

| + | |||

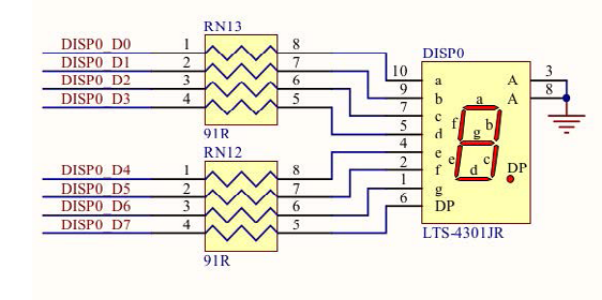

| + | ; Sistema de numeração binário: | ||

| + | * Compreender o funcionamento do display de sete segmentos; | ||

| + | * Compreender o funcionamento do codificador binário para sete segmentos; | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Fazer a simulação funcional do circuito com o QSIM; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DE2-115 | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Decodificador de 3 para 8, 1 para 2, 2 para 4 (binário para one-hot): | ||

| + | * Compreender o funcionamento do decodificador 3 para 8; [http://www.ti.com/lit/ds/symlink/sn54als138a.pdf 74X138] | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Fazer a simulação funcional do circuito com o QSIM; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DE0-NANO | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Multiplexadores/Demultiplexadores: | ||

| + | * Multiplexador/Seletor de 8 para 1; [http://www.ti.com/lit/ds/symlink/sn54als151.pdf 74X151] | ||

| + | * 2x Multiplexador/Seletor de 4 para 1; [http://www.ti.com/lit/ds/symlink/sn54als153.pdf 74X153] | ||

| + | * 4x Multiplexador/Seletor de 2 para 1; [http://www.ti.com/lit/ds/symlink/sn54als158.pdf 74X157/158] | ||

| + | * XXXXXXXXXXXX | ||

| + | |||

| + | ; Tipos de Flip-Flops e Latch: | ||

| + | * Compreender o funcionamento de Flip-Flops D, RS, JK e Latch RS e D; | ||

| + | * Compreender e observar o funcionando do CLOCK nos circutos; | ||

| + | * Fazer a simulação funcional dos circuito com o QSIM; | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DEO-NANO | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Contador UP/DOWN: | ||

| + | * Inserir diagrama esquemático de um circuito lógico com o Quartus II (circuito discreto); | ||

| + | * Fazer a simulação funcional de um circuito com o QSIM; | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Fazer a simulação temporal do circuito com o QSIM; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DE0-NANO | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Contadores comerciais: (74XX) | ||

| + | * Inserir diagrama esquemático de um circuito lógico com o Quartus II; | ||

| + | * Fazer a simulação funcional de um circuito com o QSIM; | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Fazer a simulação temporal do circuito com o QSIM; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DE2-115 | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Registrador de deslocamento: | ||

| + | * Inserir diagrama esquemático de um circuito lógico com o Quartus II; | ||

| + | * Fazer a simulação funcional de um circuito com o QSIM; | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Fazer a simulação temporal de um circuito com o QSIM; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DEO-NANO | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Comparador de magnitude: | ||

| + | * Utilizar o diagrama esquemático do Quartus II para inserir um circuito; | ||

| + | * Gerar formas de onda para entrada de simulação usando o QSIM; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Compreender o funcionamento do comparador de magnitude na forma de CI; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DE0-NANO | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Somador/Subtrator/Complemento de 2; (4 e 8 bits): | ||

| + | * Compreender o funcionamento dos circuitos aritméticos somador, subtrator e complemento de 2; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Analisar os resultados obtidos para entender e associar os tipos de operações realizados; | ||

| + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; DE0-NANO | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Projeto de circuito para detectar Erros; | ||

| + | * Projetar circuito para detectar Erro em operações com números binários; | ||

| + | * Detectar a ocorrência de Erros; | ||

| + | * Entender funcionamento do Mapa de Karnaugh; | ||

| + | |||

| + | ; Multiplicador discreto: | ||

| + | * Compreender o funcionamento Multiplicador discreto; | ||

| + | * Construção de um projeto hierárquico; | ||

| + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ; Multiplicador: | ||

| + | * Compreender o funcionamento multiplicador binário de 4 bits por 4 bits; [http://www.ti.com/lit/ds/symlink/sn74284.pdf 74X284/285] | ||

| + | * Gerar formas de onda para entrada de simulação; | ||

| + | * Fazer a simulação temporal do circuito com o QSIM; | ||

| + | * Verificar os resultados obtidos; | ||

| + | |||

| + | ;Semana 06: 12-16 Maio: | ||

| + | * Término das escolhas dos circuitos e das definições dos objetivos dos mesmos; | ||

| + | * Edição do formulário dos Professores: fase implementação; | ||

| + | * Criação de um link na wiki para a descrição de todos os experimentos selecionados, incluindo objetivos e CIs que serão utilizados; | ||

| + | * Incluir o link no formulário; | ||

| + | * [[Projeto MALCIL - Sugestão de experimentos]] | ||

| + | |||

| + | ;Semana 07: 19-23 Maio: | ||

| + | |||

| + | *Início das implementações e documentação dos roteiros. | ||

| + | |||

| + | *'''Links Importantes:''' [ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE2-115/DE2_115.qsf Pinagem DE2-115] [ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE0-Nano/DE0_Nano.qsf Pinagem DE0-NANO] | ||

| + | |||

| + | ;Semana 08: 26-30 Maio: | ||

| + | |||

| + | *Implementações dos experimentos: 1/2/3/... | ||

| + | *Roteiro 1 -OK (Falta: Inserir Tabela Verdade) | ||

| + | |||

| + | ==Junho== | ||

| + | ;Semana 09: 02-06 Junho: | ||

| + | *Editar o experimento do roteiro 1; | ||

| + | *Implementar o .vwf e disponibilizar o doc no roteiro pelo Dropbox; | ||

| + | *Continuar implementando os experimentos propostos; | ||

| + | |||

| + | ;Semana 10: 09-13 Junho: | ||

| + | *Construção do Roteiro 2; | ||

| + | *Implementação do experimento 3/4; | ||

| + | <code>Dúvidas: | ||

| + | - Sobre o exp4, foi definido um circuito com apenas portas XNOR; | ||

| + | - Definir circuito para exp3 | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ;Semana 11: 16-18 Junho: | ||

| + | *Fazer resumo estendido sobre a pesquisa de 2013 durante a semana; | ||

| + | *Após término do resumo, dar início a confecção do banner; | ||

| + | |||

| + | |||

| + | ;Semana 12: 24-27 Junho: | ||

| + | *Implementação do Exp3 e estudos sobre o tema; | ||

| + | *Formulação roteiro 3; | ||

| + | *Término artigo SEPEI; | ||

| + | |||

| + | ==Julho== | ||

| + | ;Semana 13: 30-04 Julho: | ||

| + | *Continuando implementação dos experimentos e roteiros; | ||

| + | *Revisão do roteiro do contador para ajudar a Prof Elen em aula de laboratório com alunos do Integrado dia 07/07; | ||

| + | |||

| + | ;Semana 14: 07-11 Julho: | ||

| + | |||

| + | *Auxilar aula de laboratório CIL (Roteiro contador); | ||

| + | *Implementação experimento 4; | ||

| + | *Finalizar roteiros 3; | ||

| + | |||

| + | ;Semana 15 e 16: 14-25 Julho: | ||

| + | *Experimentos 4,5,9,10 e 11; | ||

| + | |||

| + | ==Agosto== | ||

| + | ;Semana 16 e 17: 30 Julho - 08 Agosto: | ||

| + | *Roteiros 4,5,9,10 e 11; | ||

| + | Obs:Quartus com problema na programação do kit | ||

| + | *Experimento 4: | ||

| + | <code> | ||

| + | #============================================================ | ||

| + | # SW | ||

| + | #============================================================ | ||

| + | set_location_assignment PIN_AB28 -to SW[0] | ||

| + | set_location_assignment PIN_AC28 -to SW[1] | ||

| + | set_location_assignment PIN_AC27 -to SW[2] | ||

| + | set_location_assignment PIN_AD27 -to SW[3] | ||

| + | set_location_assignment PIN_AB27 -to SW[4] | ||

| + | set_location_assignment PIN_AC26 -to SW[5] | ||

| + | set_location_assignment PIN_AD26 -to SW[6] | ||

| + | set_location_assignment PIN_AB26 -to SW[7] | ||

| + | #============================================================ | ||

| + | # LED | ||

| + | #============================================================ | ||

| + | set_location_assignment PIN_E21 -to LEDG[0] | ||

| + | set_location_assignment PIN_E22 -to LEDG[1] | ||

| + | set_location_assignment PIN_E25 -to LEDG[2] | ||

| + | set_location_assignment PIN_E24 -to LEDG[3] | ||

| + | set_location_assignment PIN_H21 -to LEDG[4] | ||

| + | </syntaxhighlight> | ||

| + | *DE0-NANO: family='''Cyclone IV''' device='''EP4CE22F17C6N''' | ||

| + | *DE2-115: family='''Cyclone IV''' device='''EP4CE115F29C7N''' | ||

| + | ;Semana 18: 11-15 Agosto: | ||

| + | *Elaboração do banner para o SEPEI; | ||

| + | ;IMPORTANTE: | ||

| + | Erro encontrado no arquivo de pinagem da DE2-115: Os pinos correspondentes aos leds vermelhos(LED1 e LED2) estão invertidos | ||

| + | #LED1- PIN_F19 | ||

| + | #LED2- PIN_E19 | ||

| + | *Print: ordem dos pinos invertida | ||

| + | [[Imagem:erroArq.png]] | ||

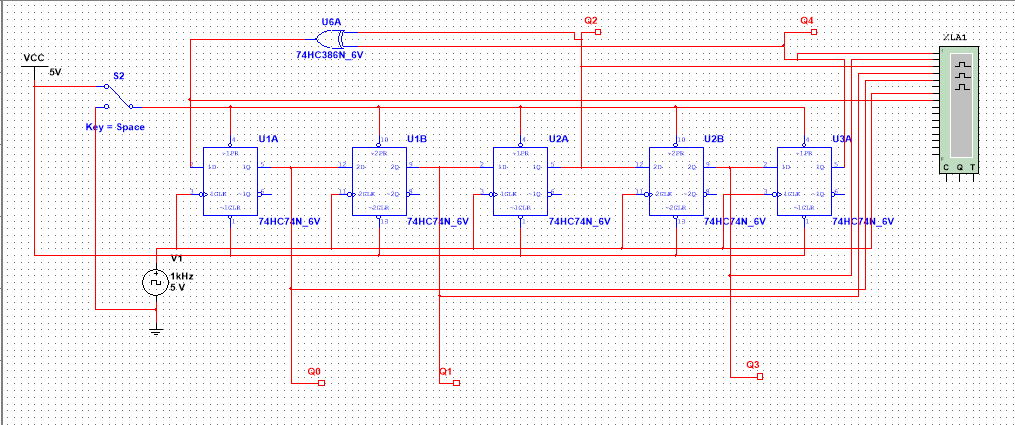

| + | *Fazer um experimento de contador assíncrono crescente para colocar as imagens no banner(sem pinagem e sem display 7-seg). Para uma simples explicação. | ||

| + | |||

| + | ;Semana 19: 18-22 Agosto: | ||

| + | *Roteiro 5; | ||

| + | *Finalização do banner SEPEI; | ||

| + | *Estudar PEDRONI e Módulo 8810 para definir quais implementações que ainda não foram feitas(Exp6, 7, 8, 12, 13, 14, 15 e 16); | ||

| + | |||

| + | ;Semana 20: 25-29 Agosto: | ||

| + | *Experimento 12; | ||

| + | *Estudos sobre exp 15 e 16; | ||

| + | *Novo roteiro do cont assíncrono crescente atualizado para Quartus v.13 (Apresentação para os Profs); | ||

| + | [[Contador Assíncrono Crescente - Roteiro para implementação e simulação com QUARTUS II(v.13), QSIM e kit DE2-115]] | ||

| + | |||

| + | ==Setembro== | ||

| + | ;Semana 21: 01-05 Setembro: | ||

| + | *Semana SEPEI; | ||

| + | ;Semana 22: 08-12 Setembro: | ||

| + | *Tutorial sobre Quartus para profs da área; | ||

| + | *Editar Contador assíncrono crescente e o Experimento1 com os primeiros passos para inclusão do diagrama esquemático no QuartusI; | ||

| + | *Nomear cada experimento para incluir na listagem do banner pra MCC; | ||

| + | *Elaboração do banner pra MCC; | ||

| + | Rascunho da listagem dos nomes dos experimentos: | ||

| + | # Introdução à ferramenta de ensino Quartus II; | ||

| + | # Simulação de portas do tipo OR, NOT e NOR; | ||

| + | # Aplicação do Teorema de De Morgan; | ||

| + | # Programação no FPGA; | ||

| + | # Introdução à sistema de numeração binário; | ||

| + | # Implementação de Decodificadores; | ||

| + | # Implementação de Multiplexadores; | ||

| + | # Introdução à tipos de Flip-Flops; | ||

| + | # Contadores assíncronos crescente e decrescente (Discretos); | ||

| + | # Contador assíncrono crescente (Comercial); | ||

| + | # Registador de deslocamento; | ||

| + | # Comparador de magnitude; | ||

| + | # Aritmética binária(Somador/Subtrator/Complemento de 2); | ||

| + | # Projeto de circuito para detectar Erros e aplicação do Mapa de Karnaugh; | ||

| + | # Multiplicador (discreto); | ||

| + | # Multiplicador; | ||

| + | |||

| + | ;Semana 22: 15-19 Setembro: | ||

| + | *Implementação dos experimentos que envolvem circuitos aritméticos no Quartus. | ||

| + | *Elaboração do mini curso Quartus para a MCC; | ||

| + | |||

| + | ;Semana 23: 22-26 Setembro: | ||

| + | *Implementação do experimento e roteiro do Comparador de magnitude; | ||

| + | *Roteiro sobre circuitos aritméticos; | ||

| + | |||

| + | ==Outubro== | ||

| + | ;Semana 24: 06-10 Outubro: | ||

| + | *'''Programação para o mês de Outubro: Terminar todos os experimentos e roteiros.''' | ||

| + | ;Semana 25: 13-17 Outubro: | ||

| + | *MCC; | ||

| + | ;Semana 26 e 27: 20 - 31 Outubro: | ||

| + | *Implementação do roteiro Multiplicador (Comercial); | ||

| + | *Implementação do experimento e roteiro Multiplicador (Discreto); | ||

| + | *Implementação do experimento Multiplexadores; | ||

| + | |||

| + | Exemplo tabela verdade: | ||

| + | *Preencha a tabela verdade: | ||

| + | |||

| + | {| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

| + | ! colspan="6" style="background: #efefef;" | Entradas | ||

| + | ! colspan="1" style="background: #ffdead;" | Saídas | ||

| + | |- | ||

| + | !width="30"| A | ||

| + | !width="30"| B | ||

| + | !width="30"| C | ||

| + | !width="30"| D | ||

| + | !width="30"| Sel0 | ||

| + | !width="30"| Sel1 | ||

| + | !width="50"| y | ||

| + | |- | ||

| + | | || || || || 0 || 0 || | | ||

| + | |- | ||

| + | | || || || || 0 || 1 || | | ||

| + | |- | ||

| + | | || || || || 1 || 0 || | | ||

| + | |- | ||

| + | | || || || || 1 || 1 || | | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | |||

| + | ==Novembro== | ||

| + | |||

| + | ;Semana 28: 03 - 07 Novembro: | ||

| + | *Estudar o experimento do Decod de endereços. Obs.: Não esquecer do exemplo de aplicação no roteiro; | ||

| + | *Iniciando a documentação do relatório técnico final; | ||

| + | |||

| + | ;Semana 29: 10 - 14 Novembro: | ||

| + | *Término do roteiro de Circuitos aritméticos; | ||

| + | *Desenvolvimento do relatório técnico. | ||

| + | |||

| + | ;Semana 30: 17 - 21 Novembro: | ||

| + | *Implementação e roteiro Decod endereços; | ||

| + | *Estudar mapa de Karnaugh; | ||

| + | *Obs.: Faltando terminar os Resultados do relatório técnico; | ||

| + | |||

| + | ;Semana 31: 24 - 28 Novembro: | ||

| + | *Término do relatório final; | ||

| + | *Definição do roteiro sobre Flip-Flops: | ||

| + | #Começar com dlatch (criar: pg 278 PEDRONI); | ||

| + | #dff,tff,tffe,jkff,srff; | ||

| + | #testar set/reset | ||

| + | #Mostrar tabela verdade | ||

| + | #Simulação temporal; | ||

| + | *Implementar 3 mini-roteiros: | ||

| + | # Como incluir .bdf em um projeto e uso do top-level (Como trocar a família do FPGA); - OK | ||

| + | # Simulação funcional (como criar formas de onda); - OK | ||

| + | # Simulação temporal (como criar formas de onda); - OK | ||

| + | |||

| + | *Reimplementar decodificador 7-seg discreto a partir do Mapa de Karnaugh; - OK | ||

| + | *Implementar Somador comercial no lugar do projeto de detecção de erros (fazer simulação temporal e propor a comparação com discreto -- qual é mais rápido?); - OK | ||

| + | *Aplicação do uso de decodificadores de endereço: Montar circuito que simula o barramento de uma CPU (TOCCI); | ||

| + | *"Assinar" projetos; | ||

| + | |||

| + | {{Collapse bottom}} | ||

| + | |||

| + | {{Collapse top | 2013: Pesquisa}} | ||

| + | |||

| + | =Diário do Bolsista 2013: Pesquisa= | ||

| + | ;07mai2013: | ||

*Discussão sobre as etapas do projeto. Planejamento. Esclarecimento de dúvidas. | *Discussão sobre as etapas do projeto. Planejamento. Esclarecimento de dúvidas. | ||

* Assistir as aulas de CIL29003 (para rever a disciplina sob outro enfoque). | * Assistir as aulas de CIL29003 (para rever a disciplina sob outro enfoque). | ||

| Linha 17: | Linha 424: | ||

*Ler PEDRONI, Volnei A. Eletrônica Digital Moderna e VHDL: Princípios Digitais, Eletrônica Digital, Projeto Digital, Microeletrônica e VHDL. 1 ed. [S.l.]:Elsevier, 2010. 648 p. ISBN 978-8535234657. (Cap 18) | *Ler PEDRONI, Volnei A. Eletrônica Digital Moderna e VHDL: Princípios Digitais, Eletrônica Digital, Projeto Digital, Microeletrônica e VHDL. 1 ed. [S.l.]:Elsevier, 2010. 648 p. ISBN 978-8535234657. (Cap 18) | ||

| − | ;08maio2013 | + | ;08maio2013: |

*Iniciando os estudos sobre Dispositivos Lógicos Programáveis (PEDRONI, Volnei A.) cáp 18. | *Iniciando os estudos sobre Dispositivos Lógicos Programáveis (PEDRONI, Volnei A.) cáp 18. | ||

*Ler página [[CIL-EngTel (página)]]. | *Ler página [[CIL-EngTel (página)]]. | ||

| Linha 30: | Linha 437: | ||

*Início da pesquisa sobre as melhores faculdades de tecnologia do mundo (com foco em eletrônica), projetos e afins. | *Início da pesquisa sobre as melhores faculdades de tecnologia do mundo (com foco em eletrônica), projetos e afins. | ||

*Vídeos sobre programação, teste e aplicação produtos ALTERA (YouTube). | *Vídeos sobre programação, teste e aplicação produtos ALTERA (YouTube). | ||

| − | + | ||

;13maio2013; | ;13maio2013; | ||

*Leitura de tópicos importantes do capítulo 13 da seguinte bibliografia: TOCCI, Ronald J.; WIDMER, Neal S.; MOSS, Gregory L. Sistemas digitais: Princípios e Aplicações. 10 ed. [S.l.]:Pearson Prentic Hall, 2007. | *Leitura de tópicos importantes do capítulo 13 da seguinte bibliografia: TOCCI, Ronald J.; WIDMER, Neal S.; MOSS, Gregory L. Sistemas digitais: Princípios e Aplicações. 10 ed. [S.l.]:Pearson Prentic Hall, 2007. | ||

| − | * | + | *Obs.: Resumo no final do capítulo é claro e objetivo, para futuras dúvidas sobre a arquitetura dos DLPs, consultá-lo. |

;14maio2013; | ;14maio2013; | ||

| Linha 52: | Linha 459: | ||

{{com| Note que neste caso (Gerador de sequencia pseudoaleatória) temos a montagem de um projeto, no qual o aluno precisa decidir quais devem ser as conexões, ligações e componentes a serem usados. O tempo de projeto e implementação será maior que no caso de uma simples implementação ([[Registrador de Deslocamento - BDF e QSIM]]), no qual todas as ligações já estão previamente definidas. Tente dimensionar as dificuldades e tempo nos dois casos. 1) Implementação; 2) Projeto e implementação. --[[Usuário:Moecke|Marcos Moecke]] 10h51min de 17 de maio de 2013 (BRT)}} | {{com| Note que neste caso (Gerador de sequencia pseudoaleatória) temos a montagem de um projeto, no qual o aluno precisa decidir quais devem ser as conexões, ligações e componentes a serem usados. O tempo de projeto e implementação será maior que no caso de uma simples implementação ([[Registrador de Deslocamento - BDF e QSIM]]), no qual todas as ligações já estão previamente definidas. Tente dimensionar as dificuldades e tempo nos dois casos. 1) Implementação; 2) Projeto e implementação. --[[Usuário:Moecke|Marcos Moecke]] 10h51min de 17 de maio de 2013 (BRT)}} | ||

| − | |||

;20maio2013; | ;20maio2013; | ||

*A implementação do exercício feito em laboratório RegDeslocamento foi simples de ser feita, com exceção do erro que apresentou o Qsim | *A implementação do exercício feito em laboratório RegDeslocamento foi simples de ser feita, com exceção do erro que apresentou o Qsim | ||

| Linha 75: | Linha 481: | ||

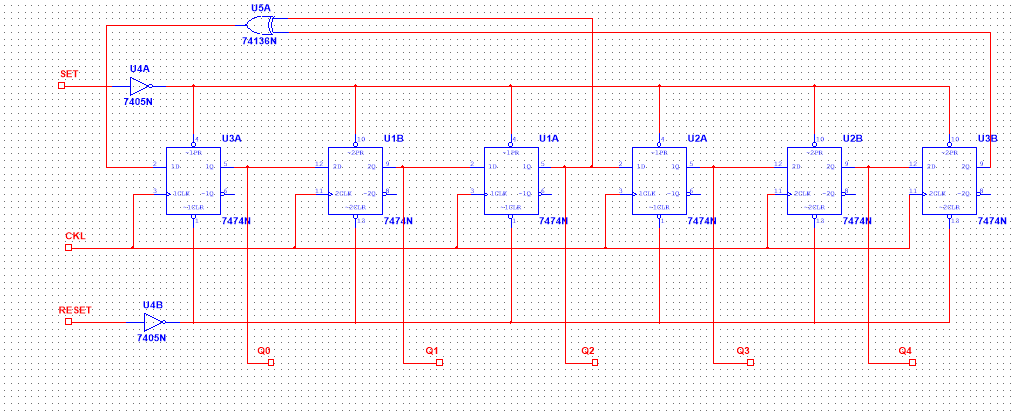

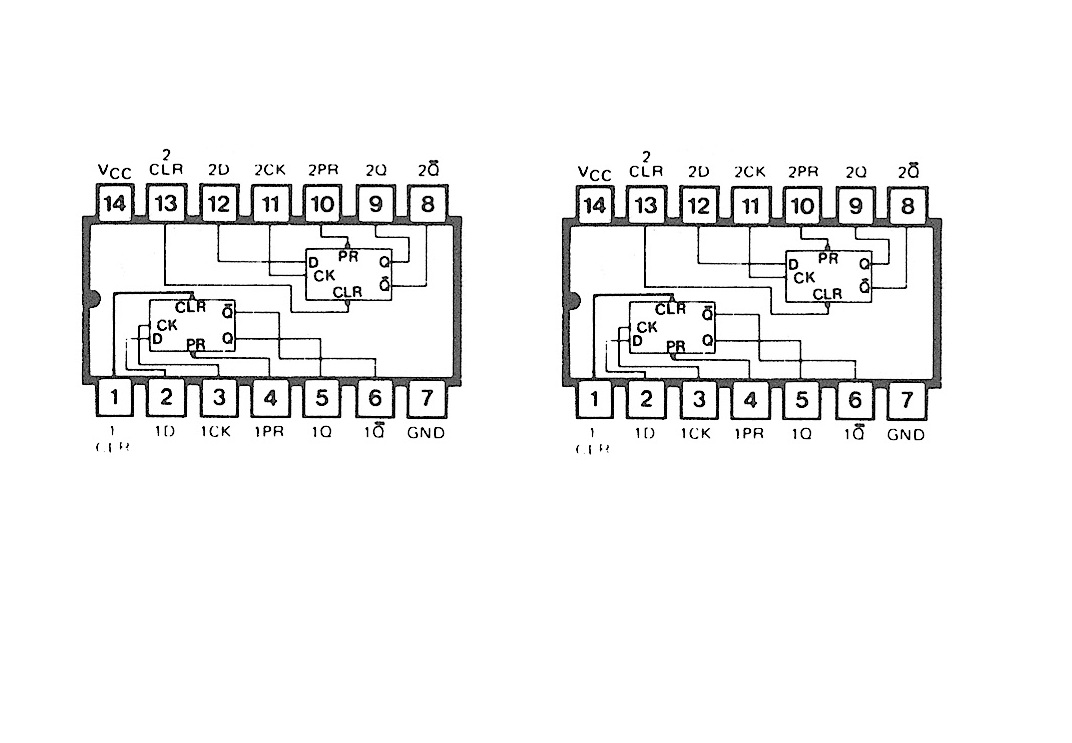

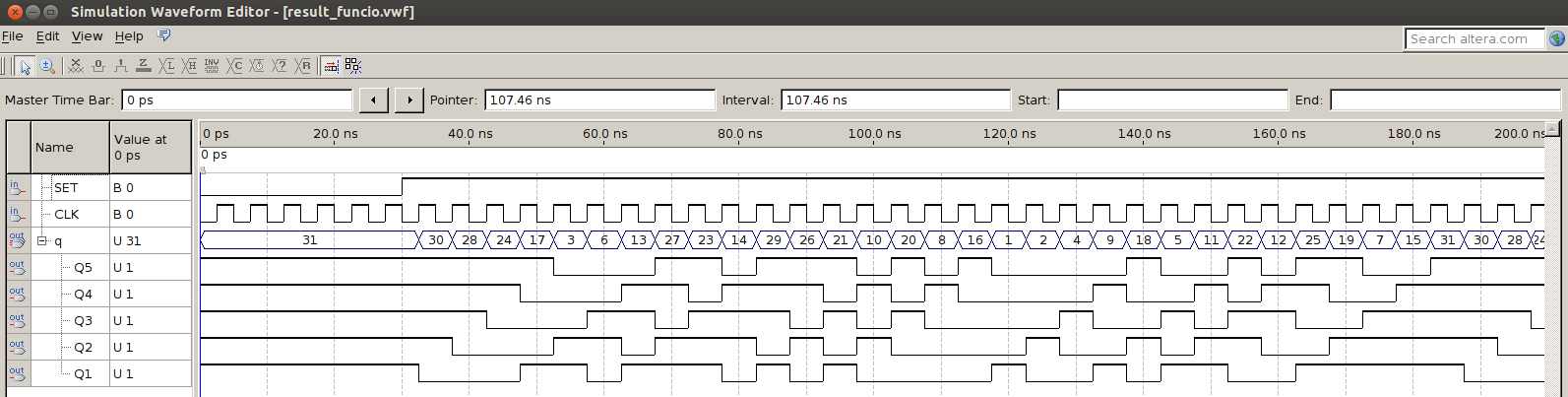

*Implementação do contador assíncrono crescente com CIs (7474), no QuartusII | *Implementação do contador assíncrono crescente com CIs (7474), no QuartusII | ||

*'''Obs.:''' Na simulação do Qsim, as saídas Q2 e Q4 saem zeradas. | *'''Obs.:''' Na simulação do Qsim, as saídas Q2 e Q4 saem zeradas. | ||

| − | |||

| − | |||

;27maio2013; | ;27maio2013; | ||

| Linha 92: | Linha 496: | ||

*Erro com a máquina virtual(não foi instalada no usuário "Kamila") | *Erro com a máquina virtual(não foi instalada no usuário "Kamila") | ||

*Obs.:As implementações foram salvas em BrOffice. Todas estão na máquina MATLAB. | *Obs.:As implementações foram salvas em BrOffice. Todas estão na máquina MATLAB. | ||

| − | |||

| − | |||

;03junho2013; | ;03junho2013; | ||

*Instalação do Windows XP na máquina virtual do usuário "Kamila". | *Instalação do Windows XP na máquina virtual do usuário "Kamila". | ||

*Erro na implementação do contador síncrono | *Erro na implementação do contador síncrono | ||

| − | * | + | *Obs.: Não é possível conectar um fio a outro. |

;04junho2013; | ;04junho2013; | ||

| Linha 119: | Linha 521: | ||

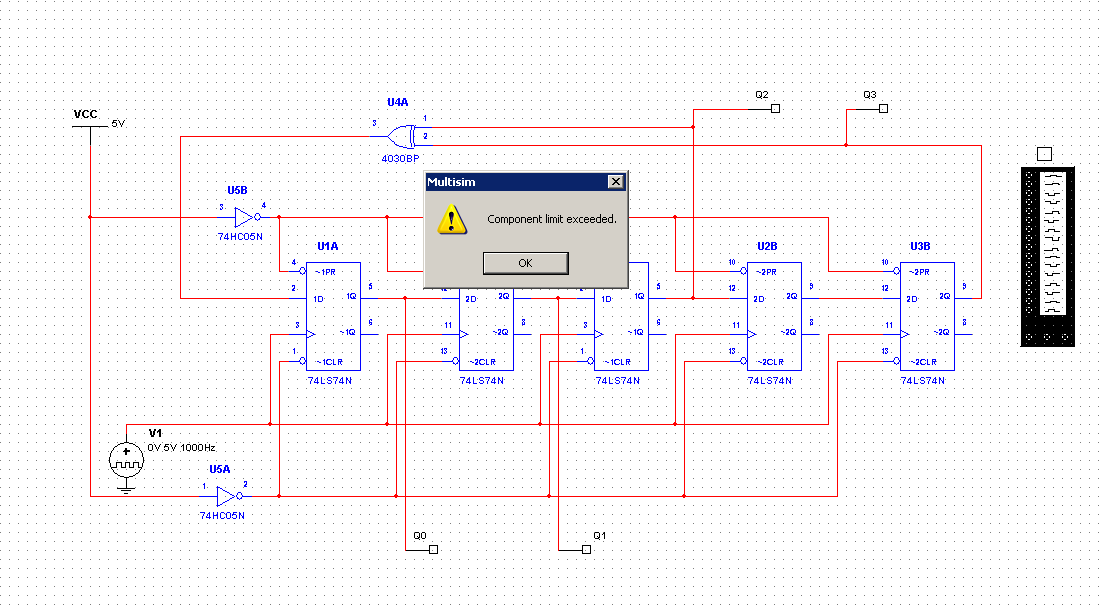

*O gerador de função apresentou um erro de "limitação de componentes": | *O gerador de função apresentou um erro de "limitação de componentes": | ||

[[Imagem:kamila18.png|600px]] | [[Imagem:kamila18.png|600px]] | ||

| − | |||

| − | |||

;12junho2013; | ;12junho2013; | ||

| Linha 132: | Linha 532: | ||

*Reimplementação dos contadores no MultiSim versão estudante. | *Reimplementação dos contadores no MultiSim versão estudante. | ||

| − | |||

;17junho2013; | ;17junho2013; | ||

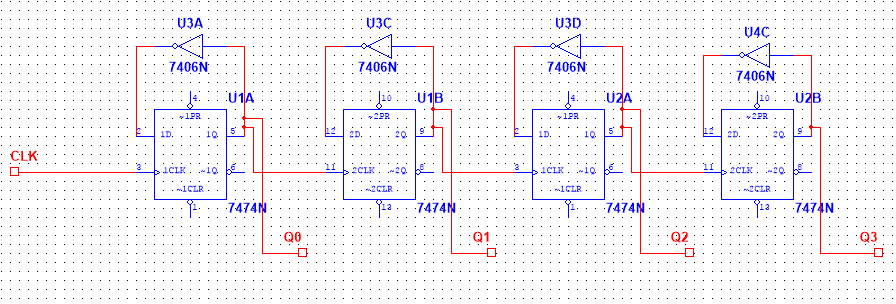

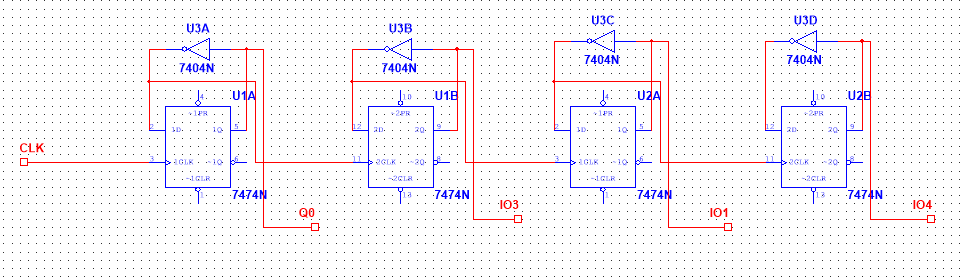

*Implementação: | *Implementação: | ||

| Linha 155: | Linha 554: | ||

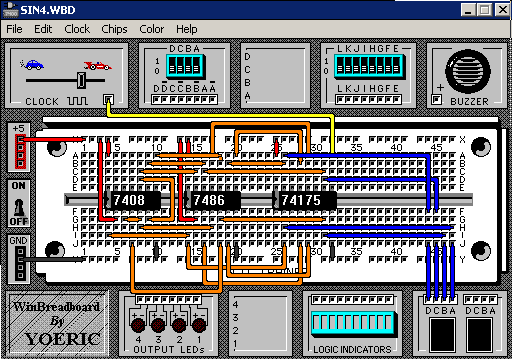

*Contador assíncrono decrescente no protoboard virtual: | *Contador assíncrono decrescente no protoboard virtual: | ||

[[Imagem:Kamila24.png|400px]] | [[Imagem:Kamila24.png|400px]] | ||

| − | * | + | *Obs.:Não estou conseguindo analisar, pois está apresentando um erro que ainda não encontrei. Esse ficou uma gracinha hein?! |

*Gerador de sequência pseudoaleatória em TTL: | *Gerador de sequência pseudoaleatória em TTL: | ||

| Linha 163: | Linha 562: | ||

[[Imagem:kamila23.png|400px]] | [[Imagem:kamila23.png|400px]] | ||

| − | |||

;24junho2013; | ;24junho2013; | ||

*Término das implementações na nova versão do MultiSim, faltantando apenas o contador síncrono. | *Término das implementações na nova versão do MultiSim, faltantando apenas o contador síncrono. | ||

| Linha 180: | Linha 578: | ||

*Aula de CIL. | *Aula de CIL. | ||

| − | |||

;01jul2013; | ;01jul2013; | ||

*Término da implementação do gerador de sequência pseudoaleatória, que precisava da chave para funcionar corretamente. | *Término da implementação do gerador de sequência pseudoaleatória, que precisava da chave para funcionar corretamente. | ||

| Linha 197: | Linha 594: | ||

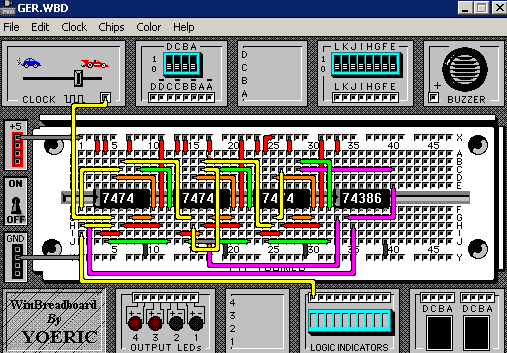

*Continuação das implementações no protoboard virtual, com os novos CIs escolhidos. | *Continuação das implementações no protoboard virtual, com os novos CIs escolhidos. | ||

| − | |||

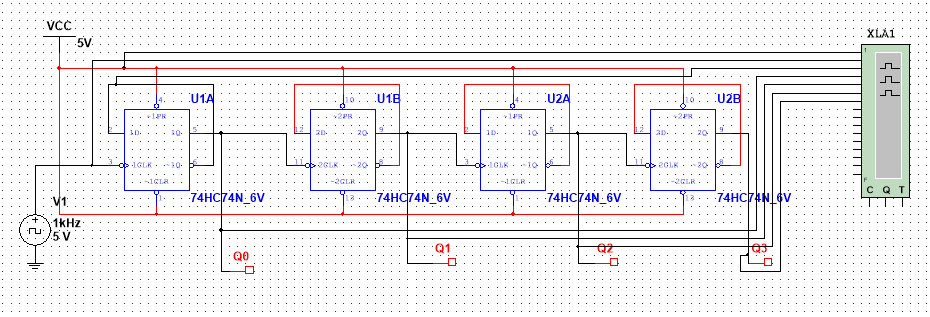

;09julho2013; | ;09julho2013; | ||

*Aula CIL | *Aula CIL | ||

| Linha 218: | Linha 614: | ||

[[Imagem:kamila509.png|800px]] | [[Imagem:kamila509.png|800px]] | ||

| − | |||

;15julho2013; | ;15julho2013; | ||

*Continuação das implementações do contador síncrono e gerador de sequência no protoboard virtual. | *Continuação das implementações do contador síncrono e gerador de sequência no protoboard virtual. | ||

| Linha 226: | Linha 621: | ||

*Correção da versão do contador síncrono no Quartus do 7474, imagens já postadas. | *Correção da versão do contador síncrono no Quartus do 7474, imagens já postadas. | ||

*'''Obs.: Versão do MultiSim Estudante expirou.''' | *'''Obs.: Versão do MultiSim Estudante expirou.''' | ||

| + | |||

;16Julho2013; | ;16Julho2013; | ||

*Aula CIL. | *Aula CIL. | ||

*Reunião. | *Reunião. | ||

| + | |||

;17Julho2013; | ;17Julho2013; | ||

*Com a pinagem feita nos CIs a finalização do contador síncrono foi facilitada no protoboard virtual. Já postado no link dos contadores. | *Com a pinagem feita nos CIs a finalização do contador síncrono foi facilitada no protoboard virtual. Já postado no link dos contadores. | ||

*Concluindo o gerador de sequência com a pinagem. | *Concluindo o gerador de sequência com a pinagem. | ||

| + | |||

;18Julho2013; | ;18Julho2013; | ||

*Conferido a pinagem com a montagem do gerador de sequência pseudo-aleatória. Montagem correta, porém não funciona como o esperado. | *Conferido a pinagem com a montagem do gerador de sequência pseudo-aleatória. Montagem correta, porém não funciona como o esperado. | ||

*Correção de algumas modificações do gerador de sequência pseudo-aleatória no Quartus e simulação no Qsim. Já postadas no link dos contadores. | *Correção de algumas modificações do gerador de sequência pseudo-aleatória no Quartus e simulação no Qsim. Já postadas no link dos contadores. | ||

*Aula de CIL. | *Aula de CIL. | ||

| + | |||

;19Julho2013; | ;19Julho2013; | ||

*Implementação do contador síncrono no protoboard real. | *Implementação do contador síncrono no protoboard real. | ||

| Linha 242: | Linha 641: | ||

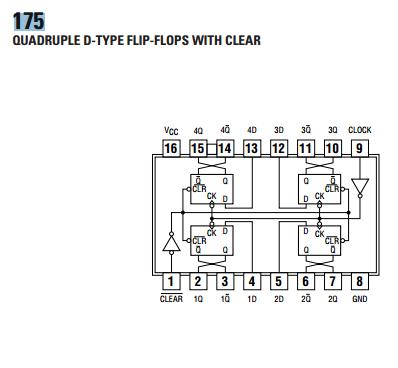

*Componentes necessários: Fios, CI 74LS175, CI 74386(não disponível), CI 74LS08, alicates e plataforma com protoboard. | *Componentes necessários: Fios, CI 74LS175, CI 74386(não disponível), CI 74LS08, alicates e plataforma com protoboard. | ||

| − | |||

;22julho2013; | ;22julho2013; | ||

*Reimplementando o contador síncrono no protoboard virtual com o CI 7486, pois não há disponibilidade do CI 74386. | *Reimplementando o contador síncrono no protoboard virtual com o CI 7486, pois não há disponibilidade do CI 74386. | ||

| Linha 262: | Linha 660: | ||

*Refazendo a implementação do gerador de sequência. O que já está com as ligações feitas e conferidas não funcionam corretamente. Obs.: Já foram trocados os CIs para testar se eles estavam queimados e nada mudou. | *Refazendo a implementação do gerador de sequência. O que já está com as ligações feitas e conferidas não funcionam corretamente. Obs.: Já foram trocados os CIs para testar se eles estavam queimados e nada mudou. | ||

| − | |||

;29julho2013; | ;29julho2013; | ||

*Apesar de conferido, refeito, e testado diversas vezes, o gerador continua com um erro e não funciona corretamente. | *Apesar de conferido, refeito, e testado diversas vezes, o gerador continua com um erro e não funciona corretamente. | ||

| + | |||

;30julho2013; | ;30julho2013; | ||

*Refazendo o gerador de sequência no Quartus, agora com o D numa entrada qualquer e com o CI 7486 apenas ligado em uma saída. | *Refazendo o gerador de sequência no Quartus, agora com o D numa entrada qualquer e com o CI 7486 apenas ligado em uma saída. | ||

| Linha 271: | Linha 669: | ||

*Refazer o gerador de sequência no protoboard virtual de acordo com a nova versão do Quartus. | *Refazer o gerador de sequência no protoboard virtual de acordo com a nova versão do Quartus. | ||

*Obs.: Clock e entrada ligados a uma chave. | *Obs.: Clock e entrada ligados a uma chave. | ||

| − | + | ||

;19Agosto2013; | ;19Agosto2013; | ||

*Refazendo alguns testes com o gerador de sequência pseudoaleatória. É necessário que o teste no Qsim apresente um loop, após gerar uma sequência. | *Refazendo alguns testes com o gerador de sequência pseudoaleatória. É necessário que o teste no Qsim apresente um loop, após gerar uma sequência. | ||

| Linha 324: | Linha 722: | ||

;23Agosto2013; | ;23Agosto2013; | ||

;PINAGEM; | ;PINAGEM; | ||

| − | |||

;Versão sem pinagem; | ;Versão sem pinagem; | ||

| − | [[Imagem:k002.png| | + | [[Imagem:k002.png|200px]] |

| − | |||

;26Agosto2013; | ;26Agosto2013; | ||

*Para explicar as etapas do contador assíncrono crescente, analisar e resumir o livro do Pedroni referente a esse assunto. | *Para explicar as etapas do contador assíncrono crescente, analisar e resumir o livro do Pedroni referente a esse assunto. | ||

| Linha 337: | Linha 733: | ||

*Roteiro Quartus finalizado. | *Roteiro Quartus finalizado. | ||

*Escolhidos alunos que participarão dos teste: | *Escolhidos alunos que participarão dos teste: | ||

| − | |||

**Vinicuis Kachniacz - 4 fase Tecnólogo Telecom | **Vinicuis Kachniacz - 4 fase Tecnólogo Telecom | ||

| − | |||

| − | |||

| − | |||

**Maykon Chagas - 7 fase Tecnólogo Telecom | **Maykon Chagas - 7 fase Tecnólogo Telecom | ||

| − | **Everton Lopes - | + | **Everton Lopes - 8 fase Técnico-Integrado Telecom |

| − | + | **Fábio Mafra - 2 fase Engenharia de Telecom | |

;28Agosto2013; | ;28Agosto2013; | ||

*Refeito o esquemático no protoboard real, e encontrado um erro na pinagem. | *Refeito o esquemático no protoboard real, e encontrado um erro na pinagem. | ||

| Linha 352: | Linha 744: | ||

*Versão do Quartus será feita com o CI comercial, mas para a inciação da implementação será necessária a versão em dff imprimida. | *Versão do Quartus será feita com o CI comercial, mas para a inciação da implementação será necessária a versão em dff imprimida. | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

;02Setembro2013; | ;02Setembro2013; | ||

*Editando imagens para a utilização nos teste (incluindo resumo do livro Pedroni que menciona o contador, e imagens do Quartus com a versão do contador em DFF). | *Editando imagens para a utilização nos teste (incluindo resumo do livro Pedroni que menciona o contador, e imagens do Quartus com a versão do contador em DFF). | ||

| Linha 370: | Linha 757: | ||

*Refazer o projeto no MultiSim versão demo, mas colocando as saídas no display. Ver se é possível fazer a análise de ondas como no outro modelo. | *Refazer o projeto no MultiSim versão demo, mas colocando as saídas no display. Ver se é possível fazer a análise de ondas como no outro modelo. | ||

| − | |||

;09Setembro2013; | ;09Setembro2013; | ||

*Refazer a pinagem da primeira etapa do teste(pinagem muito facilitada). | *Refazer a pinagem da primeira etapa do teste(pinagem muito facilitada). | ||

| Linha 399: | Linha 785: | ||

**O módulo de como os questionários serão feitos já foi analisado. Já foi criado um arquivo com contendo algumas perguntas. Porém, faltam discussões mais aprofundadas sobre o teor das perguntas que serão questionadas aos alunos e profs, com o intuito de não perder o enfoque da pesquisa. | **O módulo de como os questionários serão feitos já foi analisado. Já foi criado um arquivo com contendo algumas perguntas. Porém, faltam discussões mais aprofundadas sobre o teor das perguntas que serão questionadas aos alunos e profs, com o intuito de não perder o enfoque da pesquisa. | ||

| − | |||

;23Setembro2013; | ;23Setembro2013; | ||

*Fazendo estudo teórico sobre os contadores para a inicialização das explicações nos testes. | *Fazendo estudo teórico sobre os contadores para a inicialização das explicações nos testes. | ||

| Linha 418: | Linha 803: | ||

;04Outubro2013; | ;04Outubro2013; | ||

*Fazer instalação do Quartus no pc202. | *Fazer instalação do Quartus no pc202. | ||

| − | + | ||

;07Outubro2013; | ;07Outubro2013; | ||

*Erro na instalação do Quartus no pc do labIC2 (no Qsim) | *Erro na instalação do Quartus no pc do labIC2 (no Qsim) | ||

| Linha 432: | Linha 817: | ||

*Tentativa de implementação no lab de PRG, porém houve um erro causado pela licença. | *Tentativa de implementação no lab de PRG, porém houve um erro causado pela licença. | ||

*Atualizar o doc da licença. | *Atualizar o doc da licença. | ||

| − | + | ||

;22Outubro2013; | ;22Outubro2013; | ||

*Implementação no laboratório de PRG com a placa DEO-Nano realizada com sucesso. | *Implementação no laboratório de PRG com a placa DEO-Nano realizada com sucesso. | ||

| Linha 462: | Linha 847: | ||

*Nova tentativa de implementação com a placa DE2-115 | *Nova tentativa de implementação com a placa DE2-115 | ||

| − | |||

;29Outubro2013; | ;29Outubro2013; | ||

*Analisar: | *Analisar: | ||

| Linha 497: | Linha 881: | ||

*[[Contador Assíncrono Crescente - Roteiro para implementação e simulação com QUARTUS II, QSIM e kit DE2-115]] | *[[Contador Assíncrono Crescente - Roteiro para implementação e simulação com QUARTUS II, QSIM e kit DE2-115]] | ||

| − | |||

;05Outubro2013; | ;05Outubro2013; | ||

*Fazer roteiro do Multisim e matriz virtual | *Fazer roteiro do Multisim e matriz virtual | ||

| Linha 540: | Linha 923: | ||

*Testando o Lab RedesI para o uso do Multisim e protoboard virtual. (Máq virtual Windows já instalada) | *Testando o Lab RedesI para o uso do Multisim e protoboard virtual. (Máq virtual Windows já instalada) | ||

*Os dois softwares necessários estão instalados e funcionando corretamente. | *Os dois softwares necessários estão instalados e funcionando corretamente. | ||

| + | *Contador implementado no Multisim. Tudo ok. | ||

| + | *Contador implementado no WBR a partir da montagem do multisim. Tudo ok. | ||

| + | |||

| + | ;11Novembro2013; | ||

| + | *Término do primeiro e segundo roteiro. | ||

| + | ;12Novembro2013; | ||

| + | *Revisão do projeto no Quartus. | ||

| + | *Projeto no Quartus foi implementado e programado. | ||

| + | ;13Novembro2013; | ||

| + | *Atualizar o roteiro do Quartus. | ||

| + | *Concluir a parte de gravação. | ||

| + | *Atualizar as imagens do Qsim. | ||

| + | ;14Novembro2013; | ||

| + | *Erro no arquivo da pinagem da ALTERA. | ||

| + | *Utilizando no projeto os LEDs verdes. | ||

| + | *Roteiro finalizado. | ||

| + | |||

| + | ;18-22Novembro2013; | ||

| + | *Viagem de estudos para São Paulo. | ||

| + | |||

| + | ;25Novembro2013; | ||

| + | *Realizado duas etapas (Montagem na matriz e Multisim/matriz virtual) com três alunos. | ||

| + | *Os testes serão feitos no LabAA. | ||

| + | *Quartus já foi atualizado para poder programar nos pcs do LabAA. | ||

| + | |||

| + | ;27Novembro2013; | ||

| + | *Teste pela manhã com o Maykon 3 etapa (Quartus e Qsim) | ||

| + | *Teste pela tarde com o Vinícius 3 etapa (Quartus e Qsim) | ||

| + | *Teste pela noite com o Everton 3 etapa (Quartus e Qsim) | ||

| + | |||

| + | ;28Novembro2013; | ||

| + | *Teste pela noite com o Fábio Mafra (Eng Telecom) 1 (Matriz real) e 2 etapa (Matriz real e Multisim/Matriz virtual) | ||

| + | *Mandar os emails para os alunos que já completaram os experimentos. | ||

| + | *Analisar o formulário dos professores e enviar versão final. | ||

| + | |||

| + | ;29Novembro2013; | ||

| + | *Teste pela tarde com o Fábio 2 etapa (Multisim/Matriz virtual) e 3 etapa (Quartus e Qsim) | ||

| + | *Terminar alguns detalhes dos formulários. | ||

| + | |||

| + | |||

| + | ;02Dezembro2013; | ||

| + | *Mandar os emails para os alunos que já finalizaram os testes (Maykon, Everton, Vinicius e Fabio)., | ||

| + | *Racunho de email para os professores. | ||

| + | |||

| + | ;03Dezembro2013; | ||

| + | *Teste pela manhã com dois alunos do tecnólogo (Matriz Real e Multisim/Matriz virtual) | ||

| + | |||

| + | ;04Dezembro2013; | ||

| + | *Email já foi mandando para os professores com os formulários. | ||

| + | *Professora Elen implementará o roteiro com uma turma do Integrado | ||

| + | *Fazer roteiro com pinagem para a Mercúrio VI | ||

| + | *Pinagem [http://wiki.sj.ifsc.edu.br/index.php/Pinagem_dos_dispositivos_de_entrada_e_sa%C3%ADda_do_kit_MERCURIO_IV MERCURIO IV] | ||

| + | *Manual [http://wiki.sj.ifsc.edu.br/images/6/68/ManualMercurio.pdf MERCURIO IV] | ||

| + | *[[Imagem:7seg_mercurio.png]] | ||

| + | |||

| + | |||

| + | ;06Dezembro2013; | ||

| + | *Realizar os roteiros com a Jessica (Matriz Real, Multisim/matriz virtual e Quartus). | ||

| + | *Preparar o roteiro para a Mercúrio IV que será utilizado em aula pela Professora Elen. | ||

| + | [[Contador Assíncrono Crescente- Roteiro para implementação e simulação com QUARTUS II, QSIM e kit]] | ||

| + | |||

| + | ;09-13Dezembro2013; | ||

| + | *Testar contador na Mercurio IV. | ||

| + | *Pinagem [ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE0-Nano/DE0_Nano.qsf DEO-NANO] | ||

| + | ;10Dezembro2013; | ||

| + | *Quartus foi apresentado para a Professora Elen. | ||

| + | *Definido com a Prof Elen que a aula de Eletrônica digital para a turma do integrado será na sexta-feira. Serão usados apenas os kits DE2-115. | ||

| + | ;11Dezembro2013 | ||

| + | *O contador foi realizado para a MERCURIO IV, adicionando um circuito anti-repique. | ||

| + | *A pinagem também foi concluída, com algumas mudanças pelo funcionamento da matriz dos LED's. | ||

| + | ;12Dezembro2013; | ||

| + | *Iniciar relatório técnico. | ||

| + | *Separar as placas DE2-115 para o experimento na sexta-feira. | ||

| + | *Aplicar os formulários com os alunos do Integrado. | ||

| + | ;13Dezembro2013; | ||

| + | *Aula com a professora Elen na turma do Integrado no primeiro horário da tarde. | ||

| + | *Aula com o professor Eduardo, dando continuidade no projeto feito no Quartus com os alunos, no segundo horário da tarde. | ||

| + | |||

| + | ;16-18Dezembro2013; | ||

| + | *Realizar testes com o Quartus com 2 alunos. | ||

| + | *Relatório Técnico. | ||

| + | {{Collapse bottom}} | ||

| + | {{Collapse top | Roteiros - Contadores Assíncronos Crescente}} | ||

| + | |||

| + | * [[Contador Assíncrono Crescente - Roteiro para montagem na matriz de contatos real]] | ||

| + | * [[Contador Assíncrono Crescente - Roteiro para simulação no MULTISIM e montagem na matriz de contatos virtual]] | ||

| + | * [[Contador Assíncrono Crescente - Roteiro para implementação e simulação com QUARTUS II, QSIM e kit DE2-115]] | ||

| + | * [http://wiki.sj.ifsc.edu.br/index.php/Contador_Ass%C3%ADncrono_Crescente_-_Roteiro_para_implementa%C3%A7%C3%A3o_e_simula%C3%A7%C3%A3o_com_QUARTUS_II%28v.13%29,_QSIM_e_kit_DE2-115 Contador Assíncrono Crescente - Roteiro para implementação e simulação com QUARTUS II, QSIM e kit DE2-115 V.13 ] | ||

| + | |||

| + | {{Collapse bottom}} | ||

| − | + | {{Collapse top |Métodos de pesquisa e aplicação }} | |

| − | + | <big>'''Contador Assíncrono Crescente:'''</big> | |

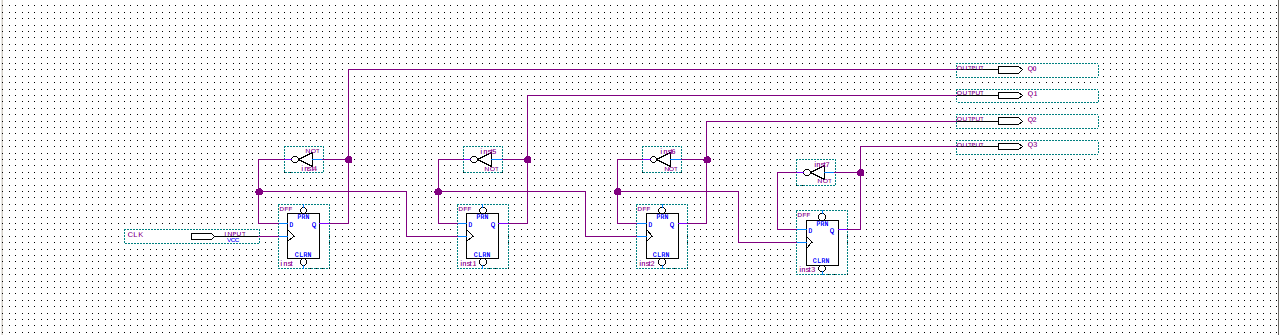

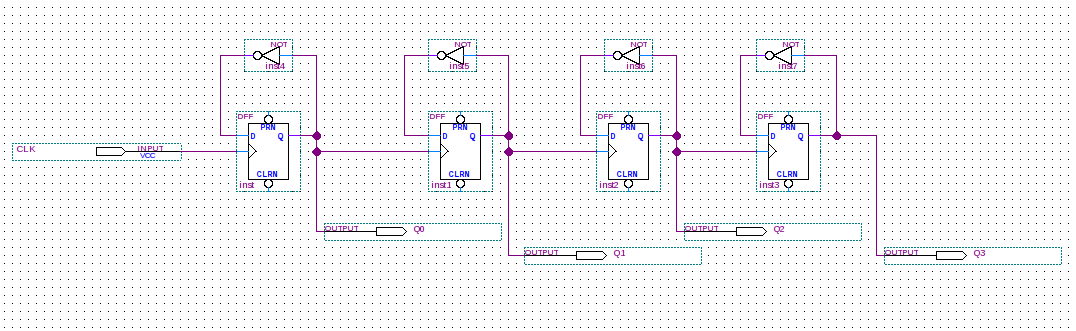

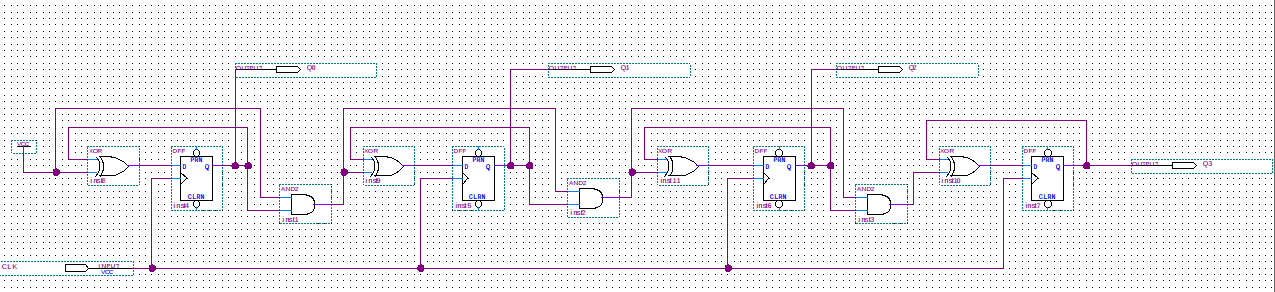

*'''Quartus:''' | *'''Quartus:''' | ||

[[Imagem:Kamila400.png|800px]] | [[Imagem:Kamila400.png|800px]] | ||

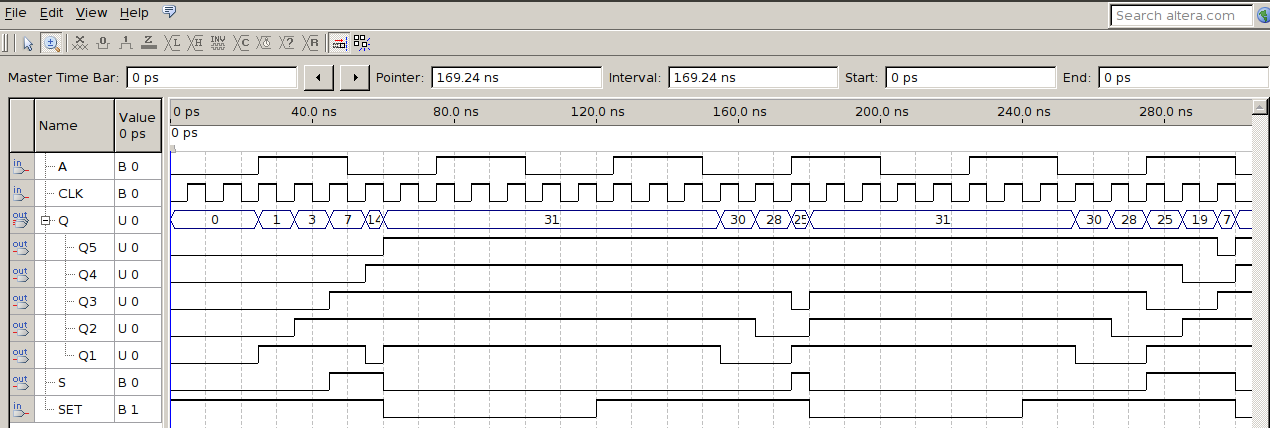

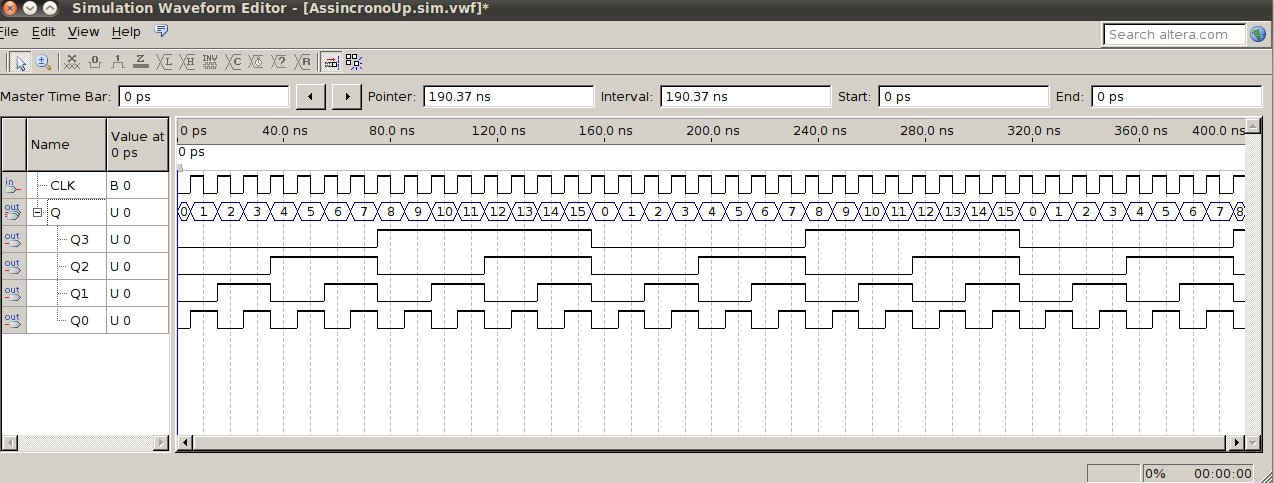

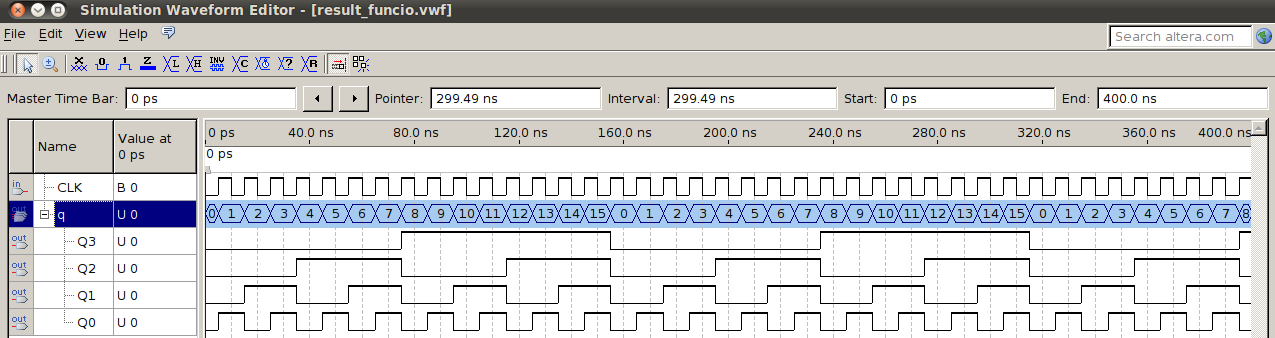

*'''QSim Funcional:''' | *'''QSim Funcional:''' | ||

[[Imagem:Kamila401.png|800px]] | [[Imagem:Kamila401.png|800px]] | ||

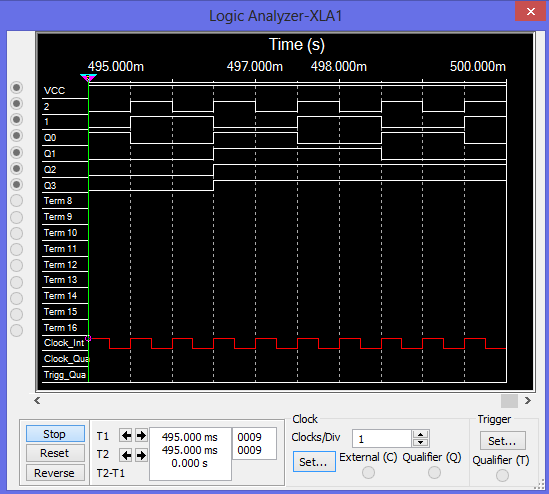

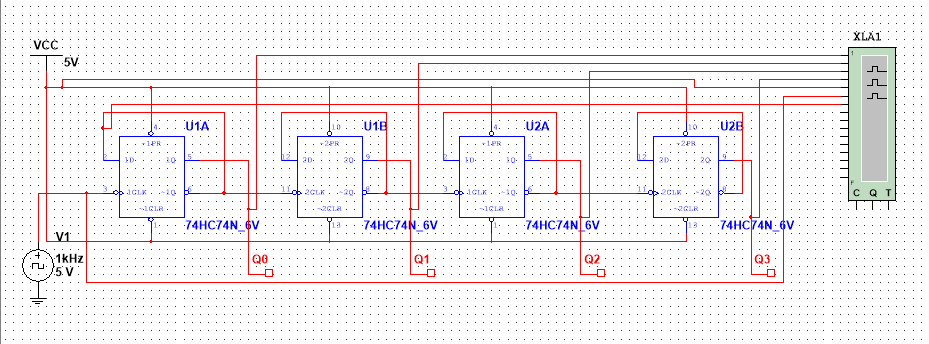

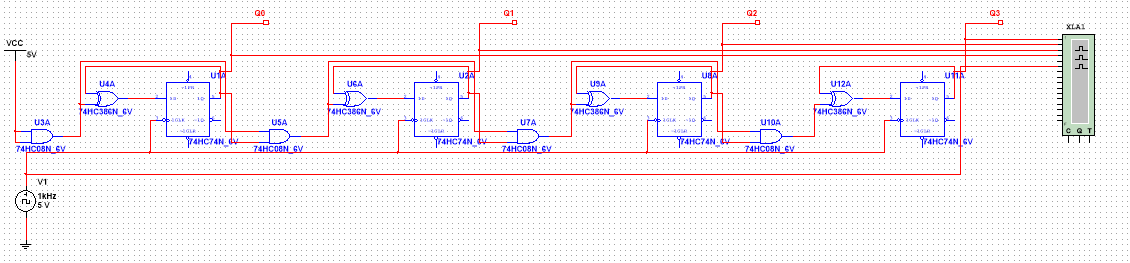

| − | *''' | + | *'''Multisim:''' |

[[Imagem:Kamila41.png|800px]] | [[Imagem:Kamila41.png|800px]] | ||

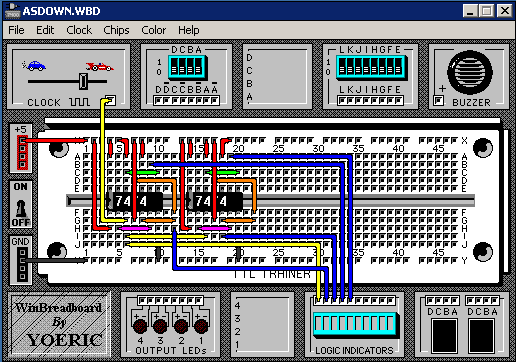

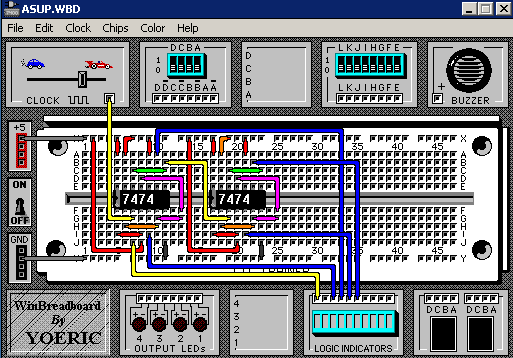

*'''Protoboard virtual:''' | *'''Protoboard virtual:''' | ||

| Linha 555: | Linha 1 028: | ||

[http://youtu.be/mzts7yDE828 Contador assíncrono crescente] | [http://youtu.be/mzts7yDE828 Contador assíncrono crescente] | ||

| − | + | <big>'''Contador Assíncrono Decrescente:'''</big> | |

*'''Quartus:''' | *'''Quartus:''' | ||

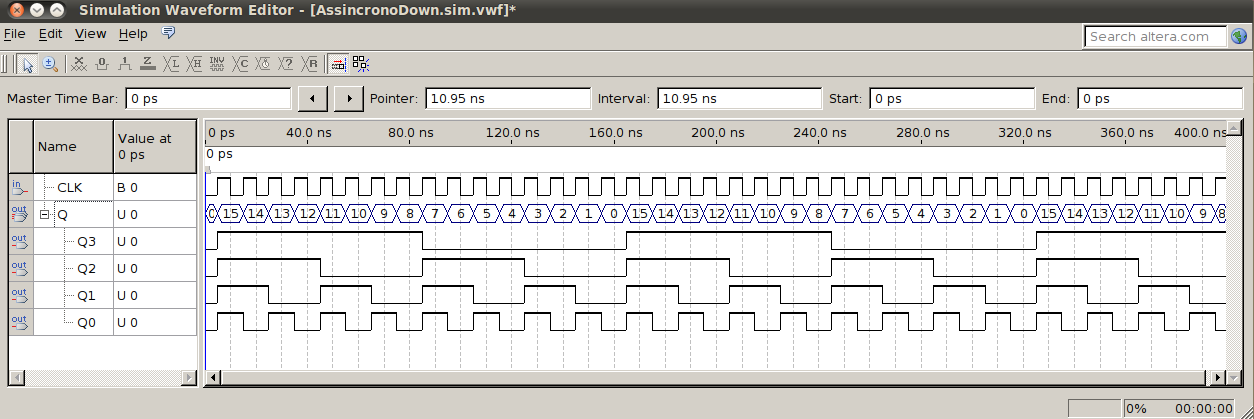

[[Imagem:Kamila43.png|800px]] | [[Imagem:Kamila43.png|800px]] | ||

*'''QSim funcional:''' | *'''QSim funcional:''' | ||

[[Imagem:Kamila403.png|800px]] | [[Imagem:Kamila403.png|800px]] | ||

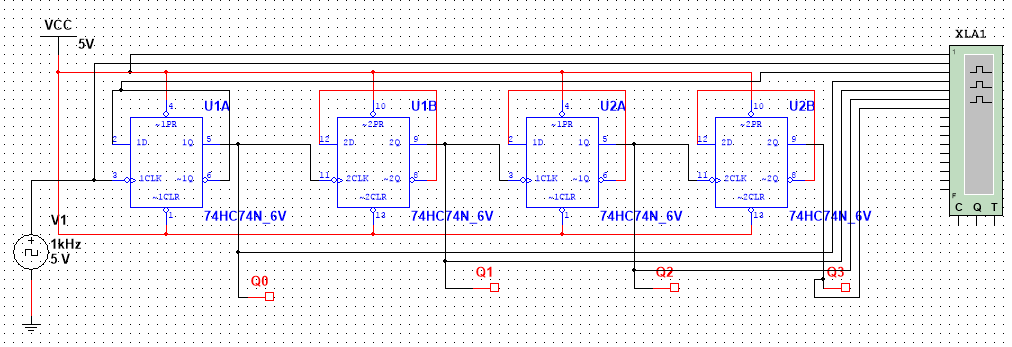

| − | *''' | + | *'''Multisim:''' |

[[Imagem:Kamila44.png|800px]] | [[Imagem:Kamila44.png|800px]] | ||

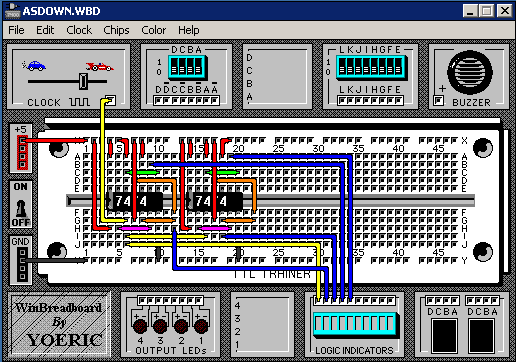

*'''Protoboard virtual:''' | *'''Protoboard virtual:''' | ||

| Linha 567: | Linha 1 040: | ||

[http://youtu.be/FYYbcwGmnCQ Contador assíncrono decrescente] | [http://youtu.be/FYYbcwGmnCQ Contador assíncrono decrescente] | ||

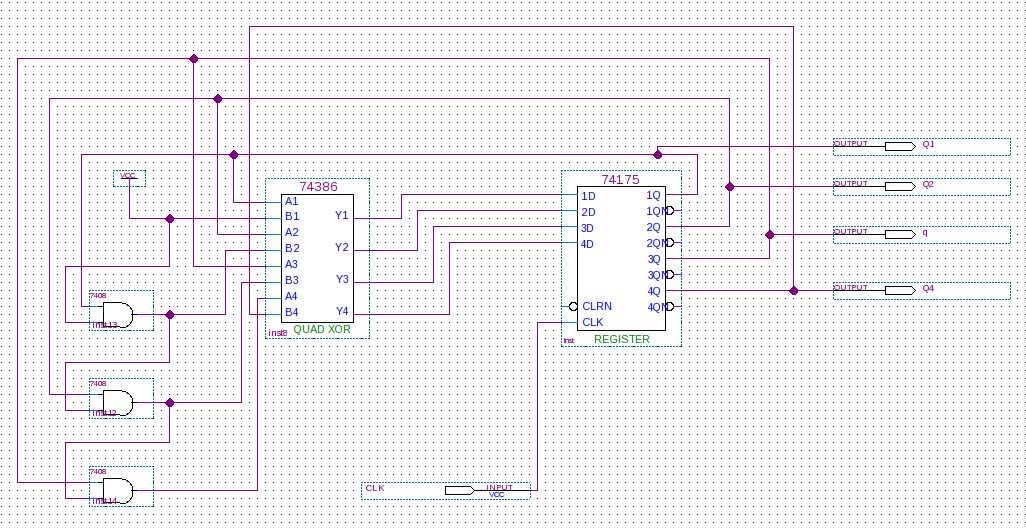

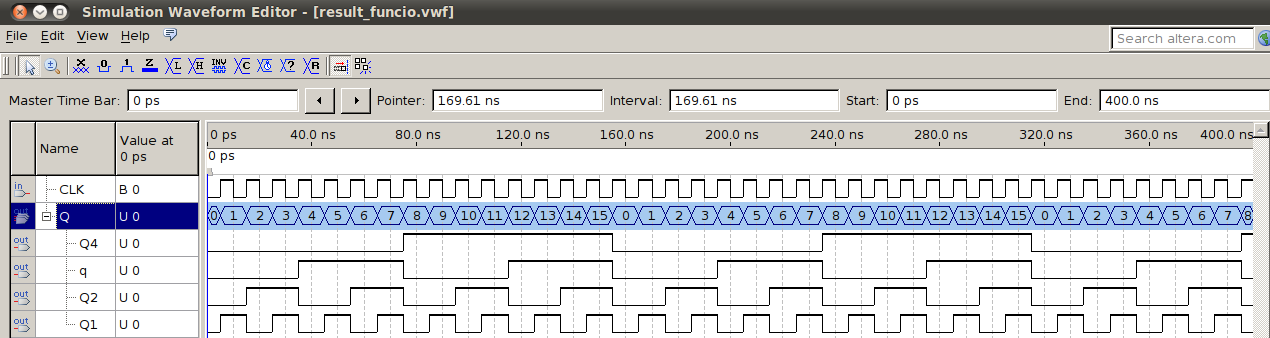

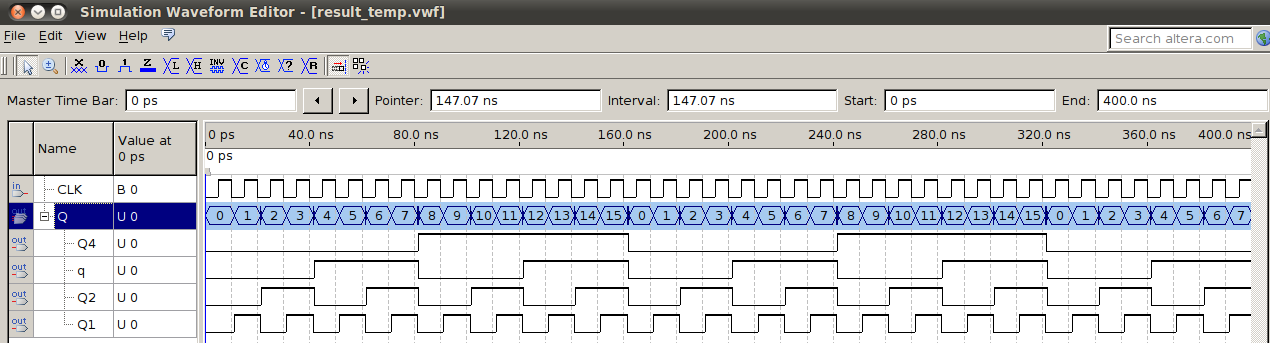

| − | + | <big>'''Contador Síncrono:'''</big> | |

| − | |||

*'''Quartus:''' | *'''Quartus:''' | ||

[[Imagem:Kamila800.png|900px]] | [[Imagem:Kamila800.png|900px]] | ||

*'''QSim funcional:''' | *'''QSim funcional:''' | ||

[[Imagem:Kamila801.png|800px]] | [[Imagem:Kamila801.png|800px]] | ||

| − | *''' | + | *'''Multisim:''' |

[[Imagem:Kamila47.png|900px]] | [[Imagem:Kamila47.png|900px]] | ||

*'''Protoboard virtual:''' | *'''Protoboard virtual:''' | ||

| Linha 580: | Linha 1 052: | ||

[http://youtu.be/bpIu9UtG4ek Contador Síncrono] | [http://youtu.be/bpIu9UtG4ek Contador Síncrono] | ||

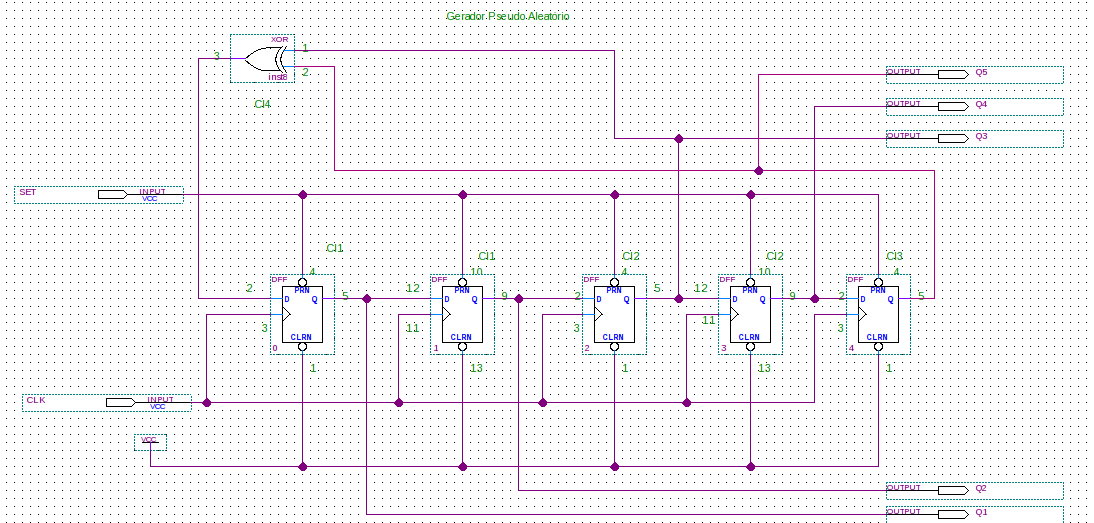

| − | + | <big>'''Gerador de Sequência Pseudoaleatória:'''</big> | |

*'''Quartus:''' | *'''Quartus:''' | ||

[[Imagem:Kamila499.png|800px]] | [[Imagem:Kamila499.png|800px]] | ||

*'''QSim funcional:''' | *'''QSim funcional:''' | ||

[[Imagem:Kamila580.png|800px]] | [[Imagem:Kamila580.png|800px]] | ||

| − | *''' | + | *'''Multisim:''' |

[[Imagem:Kamila50.png|800px]] | [[Imagem:Kamila50.png|800px]] | ||

*'''Protoboard virtual:''' | *'''Protoboard virtual:''' | ||

Edição atual tal como às 01h33min de 9 de maio de 2015

- Publicação: Modernização das aulas de Laboratório de Circuitos Lógicos - 2013.

- Publicação: Modernização das aulas de laboratório de circuitos lógicos: fase implementação - 2014.

- Sugestão de Experimentos.

- Estudo de Circuitos Aritméticos e Implementação em Dispositivos Lógicos Programáveis

- TCC - Estudo de Unidades de Aritmética implementadas com DLP

| Mestrado |

|---|

|

| 2014: Implementação | ||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Semanário do Bolsista 2014: Implementação

Abril

Maio

Junho

| ||||||||||||||||||||||||||||||||||||||||||

| 2013: Pesquisa |

|---|

Diário do Bolsista 2013: Pesquisa

Obs.:O clock é ligado a saída (Q'), apresentei essa solução já que não encontrei uma porta(dff, etc) que houvesse duas saídas Q e Q'

Apostila de Eletrônica Digital Marcos Moecke

|

| Métodos de pesquisa e aplicação |

|---|

|

Contador Assíncrono Crescente:

Contador Assíncrono Decrescente:

Contador assíncrono decrescente Contador Síncrono:

Gerador de Sequência Pseudoaleatória:

XXXX |