Mudanças entre as edições de "Implementação de sistemas de telecomunicações digitais utilizando simulink e HDL coder"

| (31 revisões intermediárias por 2 usuários não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

| + | Link curto: http://bit.ly/Simulink2HDL-IFSC | ||

| + | |||

=Resumo do projeto= | =Resumo do projeto= | ||

| Linha 41: | Linha 43: | ||

#*Será feito através da plataforma dot.project (https://dotproject.sj.ifsc.edu.br/) disponível no campus São José. | #*Será feito através da plataforma dot.project (https://dotproject.sj.ifsc.edu.br/) disponível no campus São José. | ||

| + | =Implementação - FFT utilizando simulink= | ||

| + | |||

| + | Arquivos das versões da FFT: [[Media:Versoes_FFT.zip | Versões FFT]] | ||

| + | |||

| + | Documentação das modificações da FFT: [[Media:VERSION.txt | Versões]] | ||

| + | |||

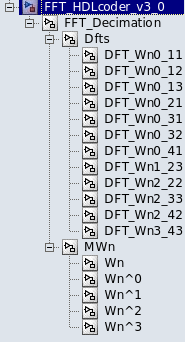

| + | *Versão 3_0 - ultima versão | ||

| + | |||

| + | Uma visão geral dos blocos: | ||

| + | |||

| + | [[Imagem:FFT_funcionamento.png| center | 200 px]] | ||

| + | <center> Figura 1 - Visão macroscópica da FFT </center> | ||

| + | |||

| + | ==Blocos da FFT== | ||

| + | |||

| + | ===Bloco - "FFT Decimation"=== | ||

| + | |||

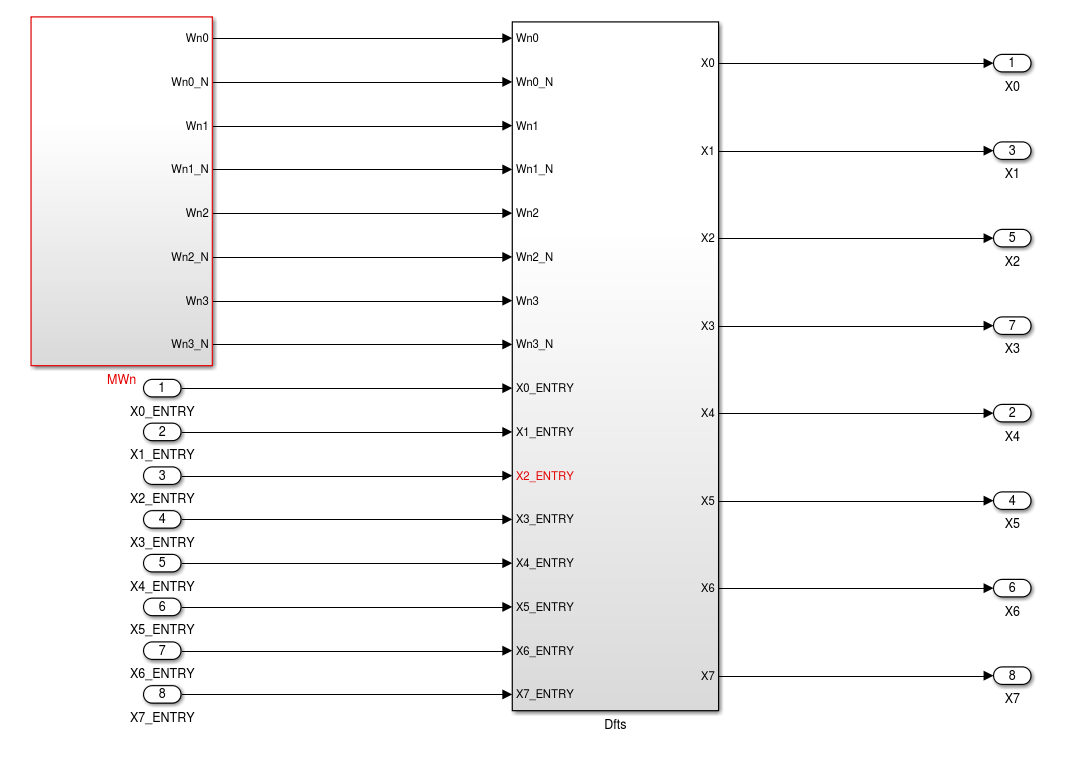

| + | O bloco '''FFT Decimation''' é um subsistema que agrupa os subsistemas '''Dfts''' e '''Mwn'''. Na versão atual (3.0) as entradas são {x0_ENTRY .. x7_ENTRY} para 8 amostras temporais do sinal. As saídas no domínio transformado são {X0 .. X7}. Para a utilização do subsistema é necessário dividir o sinal de entrada em quadros de 8 amostras paralelas e processá-las. Para possibilitar uma melhor resolução de frequência da FFT é necessário aumentar o número de amostras do sinal no tempo, e para tal será desenvolvido um desserializador e um serializador para permitir o uso de entradas e saídas seriais, nas quais as amostras entram sequencialmente formando um quadro de N amostras. | ||

| + | |||

| + | [[Imagem:Imagem geral.png| center | 800 px]] | ||

| + | <center> Figura 1 - Composição do Bloco - "FFT Decimation </center> | ||

| + | |||

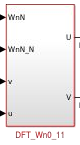

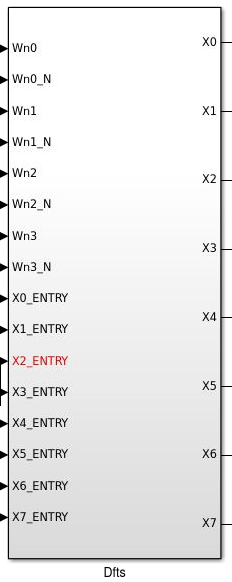

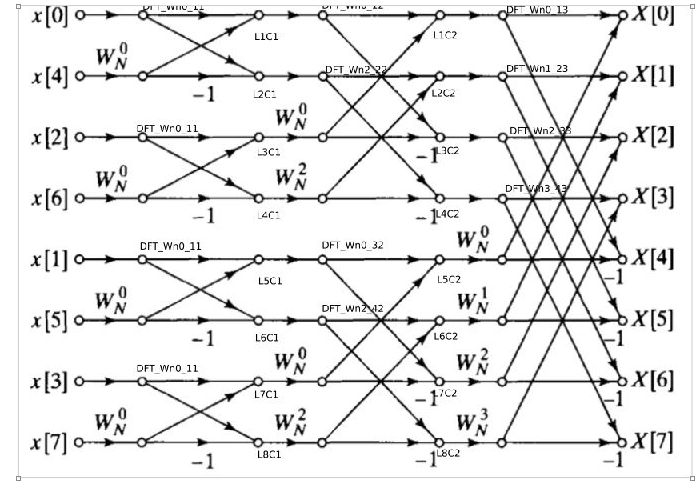

| + | === Bloco - "Dfts" === | ||

| + | O bloco '''Dfts''' realiza os cálculos das ''butterflies'' através de pequenas células (ver figura). O subsistema '''Dfts''' possui 16 entradas, sendo 8 correspondentes as amostras temporais do sinal de entrada do bloco '''FFT Decimation''', e 8 correspondentes ao valores calculados de Wn (mostrado abaixo). Esse bloco é implementado através de 12 blocos idênticos (células {DFT_Wn0_11 .. DFT_Wn043}) que realizam o cálculo da ''butterfly''. As saídas do .... | ||

| + | {| | ||

| + | |[[Imagem:Dfts.png| 200 px]] | ||

| + | |[[Imagem:Butter.png| 650 px]] | ||

| + | |} | ||

| + | |||

| + | Em conjunto, os blocos do dft calculam as butterflies de acordo com a figura 5. A célula recebe quatro entradas: '''({u, v})''' e '''({WnN, WnN_N})'''. As entradas '''({u, v})''' vem ou da entrada inicial do FFT Decimation ou da saída de uma outra butterfly. Os valores de '''{WnN, WnN_N}''' são oriundos do bloco '''Mwn''', que será explicado mais adiante. | ||

| + | |||

| + | [[Imagem:Celula.png| center | 150 px]] | ||

| + | <center> Figura 4 - Bloco-célula de uma butterfly </center> | ||

| + | |||

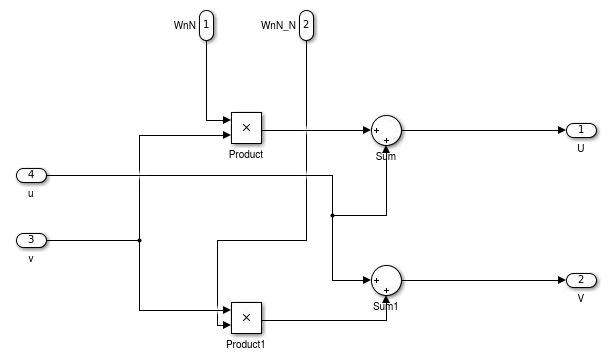

| + | As quatro entradas se relacionam de acordo com a figura 5. A entrada '''v''' é multiplicada por '''WnN''' e por '''WnN_N'''. Os dois resultados gerados são somados com a entrada '''u'''. A butterfly gera, no fim, uma saída '''U''' e uma saída '''V''', que poderá ser a saída final da FFT ou pode ser cascateada para outra butterfly. | ||

| + | |||

| + | [[Imagem:Isolado.png| center | 600 px]] | ||

| + | <center> Figura 5 - Esquema interno butterfly </center> | ||

| + | |||

| + | O procedimento que ocorre dentro da butterfly pode ser descrito, didaticamente, de acordo com a figura 6. | ||

| + | |||

| + | [[Imagem:Fly.png| center | 600 px]] | ||

| + | <center> Figura 6 - Funcionamento didático butterfly </center> | ||

| + | |||

| + | === Bloco - "Mwn" === | ||

| + | O segundo grande bloco do subsystem FFT Decimation é o Mwn. Esse bloco é o responsável pelo cálculo dos Wn do sistema. | ||

| + | {| | ||

| + | |[[Ficheiro: Mwn.png |Mwn| center | 200 px]] | ||

| + | |[[Ficheiro: Interno.png|Estrutura interna do Mwn|center | center | 600 px]] | ||

| + | <center> Figura 7 - Mwn e sua estrutura interna </center> | ||

| + | |} | ||

| + | |||

| + | O subsistema '''Mwn''' possui apenas saídas. São 8 saídas que correspondem aos Wn calculados. Na versão 3_0 possui uma constante chamada '''constant8''' que vale (1/8), mas na verdade ela representa 1/N, porém, essa versão comporta apenas 8 entradas, por isso optou-se por uma constante de valor 1/8. Em futuras versões esse bloco irá ter 1 entrada que irá corresponder ao N (número de entradas). A figura 7 representa uma visão geral do bloco Mwn. | ||

| + | |||

| + | ==== Bloco - "Wn" ==== | ||

| + | |||

| + | O bloco Wn possui 1 entrada ('''1:N''') e uma saída ('''Wn'''). A Figura 8 demonstra sua visão macroscópica e a figura 9 representa seu esquema interno. | ||

| + | |||

| + | [[Imagem:Wn.png| center | 100 px]] | ||

| + | <center> Figura 8 - Visão Macroscópica de Wn </center> | ||

| + | |||

| + | *Esqueleto interno do bloco Wn: | ||

| + | |||

| + | [[Imagem:Wn interno.png| center | 800 px]] | ||

| + | <center> Figura 9 - Esquema interno Wn </center> | ||

| + | |||

| + | *Para se adequar ao HDL Coder, foi necessário utilizar a estratégia apresentada na figura 10: | ||

| + | |||

| + | [[Imagem:Sen.png| 600 px| center | 800 px]] | ||

| + | <center> Figura 10 - Desmembramento de Wn </center> | ||

| + | |||

| + | O formato padrão de cálculo do Wn se dá por um '''e''' elevado a uma função de N, porém, os blocos disponíveis no HDL coder não suportam o uso de potências de funções. A solução para esse problema foi desmembrar a função Wn em cosseno e seno, além de utilizar equivalências da fórmula de euler, como descrito na figura 10. | ||

| + | |||

| + | ==== Blocos - "{Wn^0 .. Wn^3}" ==== | ||

| + | Dentro do Mwn existem 4 blocos responsáveis pelas potências de Wn (Wn^0, Wn^1, Wn^2, Wn^3). | ||

| + | |||

| + | *Bloco Wn^0: | ||

| + | |||

| + | [[Imagem:wn0.png| center | 100 px]] | ||

| + | <center> Figura 11 - Visão macroscópica Wn^0 </center> | ||

| + | |||

| + | A estratégia menos custosa encontrada para resolver o cálculo de Wn^0 foi levar em consideração que qualquer número elevado a zero é igual a 1. Como descrito na imagem 12, percebe-se que o bloco em questão não possui entradas. Isso ocorre pelo mesmo motivo descrito anteriormente. Não importa qual o valor de Wn, já que o único valor possível será 1. O bloco possui 2 saídas: '''W0''' e '''W0_N'''. O '''W0''' corresponde ao '''Wn^0''' original e o '''W0_N''' corresponde ao '''Wn^0''' negado. Para calcular a parte negada, foi usado o bloco unary minus, que nada mais é do que um inversor. | ||

| + | |||

| + | Esquema interno Wn^0: | ||

| + | |||

| + | [[Imagem:wn0 int.png| center |600 px]] | ||

| + | <center> Figura 12 - Esquema interno Wn^0 </center> | ||

| + | |||

| + | *Bloco Wn^1: | ||

| + | |||

| + | [[Imagem:wn1.png| center | 100 px]] | ||

| + | <center> Figura 13 - Visão macroscópica Wn^1 </center> | ||

| + | |||

| + | O bloco '''Wn^1''' segue quase o mesmo esquema do '''Wn^0'''. O bloco possui 1 entrada que corresponde ao valor de Wn calculado no bloco '''Wn'''. Como esse bloco é Wn^1, sabemos que todo número elevado a 1 é igual a ele mesmo, portanto, o valor de Wn^1 será sempre ele mesmo. Assim como no bloco Wn^0, esse bloco possui 2 saídas: '''Wn1''' e '''~Wn1'''. Wn1 corresponde ao valor original de '''Wn^1''' e '''~Wn1''' é o seu valor negado. Foi utilizado a mesma estratégia do unary minus. Se esquema é representado na figura 14. | ||

| + | |||

| + | Esquema interno Wn^1: | ||

| + | |||

| + | [[Imagem:wn1 int.png| center |600 px]] | ||

| + | <center> Figura 14 - Esquema interno Wn^1 </center> | ||

| + | |||

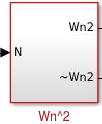

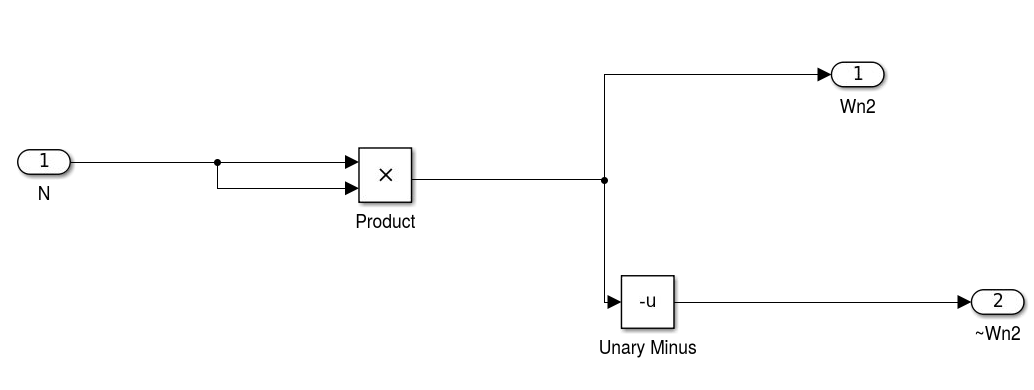

| + | *Bloco Wn^2: | ||

| + | |||

| + | [[Imagem:wn2.png| center | 100 px]] | ||

| + | <center> Figura 15 - Visão macroscópica Wn^2 </center> | ||

| + | |||

| + | No bloco Wn^2 foi utilizada uma estratégia um pouco diferente dos blocos anteriores. Como já explanado anteriormente, o HDL coder não possui suporte para potências, portanto, o cálculo de Wn^2 necessita de algum estratégia para fazer essa potência. Sabemos que Wn^2 = Wn*Wn, logo, podemos utilizar a única entrada do bloco e conjunto com um bloco product para multiplicar a entrada N (que corresponde ao Wn calculado no bloco Wn) e obter o mesmo resultado de Wn^2. O bloco Wn^2 também possui 2 saídas: '''Wn2''' e '''~Wn2'''. Wn2 corresponde ao valor original de '''Wn^2''' e '''~Wn2''' é o seu valor negado. Foi utilizado a mesma estratégia do unary minus. Seu esquema é representado na figura 16. | ||

| + | |||

| + | Esquema interno Wn^2: | ||

| + | |||

| + | [[Imagem:wn2 int.png| center |800 px]] | ||

| + | <center> Figura 16 - Esquema interno Wn^2 </center> | ||

| + | |||

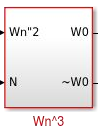

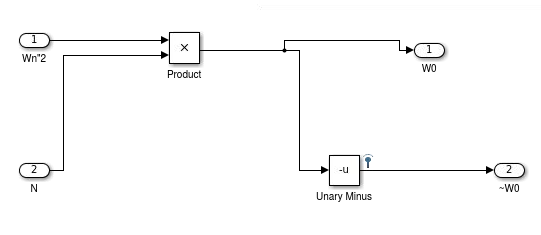

| + | *Bloco Wn^3: | ||

| + | |||

| + | [[Imagem:wn3.png| center | 100 px]] | ||

| + | <center> Figura 17 - Visão macroscópica Wn^3 </center> | ||

| + | |||

| + | O bloco Wn^3 possui uma estratégia para que seja poupado hardware. Sabemos que Wn^3 = Wn*Wn*Wn. Seria natural utilizar 2 blocos products para realizar essa operação, porém, podemos pegar a saída '''Wn2''' e cascatear para esse bloco. Como Wn2 foi calculado como Wn*Wn, precisamos apenas fazer Wn2*Wn e iremos obter Wn3. Essa estratégia é descrita na figura 18. O bloco Wn^3 também possui 2 saídas: '''Wn3''' e '''Wn3_N'''. Wn3 corresponde ao valor original de '''Wn^2''' e '''Wn3_N''' é o seu valor negado. Foi utilizado a mesma estratégia do unary minus. Seu esquema é representado na figura 18. | ||

| + | |||

| + | Esquema interno Wn^3: | ||

| + | |||

| + | [[Imagem:wn3 int.png| center |800 px|]] | ||

| + | <center> Figura 18 - Esquema interno Wn^3 </center> | ||

=Viabilidade da implementação dos Modelos do projeto: [[INCENTIVANDO O USO DO SIMULINK NOS CURSOS DE TELECOMUNICAÇÕES]]= | =Viabilidade da implementação dos Modelos do projeto: [[INCENTIVANDO O USO DO SIMULINK NOS CURSOS DE TELECOMUNICAÇÕES]]= | ||

| + | |||

| + | *Os blocos que possuem suporte para HDL estão em: [[Blocos Simulink com suporte HDL]] | ||

| + | |||

{{Collapse top |expand = true |[[ Modulações Analógicas | Modulações Analógicas (AM,FM,PM) ]]}} | {{Collapse top |expand = true |[[ Modulações Analógicas | Modulações Analógicas (AM,FM,PM) ]]}} | ||

| Linha 187: | Linha 315: | ||

{{Collapse bottom}} | {{Collapse bottom}} | ||

| − | {{Collapse top |expand = true |[[Modulação por Codificação Diferencial de Pulso (DPCM)]]}} | + | {{Collapse top |expand = true |[[Modulação por Codificação Diferencial de Pulso(DPCM)]]}} |

{{TabComparar3 | Simulink |Suporte HDL Coder no MATLAB 2014 | Suporte HDL Coder no MATLAB 2015}} | {{TabComparar3 | Simulink |Suporte HDL Coder no MATLAB 2014 | Suporte HDL Coder no MATLAB 2015}} | ||

| Linha 324: | Linha 452: | ||

{{TabComparar3 |DSP System Toolbox|Suporte HDL Coder no MATLAB 2014 | Suporte HDL Coder no MATLAB 2015}} | {{TabComparar3 |DSP System Toolbox|Suporte HDL Coder no MATLAB 2014 | Suporte HDL Coder no MATLAB 2015}} | ||

| − | {{TabComparar3linha |Variance Não| Não}} | + | {{TabComparar3linha |Variance| Não| Não}} |

|} | |} | ||

| Linha 414: | Linha 542: | ||

{{Collapse bottom}} | {{Collapse bottom}} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

=Professor Orientador= | =Professor Orientador= | ||

| Linha 442: | Linha 551: | ||

=Características da Bolsa= | =Características da Bolsa= | ||

O projeto será financiado com bolsa [http://www.cnpq.br/web/guest/pibiti PIBITI do CNPq] e será executado entre Agosto de 2015 e Julho de 2015. | O projeto será financiado com bolsa [http://www.cnpq.br/web/guest/pibiti PIBITI do CNPq] e será executado entre Agosto de 2015 e Julho de 2015. | ||

| + | |||

| + | |||

| + | [[Categoria:Trabalhos de Alunos]] | ||

| + | [[Categoria:Projeto de Pesquisa]] | ||

Edição atual tal como às 14h30min de 9 de setembro de 2016

Link curto: http://bit.ly/Simulink2HDL-IFSC

Resumo do projeto

Este projeto pretende-se realizar um trabalho de pesquisa que visa estudar a utilização do ambiente Simulink® associado ao HDL (Hardware Description Language) Coder, para a realização em hardware programável, especificamente FPGA (Field Programmable Gate Array), de blocos comumente utilizados em sistemas de telecomunicações. São objetivos do projeto o estudo do Simulink®, HDL Coder e HDL Verifier da Matworks. O desenvolvimento de blocos comumente utilizados em sistemas de telecomunicações tais como moduladores, filtros digitais, misturadores e geradores de sinal, utilizando para tal o Simulink, que é um ambiente de diagramas de blocos para a simulação de projetos baseados em modelos. A realização e teste destes blocos em hardware será feita através da conversão de código para VHDL utilizando os toolboxes HDL Coder e HDL Verifier e Modelsim da ALTERA. A síntese e programação dos blocos desenvolvidos em FPGA será realizada utilizando o software Quartus II da ALTERA.

Introdução e Justificativa da Proposição

A maioria dos setores que de produção de equipamentos eletrônicos, especialmente na área de telecomunicações utilizam nos circuitos eletrônicos digitais. Entre estes circuitos a maioria deles atualmente é implementada em hardware utilizandose ASICs (Application Specific Integrated Circuits), DSPs (Digital Signal Processor) ou FPGAs (Field Programmable Gate Array). O projeto, simulação e síntese dos últimos dois tipos é realizada utilizandose ambientes de projeto assistido por computador (por exemplo Quartus II e Modelsim) e alguma linguagem de descrição de hardware (por exemplo Verilog ou VHDL) a qual permite descrever o circuito em um baixo nível, de modo a descrever até a ligação entre os componentes configuráveis nos FPGAs ou ASICs. Como a disponibilização de circuitos lógicos programáveis tais como os FPGAs a um custo cada vez mais baixo (menor que U$50,00), e velocidades crescentes de operação, está ocorrendo um grande aumento no interesse e aplicação dessa tecnologia de hardware em diversos aplicações anteriormente realizadas através de software ou eletrônica discreta. Empresas do setor de equipamentos de telecomunicações passaram a considerar essa tecnologia como uma possibilidade de implementação de grandes partes dos sistemas.

Objetivos do projeto:

- Primeira etapa - Utilizar o ambiente Simulink® para a modelagem e simulação de blocos comumente utilizados em sistemas de telecomunicações.

- Segunda etapa - Utilizar o HDL Coder e Verifier para a transformação dos blocos da primeira etapa em linguagem VHDL.

- Os circuitos da obtidos serão simulados utilizando ModelSim

- Terceira etapa - Os circuitos da segunda etapa serão sintetizados e programados no hardware programável do tipo FPGA.

- Aqui também serão feitos os testes finais.

Metodologia do projeto

- Estudo do Simulink®

- Estudo da sua configuração, interfaces, sinais, blocos, modelagem e simulação de sistemas, geração de código de software e hardware.

- Esta etapa será baseada na leitura de manuais e também sites de ajuda do próprio fabricante (MATHWORKS, 2015a, 2015c, 2015b).

- Estudo das bases da linguagem VHDL

- Esta etapa será baseada na leitura dos capítulos 18 e 19 de (PEDRONI, 2010).

- Estudo do HDL Coder e Verifier®

- Esta etapa será baseada na leitura de manuais e também sites de ajuda do próprio fabricante (MATHWORKS, 2015a, 2015c, 2015b).

- Análise de blocos disponibilizadas

- Analisar blocos disponibilizados por outras universidades e institutos de pesquisa (NAVAS, 2014; TYAGI, 2012; GIORDANO; LEVESQUE, 2015; KRUKOWSKI; KALE, 2011) na área de telecomunicações.

- Desenvolvimento de blocos para sistemas de telecomunicações

- Desenvolvimento de blocos tais como moduladores, filtros digitais, misturadores e geradores de sinal.

- Realização e teste em hardware FPGA

- Utilizando o HDL Coder para a conversão dos blocos para VHDL.

- A implementação será realizada utilizando um kit de desenvolvimento de FPGA.

- Para os testes finais tanto o SignalTap® da ALTERA como um equipamento analisador lógico externo serão necessários.

- Documentação do projeto

- Escrita de relatórios parciais e do relatório final do projeto.

- Preparação de pôster para apresentação em eventos do IFSC, e de artigo para submissão em revista.

- Gerenciamento do projeto

- Será feito através da plataforma dot.project (https://dotproject.sj.ifsc.edu.br/) disponível no campus São José.

Implementação - FFT utilizando simulink

Arquivos das versões da FFT: Versões FFT

Documentação das modificações da FFT: Versões

- Versão 3_0 - ultima versão

Uma visão geral dos blocos:

Blocos da FFT

Bloco - "FFT Decimation"

O bloco FFT Decimation é um subsistema que agrupa os subsistemas Dfts e Mwn. Na versão atual (3.0) as entradas são {x0_ENTRY .. x7_ENTRY} para 8 amostras temporais do sinal. As saídas no domínio transformado são {X0 .. X7}. Para a utilização do subsistema é necessário dividir o sinal de entrada em quadros de 8 amostras paralelas e processá-las. Para possibilitar uma melhor resolução de frequência da FFT é necessário aumentar o número de amostras do sinal no tempo, e para tal será desenvolvido um desserializador e um serializador para permitir o uso de entradas e saídas seriais, nas quais as amostras entram sequencialmente formando um quadro de N amostras.

Bloco - "Dfts"

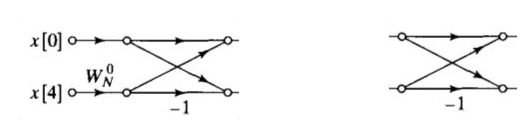

O bloco Dfts realiza os cálculos das butterflies através de pequenas células (ver figura). O subsistema Dfts possui 16 entradas, sendo 8 correspondentes as amostras temporais do sinal de entrada do bloco FFT Decimation, e 8 correspondentes ao valores calculados de Wn (mostrado abaixo). Esse bloco é implementado através de 12 blocos idênticos (células {DFT_Wn0_11 .. DFT_Wn043}) que realizam o cálculo da butterfly. As saídas do ....

|

|

Em conjunto, os blocos do dft calculam as butterflies de acordo com a figura 5. A célula recebe quatro entradas: ({u, v}) e ({WnN, WnN_N}). As entradas ({u, v}) vem ou da entrada inicial do FFT Decimation ou da saída de uma outra butterfly. Os valores de {WnN, WnN_N} são oriundos do bloco Mwn, que será explicado mais adiante.

As quatro entradas se relacionam de acordo com a figura 5. A entrada v é multiplicada por WnN e por WnN_N. Os dois resultados gerados são somados com a entrada u. A butterfly gera, no fim, uma saída U e uma saída V, que poderá ser a saída final da FFT ou pode ser cascateada para outra butterfly.

O procedimento que ocorre dentro da butterfly pode ser descrito, didaticamente, de acordo com a figura 6.

Bloco - "Mwn"

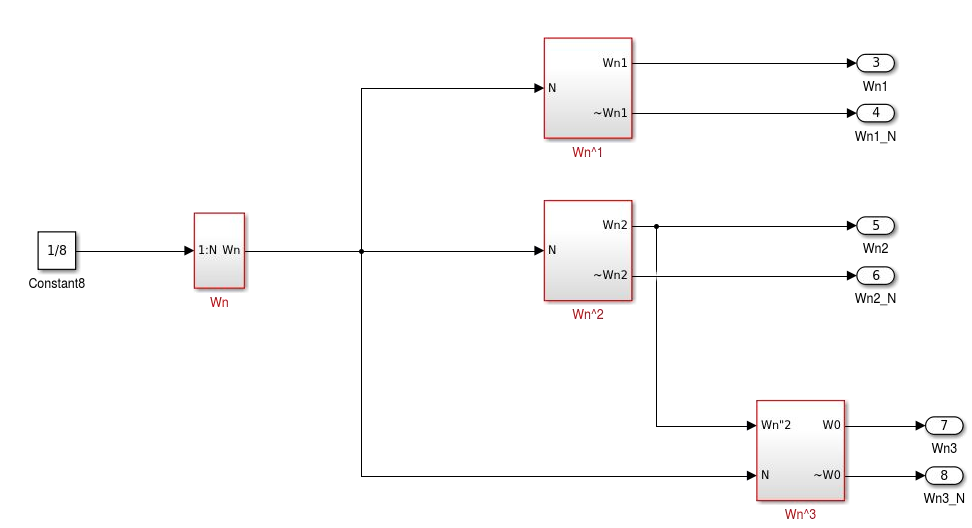

O segundo grande bloco do subsystem FFT Decimation é o Mwn. Esse bloco é o responsável pelo cálculo dos Wn do sistema.

|

|

O subsistema Mwn possui apenas saídas. São 8 saídas que correspondem aos Wn calculados. Na versão 3_0 possui uma constante chamada constant8 que vale (1/8), mas na verdade ela representa 1/N, porém, essa versão comporta apenas 8 entradas, por isso optou-se por uma constante de valor 1/8. Em futuras versões esse bloco irá ter 1 entrada que irá corresponder ao N (número de entradas). A figura 7 representa uma visão geral do bloco Mwn.

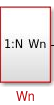

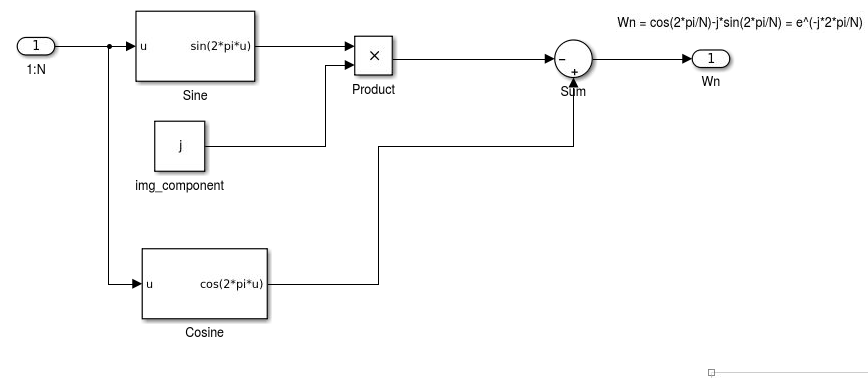

Bloco - "Wn"

O bloco Wn possui 1 entrada (1:N) e uma saída (Wn). A Figura 8 demonstra sua visão macroscópica e a figura 9 representa seu esquema interno.

- Esqueleto interno do bloco Wn:

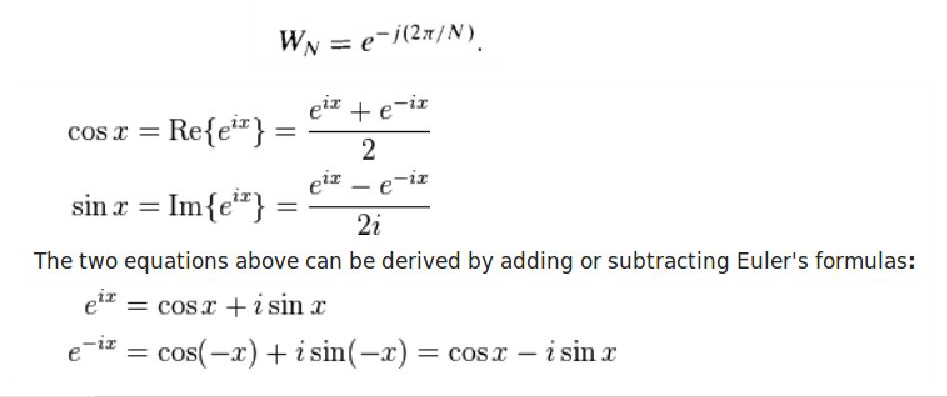

- Para se adequar ao HDL Coder, foi necessário utilizar a estratégia apresentada na figura 10:

O formato padrão de cálculo do Wn se dá por um e elevado a uma função de N, porém, os blocos disponíveis no HDL coder não suportam o uso de potências de funções. A solução para esse problema foi desmembrar a função Wn em cosseno e seno, além de utilizar equivalências da fórmula de euler, como descrito na figura 10.

Blocos - "{Wn^0 .. Wn^3}"

Dentro do Mwn existem 4 blocos responsáveis pelas potências de Wn (Wn^0, Wn^1, Wn^2, Wn^3).

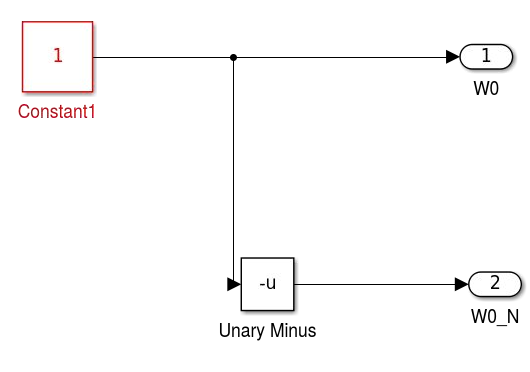

- Bloco Wn^0:

A estratégia menos custosa encontrada para resolver o cálculo de Wn^0 foi levar em consideração que qualquer número elevado a zero é igual a 1. Como descrito na imagem 12, percebe-se que o bloco em questão não possui entradas. Isso ocorre pelo mesmo motivo descrito anteriormente. Não importa qual o valor de Wn, já que o único valor possível será 1. O bloco possui 2 saídas: W0 e W0_N. O W0 corresponde ao Wn^0 original e o W0_N corresponde ao Wn^0 negado. Para calcular a parte negada, foi usado o bloco unary minus, que nada mais é do que um inversor.

Esquema interno Wn^0:

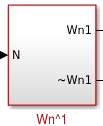

- Bloco Wn^1:

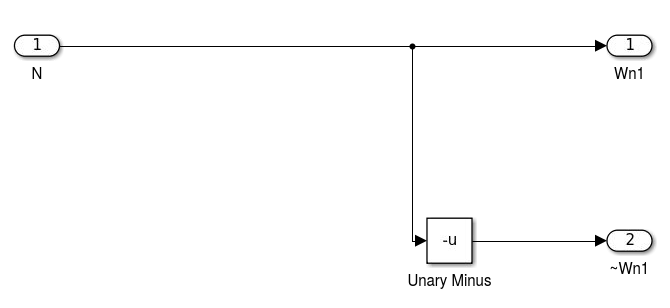

O bloco Wn^1 segue quase o mesmo esquema do Wn^0. O bloco possui 1 entrada que corresponde ao valor de Wn calculado no bloco Wn. Como esse bloco é Wn^1, sabemos que todo número elevado a 1 é igual a ele mesmo, portanto, o valor de Wn^1 será sempre ele mesmo. Assim como no bloco Wn^0, esse bloco possui 2 saídas: Wn1 e ~Wn1. Wn1 corresponde ao valor original de Wn^1 e ~Wn1 é o seu valor negado. Foi utilizado a mesma estratégia do unary minus. Se esquema é representado na figura 14.

Esquema interno Wn^1:

- Bloco Wn^2:

No bloco Wn^2 foi utilizada uma estratégia um pouco diferente dos blocos anteriores. Como já explanado anteriormente, o HDL coder não possui suporte para potências, portanto, o cálculo de Wn^2 necessita de algum estratégia para fazer essa potência. Sabemos que Wn^2 = Wn*Wn, logo, podemos utilizar a única entrada do bloco e conjunto com um bloco product para multiplicar a entrada N (que corresponde ao Wn calculado no bloco Wn) e obter o mesmo resultado de Wn^2. O bloco Wn^2 também possui 2 saídas: Wn2 e ~Wn2. Wn2 corresponde ao valor original de Wn^2 e ~Wn2 é o seu valor negado. Foi utilizado a mesma estratégia do unary minus. Seu esquema é representado na figura 16.

Esquema interno Wn^2:

- Bloco Wn^3:

O bloco Wn^3 possui uma estratégia para que seja poupado hardware. Sabemos que Wn^3 = Wn*Wn*Wn. Seria natural utilizar 2 blocos products para realizar essa operação, porém, podemos pegar a saída Wn2 e cascatear para esse bloco. Como Wn2 foi calculado como Wn*Wn, precisamos apenas fazer Wn2*Wn e iremos obter Wn3. Essa estratégia é descrita na figura 18. O bloco Wn^3 também possui 2 saídas: Wn3 e Wn3_N. Wn3 corresponde ao valor original de Wn^2 e Wn3_N é o seu valor negado. Foi utilizado a mesma estratégia do unary minus. Seu esquema é representado na figura 18.

Esquema interno Wn^3:

Viabilidade da implementação dos Modelos do projeto: INCENTIVANDO O USO DO SIMULINK NOS CURSOS DE TELECOMUNICAÇÕES

- Os blocos que possuem suporte para HDL estão em: Blocos Simulink com suporte HDL

| Modulações Analógicas (AM,FM,PM) | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| Amostragem de sinais | |||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| Quantização | |||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| Modulação por Codificação de Pulso (PCM) | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

{{Collapse bottom}

|

| Modulação por Amplitude de Pulso M-ária (PAM-M) | |||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| Transmissão digital em banda base | |||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| Modulações digitais binárias | ||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| Modulações digitais M-árias | |||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

| Transmissão digital em banda passante | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| Multipath Fading Channel | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| Digital Communications Ber Performance in AWGN or Fading | |||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| Orthogonal Frequency Multiplex Division (OFDM) | ||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Professor Orientador

Aluno bolsista

Características da Bolsa

O projeto será financiado com bolsa PIBITI do CNPq e será executado entre Agosto de 2015 e Julho de 2015.