DLP29007-2015-1

1 EngTel: Programmable Logic Devices II - 2015-1

- Lecturers: Arliones Hoeller e Marcos Moecke

- Class: 29007

- Meetings: tuesdays at 9:40 and thursdays at 7:30 at Laboratório de Programação.

- Extra-class hours:

- Arliones

- Tuesdays, 14:30 to 15:30

- Thursdays, 10:30 to 11:30

- Marcos

- Tuesdays, 13:30 to 14:30

- Thursdays, 10:30 to 11:30

- Arliones

1.1 Course Plan (in Portuguese)

1.2 Class Schedule

1.3 Grades

| Registration | T0 | T1 | T2 | T3 | T4 | T5 | Final |

|---|---|---|---|---|---|---|---|

2 Class Material

2.1 Bibliographic References

- Pong P. Chu, RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability. Wiley-IEEE Press, Hoboken, 2006, Pages 1-22, ISBN 0471720925.

- David Money Harris and Sarah L. Harris, Digital Design and Computer Architecture, Morgan Kaufmann, Burlington, 2007, Pages 3-48, ISBN 9780123704979, http://dx.doi.org/10.1016/B978-012370497-9/50002-0.

2.2 Lecture Notes

These lecture notes are based on the ones made available by Prof. Pong P. Chu at [1].

- Lecture 01: Complexity Mangement and the Design of Complex Digital Systems

- Lecture 02: Efficient Design of Combinational Circuits

- Lecture 03: Efficient Design of Sequential Circuits

- Lecture 04: Design of Sequential Circuits: Practice

- Lecture 05: Finite State Machines: Principle and Practice

- Lecture 06: Register Transfer Methodology: Principle

- Lecture 07: Register Transfer Methodology: Practice

- Lecture 08: Hierarchical Design

- [ Lecture 09: Parameterized Design: Principle]

- [ Lecture 10: Parameterized Design: Practice]

- [ Lecture 11: Clock and Synchronization: Principle and Practice]

2.3 Recursos de Laboratório

Para uso fora do IFSC dos recursos computacionais com licença educacional, o IFSC disponibiliza para seus alunos o IFSC-CLOUD. Atualmente a forma mais eficiente de acesso é através do Cliente X2GO. O procedimento de instalação/ configuração e uso do Quartus/Modelsim/QSIM está descrito em Acesso ao IFSC-CLOUD#Cliente X2GO (recomendado).

Para a geração de documentação/relatórios técnicos/artigos, está disponibilizada a plataforma Sharelatex do IFSC-CLOUD. Utilize preferencialmente o modelo de artigo no padrão ABNT.

2.4 Homework

| Homework 01: Combinational Circuits (Deadline: 19/02/2015) |

|---|

|

Download the Operator Sharing Source Code (qar) or Operator Sharing Source Code (qar.zip) and, for each architecture of each one of the three examples, do the following:

Write a report containing the numeric results of your experiments. For each example, answer the following questions:

Email the results to the professors until 17/02/2015. |

| Homework 02: Combinational Circuits (Deadline 26/02/2015) |

|---|

|

Download the Function Sharing Source Code (qar.zip) and, for each architecture of each one of the examples, do the following:

Write a report containing the numeric results of your experiments. For each example, answer the following questions:

Email the results to the professors until next class. |

| Homework 03: Combinational Circuits (Deadline: 03/03/2015) |

|---|

|

Groups of two students will study and explain to the class one of these circuits in Chapter 7 of bibliographic reference 1: 7.5.2 (Programmable Priority Encoder), 7.5.4 (Combinational Adder-Based Multiplier), 7.5.5 (Hamming Distance Circuit). |

| Homework 04: Synchronous Project - Timer (hour, minute, second) - (Deadline: 24/03/2015) |

|---|

create_clock -name CLK50MHz -period 20 [get_ports {clk}]

OR create_clock -name CLK50MHz -period 250MHz [get_ports {clk}]

|

| Homework 05: Sequential Circuits (Deadline: 26/03/2015) |

|---|

|

Each student will synthesize and analyze a counter, according to the list bellow.

Students must:

create_clock -name CLK250MHz -period 250MHz [get_ports {clk}]

|

| Homework 06: Finite State Mahines with Datapath (Deadline: 19/05/2015) |

|---|

|

In this homework you must produce a report in the format of an article. The article template can be downloaded here. The report will describe a lab experiment including the exercises from the Pong Chu book, enumerated bellow. You must simulate your designs to show that they work properly, and report differences in area and maximum clock among different designs. Don't forget to include the FSM/FSMD and/or ASM/ASMD in the report. When modifying a design shown in the book, compare the results with the original design. Exercises:

|

3 Class log

3.1 05/02: Course presentation. Complexity Management. Overview of Complex Digital Systems Desgin.

3.1.1 Recommended reading

- Chapter 1 of bibliographic references 1 AND 2.

- Lecture notes 1.

3.2 12/02 - 26/02: Design of efficient combinational circuits

3.2.1 Recommended reading

- Chapter 7 of bibliographic reference 1.

- Lecture notes 2.

- TimeQuest Help, mainly Propagation Delay Report.

3.3 12/02: Design of efficient combinational circuits: Operator sharing

3.3.1 Recommended reading

- Chapter 7 of bibliographic reference 1.

- Lecture notes 2.

3.4 19/02: Design of efficient combinational circuits: Function sharing

3.4.1 Recommended reading

- Chapter 7 of bibliographic reference 1.

- Lecture notes 2.

3.5 26/02: Design of efficient combinational circuits: Layout Considerations

3.5.1 Recommended reading

- Chapter 7 of bibliographic reference 1.

- Lecture notes 2.

3.6 03/03: Design of efficient combinational circuits: General Circuits

Students presented and discussed the general circuits of section 7.5 of bibliographic reference 1.

3.6.1 Recommended reading

- Chapter 7 of bibliographic reference 1.

- Lecture notes 2.

3.7 05/03: Design of efficient sequential circuits: principle

3.7.1 Recommended reading

- Chapter 8 of bibliographic reference 1.

- Lecture note 3.

3.8 12/03, 17/03, 26/03 and 31/03: Design of efficient sequential circuits: principle and practice

3.8.1 Recommended reading

- Chapter 8 of bibliographic reference 1.

- Chapter 9 of bibliographic reference 1.

- Lecture notes 3.

- Lecture notes 4.

- Quartus II help - create_clock - ALTERA

3.9 07/04, 09/04 and 16/04: Design of Efficient Finite State Machines: principle and practice

3.9.1 Recommended reading

- Chapter 10 of bibliographic reference 1.

- Lecture notes 5.

3.10 23/04: Register Transfer Methodology: Principle

3.10.1 Recommended reading

- Chapter 11 of bibliographic reference 1.

- Lecture notes 6.

3.11 11/06: Embedded Processors (SoC)

In this class we will follow an Altera tutorial to build a System-on-a-Chip (SoC), synthesizing a NIOS processor softcore in a FPGA and loading an OS on it. Later on we will integrate our own logic with this processor.

The guidelines to this tutorial are on this page.

You will need these additional components:

If the Eclipse SBT for Nios II does not start in your Ubuntu 14.04 system, you may need to install libGTK2:

sudo apt-get install libgtk2.0-0:i386

3.12 23/06: Final Project

3.12.1 Overview

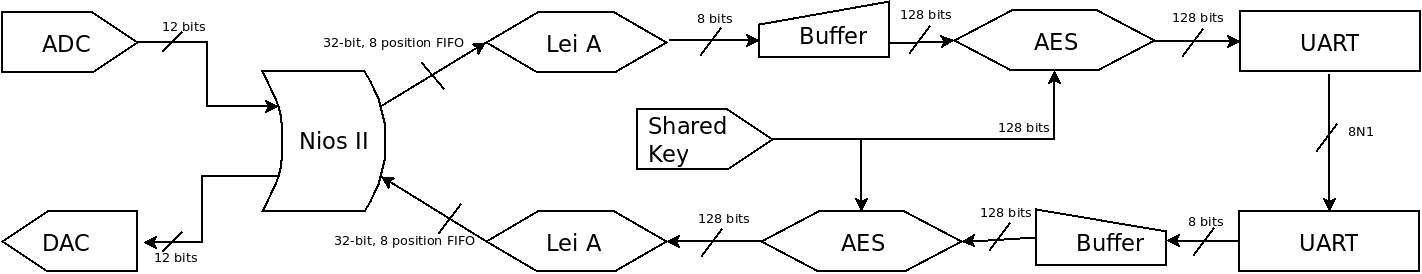

In this project you'll implement a secure audio transceiver using Macnica's Mercurio IV platform with an Cyclone IV E FPGA. A general overview is presented in the figure above, which is comprised of these blocks:

- Inputs

- in ADC: the ADC chip avaliable in the board. It is connected to the FPGA through an SPI interface, delivering a 12-bit decimal value.

- in Shared Key: a 128-bit shared key for the AES block cipher.

- out DAC: the DAC chip avaliable in the board. It is connected to the FPGA through an SPI interface, receiving a 12-bit decimal value.

- Processing blocks

- Nios II: The Nios II will act as SPI master to read data from the ADC and write data to the DAC. The software in the CPU will read data from the ADC at a 8KHz rate and insert the 12-bit values in an 8-position, 32-bit output FIFO. It will also read data from the input FIFO at an 8KHz rate and write it to the DAC. Note: you will only use the 12 LSB of FIFOs' entries.

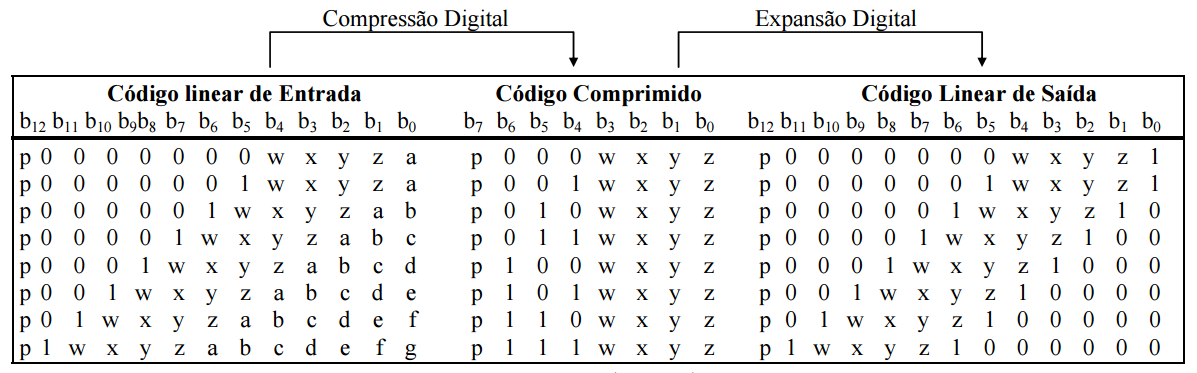

- Lei A: the LeiA block of the sending segment will read each 12-bit entry from the FIFO and generate a compressed 8-bit output. In the receive segment, the LeiA block will receive 8-bit values from the AES block and expand them to 12-bit values.

- AES: The data will be encrypted using an AES-128 algorithm. In the transmission segment, the AES block will need to receive successive 8-bit results from the LeiA block and assembly a 128-bit block to input the cipher. In the receive segment, the AES block will receive successive 8-bit data from the UART block to assembly a 128-bit block to input to the decrypt algorithm.

- UART: data transmission will be performed through an UART interface connected to an RS-232 transceiver in the board. The UART receiver and transmitter must be extended from the UART receiver studied in class to include the transceiver and the RTS and CTS signals.

- The following files are avaliable to integrate to your project:

- Download here a QAR File containing the ADC and DAC adaptation circuit and a Nios2 processor. From this file, you will use a the ADC_OUT FIFO as a data source to your LawA compressor, and the DAC_IN FIFO as a data destination for your LawA decompressor.

- Download here the ecliplse project of the application that should run on the Nios2 processor. You will need to generate the BSP (sopcinfo file is in the QAR).

3.12.2 Material de apoio para o projeto

- Conversores Analógico-Digital (CAD) e Conversor Digital-Analógico (CDA)

- Implementação de um codificador/decodificador para Lei A.

- Implementação de uma Interface Serial Assíncrona.

3.13 25/06: Final Project

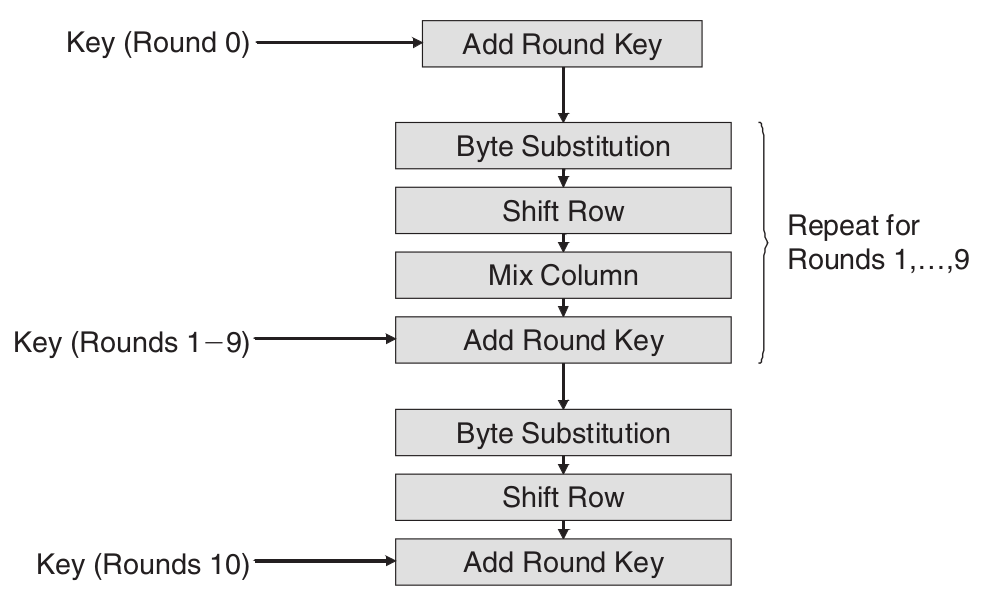

- Implementation of VHDL description of an AES 128 cypher operating with 128-bit keys and 128-bit data blocks.

- See this article for the description of the algorithm;

- Read printed book segment handed on to you in class.

- Check out these software implementations that may help you with the Register Transfer Methodology to implement AES. The software in Python is a high-level implementation (easy to understand). The C++ implementations are Object-Oriented and easy to integrate in software projects, but their code show several tweaks to make it faster in x86 machines with ssse3 instructions, or certain DSP devices (only recommended for those with a strong heart).