Mudanças entre as edições de "SST20707-2014-1"

| Linha 510: | Linha 510: | ||

**Para as demais operações, a leitura do segundo operando é realizada em um estado adicional - Enable_1 e Enable_2 precisam ser devidamente controlados em cada estado.Para essas operações, quando o Enter for pressionado pela segunda vez (Key(1) = ‘0’), o resultado é escrito nos registradores de saída (Enable_1=‘1’), e a FSM retorna para o estado inicial “Esperando”. | **Para as demais operações, a leitura do segundo operando é realizada em um estado adicional - Enable_1 e Enable_2 precisam ser devidamente controlados em cada estado.Para essas operações, quando o Enter for pressionado pela segunda vez (Key(1) = ‘0’), o resultado é escrito nos registradores de saída (Enable_1=‘1’), e a FSM retorna para o estado inicial “Esperando”. | ||

| − | = | + | = 30/06: 2ª Avaliação e 1ª Recuperação= |

| + | |||

| + | Utilizando os conceitos de máquinas de estado, projete um circuito que analisa a senha de 3 dígitos (ex.: 306) para um controle de acesso. | ||

| + | |||

| + | [[imagem:senha.png|400px|center]] | ||

| + | |||

| + | *Obs.: | ||

| + | **Tecla: Valor BCD de 0-9 e 15 para não pressionado. | ||

| + | **Reset, Libera e Espera: Ativo em 1. | ||

| + | **Intervalo de tempo máximo entre toques das teclas é 3 ciclos de clock. | ||

| + | **Intervalo de tempo do sinal libera é 5 ciclos de clock. | ||

| + | |||

| + | *Entrega: | ||

| + | **Desenho máquina de estado | ||

| + | **Arquivo *.vhd da FSM | ||

| + | **Arquivo *.do testando a FSM | ||

| + | |||

| + | '''Recuperação:''' | ||

| + | *Implementar o topo conforme o imagem abaixo e modificar o decodificador para mostrar de 0-9 e '–' para outro valor BCD. | ||

| + | |||

| + | [[imagem:senha-topo.png|600px|center]] | ||

Edição das 15h46min de 30 de junho de 2014

Síntese de Sistemas de Telecomunicações: Diário de Aula 2014-1

Professor: Roberto de Matos

Encontros: 2ª e 3ª feira às 13:30

Atendimento paralelo: 2ª feira das 15:40 às 17:30.

Assuntos trabalhados

- Introdução aos dispositivos lógicos programáveis

- Introdução à tecnologia FPGA

- Introdução a linguagem VHDL

Apoio Desenvolvimento

Slides

- Slides de Introdução

- Fluxo de Projeto Quartus

- Introdução à Linguagem VHDL

- Componentes em VHDL

- Mux e Decode

- Circuitos Seqüênciais

- Máquinas de Estado

10/02: Apresentação

- Apresentação do professor.

- Apresentação dos alunos: Nome, perfil, preferências, etc.

- Apresentação da disciplina: conteúdo, bibliografia e avaliação.

- Aula Introdutória:

- Por que dispositivos lógicos programáveis?

- Histórico

11/02: Desenvolvimento com PLDs

- Famílias de Componentes Lógicos Programáveis

- Arquitetura dos FPGAS

- Introdução ao Fluxo de Projeto do Quartus

17/02: Laboratório Quartus

- Fluxo de projeto esquemáticos com Quartus e Modelsim (Porta AND)

- Exercício: Projeto, Simulação e Teste do meio-somador

18/02: Introdução à Linguagem VHDL

- Finalização do fluxo de projeto do Meio somador no Quartus e Modelsim, utilização a entrada de esquemático.

- Apresentação da Linguagem VHDL

- Conceitos de entidade (entity) e arquitetura (architecture)

24/02: Linguagem VHDL

Exemplos VHDL (Entity e Architecture)

- Meio Somador

- LCD and Switch

Componentes (COMPONENT, PORT MAP)

- Sintaxe Simplificada:

--Declaração---------------------------------------------------------- COMPONENT component_name [IS] [GENERIC ( const_name: const_type := const_value; ...);] PORT ( port_name: port_mode signal_type; ...); END COMPONENT [component_name]; --Instanciação---------------------------------------------------------- label: [COMPONENT] component_name [GENERIC MAP (generic_list) ] PORT MAP (port_list);

- Exemplo:

--Declaração----------------------------------------------------------

COMPONENT nand_gate IS

PORT ( a, b: IN STD_LOGIC;

c: OUT STD_LOGIC);

END COMPONENT;

--Instanciação---------------------------------------------------------

nand1: nand_gate PORT MAP (x, y, z); --mapeamento posicional

nand2: nand_gate PORT MAP (a=>x, b=>y, c=>z); --mapeamento nominal

</syntaxhighlight>

- Exemplo GENERIC:

--Declaração----------------------------------------------------------

COMPONENT xor_gate IS

GENERIC (N: INTEGER := 8);

PORT ( a: IN STD_LOGIC(1 TO N);

b: OUT STD_LOGIC);

END COMPONENT;

--Instanciação----------------------------------------------------------

xor1: xor_gate GENERIC MAP (16) PORT MAP (x, y); --map. posicional

xor2: xor_gate GENERIC MAP (N=>16) PORT MAP (a=>x, b=>y); --map. nominal

</syntaxhighlight>

10/03: Código Concorrente (WHEN, SELECT)

WHEN

- Sintaxe Simplificada:

signal_name <=

value_expr_1 when boolean_expr_1 else

value_expr_2 when boolean_expr_2 else

value_expr_3 when boolean_expr_3 else

...

value_expr_n

</syntaxhighlight>

- Exemplo:

x <= a when (s="00") else

b when (s="01") else

c when (s="10") else

d;

</syntaxhighlight>

SELECT

- Sintaxe Simplificada:

with select_expression select

signal_name <= value_expr_1 when choice_1,

value_expr_2 when choice_2,

value_expr_3 when choice_3,

...

value_expr_n when choice_n;

</syntaxhighlight>

- Exemplo:

with s select

x <= "0001" when "00",

"0010" when "01",

"0011" when "10",

"0100" when others;

</syntaxhighlight>

Exercícios

- Implementação MUX comportamental e estrtural

- Verificação

17/03: Exercícios: Decode 7-seg e UPC

Decode 7-seg

- Implementação Decode IFSC:

entity decodIFSC is

port (C: in std_logic_vector(2 downto 0);

F: out std_logic_vector(6 downto 0)

);

end decodIFSC;

architecture decod_bhv of decodIFSC is

Begin

with C select

F <= "1001111" when "000", -- I

"0001110" when "001", -- F

"0010010" when "010", -- S

"1000110" when "011", -- C

"1111111" when others;

end decod_bhv;

</syntaxhighlight>

- "Virtual Function" em arquivo *.do:

vlib work

vcom -93 -work work {../../decodIFSC.vhd}

vsim work.decodifsc

virtual type {{0b1001111 seg_I} {0b0001110 seg_F} {0b0010010 seg_S} {0b1000110 seg_C} {0b1111111 seg_others}} d7seg_ifsc_type

virtual function {(d7seg_ifsc_type)/decodIFSC/F} display_virtual

add wave -position end sim:/decodifsc/C

add wave -position end sim:/decodifsc/F

add wave display_virtual

force -freeze sim:/decodifsc/C 000 0

run

force -freeze sim:/decodifsc/C 001 0

run

force -freeze sim:/decodifsc/C 010 0

run

force -freeze sim:/decodifsc/C 011 0

run

force -freeze sim:/decodifsc/C 100 0

run

</syntaxhighlight>

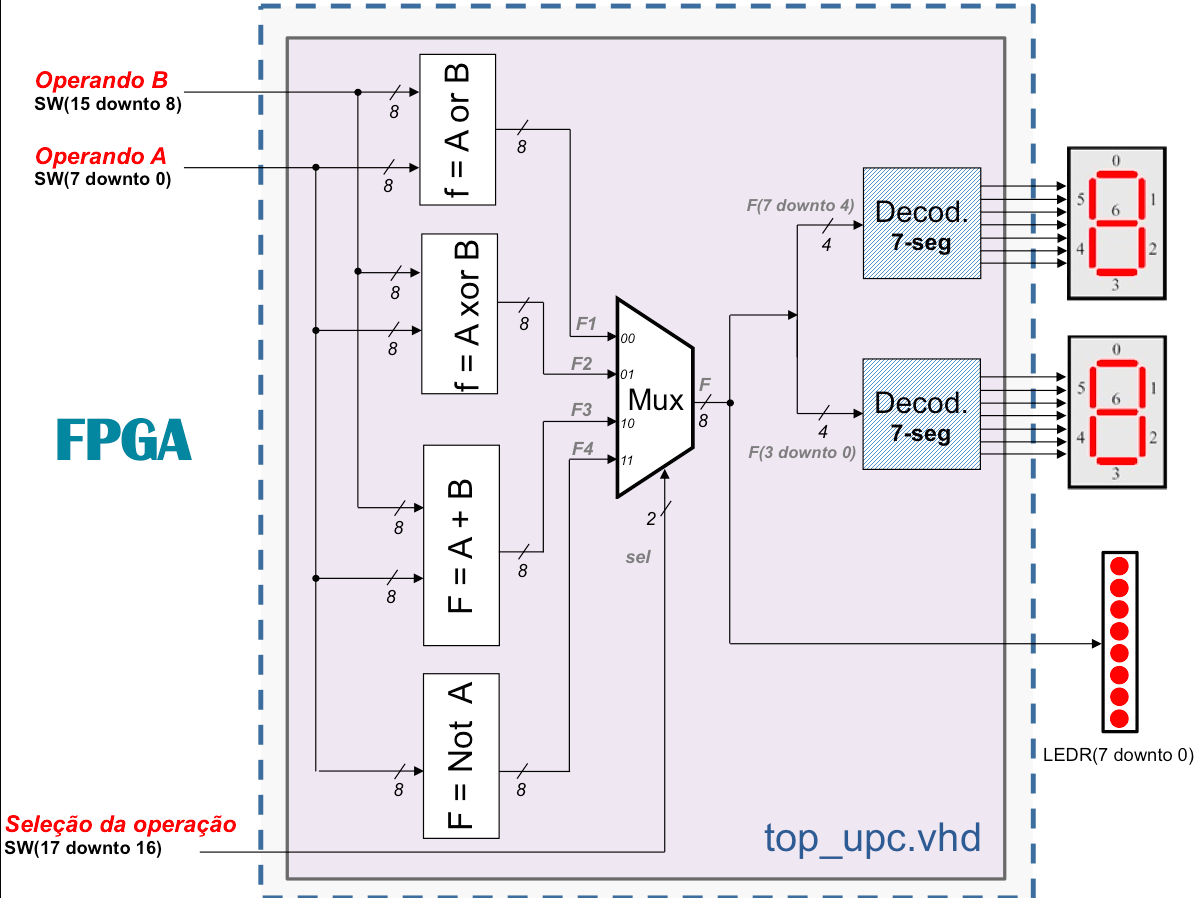

UPC: Unidade de Processamento Combinacional

24/03: Exercícios (cont.)

31/03: Não Houve Aula - Reunião Inova Telecom

07/04: Prova Combinacional

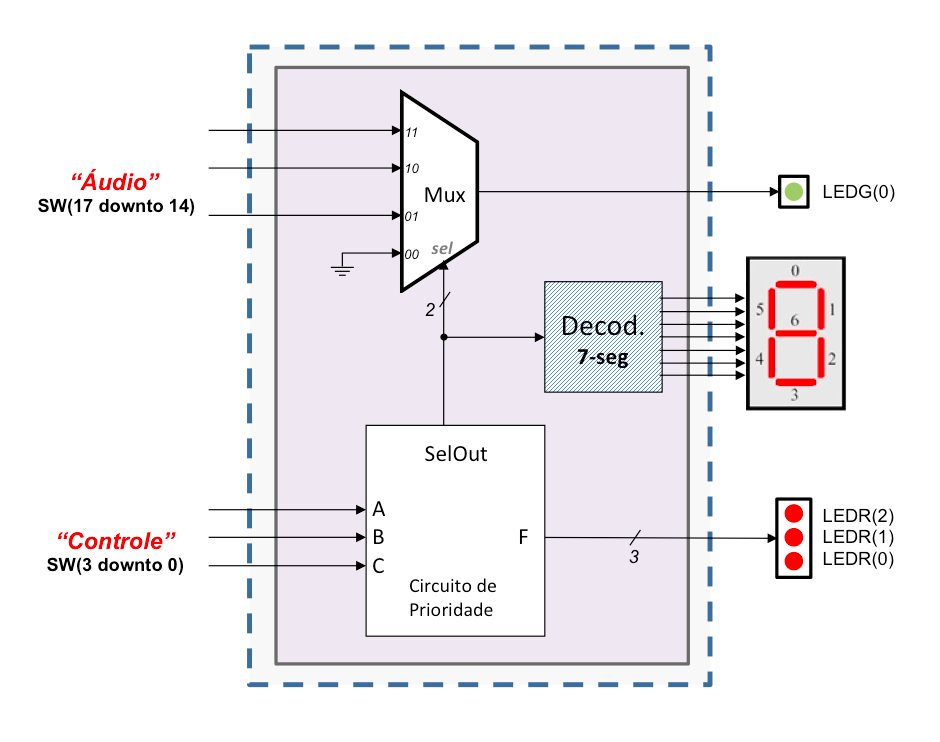

Desenvolver um projeto hierárquico com módulos em VHDL que implemente o circuito abaixo. Esse circuito controla 3 canais de áudio com prioridade. Os canais de áudio são “simulados” por chaves. A ordem decrescente de prioridade das entradas é A, B e C. O bloco de prioridade deve selecionar (SelOut) corretamente a entrada do MUX que deve ser chavetada para saída. Além disso, a saída F deve mostrar nos LEDs a saída selecionada. O decodificador de 7 segmentos deve decodificar a saída SelOut e mostrar no display “A”, “b” ou “C”, dependendo da saída selecionada.

Todos os módulos devem ter arquivos de teste (*.do), inclusive o topo. O teste do decodificador deve incluir um “virtual type” para simplificar a simulação.

CESUP

14/04: Introdução ao Código Seqüencial

- Seqüencial vs. Combinacional

- Exemplo Flip-Flop RS

- Lista de Sensibilidade

- Exercícios:

- UPC com Registradores

- Exemplo:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity test_proc is

port(

data_in : in std_logic;

data_out: out std_logic

);

end test_proc;

architecture circuit of test_proc is

signal A,B,C,D: std_logic;

begin

A <= data_in;

data_out <= D;

--Version 1 --Version 2

process(A) --process (A,C)

begin

B <= A;

B <= '0';

C <= A and '1';

C <= not A;

D <= C;

end process;

end circuit;

</syntaxhighlight>

- Lista de Sensibilidade (reentrada no process)

- test_proc.vhd (não funciona no Quartus):

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity test_proc is

port(

data_in : in std_logic;

data_out: out std_logic

);

end test_proc;

architecture circuit of test_proc is

signal A,B,C,D: std_logic;

begin

A <= data_in;

data_out <= D;

process

begin

wait on A,C;

if A'event then

wait for 1 ns;

elsif C'event then

wait for 3 ns;

end if;

B <= A;

B <= '0';

C <= A and '1';

C <= not A;

D <= C;

end process;

end circuit;

</syntaxhighlight>

- test.do:

vlib work

vcom -93 -work work {test_proc.vhd}

vsim work.test_proc

add wave -noupdate /test_proc/data_in

add wave -noupdate /test_proc/A

add wave -noupdate /test_proc/B

add wave -noupdate /test_proc/C

add wave -noupdate /test_proc/D

add wave -noupdate /test_proc/data_out

force -freeze sim:/test_proc/data_in 0 @10ns,1 @20ns,0 @30ns

run 40ns

</syntaxhighlight>

21/04: Não houve Aula – Feriado Tiradentes

28/04: Não houve Aula – Inova Telecom

05/05: Código Seqüencial

- Conceito de Variável

- Variável vs. Signal

- Estruturas de Controle

- Exercícios:

- Contador até 10

- Temporizador 60 segundos

Variável vs. Sinal

library ieee;

use ieee.std_logic_1164.all;

entity sig_var is

port( d1: in std_logic;

res1, res2: out std_logic);

end sig_var;

architecture behv of sig_var is

signal sig_s1: std_logic;

begin

proc1: process(d1)

variable var_s1: std_logic;

begin

var_s1 := d1;

res1 <= var_s1;

end process;

proc2: process(d1)

begin

sig_s1 <= d1;

res2 <= sig_s1;

end process;

end behv;

</syntaxhighlight>

Estruturas de Controle

IF

- Sintaxe Simplificada:

[ label: ] if condition1 then

sequence-of-statements

elsif condition2 then \_ optional

sequence-of-statements /

elsif condition3 then \_ optional

sequence-of-statements /

...

else \_ optional

sequence-of-statements /

end if [ label ] ;

</syntaxhighlight>

- Exemplo:

if a=b then

c:=a;

elsif b<c then

d:=b;

b:=c;

else

do_it;

end if;

</syntaxhighlight>

LOOP

- Sintaxe Simplificada:

[ label: ] loop

sequence-of-statements -- use "exit statement" or "next statement"

end loop [ label ] ;

[ label: ] for variable in range loop

sequence-of-statements

end loop [ label ] ;

[ label: ] while condition loop

sequence-of-statements

end loop [ label ] ;

</syntaxhighlight>

- Exemplo:

loop

input_something;

exit when end_file;

end loop;

for I in 1 to 10 loop

AA(I) := 0;

end loop;

while not end_test loop

input_something;

end loop;

</syntaxhighlight>

CASE

- Sintaxe Simplificada:

[ label: ] case expression is

when choice1 =>

sequence-of-statements

when choice2 => \_ optional

sequence-of-statements /

...

when others => \_ optional if all choices covered

sequence-of-statements /

end case [ label ] ;

</syntaxhighlight>

- Exemplo:

case my_val is

when 1 =>

a:=b;

when 3 =>

c:=d;

do_it;

when others =>

null;

end case;

</syntaxhighlight>

26/05: Introdução a FSM

- Introdução a máquina de estado:

- Estado

- Transição

- Ação

- Estrutura de máquinas de estado

- Técnicas de implementação (1, 2 e 3 processos)

- Exercício de simulação de uma FSM

02/06: Continuação exercícios FSM

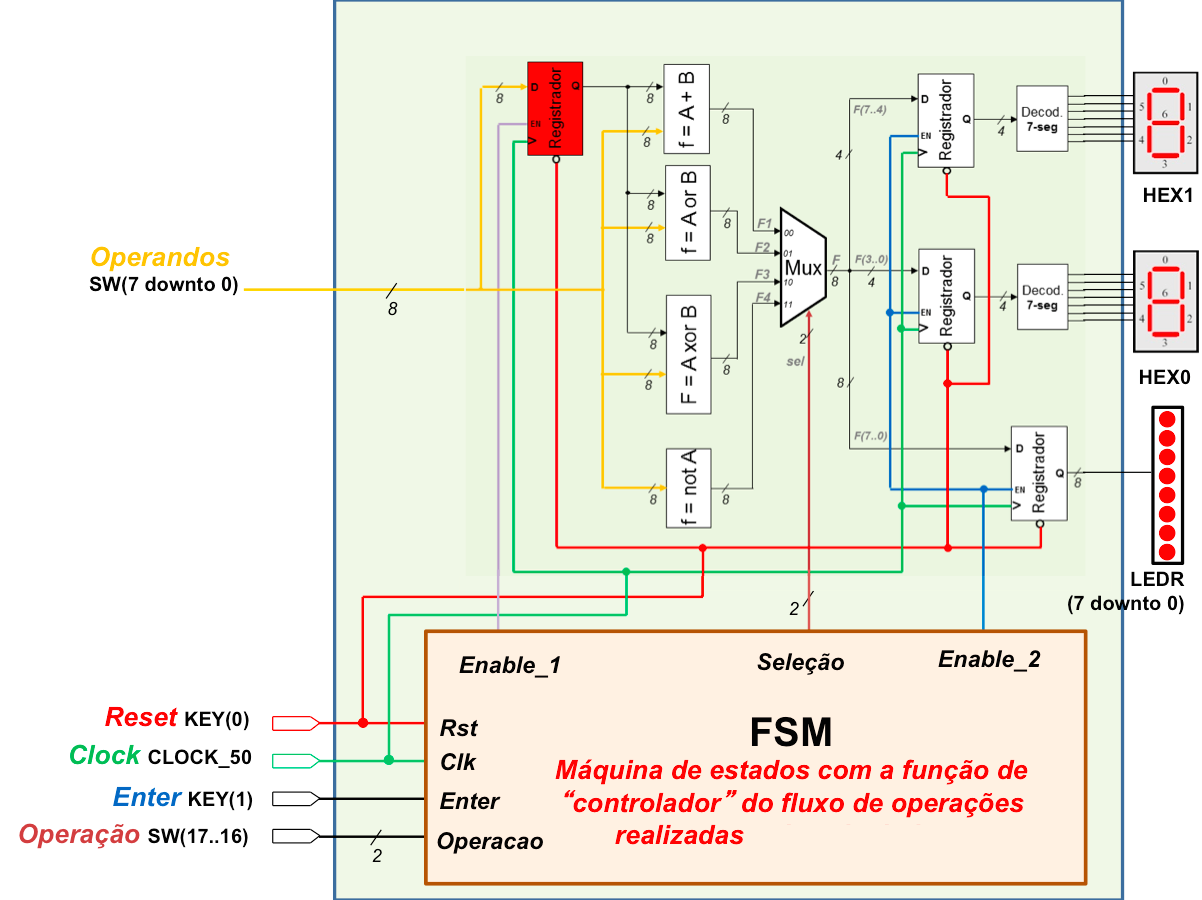

24/06: Exercício UPC Sequencial

Objetivo

Reduzir a quantidade de chaves no projeto combinacional da primeira avaliação, utilizando apenas um conjunto de 8 chaves, SW(7..0), para leitura dos dois operandos. A UPC terá o seguinte funcionamento:

- Definir a operação (SW(17..16))

- Entrar com o primeiro operando (SW(7..0)), pressionar Enter

- Entrar com o segundo operando (SW(7..0)), pressionar Enter (somente para as operações "soma", "xor ou "or")

- Mostrar o valor da operação

A partir do objetivo geral, temos o seguintes objetivos específicos:

- Implementar um registrador de tamanho genérico;

- Adicionar um registrador para armazenar o primeiro operando;

- Adicionar registradores para armazenar o resultado das operações;

- Implementar e adicionar uma máquina de estado (FSM) para fazer o controle como descrito abaixo.

- A FSM terá o seguinte funcionamento:

- No estado inicial, “Esperando”, as saídas da FSM estão desabilitadas (Enable_1=‘0’, Enable_2=‘0’, Selecao=“XX”). Isso garante que nenhuma atividade ocorrerá na calculadora, enquanto o usuário não fornecer os operandos e a operação.

- Quando Enter (Key(1)) for ‘0’, a FSM avança para o próximo estado, para aguardar até o Enter voltar para ‘1’ (botão “não pressionado”).

- No estado “Operação” é realizada uma transição para o próximo estado, de acordo com a operação selecionada.

- Se a operação for “ID” (de apenas um operando), a operação é realizada, o resultado é armazenado no registrador de saída (Enable_2=‘1’) e a FSM retorna para o estado inicial “Esperando”.

- Para as demais operações, a leitura do segundo operando é realizada em um estado adicional - Enable_1 e Enable_2 precisam ser devidamente controlados em cada estado.Para essas operações, quando o Enter for pressionado pela segunda vez (Key(1) = ‘0’), o resultado é escrito nos registradores de saída (Enable_1=‘1’), e a FSM retorna para o estado inicial “Esperando”.

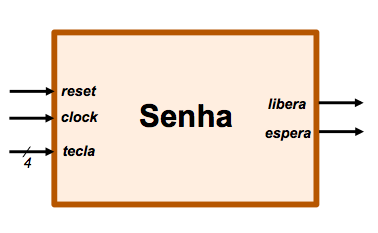

30/06: 2ª Avaliação e 1ª Recuperação

Utilizando os conceitos de máquinas de estado, projete um circuito que analisa a senha de 3 dígitos (ex.: 306) para um controle de acesso.

- Obs.:

- Tecla: Valor BCD de 0-9 e 15 para não pressionado.

- Reset, Libera e Espera: Ativo em 1.

- Intervalo de tempo máximo entre toques das teclas é 3 ciclos de clock.

- Intervalo de tempo do sinal libera é 5 ciclos de clock.

- Entrega:

- Desenho máquina de estado

- Arquivo *.vhd da FSM

- Arquivo *.do testando a FSM

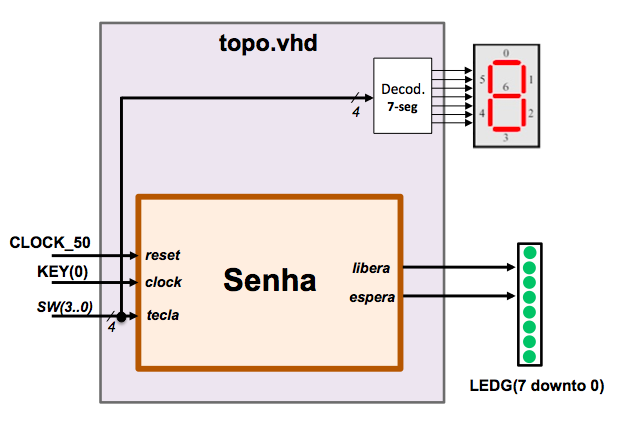

Recuperação:

- Implementar o topo conforme o imagem abaixo e modificar o decodificador para mostrar de 0-9 e '–' para outro valor BCD.