Mudanças entre as edições de "Preparando para gravar o circuito lógico no FPGA"

| Linha 1: | Linha 1: | ||

| + | ==Escolha do kit com o FPGA== | ||

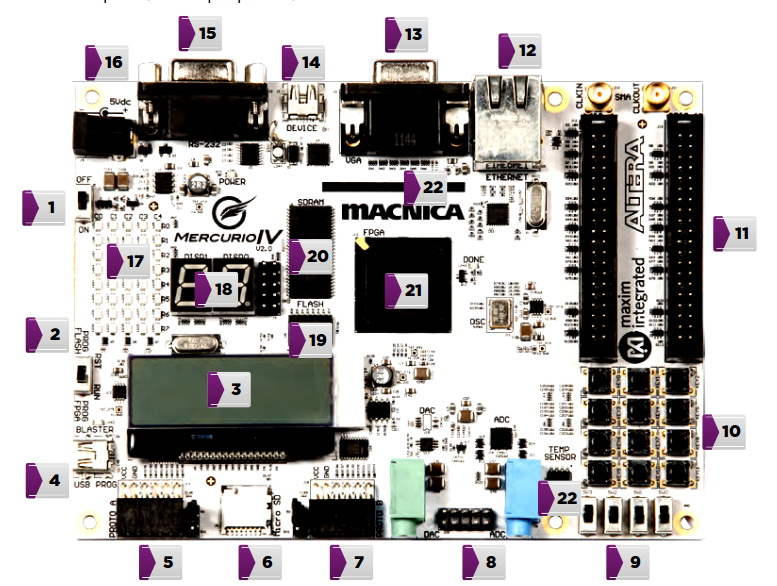

| + | *Para realizar a implementação do sistema digital em um FPGA, os fabricantes de chips disponibilizam kits de desenvolvimento/educacionais nos quais além do FPGA componentes periféricos diversos estão disponíveis para o desenvolvedor. Entre as caracteristicas comuns desses kits está a presença de: Leds, Chaves, Displays, Conectores ligados diretamente a um conjunto de pinos do chip FPGA, entre outros. Para conhecer a característica de cada kit, recomenda-se que o desenvolvedor analise o manual do fabricante. | ||

| + | |||

| + | O IFSC dispõe de alguns kits que podem ser utilizados pelos professores/alunos, cujo uso é destinado prioritariamente para as disciplinas dos cursos técnico e de engenharia de telecomunicações. | ||

| + | ;Kits disponíveis: | ||

| + | *10 DE2-115 - ALTERA | ||

| + | *4 DE0-Nano - ALTERA | ||

| + | *2 DE5 - ALTERA | ||

| + | *20 Mercurio IV - MACNICA | ||

| + | |||

| + | Após escolher o kit, deverá ser feita a atribuição da pinagem do FPGA conforme as conexões previamente existentes no kit escolhido. A pinagem de cada kit pode ser encontrada nos respectivos manuais. Para facilitar a configuração da pinagem mais utilizada consulte a página correspondente a seguir: | ||

| + | {| class="wikitable" border="1" cellpadding="3" cellspacing="0" style="text-align:left; font-size:100%" bgcolor="#efefef" | ||

| + | ! scope="col" width=50% align="center" | Kit | ||

| + | ! scope="col" width=10% align="center" | Fabricante | ||

| + | ! scope="col" width=10% align="center" | Site | ||

| + | ! scope="col" width=10% align="center" | Manual | ||

| + | ! scope="col" width=10% align="center" | Arquivo qsf | ||

| + | ! scope="col" width=10% align="center" | Pinagem do kit | ||

| + | |||

| + | |- | ||

| + | | DE0-Nano | ||

| + | | align="center" | TERASIC | ||

| + | | align="center" | [http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=165&No=593&PartNo=1] | ||

| + | | align="center" | [[Media:ManualDE0Nano.pdf]] | ||

| + | | align="center" | [[Media:qsfDE0Nano.qsf]] | ||

| + | | align="center" | [[Pinagem do kit DE0-Nano]] | ||

| + | |- | ||

| + | | DE2-115 | ||

| + | | align="center" | TERASIC | ||

| + | | align="center" | [http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&No=502] | ||

| + | | align="center" | [[Media:ManualDE2-115.pdf]] | ||

| + | | align="center" | [[Media:qsfDE2-115.qsf]] | ||

| + | | align="center" | [[Pinagem do kit DE2-115]] | ||

| + | |- | ||

| + | | C5GT - Cyclone V GT FPGA Development Kit | ||

| + | | align="center" | TERASIC | ||

| + | | align="center" | [http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=165&No=843] | ||

| + | | align="center" | [[Media:ManualC5GT.pdf]] | ||

| + | | align="center" | [[Media:qsfC5GT.qsf]] | ||

| + | | align="center" | [[Pinagem do kit C5GT]] | ||

| + | |- | ||

| + | | MERCÚRIO IV | ||

| + | | align="center" | MACNICA | ||

| + | | align="center" | [http://www.macnicadhw.com.br/products/mercurion-4-devkit-board;jsessionid=D98DEAF9F3E3E352079DB96CED5C4096] | ||

| + | | align="center" | 88.46% | ||

| + | | align="center" | | ||

| + | |} | ||

| + | |||

| + | |||

| + | == | ||

| + | |||

*[[Configuração da USB para programação do FPGA via JTAG]] | *[[Configuração da USB para programação do FPGA via JTAG]] | ||

| Linha 46: | Linha 97: | ||

*[[Software e equipamentos recomendados para programação de FPGAs]] | *[[Software e equipamentos recomendados para programação de FPGAs]] | ||

| + | |||

| + | *[ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/] | ||

Edição das 15h57min de 10 de março de 2015

Escolha do kit com o FPGA

- Para realizar a implementação do sistema digital em um FPGA, os fabricantes de chips disponibilizam kits de desenvolvimento/educacionais nos quais além do FPGA componentes periféricos diversos estão disponíveis para o desenvolvedor. Entre as caracteristicas comuns desses kits está a presença de: Leds, Chaves, Displays, Conectores ligados diretamente a um conjunto de pinos do chip FPGA, entre outros. Para conhecer a característica de cada kit, recomenda-se que o desenvolvedor analise o manual do fabricante.

O IFSC dispõe de alguns kits que podem ser utilizados pelos professores/alunos, cujo uso é destinado prioritariamente para as disciplinas dos cursos técnico e de engenharia de telecomunicações.

- Kits disponíveis

- 10 DE2-115 - ALTERA

- 4 DE0-Nano - ALTERA

- 2 DE5 - ALTERA

- 20 Mercurio IV - MACNICA

Após escolher o kit, deverá ser feita a atribuição da pinagem do FPGA conforme as conexões previamente existentes no kit escolhido. A pinagem de cada kit pode ser encontrada nos respectivos manuais. Para facilitar a configuração da pinagem mais utilizada consulte a página correspondente a seguir:

| Kit | Fabricante | Site | Manual | Arquivo qsf | Pinagem do kit |

|---|---|---|---|---|---|

| DE0-Nano | TERASIC | [1] | Media:ManualDE0Nano.pdf | Media:qsfDE0Nano.qsf | Pinagem do kit DE0-Nano |

| DE2-115 | TERASIC | [2] | Media:ManualDE2-115.pdf | Media:qsfDE2-115.qsf | Pinagem do kit DE2-115 |

| C5GT - Cyclone V GT FPGA Development Kit | TERASIC | [3] | Media:ManualC5GT.pdf | Media:qsfC5GT.qsf | Pinagem do kit C5GT |

| MERCÚRIO IV | MACNICA | [4] | 88.46% |

==

Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit DE0-Nano.

- Mude a família e dispositivo a ser usado (Assignments > Devices), [Family = Cyclone IV E] e selecione EP4CE22F17C6

- Para ver as pinagens completa das Interfaces de entrada e saída da DE2-115 no Manual.

- Pinagem dos dispositivos de entrada e saída do kit MERCURIO IV Manual - MERCURIO IV.

- pinagem do kit DE0-Nano

- pinagem do kit DSP

- Atribua os pinos conforme a necessidade do projeto

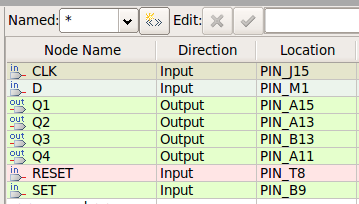

- Ao final da configuração dos pinos, o Pin Planner deverá mostrar a seguinte pinagem:

- Exemplo de atribuição de pinagem

- Defina como alta impedância o estado dos pinos não utilizados no projeto. [Assignments > Devices > Device and Pin Options... > Category:Unused Pins > Reserve all unused pins: [As input tri-stated] > OK].

- Compile o projeto.

Preparando para gravar o circuito lógico no FPGA

Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit MERCURIO IV.

- Mude a família e dispositivo a ser usado (Assignments > Devices), [Family = Cyclone IV E] e selecione EP4CE30F23C7.

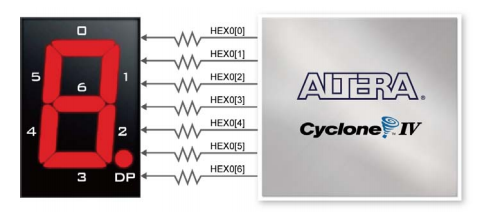

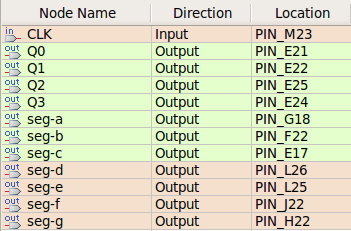

- Utilize o display HEX0 do kit para mostrar a contagem:

- Utilize os leds de LED0 a LED3 (verdes) para mostrar a contagem em binário.

- Utilize a chave KEY0 para gerar o sinal de CLK.

- Atribua os pinos conforme a pinagem do kit MERCURIO IV.

- Ao final da configuração dos pinos, o Pin Planner deverá mostrar a seguinte pinagem:

- Defina como alta impedância o estado dos pinos não utilizados no projeto. (Assignments > Devices), [Device and Pin Options...], escolha a (Category=Unused Pins), e selecione Reserve all unused pins: As input tri-stated. [OK].

- Compile o projeto. Note que agora a numeração dos pinos também aparece no diagrama esquemático.