Mudanças entre as edições de "Predefinição:DiegoMedeiros-SST20707"

(→ENTITY) |

|||

| Linha 509: | Linha 509: | ||

Duas '''LIBRARYs''' disponibilizadas automaticamente: | Duas '''LIBRARYs''' disponibilizadas automaticamente: | ||

| + | |||

* '''STD''': tipos básicos de dados: | * '''STD''': tipos básicos de dados: | ||

| Linha 529: | Linha 530: | ||

:* TIME: Valores com unidades de tempo (ps, ms, min, hr) | :* TIME: Valores com unidades de tempo (ps, ms, min, hr) | ||

:* REAL: Número de ponto flutuante de precisão dupla | :* REAL: Número de ponto flutuante de precisão dupla | ||

| + | |||

* '''WORK''': indica onde estão armazenados os arquivos do projeto | * '''WORK''': indica onde estão armazenados os arquivos do projeto | ||

| + | |||

Um pacote frequentemente incluído é '''STD_LOGIC_1164''', da '''LIBRARY IEEE''', que define os tipos: | Um pacote frequentemente incluído é '''STD_LOGIC_1164''', da '''LIBRARY IEEE''', que define os tipos: | ||

Edição das 13h09min de 27 de fevereiro de 2015

Ementa e referências bibliográficas

Informações da disciplina

- Professor: Diego da Silva de Medeiros

- Plano de Ensino 2015-1

Diário de aula

| 2015-1 - Clicar no "+" para expandir | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||

Aulas

Apresentação da disciplina

- Roteiro

- Apresentação do professor;

- Apresentação da disciplina (Plano de Ensino);

- Avaliações: Trabalhos e Projeto Final

- Grupo da disciplina: IFSCTeleSST

- Atividade

- Ler capítulo 18 do Livro do Pedroni

Dispositivos lógicos programáveis - PLD

PLDs em sistemas digitais

Sistema digital: Saída digital definida em função de processamento realizado em entrada digital.

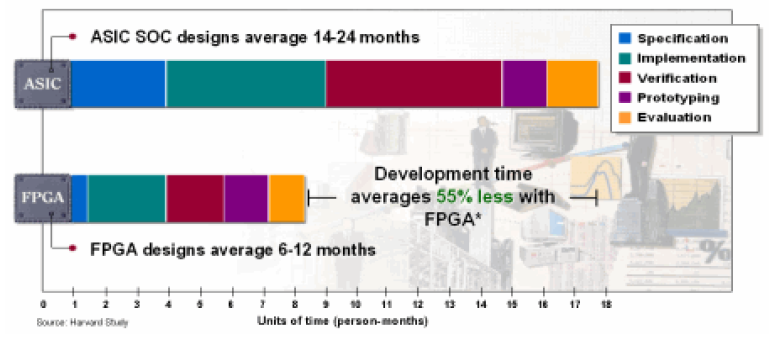

Os sistemas digitais foram por muito tempo projetados usando a chamada lógica fixa, composta por CIs (circuitos integrados) TTL que implementavam portas lógicas. Em meados de 1970, foram introduzidos os PLDs (Programmable Logic Devices), chips de uso geral cujo hardware pode ser configurado para atender especificações. Com os PLDs, sistemas digitais poderiam ser projetados a partir de CIs genéricos, com funções definidas a partir de configurações armazenadas em memórias. Desta forma, os PLDs possuem as seguintes vantagens sobre sistemas de lógica fixa [2]:

- Redução de custos de projeto, chamados de custos NRE (nonrecurring engineering cost - custo de engenharia não recorrente), com a abolição de desenvolvimentos complexos de placas

- Rapidez de desenvolvimento

- Flexibilidade no desenvolvimento: a adição de funcionalidades é feita por simples mudanças no arquivo de configuração

- Rapidez de produção do CI: por serem padronizados, os PLDs possuem entrega imediata

- Atualização de hardware em tempo real

Uma alternativa de projeto é o uso de microcontroladores, dispositivos programáveis a nível de software. Porém, mesmo nesses casos, os PLDs possuem vantagens [3]:

- PLDs são mais simples de desenvolver, pois alterações no projeto são feitas instantaneamente

- Sistemas com processadores customizados possuem desenvolvimento lento e oneroso

- Sistemas mais genéricos tendem a ter custos menores pela possibilidade de uso em diversas aplicações, facilitando o estoque de itens

Em função da arquitetura e tecnologia empregada, os PLDs foram classificados em SPLDs (simple PLDs) ou CPLDs (complex PLDs).

SPLDs

São denominados SPLDs os seguintes dispositivos:

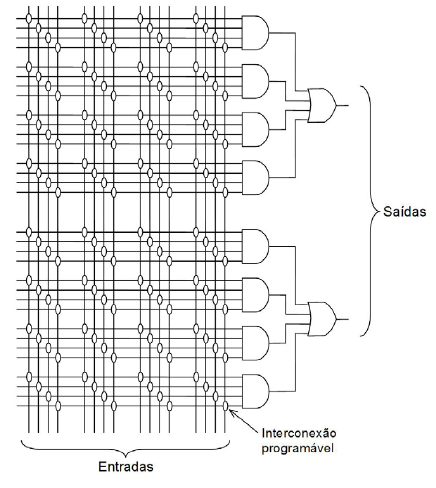

- PAL - Programmable Array Logic

Um arranjo programável de portas AND seguido por um arranjo fixo de portas OR.

Essa foi a primeira implementação de PLDs, e se baseia no fato de que qualquer função lógica pode ser reescrita como uma soma de produtos (SOP - sum of products) [4]. Por exemplo, sendo abaixo a tabela verdade da soma aritmética de um bit u de uma posição de um circuito somador, como função de x e y e do carry ci

| ci | x | y | u(ci,x,y) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Sendo as linhas 2, 3, 5 e 8, as que possuem saída 1, podemos escrever u como [5]:

Os PAL tem, porém, como limitação, a implementação apenas em circuitos combinacionais.

- PLA - Programmable Logic Array

Muito semelhante aos PALs, os PLA diferenciam-se no fato de que tanto as ligações AND quanto OR são programáveis.

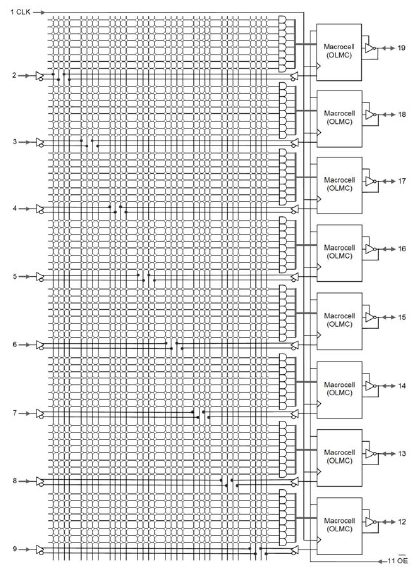

- GAL - Generic Array Logic

Características adicionais com relação aos PALs:

- Célula de saída (chamada de OLMC - output logic macrocell) com flip-flop, porta XOR, multiplexadores

- Inclusão de um sinal de retorno (feedback)

- Utilização de memórias EEPROM na programação do circuito

Um exemplo dessa arquitetura pode ser visto na figura abaixo:

CPLDs

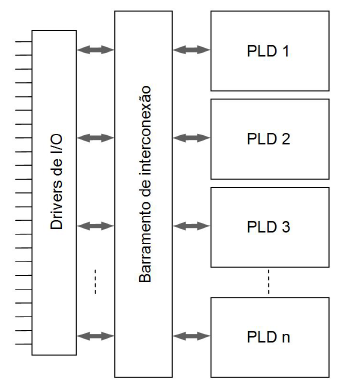

Como o próprio nome já adianta, os CPLDs possuem arquitetura muito mais complexa que os SPLDs. De fato, os primeiros CPLDs eram formados pela interconexão programável de vários SPLDs, além de outros avanços. Na figura abaixo, a arquitetura básica de um CPLD:

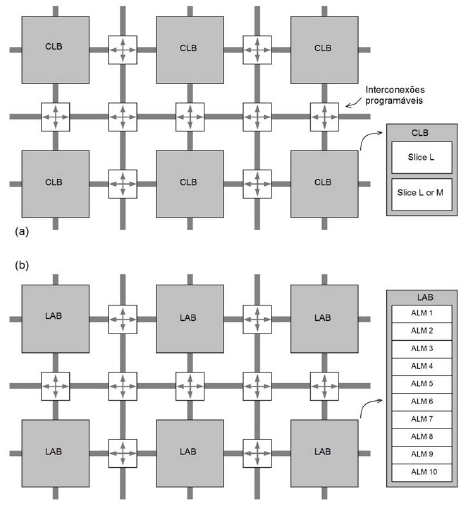

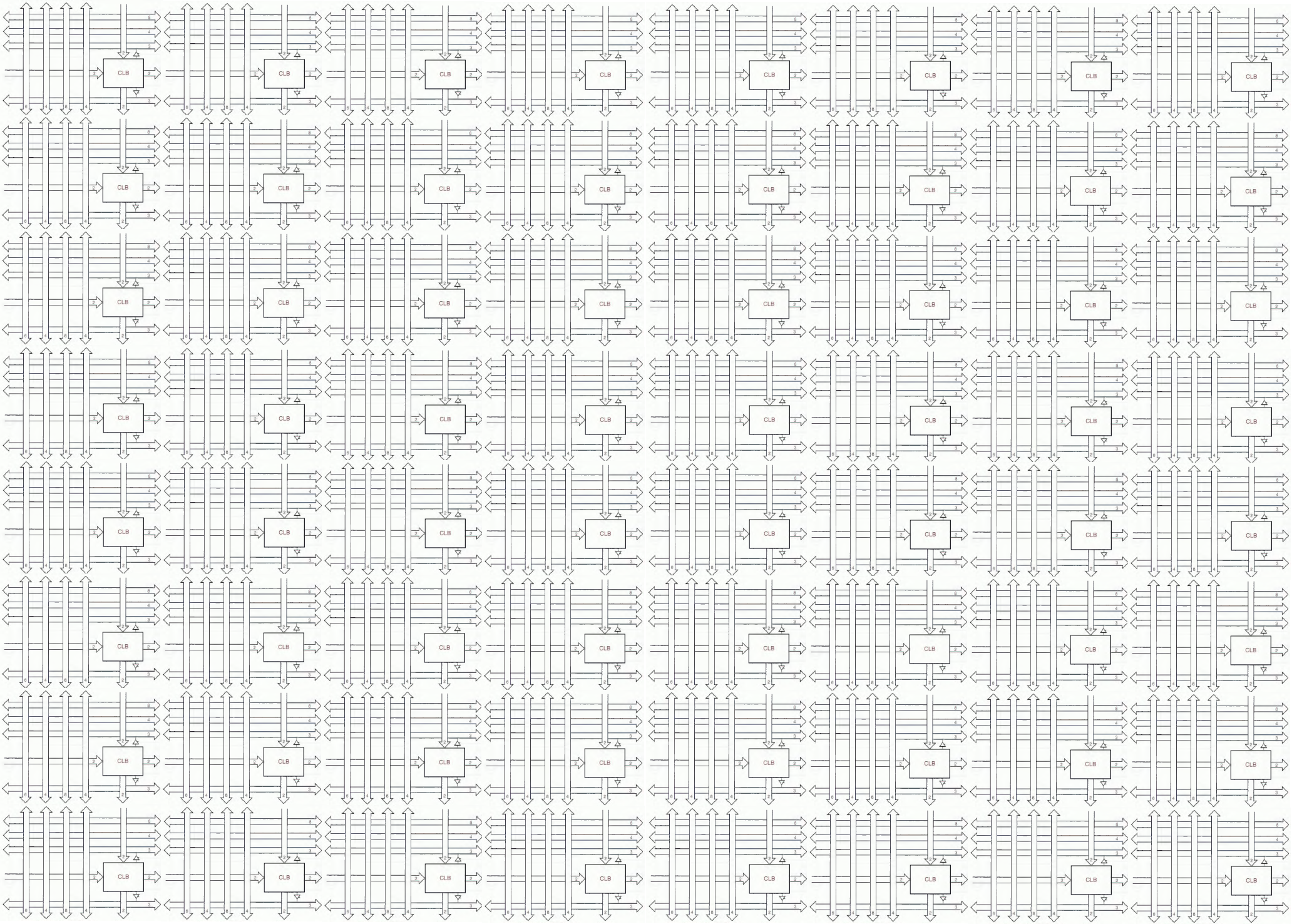

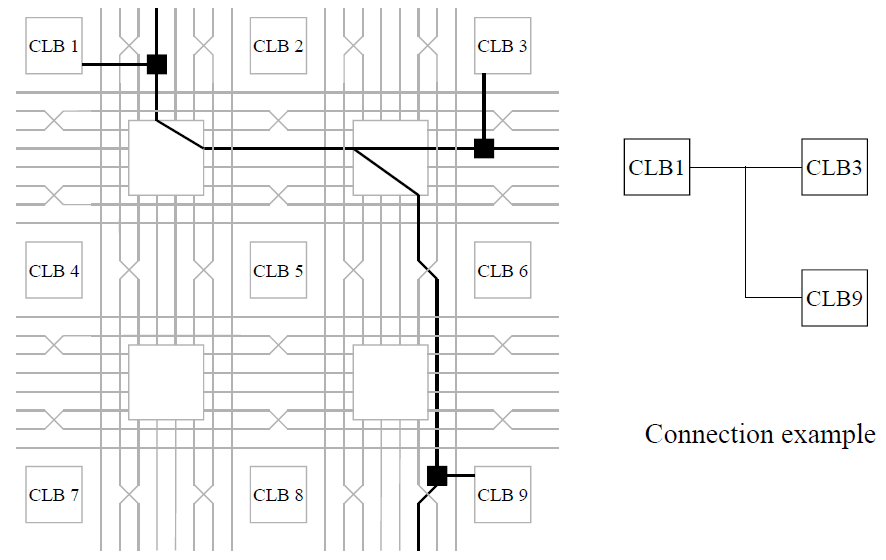

FPGAs - Field programmable gate arrays - Arranjo de portas programável em campo

Os FPGAs estendem as capacidades dos CPLDs, sendo diferentes em arquitetura, tecnologia, características embutidas e custo. Por serem voláteis, precisam de uma memória de configuração não volátil para armazenar a programação do hardware. Uma simplificação da arquitetura de FPGAs pode ser vista na figura abaixo. No caso, CLBs (configurable logic blocks) e LABs (logic array blocks) são blocos semelhantes à SPLDs GAL.

Além desses blocos, FPGAs costumam possuir também:

- Blocos RAM: Possibilitam o uso direto de memória, sem a necessidade de projetá-las

- Blocos DSP: Muito utilizados em aplicações de processamento de áudio e vídeo digitais, o bloco DSP implementa operações de soma, multiplicação e variáveis.

Comparação entre dispositivos

Uma comparação entre os dispositivos vistos nesta aula pode ser vista na figura abaixo:

onde as características de armazenamento do programa são:

- Fusível e antifusível - Configurado uma única vez

- (E)EPROM - Configurado um número limitado de vezes, mantida com o chip desconectado da alimentação (não volátil)

- SRAM - Configuração realizada cada vez que o sistema é alimantado (volátil)

Referências

[1] Midorikawa, Edson. Projeto de sistemas digitais. Disponível em Link. Acesso em 09/02/2015.

[2] Xilinx. What is Programmable Logic? Disponível em Link. Acesso em 09/02/2015.

[3] Parnell, Karen & Bryner, Roger. Comparing and contrasting FPGA and microprocessor system design and development. Disponível em Link. Acesso em 09/02/2015.

[4] Pedroni, Volnei A. Eletrônica digital moderna e VHDL. Disponível em Link. Acesso em 09/02/2015.

[5] Wikipedia. Canonical normal form. Disponível em Link. Acesso em 09/02/2015.

[6] Matos, Roberto de. Apresentação da disciplina de SST. Disponível em Link.

Tecnologia de FPGA

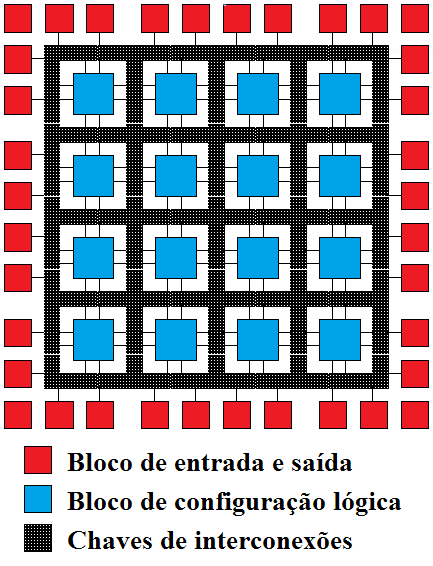

Os FPGAs são compostos por três tipos de componentes:

- Bloco de entrada e saída (Input/Output Block - IOB): Circuitos responsáveis pela interface de entrada e saída do FPGA. Compostos basicamente de buffers.

- Bloco de configuração lógica (Configurable Logic Block - CLB): Circuitos construídos usando flip-flops e lógica combinacional. Onde são construídas as funções lógicas do sistema.

- Chaves de interconexões: Trilhas configuráveis usadas para conectar os blocos de funções com os blocos de saída. O processo de escolha das interconexões é chamado de roteamento.

Os 3 blocos são interconectados em duas dimensões, otimizando as conexões entre os blocos

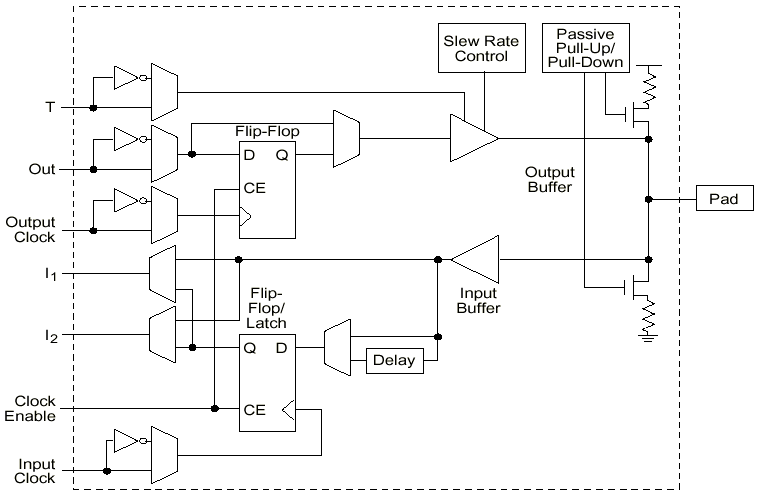

IOB

São usados para fazer a interface de entrada e saída do FPGA. Consiste em um buffer de entrada e um de saída, ambos com flip-flops, permitindo que saídas com clocks sejam disponibilizadas sem encontrar atrasos significantes e reduzindo a necessidade de manter sinais de entrada por muito tempo.

- Entrada e saída são concentradas num único pino descrito como Pad.

- Flip-flops realizam a sincronização dos dados, mas caminhos diretos, sem atrasos, são configuráveis

- Entrada do dado pelo flip-flop inferior.

- Saídas não utilizadas necessitam ser mantidas em tri-state.

- Slew rate controla a velocidade de mudança de polaridade. Valores menores reduzem ruídos.

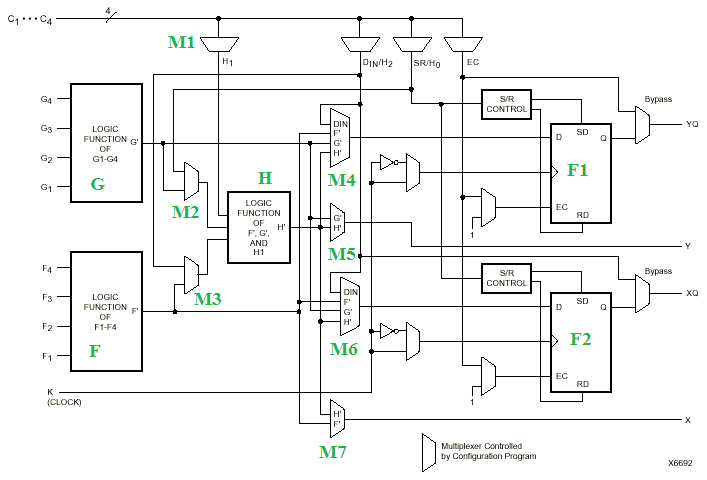

CLB [3]

Contêm a lógica do FPGA, como mostra a simplificação abaixo:

Neste bloco:

- Disponíveis 3 elementos configuráveis, dois com 4 entradas (F e G) e um com 3 entradas (H). Estes elementos podem construir qualquer função lógica a partir de suas entradas.

- Com os multiplexadores M1 a M3, é possível combinar os elementos para criar funções de mais de 4 entradas.

- Com os multiplexadores M4 a M7, a saída das funções lógicas podem ser enviadas diretamente para as saídas X e Y ou podem ser capturadas pelos flip-flops F1 e F2.

- Saída dos flip-flops nas saídas XQ e YQ, podendo os pinos serem "desativados" para simplesmente copiar sinais de entrada.

- O clock dos flip-flops pode ser configurado para a borda de subida ou descida.

- Os flip-flops podem também usar sinal de Enable.

- Os multiplexadores superiores permitem escolher a função dos sinais C1 a C4, para a entrada da função H ou outros sinais internos.

- Blocos S/R Control configuram o estado inicial dos flip-flops.

As funções lógicas são implementadas a partir de suas tabelas verdade nos elementos lógicos usando uma memória chamada de Lookup Table (LUT). Com isso, um bloco de configuração lógica também pode ser usado como uma memória, em diferentes configurações dependendo dos multiplexadores. Nesses casos, as entradas F1 a F4 e G1 a G4 fornecem endereços, e as entradas C1 a C4 fornecem os dados e sinais de enable.

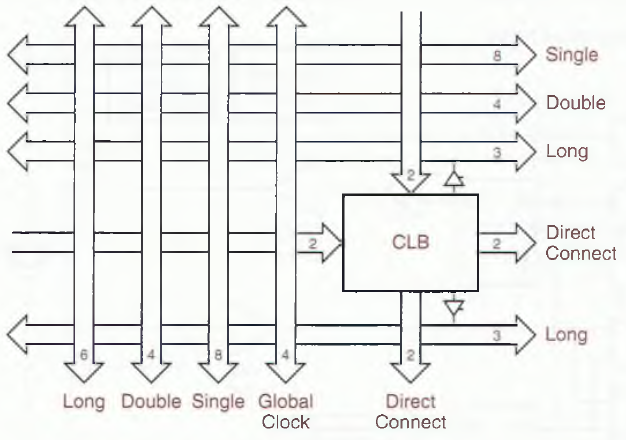

Chaves de interconexões

Os CLBs estão imersos numa rede de interconexões configuráveis. As conexões possíveis por cada bloco lógico podem ser vistas na figura abaixo.

Um FPGA com 64 blocos de configuração lógica seriam a repetição dessa figura numa matriz de 8x8

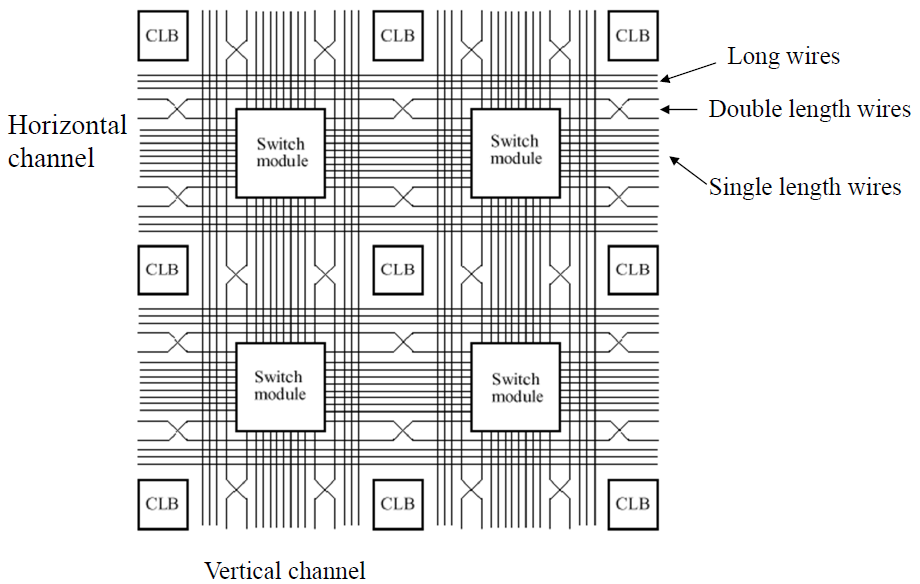

Para fazer a ligação entre CLBs vizinhos, o caminho unidirecional direct pode ser utilizado. Porém, para o roteamento de dados em maiores "distâncias", 3 outros caminhos são disponíveis, dispostos como a figura abaixo:

Na figura, uma Matriz de Comutação Programável (Programmable Switch Matrix - PSM) pode ser vista, além dos 3 caminhos indiretos:

- Single: ideal para conexão entre CLBs vizinhos, pois é conectado a todos os blocos PSM.

- Double: conectado intercaladamente nos blocos PSM

- Long: não é conectado nos blocos PSM

Os blocos PSM introduzem atraso na propagação do sinal no FPGA. Os 3 caminhos introduzem versatilidade ao balancear atrasos e propagação em longas distâncias.

O bloco PSM efetua a conexão entre pinos seguindo o esquema da figura abaixo. No esquema, os círculos vermelhos são chamados de Elementos de Comutação Programável (Programmable Switch Element - PSE).

Com isso, várias formas de conexão são possíveis, como exemplifica a figura a seguir:

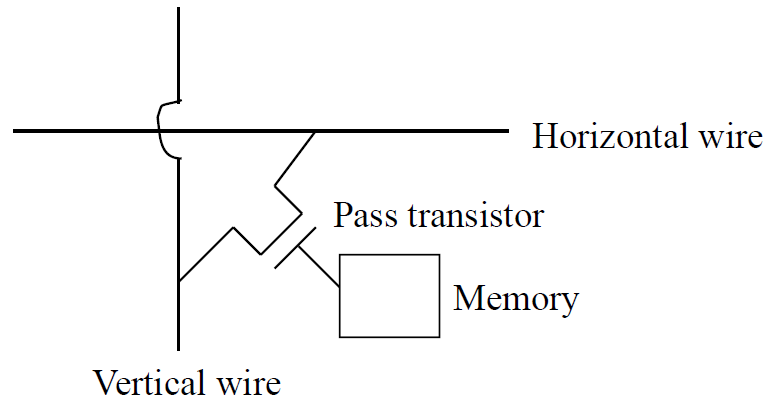

Várias tecnologias podem ser usadas para realizar a conexão num PSE:

- Antifusível: Realiza a função oposta de um fusível. Inicia com uma grande resistência, e cria um caminho condutivo ao ser aplicada uma voltagem maior do que um certo limite.

- Ocupam uma pequena área, permitindo um maior número de conexões em estruturas chamadas de Fully Populated

- Aumentam a flexibilidade

- Não podem ser reprogramados

- Transistores de passagem: Transistores controlados por posições de memória realizam a passagem do sinal entre os pinos.

- Ocupam uma grande área no chip, resultando num menor número de conexões

- Menor flexibilidade

- Pode ser reprogramado

O trabalho de roteamento de sinais dentro de um FPGA é realizado por ferramentas de Placement & Routing, que buscam otimizar a propagação de sinais.

NOTA: Os nomes dos blocos disponíveis nesta aula seguem os termos utilizados pela Xilinx, e os blocos referem-se a

uma família específica, a XC4000E. Para fabricantes diferentes, ou mesmo famílias diferentes, mudanças podem

ser observadas. Para informações sobre a arquitetura dos FPGAs da Altera, consultar [7].

Tabela comparativa entre FPGAs

A tabela a seguir é um exemplo de dados de fabricantes, no caso, da Xilinx.

- Max user I/O: Número de entradas e saídas por FPGA. Devido aos diferentes encapsulamentos possíveis, nem todos os pinos de entrada e saída podem estar disponíveis

- Flip-flops: Número total de flip-flops disponíveis, sendo 2 por CLB e 2 por IOB

- Max RAM bits (no logic): Número de bits de RAM disponíveis no caso de todos os CLBs estarem configurados como RAM

- Max gates (no RAM): Número total de portas disponíveis quando nenhum CLB estiver configurado como RAM

Referências

[1] Oskin, Mark. Apresentação sobre FPGAs da disciplina Advanced Digital Design. Disponível em Link. Acesso em 12/02/2015.

[2] Zeidman, bob. All about FPGAs. Disponível em Link. Acesso em 12/02/2015.

[3] Wakerly, John. Digital Design: Principles & practices. Disponível (versão para demonstração) em Link. Acesso em 12/02/2015.

[4] Wang, Haibo. FPGA Programmable Interconnect and I/O Cells. Disponível em Link. Acesso em 13/02/2015.

[5] Wikipedia. Field-programmable gate array. Disponível em Link. Acesso em 13/02/2015.

[6] Wong, William. FPGA Design Suite Generates Global Minimum Layout. Disponível em Link. Acesso em 13/02/2015.

[7] Altera. White Paper: FPGA architecture. Disponível em Link. Acesso em 13/02/2015.

Projetos em FPGA

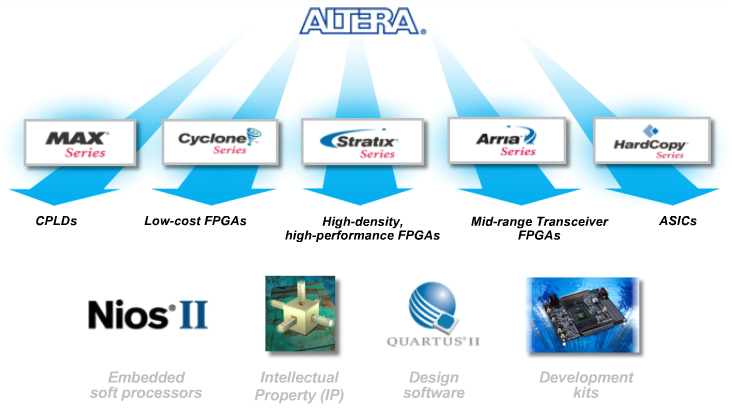

Altera

A Altera é uma das maiores fabricantes de FPGAs e CPLDs. Há no seu portfólio PLDs dos mais baixo custo até dos mais avançados do mercado. O Quartus II é o software de desenvolvimento de PLDs da Altera.

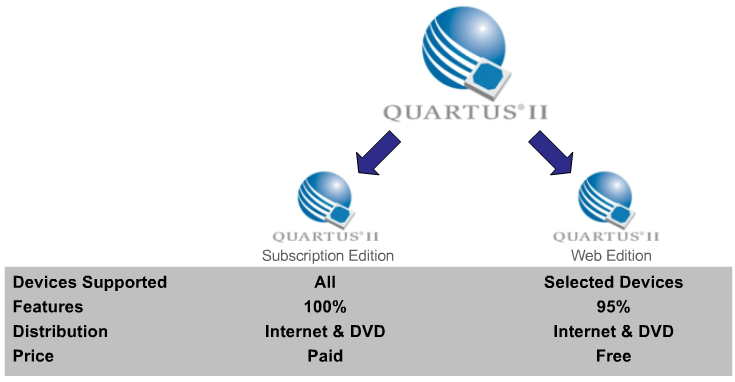

- Licença

A licença de uso é dada da seguinte forma:

- Web Edition: de uso livre, com limitações quanto ao número de DLPs disponíveis

- Full Edition - Fixed License: pago, com licença nativa no computador

- Full Edition - Float License: pago, com licença em rede

Uma comparação entre as edições Web e Full está disponível em Link.

Para configurar uma licença, acessar Link. A licença Web é gerada em Link. Alguns laboratórios do IFSC possuem computadores com licenças flutuantes, como pode ser visto no [Uso do Quartus II nos Labs do IFSC|Link].

- Como obter informações

A Altera preparou uma série de materiais sobre o desenvolvimento usando o Quartus II. Existem cursos on-line e presenciais, pagos e gratuitos:

- A página de cursos pode ser acessada em Link.

- O treinamento completo (muito material!) está disponível em Link.

- Um bom material escrito pode ser acessado em Link.

Quartus II

Abaixo, um roteiro para o reconhecimento do software da Altera:

- Abrir o Quartus II

- Getting Started

- Janelas:

- Project Navigator

- Message Window

- Tool View Window

- Tasks Window

- Custom Tasks Flow

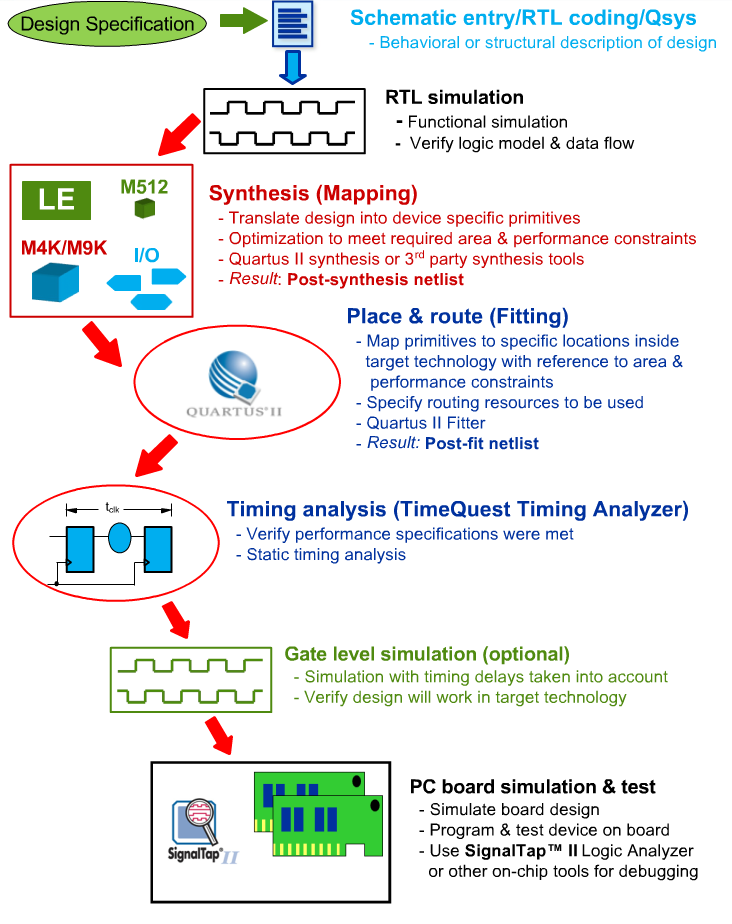

Fluxo de desenvolvimento em PLDs

- RTL: nível de abstração usado para descrever o circuito, dentre 3:

- Behavioural: mais alto nível de abstração, descreve o comportamento do circuito (entradas e saídas)

- RTL - Register Transfer Level: descrição do Hardware a partir de lógica, indicando como dados são transferidos entre registradores

- Gate Level: usa componentes como portas lógicas, flip-flops e multiplexadores

- Synthesis: processo em que o comportamento de um circuito numa forma abstrata (por exemplo, em RTL) é convertido para uma implementação em termos de portas lógicas.

- Netlist: descreve a conectividade dos terminais para o desenvolvimento do circuito.

- Place & Route - Fitting: otimiza a localização dos elementos e o roteamento dos dados entre eles.

Projeto no Quartus II

- Wizard

- Selecionar como dispositivo o Cyclone IV EP4CE30F23, ou o mais próximo disponível. É esse o modelo que será utilizado nas nossas aulas.

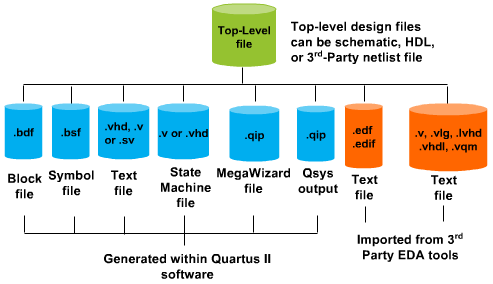

- Arquivos [2]

- .QPF - Quartus II Project File: informação da versão do Quartus 2 e da data. Traz as revisões efetuadas no projeto.

- .QDF - Quartus II Defaults File: configurações padrão de todo novo projeto criado

- .QSF - Quartus II Settings File: configurações específicas do projeto, como arquivos, dispositivo escolhido, etc.

- Pasta dB: informação do projeto compilado

- .SDC - Synopsys Design Constraint: restrições temporais do projeto

- O Quartus também oferece ferramentas para controle de versão de projetos a partir de arquivos .QAR - Quartus II Compressed Archive File. Disponível no menu Project. Com revisões, é possível fazer testes com outros parâmetros sem perder resultados anteriores.

Formas de desenvolvimento

Ir em File -> New, e selecionar um dos Design Files disponíveis.

Nesta aula, usaremos o desenvolvimento via Esquemático - Block File.

Desenvolvimento via esquemático

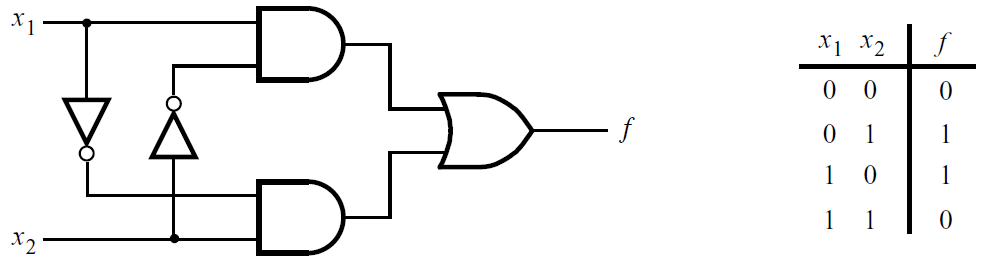

Um exemplo de sistema será usado para apresentar a ferramenta. O sistema que será desenvolvido está disponível na figura abaixo:

O desenvolvimento é feito a partir dos seguintes passos:

- Criar novo arquivo do tipo Schematic

- Importar portas lógicas

- Importar sinais de entrada e saída

- Atribuir nomes aos pinos

- Conectar os componentes

- Compilar

- Atribuir pinos físicos do FPGA aos pinos do sistema (Pin planner)

- Pinos atribuídos podem ser exportados para futuros desenvolvimentos

- Descrever sinais de entrada (criar arquivo VWF - Vector Waveform File)

- Simular (Tool -> Simulation)

Exercício 1 - Esquemático

Executar o roteiro disponível em Link sem executar a parte do FPGA.

Referências

[1] Altera Training Courses. Using the Quartus II Software: An Introduction. Disponível em Link. Acesso em 19/02/2015.

[2] Altera. Quartus II Volume I: Design and Synthesis. Disponível em Link. Acesso em 19/02/2015.

[3] Altera. Quartus II Introduction Using Schematic Designs. Disponível em Link. Acesso em 27/02/2015.

Utilizando o FPGA

No exercício da aula anterior, o roteiro para a implementação de um contador assíncrono crescente foi executado apenas no Quartus II, sem a gravação do projeto no FPGA. Nesta aula, o roteiro será encerrado.

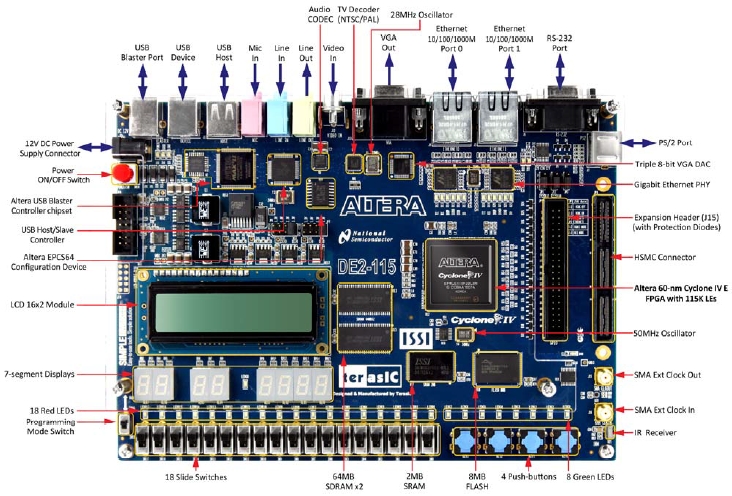

O kit DE2-115

O Kit Altera DE2-115 pode ser visto na figura abaixo.

Algumas características do kit:

- FPGA Altera Cyclone IV EP4CE115F29C7

- 2 MB de SRAM

- 64 MB de SDRAM

- 8 MB de Flash

- Interfaces:

- Botões

- Switch

- Leds

- Módulo LCD

Para ligar o kit, seguir os passos:

- Conectar o cabo USB no computador e no kit na porta USB Blaster. Talvez seja necessário instalar o driver específico para o USB da Altera. Para instalar, consultar Link e Link.

- Desligar o kit soltando o botão ON/OFF vermelho.

- Conectar o adaptador 12V.

- Selecione a posição RUN no switch RUN/PROG (SW19).

- Ligue o kit pressionando o botão ON/OFF vermelho.

Para mais informações, consultar a página

Solução do roteiro

O roteiro do exercício 1 apresenta os passos para a solução. São informações complementares ao roteiro:

- Para atribuir os pinos usando o arquivo .qsf fornecido pela Altera, usar o menu Assignments → Import Assignments.

- Uma outra referência para o processo de programação do FPGA pode ser vista em Link.

Referências

[1] Altera. DE2-115 User Manual. Disponível em Link.

Introdução ao VHDL

VHDL vem de VHSIC (Very High Speed Integrated Circuito) Hardware Description Language. É a linguagem padrão IEEE para a descrição de hardware na indústria.

- Características:

- Maior parte da linguagem não é Case Sensitive

- Expressões são terminadas com ponto-e-vírgula

- É Space Insensitive

- Comentários feitos com um "--" no início da linha. Não há comentários em bloco

Unidades do código VHDL

O código VHDL é inicialmente dividido em 3 seções:

PACKAGE ENTITY ARCHITECTURE

PACKAGE

Declara as bibliotecas utilizadas no sistema. Usa o formato:

LIBRARY nome1, nome2; USE nome1.pack_name1.object; USE nome2.pack_name2.ALL;

Duas LIBRARYs disponibilizadas automaticamente:

- STD: tipos básicos de dados:

- BIT: dois valores ('0' e '1')

- BIT_VECTOR: deve indicar a ordem dos bits

SIGNAL s1 : BIT_VECTOR (3 DOWNTO 0); SIGNAL s2 : BIT_VECTOR (0 TO 3);

- BOOLEAN: dois valores (False, true)

- INTEGER: Valores positivos e negativos em decimal

SIGNAL s3 : INTEGER; -- Número de 32 bits SIGNAL s4 : INTEGER RANGE 0 TO 255 -- Número de 8 bits

- NATURAL: Inteiro sem sinal

- CHARACTER: ASCII

- STRING: Array de ASCII

- TIME: Valores com unidades de tempo (ps, ms, min, hr)

- REAL: Número de ponto flutuante de precisão dupla

- WORK: indica onde estão armazenados os arquivos do projeto

Um pacote frequentemente incluído é STD_LOGIC_1164, da LIBRARY IEEE, que define os tipos:

- STD_LOGIC: bit com 3-state (Z) e "não importa" (-)

- STD_ULOGIC: tipo lógico com 9 valores Link

A declaração do pacote IEEE ficaria assim:

LIBRARY ieee USE ieee.std_logic_1164.all;

ENTITY

define a visão externa do modelo (símbolo). Usa o formato:

ENTITY <entity_name> IS GENERIC PORT END ENTITY <entity_name>

onde:

- PORT: descreve entradas e saídas

PORT ( nome1, nome2 : <mode> <type>; nome3, nome4 : <mode> <type> );

- <mode>:

- in (input): sinais de entrada - São apenas lidos

- out (output): sinais de saída - São apenas escritos

- inout (bidirecional): podem ser lidos e escritos

- <type>: tipo do dado

- GENERIC: passa informações globais (constantes) ao modelo

GENERIC ( nome1, nome2 : <type> (:= <initial value>); nome2, nome4 : <type> (:= <initial value>) );

- <type>: tipo do dado

- <initial value>: opcional

ARCHITECTURE

Define a função do modelo (esquemático). Segue o formato:

ARCHITECTURE <identifier> OF <entity_identifier> IS

<declaration>

BEGIN

<body>

END ARCHITECTURE <identifier>

onde:

- <entity_identifier>: nome da ENTITY a qual pertence a ARCHITECTURE

- <identifier>: nome da ARCHITECTURE, que deve ser único dentre as ARCHITECTUREs da ENTITY

- <declaration>: identificadores locais usados na ARCHITECTURE que não são PORTs nem GENERICs. Devem ser declarados antes de usados.

- <body>: corpo da ARCHITECTURE

Desenvolvimento via VHDL

Um exemplo de sistema será usado para apresentar o Quartus II e o VHDL. O sistema que será desenvolvido está disponível na figura abaixo:

O desenvolvimento é feito a partir dos seguintes passos:

- Criar novo arquivo do tipo VHDL File

- Escrever o código

- Templates podem ser usados (Edit -> Insert Template)

- Compilar

- Atribuir pinos físicos do FPGA aos pinos do sistema (Pin planner)

- Pinos atribuídos podem ser exportados para futuros desenvolvimentos

- Descrever sinais de entrada (criar arquivo VWF - Vector Waveform File)

- Simular (Tool -> Simulation)

Concorrência do código

Os código VHDL tem uma característica importante que é a concorrência. Assim, todas as instruções tem a mesma procedência, diferentemente das linguagens de programação. O exemplo abaixo demonstra isso:

A solução do problema pode ser vista abaixo:

Erros clássicos

Em desenvolvimento com VHDL, são comuns os seguintes erros [3]:

- Tipos de dados diferentes (um lado é BIT e outro é BOOLEAN) - Tamanhos não são iguais - Valor ou representação inválido (BIT não aceita valor 'Z', vetor de bits requer aspas duplas) - Indexação incorreta (ordem) - Operador de atribuição incorreto (para sinais é "<="; para variáveis e constantes é ":="

Referências

[1] Altera Training Courses. VHDL Basics. Disponível em Link. Acesso em 27/02/2015. [2] Altera. Quartus II Introduction Using VHDL Designs. Disponível em Link. Acesso em 27/02/2015. [3] Pedroni, Volnei A. Eletrônica Digital Moderna e VHDL. Rio de Janeiro: Elsevier, 2010.