Registro on-line das aulas

Unidade 1 - Introdução a disciplina

| Unidade 1 - Introdução a disciplina

|

- Encontro 1 (26 jul)

- APRESENTAÇÃO DA DISCIPLINA

- A PÁGINA DA DISCIPLINA contem os materiais que não alteram entre semestre.

- Nesta página está o REGISTRO DIÁRIO E AVALIAÇÕES.

- A entrega de atividades e avaliações será através da plataforma Moodle. A inscrição dos alunos é automática a partir do SIGAA.

- Para a comunicação entre professor-aluno, além dos avisos no SIGAA, utilizaremos o chat institucional. A princípio todos os alunos já estão previamente cadastrados pelo seu email institucional. Confiram enviando uma mensagem de apresentação.

- Durante as aulas é recomendado que o aluno utilize os softwares Quartus e Modelsim instalados nas maquinas do laboratório, mas estes também podem ser usados através da Nuvem do IFSC.

- Nas aulas é recomendado que o aluno utilize os softwares Quartus Light e ModelSim instalado nas máquinas do laboratório ou então acesse estes softwares através da NUVEM do IFSC.

- LER PARA O PRÓXIMO ENCONTRO

- Encontro 2 (28 jul)

- Introdução aos dispositivos lógicos programáveis:

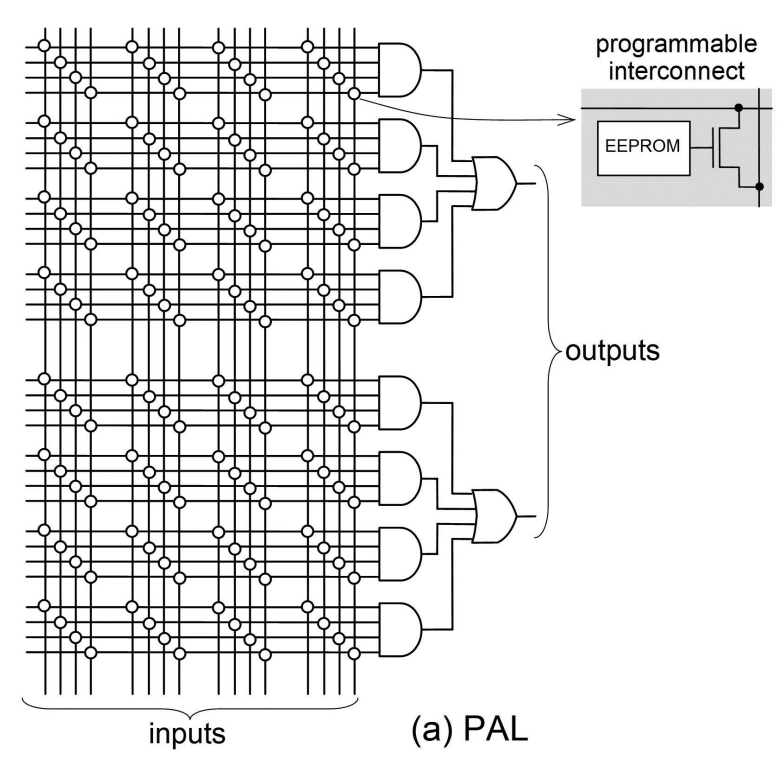

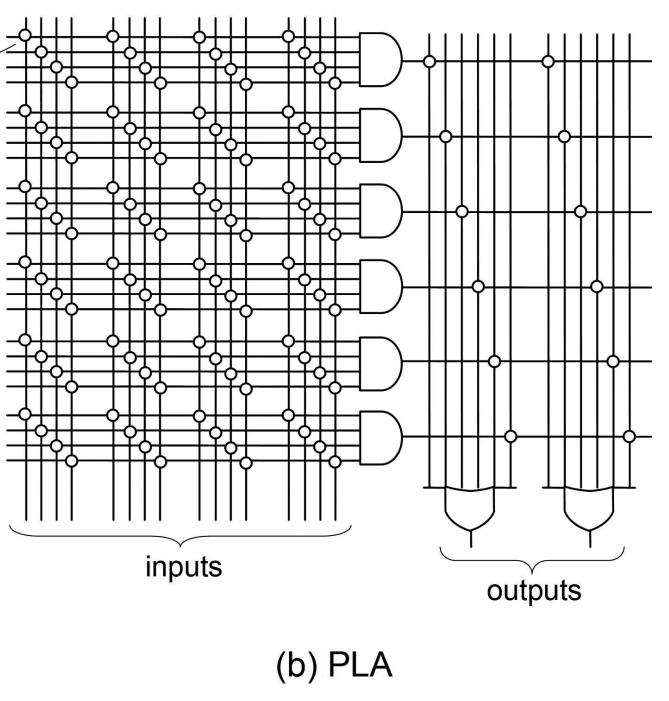

- Conceito, tipos de PLDs

- SPLD:

-

- Fabricantes de DLPs/FPGAs e familias de DLPs atuais.

- PARA O PRÓXIMO ENCONTRO

- Encontro 3 (1 ago)

- PARA O PRÓXIMO ENCONTRO

- Leia a assista a alguns dos vídeos sobre a historia e processo de produção dos chips.

PRÓXIMO

- Encontro 4 (4 ago)

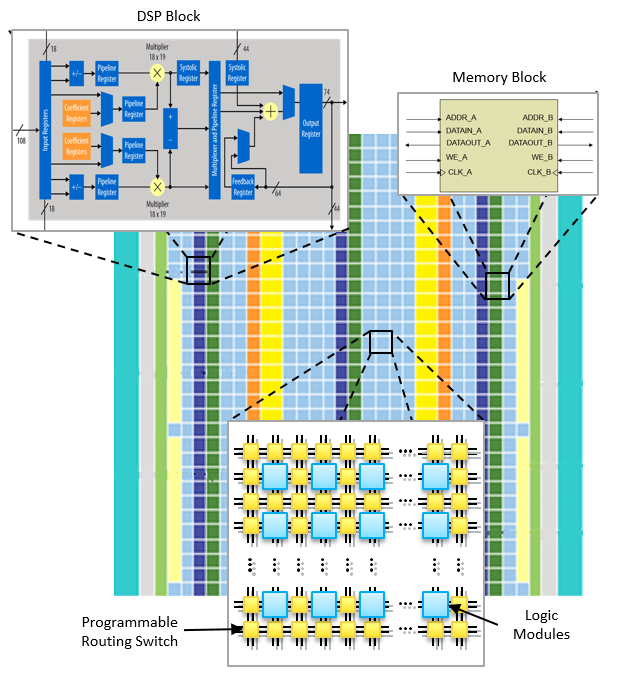

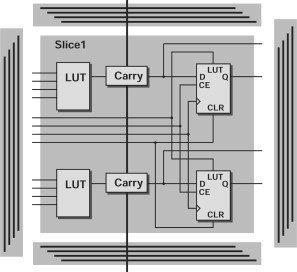

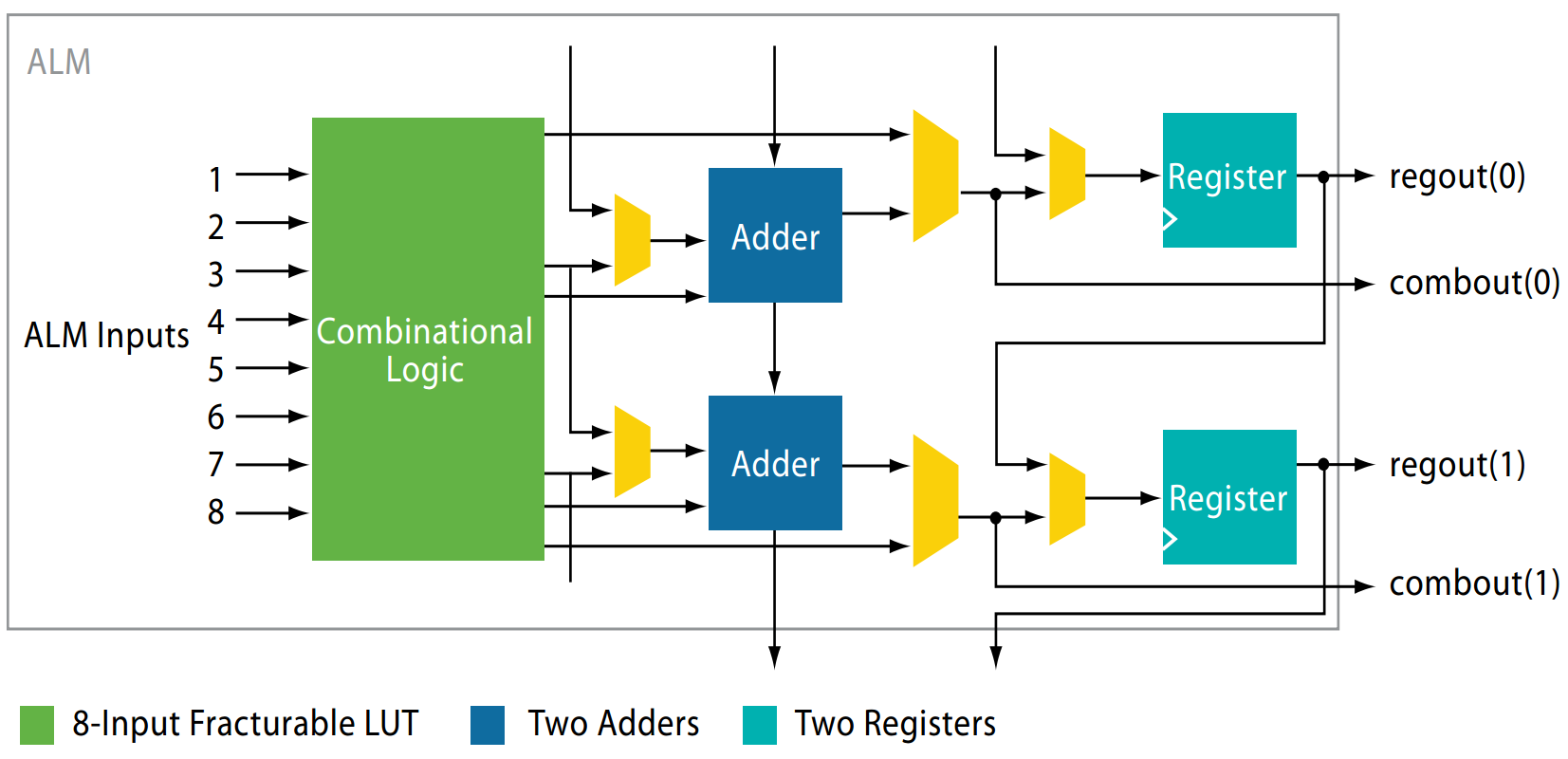

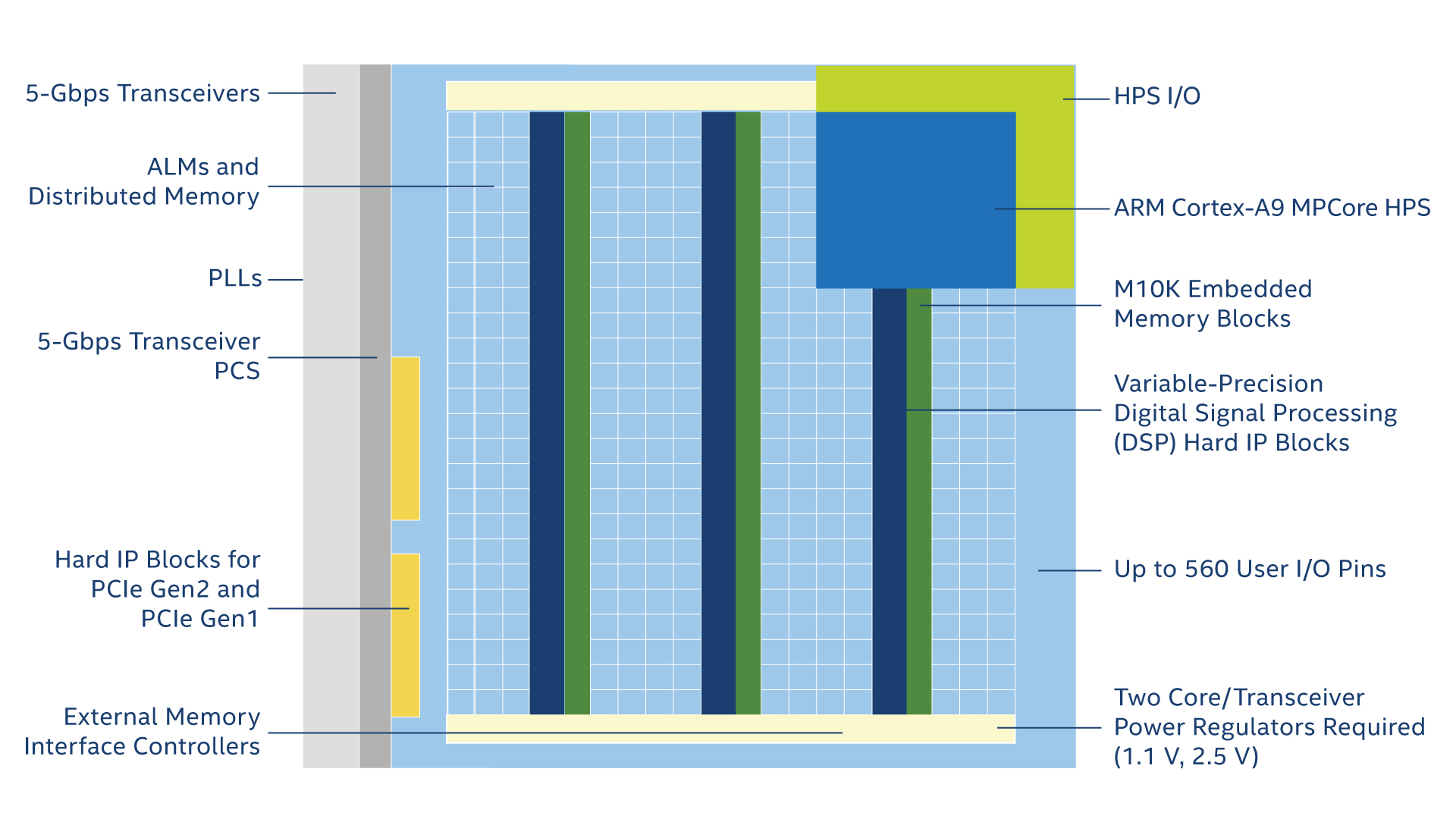

- Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, LUT, Flip_flop D, RAM, DSP, Clock, PLL, DLL, I/O

- PARA O PRÓXIMO ENCONTRO

- Leia a assista a alguns dos vídeos sobre FPGAs.

- CURIOSIDADES

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

|

|

|

Unidade 3 - Tipos de Dados e Operadores em VHDL

| Unidade 3 - Tipos de Dados e Operadores em VHDL

|

|

|

Unidade 4 - Código Concorrente

| Unidade 4 - Código Concorrente

|

|

|

Unidade 5 - Código Sequencial

| Unidade 5 - Código Sequencial

|

|

|

Unidade 6 - Projeto a nível de Sistema

| Unidade 6 - Projeto a nível de Sistema

|

|

|

Unidade 7 - Maquinas de Estado Finitas

| Unidade 7 - Maquinas de Estado Finitas

|

|

|

Unidade 8 - Testbench

Avaliações

Nas avaliações A1 e A2 vocês poderão consultar apenas as folhas entregues:

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - Unidade 1 a Unidade 4: dia XX/XX

- A2 - Unidade 5 a Unidade 7: dia XX/XX

- PF - Entrega do projeto final: dia 15/12

- R12 - Recuperação de A1 e A2 : dia 12/12

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN.

A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

AE2 - Conhecendo os dispositivos lógicos programáveis

| AE2 - Conhecendo os dispositivos lógicos programáveis

|

- Objetivos

- Conhecer o Quartus Prime e as características dos dispositivos lógicos programáveis

- Analisar os tempos de propagação em um circuito combinacional

- Alterar configurações do compilador

- Fazer a simulação funcional e temporal de um circuito combinacional.

- Atividades

- Ao escolher a família de FPGAS, escolha inicialmente um dispositivo da família Max II. Anote o código desse dispositivo.

- Capture as telas solicitadas e depois utilize-as no relatório da atividade.

- Anote o tempo utilizado para cada uma das etapas do processo de compilação.

- Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo.

- Anote algum erro (Error) ou alertas (Warnings) que o Quartus II indicar no painel de mensagens [Messages]

- Ao final salve o projeto em um arquivo QAR (sugestão PJ1.QAR)

- Observe as mudanças que ocorrem tanto no tipo de Elemento Lógico disponível, no Chip Planner, no Pin Planner, e no circuito dos pinos de I/O. Note que estes FPGAs também apresenta novos componentes, tais como: Memória, Multiplicadores, DSP, PLL, DLL, etc. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documente aqueles que encontrar.

- Compare os resultados obtidos nos procedimentos do PASSO 1 e PASSO 2.

- Ao escolher a família de FPGAS, escolha um dispositivo FPGA da família Cyclone IV E. Anote o código desse dispositivo.

- Capture as telas mostradas no roteiro e depois utilize-as no relatório da atividade.

- Anote o máximo tempo de propagação entre entrada e saída.

- Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo.

- Experimente modificar as configurações do compilador, conforme mostrado em Configurando o compilador. Se desejar mude a semente inicial trocando o valor de [Seed: 1]

- Experimente inserir diferentes restrições de atraso máximo para o compilador, e analise o resultado obtido.

- Anote algum erro (Error) ou alertas (Warnings) que o Quartus II indicar no painel de mensagens [Messages]

- Ao final salve o projeto em um arquivo QAR (sugestão PJ2.QAR)

- PASSO 4: Realize a simulação funcional de um dos projetos CI74161 ou do cálculo da distância de Hamming

- Capture as telas que mostram o circuito funcionando e depois utilize-as no relatório da atividade.

- Entregas

- Envie um arquivo QAR contendo todos os arquivos necessário para compilar cada um dos projetos.

- Envie um relatório em PDF, incluindo as imagens capturadas (inclua um título para cada figura) e escreva para cada imagem um texto comentando o que representa. O relatório também deve ter a identificação (autor, título, data) uma breve introdução e uma conclusão. A descrição dos procedimentos feita na página wiki não precisa incluída no relatório.

- Use preferencialmente o Overleaf para gerar o relatório. Mas o uso de MS-Word, Libreoffice e Google Docs também é permitida.

- A entrega será feita através do Moodle da disciplina. Observe o prazo de entrega.

|