Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

| Linha 71: | Linha 71: | ||

:*[https://www.youtube.com/watch?v=GU87SH5e0eI A dependência do mundo com a TMSC] | :*[https://www.youtube.com/watch?v=GU87SH5e0eI A dependência do mundo com a TMSC] | ||

| − | ==== | + | ====ATUAL==== |

;Encontro 4 (4 ago): | ;Encontro 4 (4 ago): | ||

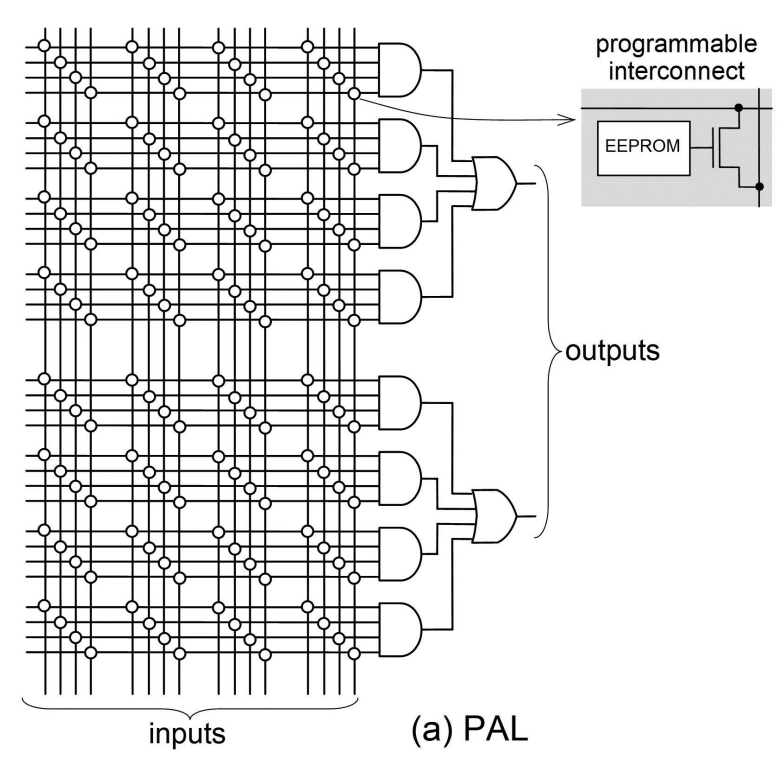

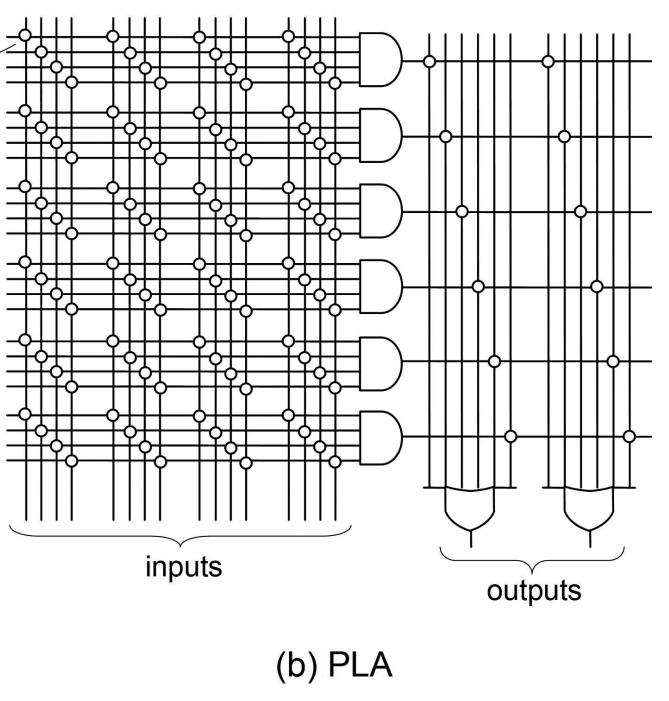

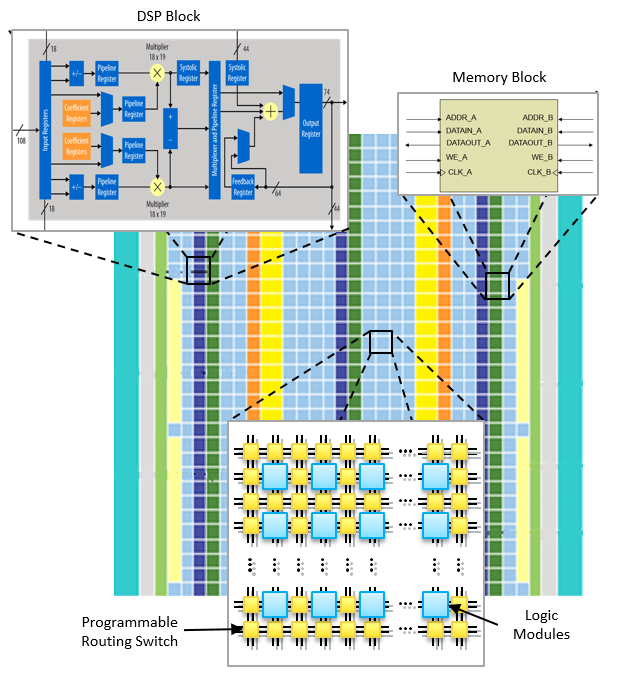

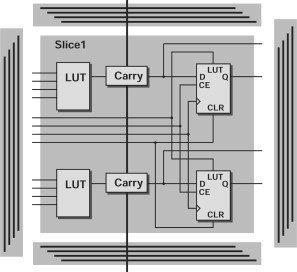

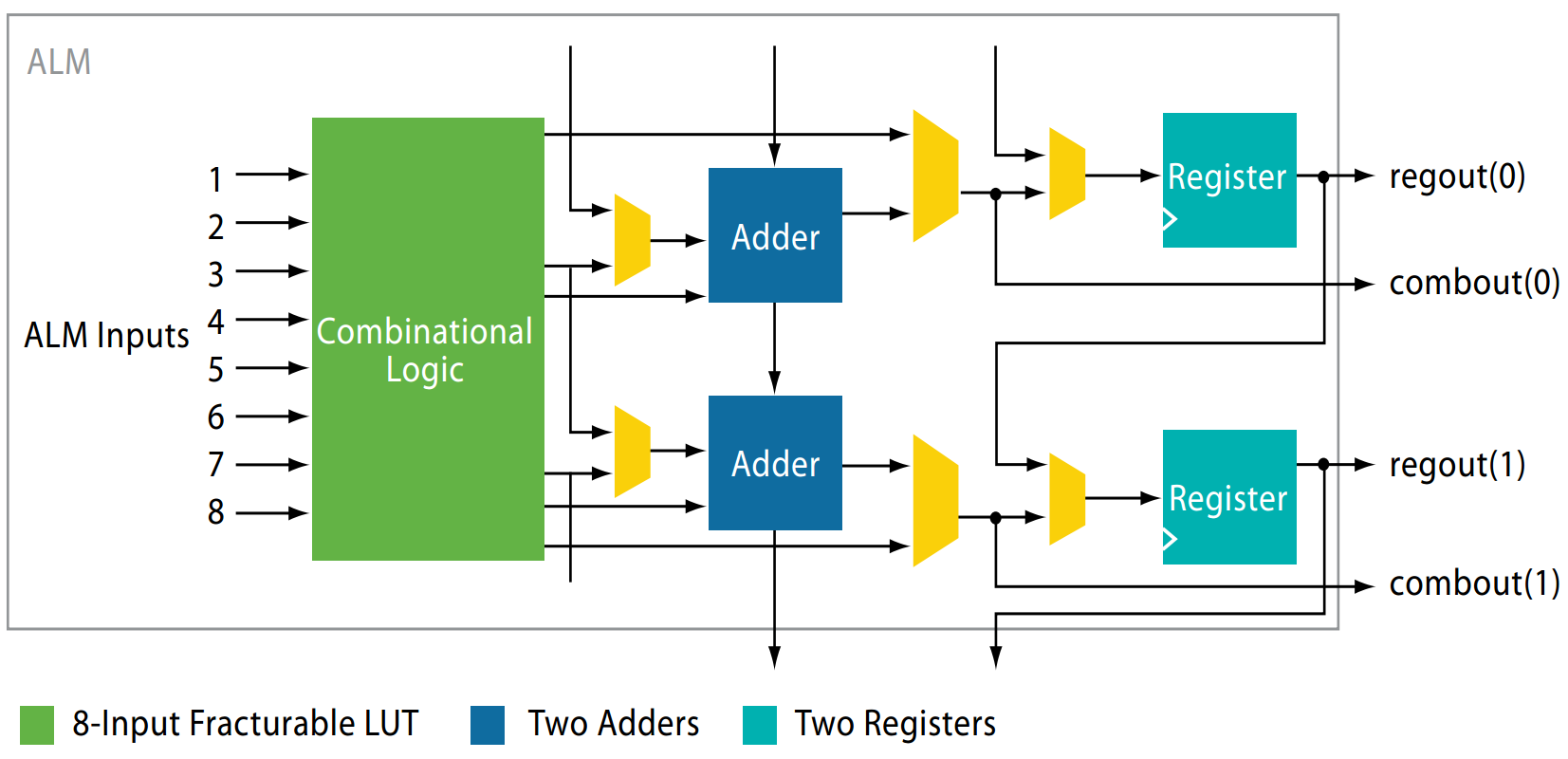

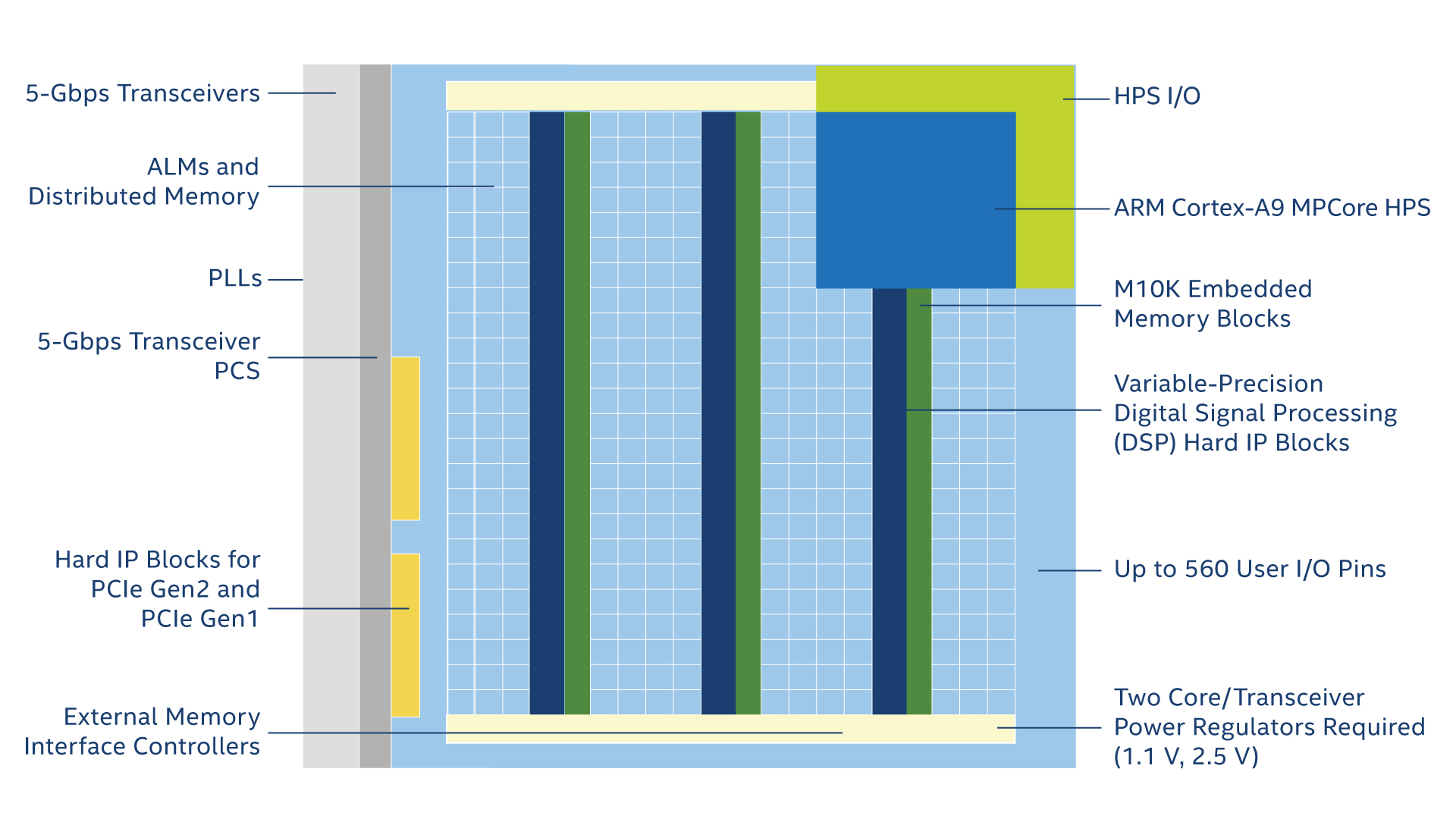

* Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, LUT, Flip_flop D, RAM, DSP, Clock, PLL, DLL, I/O | * Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, LUT, Flip_flop D, RAM, DSP, Clock, PLL, DLL, I/O | ||

| Linha 107: | Linha 107: | ||

*[https://www10.edacafe.com/book/ASIC/CH04/CH04.1.php The Antifuse], [https://www.youtube.com/watch?v=7qa1dsCpMMo EEPROM], [https://www.youtube.com/watch?v=ELl3abwYQ90&list=PL9B4edd-p2agcmJl2EscTdLudLv58uXHt&index=1 What Is Flash Memory] | *[https://www10.edacafe.com/book/ASIC/CH04/CH04.1.php The Antifuse], [https://www.youtube.com/watch?v=7qa1dsCpMMo EEPROM], [https://www.youtube.com/watch?v=ELl3abwYQ90&list=PL9B4edd-p2agcmJl2EscTdLudLv58uXHt&index=1 What Is Flash Memory] | ||

*[https://numato.com/blog/differences-between-fpga-and-asics/ FPGA Vs ASIC: Differences Between Them And Which One To Use?] | *[https://numato.com/blog/differences-between-fpga-and-asics/ FPGA Vs ASIC: Differences Between Them And Which One To Use?] | ||

| + | |||

| + | ====PRÓXIMO==== | ||

| + | ;Encontro 5 (8 ago): | ||

| + | * [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 3 e 4 | ||

| + | *Exemplo de um Circuito para cálculo da '''distância de Hamming'''. | ||

| + | :*[[Medição de tempos de propagação em circuitos combinacionais]] | ||

| + | :* Os alunos devem utilizar a nuvem para realizar a atividade. | ||

| + | :*[https://wiki.sj.ifsc.edu.br/index.php/Medi%C3%A7%C3%A3o_de_tempos_de_propaga%C3%A7%C3%A3o_em_circuitos_combinacionais#Inserindo_restri.C3.A7.C3.B5es_de_atraso_m.C3.A1ximo_para_o_compilador Inserindo restrições de atraso máximo para o compilador] | ||

| + | :* Objetivos: Copiar e colar o código no Quartus; diferença entre analise e síntese e compilação; observar o RTL (usar UNGROUP); simulação funcional e simulação temporal; observar os atrasos de propagação na simulação temporal. | ||

<!-- | <!-- | ||

Edição das 11h19min de 4 de agosto de 2023

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 6 ENCONTROS

| Unidade 1 - Introdução a disciplina |

|---|

ATUAL

PRÓXIMO

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 10 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

- 10 ENCONTROS

| Unidade 3 - Tipos de Dados e Operadores em VHDL |

|---|

Unidade 4 - Código Concorrente

- 4 ENCONTROS

| Unidade 4 - Código Concorrente |

|---|

Unidade 5 - Código Sequencial

- 7 ENCONTROS

| Unidade 5 - Código Sequencial |

|---|

Unidade 6 - Projeto a nível de Sistema

- 3 ENCONTROS

| Unidade 6 - Projeto a nível de Sistema |

|---|

Unidade 7 - Maquinas de Estado Finitas

- 3 ENCONTROS

| Unidade 7 - Maquinas de Estado Finitas |

|---|

Unidade 8 - Testbench

- 2 ENCONTROS

| Unidade 8 - Testbench |

|---|

Avaliações

Nas avaliações A1 e A2 vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - Unidade 1 a Unidade 4: dia XX/XX

- A2 - Unidade 5 a Unidade 7: dia XX/XX

- PF - Entrega do projeto final: dia 15/12

- R12 - Recuperação de A1 e A2 : dia 12/12

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN.

Atividade extra-classe (AE)

A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

AE2 - Conhecendo os dispositivos lógicos programáveis

| AE2 - Conhecendo os dispositivos lógicos programáveis |

|---|

|