Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

(→ATUAL) |

|||

| Linha 107: | Linha 107: | ||

*[https://numato.com/blog/differences-between-fpga-and-asics/ FPGA Vs ASIC: Differences Between Them And Which One To Use?] | *[https://numato.com/blog/differences-between-fpga-and-asics/ FPGA Vs ASIC: Differences Between Them And Which One To Use?] | ||

| − | |||

;Encontro 5 (8 ago): | ;Encontro 5 (8 ago): | ||

* [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 3 e 4 | * [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 3 e 4 | ||

| Linha 115: | Linha 114: | ||

:*[https://wiki.sj.ifsc.edu.br/index.php/Medi%C3%A7%C3%A3o_de_tempos_de_propaga%C3%A7%C3%A3o_em_circuitos_combinacionais#Inserindo_restri.C3.A7.C3.B5es_de_atraso_m.C3.A1ximo_para_o_compilador Inserindo restrições de atraso máximo para o compilador] | :*[https://wiki.sj.ifsc.edu.br/index.php/Medi%C3%A7%C3%A3o_de_tempos_de_propaga%C3%A7%C3%A3o_em_circuitos_combinacionais#Inserindo_restri.C3.A7.C3.B5es_de_atraso_m.C3.A1ximo_para_o_compilador Inserindo restrições de atraso máximo para o compilador] | ||

:* Objetivos: Copiar e colar o código no Quartus; diferença entre analise e síntese e compilação; observar o RTL (usar UNGROUP); simulação funcional e simulação temporal; observar os atrasos de propagação na simulação temporal. | :* Objetivos: Copiar e colar o código no Quartus; diferença entre analise e síntese e compilação; observar o RTL (usar UNGROUP); simulação funcional e simulação temporal; observar os atrasos de propagação na simulação temporal. | ||

| − | + | ;PARA CONHECER MAIS: | |

| − | |||

| − | ; | ||

| − | |||

| − | |||

| − | |||

* Ler pag. 413 a 431 de <ref name="PEDRONI2010a"> PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657 </ref> ou pag. 495 a 501 de de <ref name="PEDRONI2010b"> PEDRONI, Volnei A. '''Circuit Design and Simulation with VHDL'''; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 </ref>. | * Ler pag. 413 a 431 de <ref name="PEDRONI2010a"> PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657 </ref> ou pag. 495 a 501 de de <ref name="PEDRONI2010b"> PEDRONI, Volnei A. '''Circuit Design and Simulation with VHDL'''; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 </ref>. | ||

| − | + | * [https://en.wikipedia.org/wiki/Field-programmable_gate_array#History FPGA History] | |

| − | + | * [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Design_and_programming FPGA Design and programming] | |

| − | + | * [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Basic_process_technology_types FPGA Basic process technology types] | |

| − | + | * [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Major_manufacturers FPGA Major manufacturers] | |

| − | |||

* Assistir [https://www.coursera.org/lecture/intro-fpga-design-embedded-systems/1-many-types-of-fpgas-EWo0n Many types of FPGAs] Coursera | * Assistir [https://www.coursera.org/lecture/intro-fpga-design-embedded-systems/1-many-types-of-fpgas-EWo0n Many types of FPGAs] Coursera | ||

| − | + | * O que é um Schmitt trigger? | |

| − | + | :*[https://youtu.be/d-7Oyd8o8hE?t=93 Um pouco de lab] - lab até o minuto 5:20, depois um exemplo com AMPOP | |

| − | + | :*[https://howtomechatronics.com/how-it-works/electrical-engineering/schmitt-trigger/ como funciona] | |

| − | + | * O que é a JTAG? | |

| − | + | :*[https://www.corelis.com/educationdownload/JTAG-Tutorial.pdf Como funciona para testes e programação] - In-System-Programming pag.7 | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

;Notícias recentes do mundo dos DLPs: | ;Notícias recentes do mundo dos DLPs: | ||

| − | |||

*[https://newsroom.intel.com/press-kits/intel-acquisition-of-altera/#:~:text=Intel%20and%20Altera%20announced%20on,transaction%20closed%20December%2028%2C%202015. Intel Acquisiton of Altera] | *[https://newsroom.intel.com/press-kits/intel-acquisition-of-altera/#:~:text=Intel%20and%20Altera%20announced%20on,transaction%20closed%20December%2028%2C%202015. Intel Acquisiton of Altera] | ||

<i> | <i> | ||

| Linha 157: | Linha 142: | ||

:AMD said it has completed its '''$49 billion''' acquisition of Xilinx to create the “industry’s high-performance and adaptive computing leader,” marking the largest chip deal in history. With the acquisition, AMD is expanding beyond its purview of CPUs and GPUs with a large portfolio of reprogrammable chips called field programmable gate arrays, or FPGAs, that it said will significantly expand the company’s opportunities in data centers, embedded computing and telecommunications. Xilinx also has a footprint in other markets, like defense, broadcast and consumer electronics, which will help expand its total addressable market to $135 billion from $80 billion, according to AMD. | :AMD said it has completed its '''$49 billion''' acquisition of Xilinx to create the “industry’s high-performance and adaptive computing leader,” marking the largest chip deal in history. With the acquisition, AMD is expanding beyond its purview of CPUs and GPUs with a large portfolio of reprogrammable chips called field programmable gate arrays, or FPGAs, that it said will significantly expand the company’s opportunities in data centers, embedded computing and telecommunications. Xilinx also has a footprint in other markets, like defense, broadcast and consumer electronics, which will help expand its total addressable market to $135 billion from $80 billion, according to AMD. | ||

</i> | </i> | ||

| + | |||

| + | <!-- | ||

| + | |||

;Encontro 6 (28 fev.): | ;Encontro 6 (28 fev.): | ||

Edição das 22h23min de 10 de agosto de 2023

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 6 ENCONTROS

| Unidade 1 - Introdução a disciplina |

|---|

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 10 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

- 10 ENCONTROS

| Unidade 3 - Tipos de Dados e Operadores em VHDL |

|---|

Unidade 4 - Código Concorrente

- 4 ENCONTROS

| Unidade 4 - Código Concorrente |

|---|

Unidade 5 - Código Sequencial

- 7 ENCONTROS

| Unidade 5 - Código Sequencial |

|---|

Unidade 6 - Projeto a nível de Sistema

- 3 ENCONTROS

| Unidade 6 - Projeto a nível de Sistema |

|---|

Unidade 7 - Maquinas de Estado Finitas

- 3 ENCONTROS

| Unidade 7 - Maquinas de Estado Finitas |

|---|

Unidade 8 - Testbench

- 2 ENCONTROS

| Unidade 8 - Testbench |

|---|

Avaliações

Nas avaliações A1 e A2 vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - Unidade 1 a Unidade 4: dia XX/XX

- A2 - Unidade 5 a Unidade 7: dia XX/XX

- PF - Entrega do projeto final: dia 15/12

- R12 - Recuperação de A1 e A2 : dia 12/12

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN.

Atividade extra-classe (AE)

A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

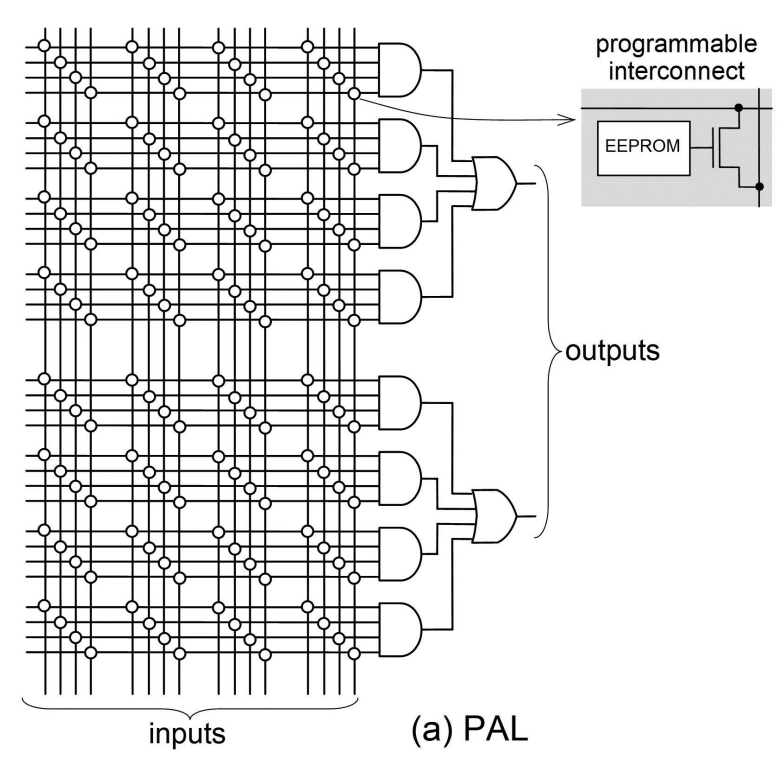

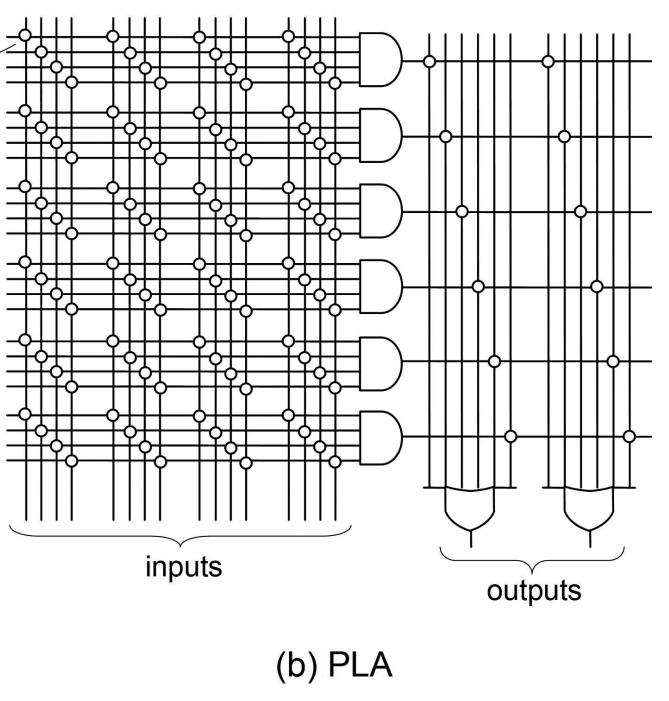

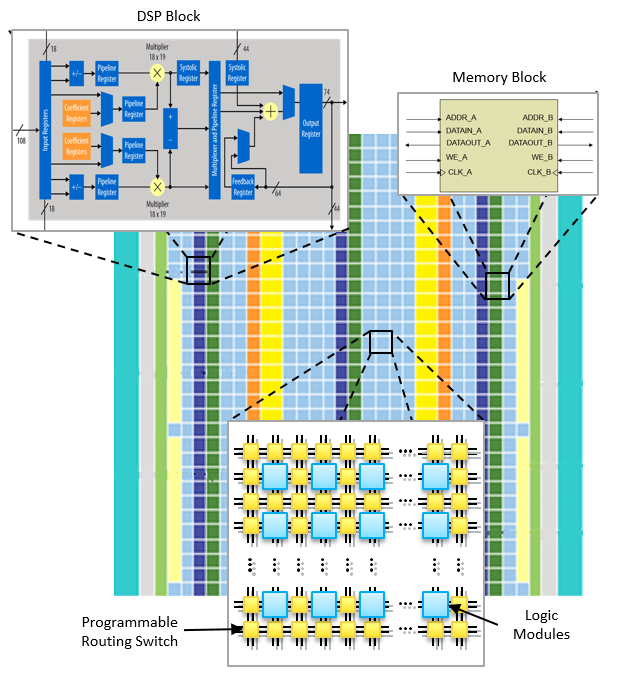

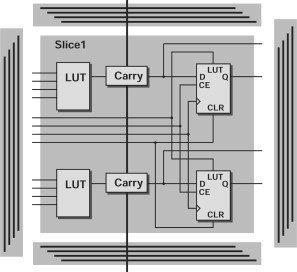

AE2 - Conhecendo os dispositivos lógicos programáveis

| AE2 - Conhecendo os dispositivos lógicos programáveis |

|---|

|