|

|

| Linha 4: |

Linha 4: |

| | {{collapse top | Unidade 1 - Introdução a disciplina}} | | {{collapse top | Unidade 1 - Introdução a disciplina}} |

| | | | |

| − | ;Aula 1 (6 Out): | + | ;Aula 1 (31 mar.): |

| | * [[DLP1-EngTel (Plano de Ensino) | APRESENTAÇÃO DA DISCIPLINA]] | | * [[DLP1-EngTel (Plano de Ensino) | APRESENTAÇÃO DA DISCIPLINA]] |

| | * Os materiais, prazos, documentação, histórico de trabalhos anteriores estão publicados nesta wiki. | | * Os materiais, prazos, documentação, histórico de trabalhos anteriores estão publicados nesta wiki. |

| Linha 14: |

Linha 14: |

| | * Para a comunicação entre professor-aluno, além dos avisos do [https://sigaa.ifsc.edu.br/sigaa/verTelaLogin.do Sistema Acadêmimco (SIGAA)], utilizaremos a [https://join.slack.com/t/dlp029006/shared_invite/zt-x8fdwxnk-q4UEEsbrvZfaS_ezhE_UyA plataforma SLACK]. Sugere-se que os alunos também a utilizem para comunicação entre eles, principalmente nos trabalhos em equipe. | | * Para a comunicação entre professor-aluno, além dos avisos do [https://sigaa.ifsc.edu.br/sigaa/verTelaLogin.do Sistema Acadêmimco (SIGAA)], utilizaremos a [https://join.slack.com/t/dlp029006/shared_invite/zt-x8fdwxnk-q4UEEsbrvZfaS_ezhE_UyA plataforma SLACK]. Sugere-se que os alunos também a utilizem para comunicação entre eles, principalmente nos trabalhos em equipe. |

| | | | |

| − | ;Aula 2 (7 Out): | + | ;Aula 2 (5 abr.): |

| | *Introdução aos dispositivos lógicos programáveis: | | *Introdução aos dispositivos lógicos programáveis: |

| | :* Conceito, tipos de PLDs | | :* Conceito, tipos de PLDs |

| Linha 48: |

Linha 48: |

| | ::* [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Major_manufacturers FPGA Major manufacturers] | | ::* [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Major_manufacturers FPGA Major manufacturers] |

| | ::* [http://www.vhdl.us/book/Pedroni_VHDL_3E_Chapter4.pdf Review of Field Programmable Gate Arrays (FPGAs)] by Volnei A. Pedroni | | ::* [http://www.vhdl.us/book/Pedroni_VHDL_3E_Chapter4.pdf Review of Field Programmable Gate Arrays (FPGAs)] by Volnei A. Pedroni |

| − | | + | <!-- |

| | ;Aula 3 (14 out): | | ;Aula 3 (14 out): |

| | * Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, RAM, DSP, Clock, PLL, I/O | | * Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, RAM, DSP, Clock, PLL, I/O |

| Linha 91: |

Linha 91: |

| | ;Curiosidades do mundo digital: | | ;Curiosidades do mundo digital: |

| | *[https://www.computerhistory.org/siliconengine/timeline/ The Silicon Engine Timeline] | | *[https://www.computerhistory.org/siliconengine/timeline/ The Silicon Engine Timeline] |

| − | | + | --> |

| | {{collapse bottom}} | | {{collapse bottom}} |

| − | | + | <!-- |

| | ===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== | | ===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== |

| | * 5 ENCONTROS | | * 5 ENCONTROS |

| Linha 412: |

Linha 412: |

| | No dia 12 será refeito o circuito, testado novamente (Passo 3) e acrescentado o circuito de anti-repique sugerido | | No dia 12 será refeito o circuito, testado novamente (Passo 3) e acrescentado o circuito de anti-repique sugerido |

| | {{collapse bottom}} | | {{collapse bottom}} |

| − | | + | --> |

| | + | <!-- |

| | ===Unidade 3 - Tipos de Dados e Operadores em VHDL=== | | ===Unidade 3 - Tipos de Dados e Operadores em VHDL=== |

| | * 9 AULAS | | * 9 AULAS |

| Linha 1 696: |

Linha 1 697: |

| | | | |

| | {{collapse bottom}} | | {{collapse bottom}} |

| − | | + | --> |

| | + | <!-- |

| | ===Unidade 4 - Código Concorrente=== | | ===Unidade 4 - Código Concorrente=== |

| | * 4 AULAS | | * 4 AULAS |

| Linha 1 972: |

Linha 1 974: |

| | * Detector de paridade | | * Detector de paridade |

| | {{collapse bottom}} | | {{collapse bottom}} |

| − | | + | --> |

| | + | <!-- |

| | ===Unidade 5 - Código Sequencial=== | | ===Unidade 5 - Código Sequencial=== |

| | * 4 ENCONTROS | | * 4 ENCONTROS |

| Linha 2 430: |

Linha 2 433: |

| | --> | | --> |

| | {{collapse bottom}} | | {{collapse bottom}} |

| − | | + | --> |

| | + | <!-- |

| | ===Unidade 6 - Projeto a nível de Sistema=== | | ===Unidade 6 - Projeto a nível de Sistema=== |

| | * 4 AULAS | | * 4 AULAS |

| Linha 2 740: |

Linha 2 744: |

| | | | |

| | {{collapse bottom}} | | {{collapse bottom}} |

| − | | + | --> |

| | + | <!-- |

| | ===Unidade 7 - Maquinas de Estado Finitas=== | | ===Unidade 7 - Maquinas de Estado Finitas=== |

| | {{collapse top| expand=true | Unidade 7 - Maquinas de Estado Finitas}} | | {{collapse top| expand=true | Unidade 7 - Maquinas de Estado Finitas}} |

| Linha 2 974: |

Linha 2 979: |

| | --> | | --> |

| | {{collapse bottom}} | | {{collapse bottom}} |

| − | | + | --> |

| | + | <!-- |

| | ===Unidade 8 - Projeto Final=== | | ===Unidade 8 - Projeto Final=== |

| | {{collapse top| expand=true | Unidade 8 - Projeto Final}} | | {{collapse top| expand=true | Unidade 8 - Projeto Final}} |

| Linha 2 986: |

Linha 2 992: |

| | | | |

| | {{collapse bottom}} | | {{collapse bottom}} |

| − | | + | <!-- |

| | ==Avaliações== | | ==Avaliações== |

| | Nas avaliações A1 e A2 serão realizadas de forma presencial e vocês poderão consultar apenas as folhas entregues: | | Nas avaliações A1 e A2 serão realizadas de forma presencial e vocês poderão consultar apenas as folhas entregues: |

| Linha 4 010: |

Linha 4 016: |

| | *A imagem do RTL do projeto (e dos componentes), não é necessário expandir os componentes até o nível de implementação. | | *A imagem do RTL do projeto (e dos componentes), não é necessário expandir os componentes até o nível de implementação. |

| | {{collapse bottom}} | | {{collapse bottom}} |

| | + | --> |

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

| Unidade 1 - Introdução a disciplina

|

- Aula 1 (31 mar.)

- APRESENTAÇÃO DA DISCIPLINA

- Os materiais, prazos, documentação, histórico de trabalhos anteriores estão publicados nesta wiki.

- A PÁGINA DA DISCIPLINA contem os materiais que não alteram entre semestre.

- Nesta página está o REGISTRO DIÁRIO E AVALIAÇÕES.

- Para a realização e entrega das atividades será utilizada a PLATAFORMA MOODLE. Chave para auto inscrição (engtelecom_aluno)

- Durante a pandemia do COVID19 os encontros síncronos serão realizados através da plataforma Google Meet. Os encontros (havendo a concordância de todos) serão gravados, e ocorrerão nos horários normais das aulas. As aulas terão duração de 1h15 minutos com possibilidade de ainda acrescer 15 minutos previstos para esclarecimento de dúvidas. As gravações ficarão disponíveis por 30 dias no Drive do aluno, mas não poderão ser baixadas por limitação do sistema.

- Além dos horários de aula síncrona, serão agendados horários de ATENDIMENTO EXTRACLASSE para que os alunos possam tirar dúvidas da disciplina ou das ferramentas de ensino.

- Para a comunicação entre professor-aluno, além dos avisos do Sistema Acadêmimco (SIGAA), utilizaremos a plataforma SLACK. Sugere-se que os alunos também a utilizem para comunicação entre eles, principalmente nos trabalhos em equipe.

- Aula 2 (5 abr.)

- Introdução aos dispositivos lógicos programáveis:

-

- SPLD: PAL, PLA e GAL

- CPLDs

-

- Fabricantes de DLPs/FPGAs e familias de DLPs atuais.

-

|

|}

-->

- FUNCTION e PROCEDURE (são chamados de subprogramas), e podem ser construídos em um PACKAGE, ENTITY, ARCHITECTURE, ou PROCESS.

A instrução ASSERT é útil para verificar as entradas de um subprograma. Seu propósito não é criar circuito, mas assegurar que certos requisitos são atendidos durante a síntese e/ou simulação. Pode ser condicional ou incondicional (condição_booleana = FALSE). A sintaxe da instrução é:

[rótulo:] assert condição_booleana

[report mensagem]

[severity nivel_severidade];

A mensagem pode ser criada usando STRINGs que podem ser concatenadas.

O nível de severidade pode ser NOTE (para passar informação para o compilador/simulator), WARNING (para informar que algo não usual ocorreu), ERROR (para informar que alguma condição não usual "sério" ocorreu), ou FAILURE (para informar que uma condição não aceitável ocorreu). Normalmente o compilador para quando ocorre um ERROR ou FAILURE. ERROR é o valor "default" [1].

- A FUNCTION: declaração, uso, mapeamento posicional x nominal, PURE x IMPURE.

function nome_funçao (lista_parametros_entrada) return tipo_saida is

declarações

begin

afirmações sequenciais

end function;

- A PROCEDURE: declaração e uso

procedure nome_procedimento (lista_parâmetros_entrada, lista_parâmetros_saída) is

declarações

begin

afirmações sequenciais

end procedure;

- Exemplos de uso ASSERT, FUNCTION e PROCEDURE

- Exemplo: Cálculo do log2 de um número inteiro. Pode ser usado para determinar o número de bits necessário para um número natural.

function log2c (n : integer) return integer is

variable m , p : integer;

begin

m := 0;

p : = 1;

while p < n loop

m : = m + 1;

p := p * 2;

end loop;

return m;

end log2c;

- Exemplo: Declaração de FUNCTION em ARCHITECTURE Ex.9.1

- Aplicação no projeto do timer0_9

- Exemplo: Declaração em FUNCTION PACKAGE Ex. 9.2

-- FILE: comparator.vhd

-- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010.

library ieee;

use ieee.numeric_std.all;

use work.my_package.all;

entity organizer is

generic (size : natural := 3);

port

(

x : in UNSIGNED(2 to 5);

y : out UNSIGNED(size - 1 downto 0)

);

end entity;

architecture organizer of organizer is

begin

y <= order_and_fill(x, size);

end architecture;

-- FILE: my_pkg.vhd

-- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335

library ieee;

use ieee.numeric_std.all;

package my_package is

function order_and_fill (input : UNSIGNED; bits : natural) return UNSIGNED;

end package;

package body my_package is

function order_and_fill (input : UNSIGNED; bits : natural) return UNSIGNED is

variable a : UNSIGNED(input'LENGTH - 1 downto 0);

variable result : UNSIGNED(bits - 1 downto 0);

begin

assert (input'LENGTH <= bits)

report "Improper input size!"

severity FAILURE;

if (input'LEFT > input'RIGHT) then

a := input;

else

for i in a'range loop

a(i) := input(input'LEFT + i);

end loop;

end if;

if (a'LENGTH < bits) then

result(bits - 1 downto a'LENGTH) := (others => '0');

result(a'LENGTH - 1 downto 0) := a;

else

result := a;

end if;

return result;

end function;

end package body;

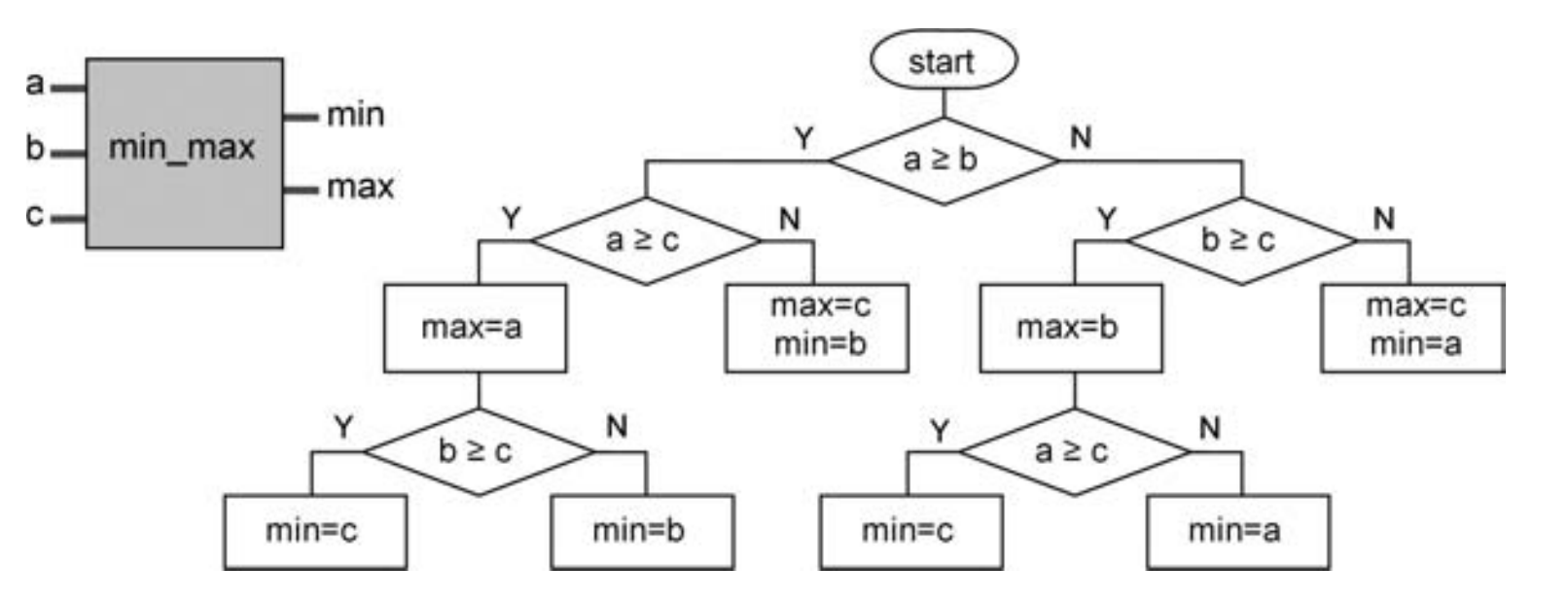

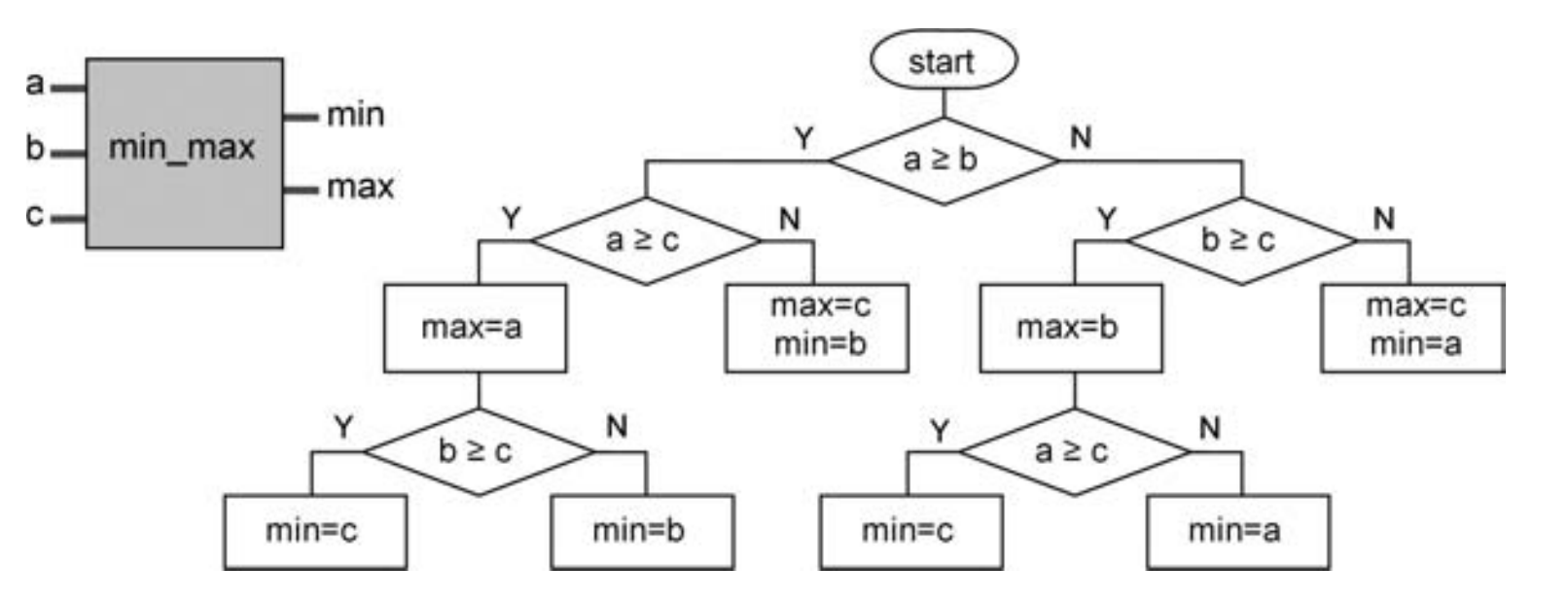

Figura 6.1 - Fluxograma da PROCEDURE min_max

Fonte: pag. 232 de [1].

Fonte: pag. 232 de [1].

-- FILE: comparator.vhd

-- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010.

use work.my_package.all;

entity comparator is

port

(

a, b, c : in integer range 0 to 255;

min, max : out integer range 0 to 255

);

end entity;

architecture comparator of comparator is

begin

min_max(a, b, c, min, max);

end architecture;

-- FILE: my_pkg.vhd

-- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010.

package my_package is

procedure min_max (

signal a, b, c : in integer;

signal min, max : out integer

);

end package;

package body my_package is

procedure min_max (

signal a, b, c : in integer range 0 to 255;

signal min, max : out integer range 0 to 255) is

begin

if (a >= b) then

if (a >= c) then

max <= a;

if (b >= c) then

min <= c;

else

min <= b;

end if;

else

max <= c;

min <= b;

end if;

else

if (b >= c) then

max <= b;

if (a >= c) then

min <= c;

else min <= a;

end if;

else

max <= c;

min <= a;

end if;

end if;

end procedure;

end package body;

- Exercícios: 9.1 a 9.4, 9.6 a 9.9

- Ver pag. 213 a 239 de [1])

- Aula 43 e 44 (12 mar) (presencial - Sábado 8h00 as 11h30)

- AE12 - Laboratório de programação de FPGA - Relógio Digital de 24 horas

|}

-->

- Aula 45 (15 mar)

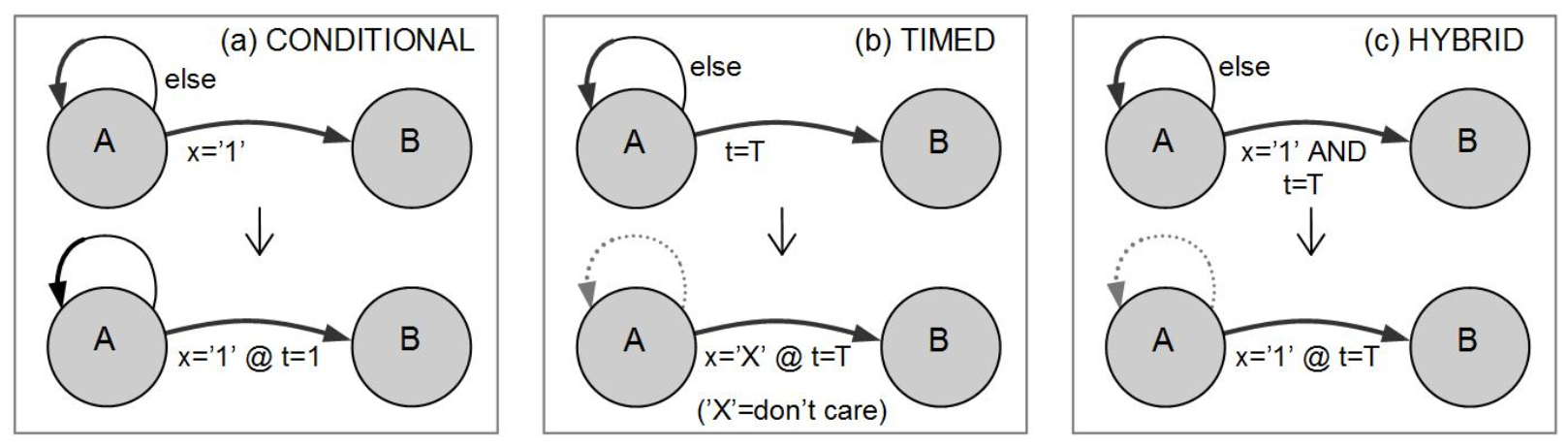

- Projeto de FSM temporizadas (nas quais as transições são ativadas também pelo tempo).

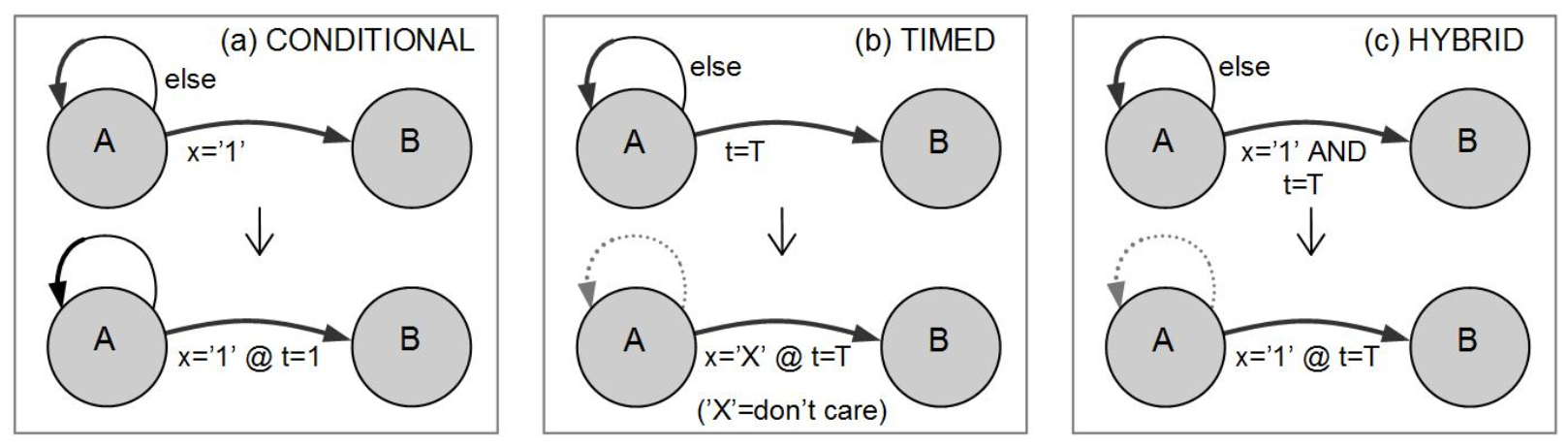

Figura 7.9 - Tipos de FSM (Condicional, Temporizada e Hibrida)

Fonte: Figura 11.12 de [1].

Fonte: Figura 11.12 de [1].

- Modelo de FSM temporizada

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

----------------------------------------------------------

ENTITY < entity_name > IS

PORT (

clk, rst : IN STD_LOGIC;

input : IN < data_type > ;

output : OUT < data_type >);

END entity;

----------------------------------------------------------

ARCHITECTURE < architecture_name > OF < entity_name > IS

TYPE state IS (A, B, C, ...);

SIGNAL pr_state, nx_state : state;

signal timer: integer range 0 to MAX;

-- ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute

-- ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential";

BEGIN

------Logica Sequencial da FSM:------------

PROCESS (clk, rst)

variable count: integer range o to MAX;

BEGIN

IF (rst = '1') THEN

pr_state <= A;

count := 0;

ELSIF (clk'EVENT AND clk = '1') THEN

count := count + 1;

if (count >= timer) then

pr_state <= nx_state;

count := 0;

end if;

END IF;

END PROCESS;

------Logica Combinacional da FSM:------------

PROCESS (pr_state, input)

BEGIN

------Valores default das saidas------------

output <= < value >;

------Valores default do timer------------

timer <= <value>;

CASE pr_state IS

WHEN A =>

output <= < value > ; -- apenas se diferente do valor default

IF (input =< value >) THEN

timer <= <value>; -- apenas se diferente do valor default

nx_state <= B;

...

ELSE

timer <= <value>; -- apenas se diferente do valor default

nx_state <= A;

END IF;

WHEN B =>

output <= < value > ; -- apenas se diferente do valor default

IF (input =< value >) THEN

timer <= <value>; -- apenas se diferente do valor default

nx_state <= C;

...

ELSE

timer <= <value>; -- apenas se diferente do valor default

nx_state <= B;

END IF;

WHEN ...

END CASE;

END PROCESS;

------Seção de Saída (opcional):-------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

new_output <= < value > ;

ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0'

new_output <= output;

END IF;

END PROCESS;

END architecture;

- Ver pag. 298 a 301 de [1]

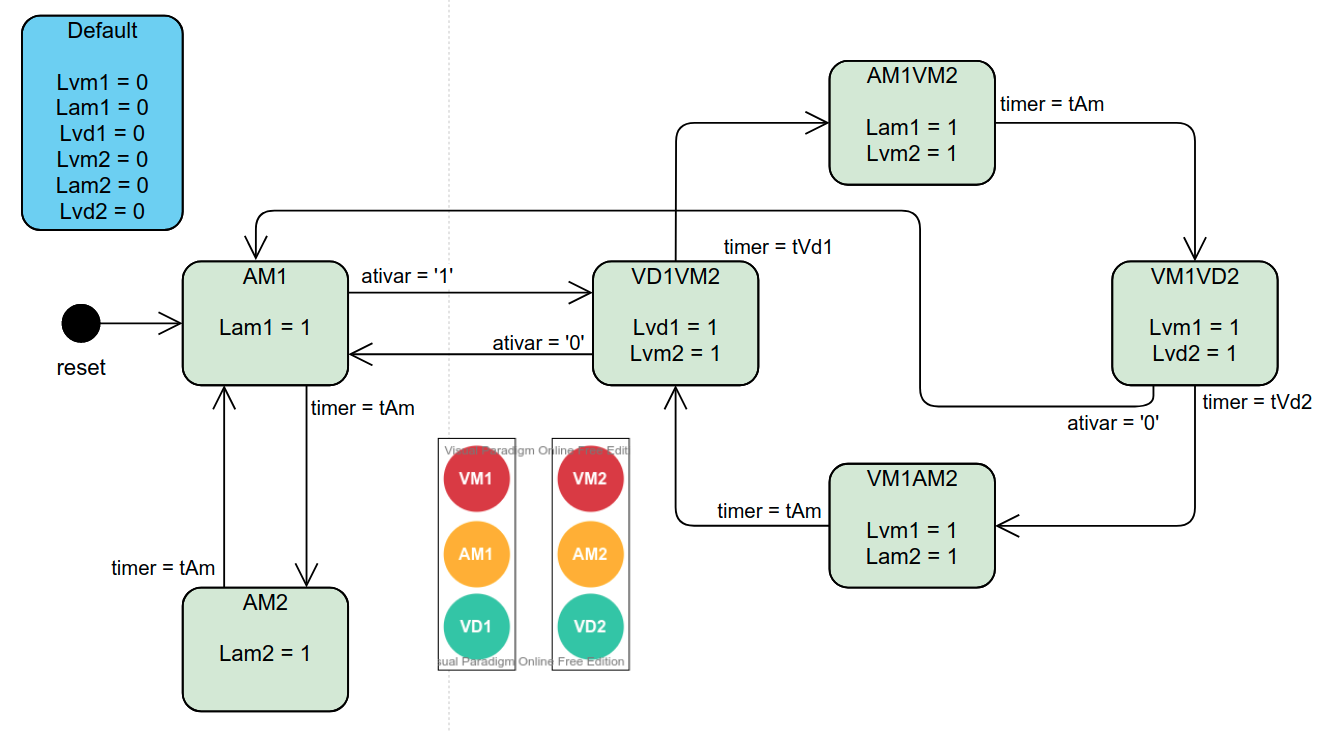

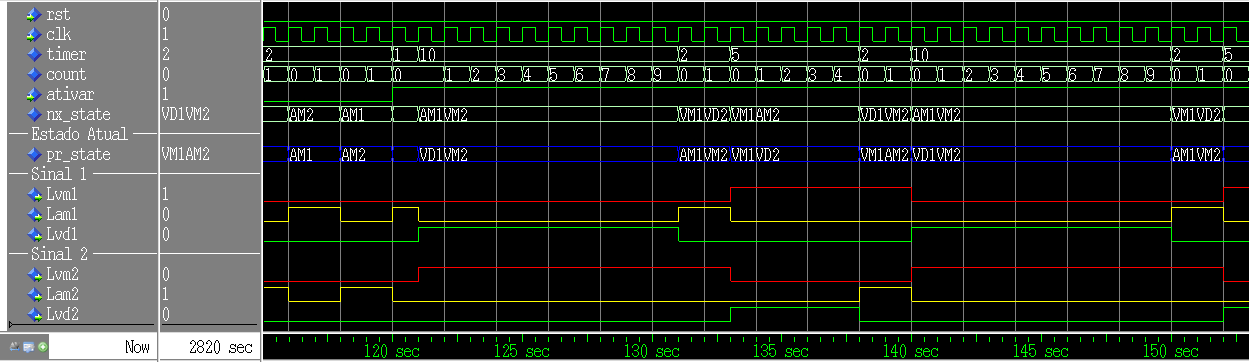

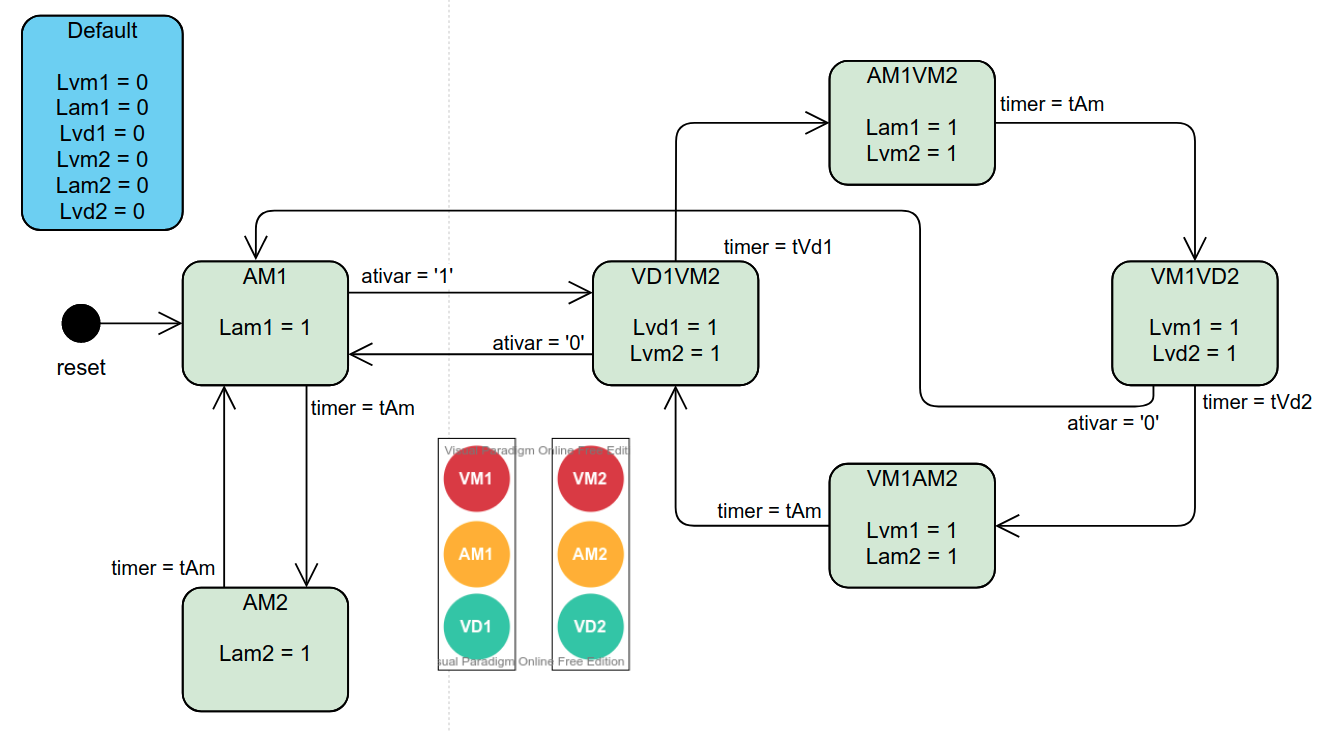

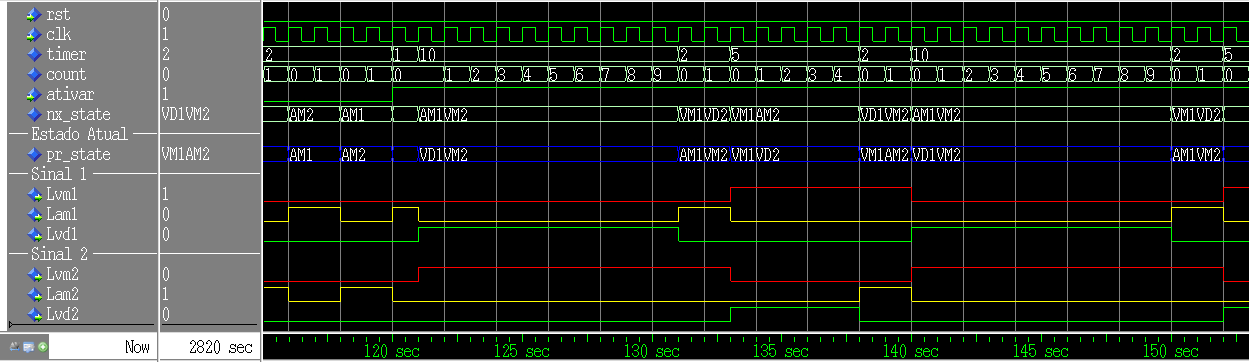

- Exemplo de FSM temporizada - semáforo temporizado

- Usando o template acima descreva em VHDL a FSM de um controlador de semáforo Regular indicado pela FSM da figura abaixo:

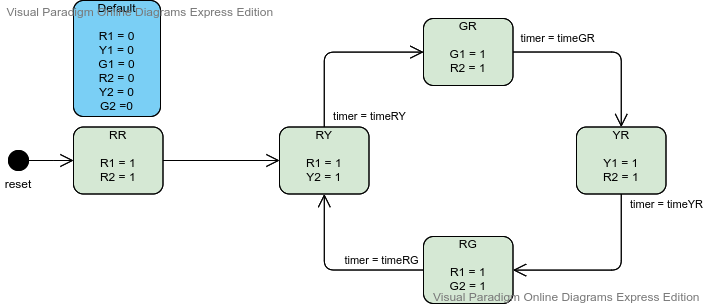

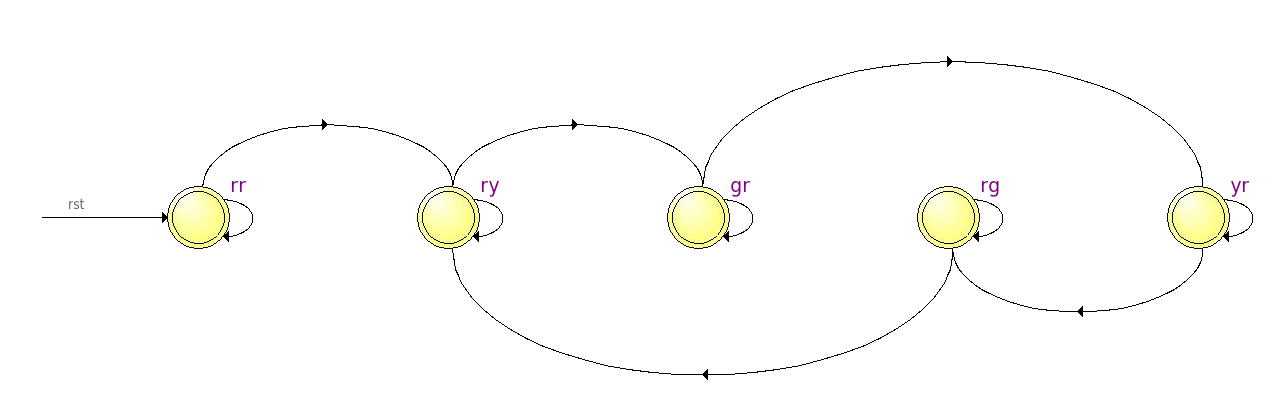

Figura 7.10 - Diagrama de estados do controlador de semáforo

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

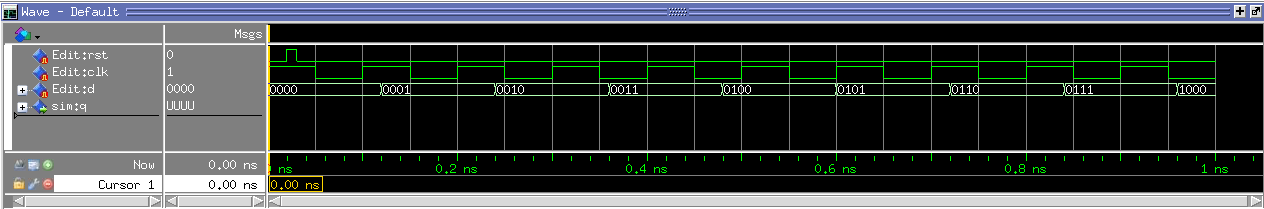

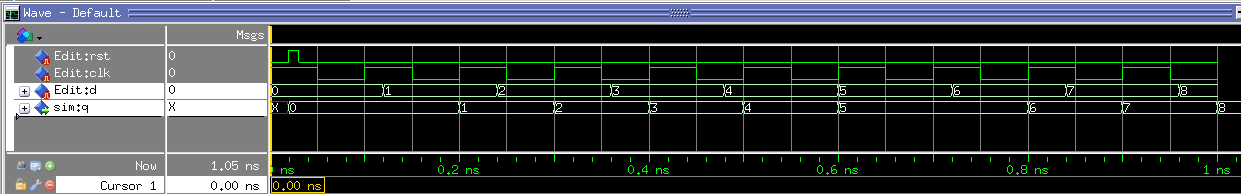

Figura 7.11 - Simulação do controlador de semáforo no Modelsim

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

| Exercício - Semaforo

|

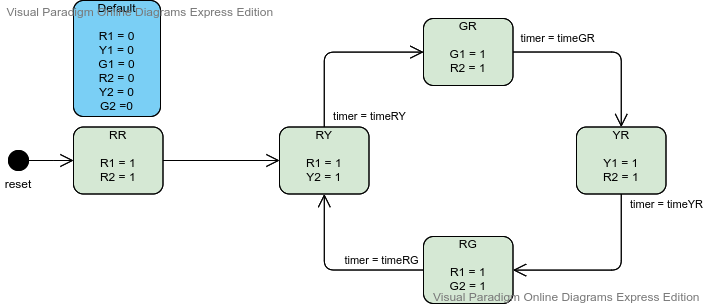

- Usando o template acima descreva em VHDL a FSM de um controlador de semáforo Regular da Figura 11.15 (pag. 304 de [1]).

Figura 7.12 - Diagrama de estados do controlador de semáforo

Fonte: Adaptado de Figura 11.15 de [1].

Fonte: Adaptado de Figura 11.15 de [1].

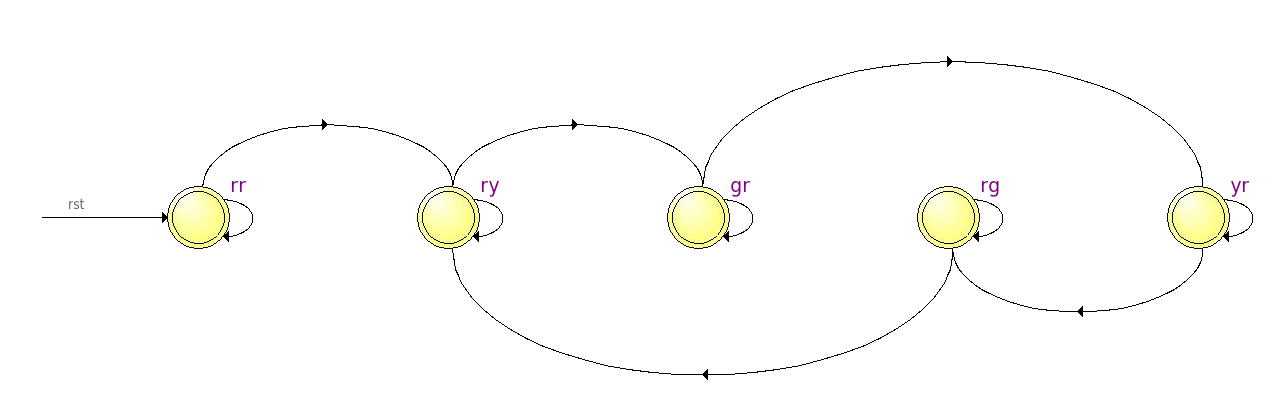

Figura 7.13 - Diagrama de estados do Quartus do controlador de semáforo

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

|

-->

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

A soma das atividades Extra-classe será correspondente a 25% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle da disciplinas, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

AE1 - Palavras-cruzadas INTRODUÇÃO

| AE1 - Palavras-cruzadas INTRODUÇÃO

|

- BÔNUS

- 0,3 pontos na avaliação A1 -

- 0,2 pontos na avaliação A1 -

- 0,1 pontos na avaliação A1 -

|

AE2 - Conhecendo os dispositivos lógicos programáveis

| AE2 - Conhecendo os dispositivos lógicos programáveis

|

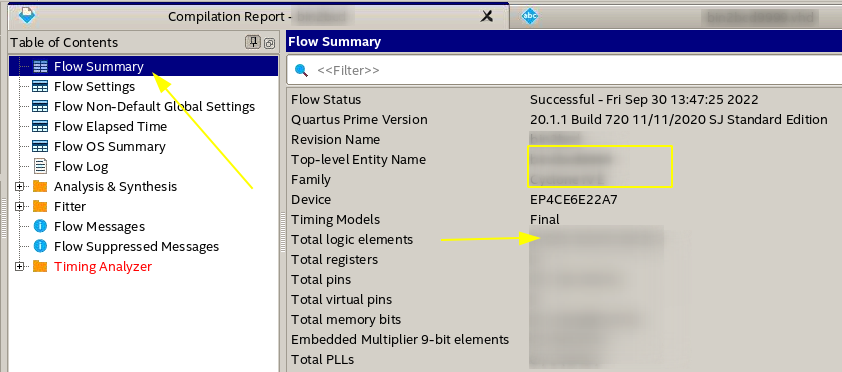

- Atividade

- Ao escolher a família de FPGAS, escolha inicialmente um dispositivo da família Cyclone II.

- Capture as telas solicitadas e depois utilize-as em um relatório da atividade.

- Anote o tempo utilizado para cada uma das etapas do processo de compilação

- Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo.

- Anote algum erro (Error) ou alertas (Warnings) que o Quartus II indicar no painel de mensagens [Messages]

- Ao final salve o projeto em um arquivo QAR (sugestão PJ1.QAR)

- Em seguida escolha um dos seguintes dispositivos e repita todo o procedimento:

- Modifique a família para Cyclone IV E e use um dispositivo para EP4CE****, e observe as mudanças que ocorre tanto no tipo de Elemento Lógico, no Chip Planner, e no Pin Planner, e no circuito dos pinos de I/O. Note que este FPGA também apresenta novos componentes, tais como: Memória, Multiplicadores, PLLs. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documento o que encontrar.

- Modifique a família para Stratix II GX e use o dispositivo para EP2SGX****, e observe as mudanças que ocorre tanto no tipo de Elemento Lógico, no Chip Planner, e no Pin Planner, e no circuito dos pinos de I/O. Note que este FPGA também apresenta novos componentes, tais como: Memória, Elementos DSP, PLL, DLL. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documento o que encontrar.

- Procure comparar os resultados obtidos nos dois procedimentos.

- Entregas

- Envie dois arquivos QAR contendo todos os arquivos necessário para compilar os dois projetos.

- Envie um relatório em PDF, incluindo as imagens capturadas (inclua legenda em cada figura) e escreva para cada imagem um texto comentando o que representa. O relatório também deve ter a identificação (autor, título, data) uma breve introdução e uma conclusão. A descrição dos procedimentos feita na página wiki não precisa incluída no relatório.

- Use preferencialmente o Overleaf para gerar o relatório. Mas o uso de MS-Word, Libreoffice e Google Docs também é permitida.

- A entrega será feita através do Moodle da disciplina. Observe o prazo de entrega.

|

AE3 - SNCT 2021 | 5G e Conectividade com IoT

| AE3 - SNCT 2021

|

| 5G e Conectividade com IoT

|

|

Após assistir a palestra e debate do dia de hoje, seguem algumas perguntas que devem ser respondidas em um PDF.

- Cite os palestrantes do evento de hoje.

- Dentro da parte inicial apresentada pelo Fabrício Sgambati, qual foi a parte que mais te impressionou? Escreva umas 10 linhas sobre o tópico.

- Qual foi a tua avaliação sobre o evento de hoje? Comente o que achou.

- Qual dos palestrantes trouxe a informação que mais te interessou? Justifique.

|

AE4 - Programação do kit Mercurio IV

| AE4 - Programação do kit Mercurio IV

|

- Objetivos

- Revisar o processo de programação do FPGA usando um kit de desenvolvimento

- Fazer as adaptações necessárias para o circuito funcionar no kit

- Verificar e corrigir o problema do repique (bouncing) da chave usada no CLK

- Procedimento de laboratório

- Passo 1

- Escrever o código do projeto counter (já simulado em aula anterior), incluindo as adaptações necessárias para o uso dos LEDs da matriz de leds do kit Mercurio IV.

entity counter is

generic (WIDTH : in natural := 4);

port (

RST : in std_logic;

CLK : in std_logic;

LOAD : in std_logic;

DATA : in std_logic_vector(WIDTH-1 downto 0);

R0 : out std_logic

Q : out std_logic_vector(WIDTH-1 downto 0));

end entity;

architecture ifsc_v1 of counter is

signal Q_aux : std_logic(WIDTH-1 downto 0);

begin

process(RST,CLK) is

begin

if RST = '1' then

Q_aux <= (others => '0');

elsif rising_edge(CLK) then

if LOAD= '1' then

Q_aux <= DATA;

else

Q_aux <= std_logic_vector(unsigned(Q_aux) + 1);

end if;

end if;

end process;

-- Adaptacao feita devido a matriz de leds acender com ZERO

Q <= not Q_aux;

-- Para acender um led eh necessario colocar ZERO na linha correspondente da matriz.

R0 <= '0';

end architecture;

- Passo 2

- Escolher o DEVICE: EP4CE30F23C7

- Usar como pinos de entrada e saída do FPGA os seguintes:

CLK: PIN_Y17 ou PIN_V21

DATA[3]: PIN_H18

DATA[2]: PIN_H20

DATA[1]: PIN_K21

DATA[0]: PIN_J21

LOAD: PIN_Y22

Q[3]: PIN_J6

Q[2]: PIN_K8

Q[1]: PIN_J8

Q[0]: PIN_L8

RST: PIN_W21

R0: PIN_F10

- Passo 3

- Realizar os seguintes testes, acionando as chaves e observando o resultado nos LEDs:

- Carregar um valor nas chaves DATA[3..0], mudar LOAD para ALTO e acionar a chave CLK. Verificar e anotar o comportamento. Repetir com valores diferentes nas DATA[3..0].

- Mudar RST para ALTO, e verificar e anotar o comportamento.

- Manter LOAD em BAIXO e acionar a chave CLK várias vezes (no mínimo 16 vezes). Verificar e anotar o comportamento. O comportamento é o esperado para o número de mudanças da chave CLK?

- Dica

- Se desejar desligar a luz do LCD, basta fixar o pino LCD_BACKLIGHT (V10) - Controlador do backlight em '0'.

-- insira na declaração das portas da entity a linha

LCD_BACKLIGHT: out std_logic;

-- insira na architecture a linha

LCD_BACKLIGHT <= '0';

- Após fazer a Análise e Síntese, defina o pino v10 para essa porta.

LCD_BACKLIGHT: PIN_V10

- Passo 4

- Eliminar o repique da chave CLK, inserindo no código um circuito anti-repique, com um tempo de anti-repique de 10ms:

entity COUNTER_db is

...

CLK50MHz : in std_logic;

...

end entity

architecture ifsc_v2 of COUNTER_db is

...

signal CLK_db: std_logic := '0';

...

begin

-- debouncer de 10ms

process (CLK50MHz, CLK, RST, CLK_db) is

constant max_cnt: natural := 500000; -- 500000 10ms para clk 20ns

variable cnt_db : integer range 0 to max_cnt-1;

begin

if (RST = '1') then

cnt_db := 0;

CLK_db <= '0';

elsif ((CLK = '0') and (CLK_db = '0')) or

((CLK = '1') and (CLK_db = '1')) then

cnt_db := 0;

elsif (rising_edge(CLK50MHz)) then

if (cnt_db = max_cnt - 1) then

CLK_db <= not CLK_db;

else

cnt_db := cnt_db + 1;

end if;

end if;

end process;

...

-- Troque no process(RST,CLK) a entrada '''CLK''' do circuito anterior pela entrada '''CLK_db'''

- Acrescentar o pinos de entrada CLK50MHz:

CLK50MHz: PIN_T1

- acrescente um arquivo para restringir a análise temporal (Timing Analysis) a 50MHz para a entrada de clock CLK50MHz

- Restringir a frequencia máxima de clock no Quartus II

create_clock -name CLK50MHz -period 50MHz [get_ports -no_case {clk*}]

- Passo 5

- Repita os teste feitos no Passo 3, acionando as chaves e observando o resultado nos LEDs:

- Carregar um valor nas chaves DATA[3..0], mudar LOAD para ALTO e acionar a chave CLK. Verificar e anotar o comportamento. Repetir com valores diferentes nas DATA[3..0].

- Mudar RST para ALTO, e verificar e anotar o comportamento.

- Manter LOAD em BAIXO e acionar a chave CLK várias vezes (no mínimo 16 vezes). Verificar e anotar o comportamento. O comportamento é o esperado para o número de mudanças da chave CLK?

- Reduza o tempo do circuito anti-repique para 1us (microsegundo) max_cnt = 50, e verifique o funcionamento da chave CLK

- Relatório Técnico

- Documentar o experimento em um relatório técnico que contenha no mínimo:

- identificação (título, disciplina, data, autores);

- introdução;

- descrição do procedimento realizado;

- resultados obtidos (com imagens dos itens importantes) e análise dos resultados;

- conclusão.

- apêndice (se desejar pode ser disponibilizados vídeos do funcionamento do circuito nos Passos 3 e 5

- O relatório deve também responder as questões levantadas e mostrar que os objetivos apresentados na introdução foram atendidos.

|

AE5 - Desafio das vagas de garagem

| AE5 - Desafio das vagas de garagem

|

- Atividade

- Ao escolher a família de FPGAS, escolha inicialmente um dispositivo da família Cyclone II.

- Capture as telas solicitadas e depois utilize-as em um relatório da atividade.

- Anote o tempo utilizado para cada uma das etapas do processo de compilação

- Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo.

- Anote algum erro (Error) ou alertas (Warnings) que o Quartus II indicar no painel de mensagens [Messages]

- Ao final salve o projeto em um arquivo QAR (sugestão PJ1.QAR)

- Em seguida escolha um dos seguintes dispositivos e repita todo o procedimento:

- Modifique a família para Cyclone IV E e use um dispositivo para EP4CE****, e observe as mudanças que ocorre tanto no tipo de Elemento Lógico, no Chip Planner, e no Pin Planner, e no circuito dos pinos de I/O. Note que este FPGA também apresenta novos componentes, tais como: Memória, Multiplicadores, PLLs. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documento o que encontrar.

- Modifique a família para Stratix II GX e use o dispositivo para EP2SGX****, e observe as mudanças que ocorre tanto no tipo de Elemento Lógico, no Chip Planner, e no Pin Planner, e no circuito dos pinos de I/O. Note que este FPGA também apresenta novos componentes, tais como: Memória, Elementos DSP, PLL, DLL. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documento o que encontrar.

- Procure comparar os resultados obtidos nos dois procedimentos.

- Entregas

- O relatório técnico em PDF deverá documentar o projeto e testes realizados,

- Documentar o experimento em um relatório técnico que contenha no mínimo: identificação (título, disciplina, data, autores); introdução; descrição do procedimento realizado para simular os circuitos; resultados obtidos (com imagens dos itens importantes) e análise dos resultados, comparando as 4 soluções implementadas; conclusão; apêndice (coloque os códigos dos 4 circuitos implementados).

- Envie um arquivo QAR contendo todos os arquivos necessário para compilar as diferentes versões (3 ou 4 circuitos).

- Recomenda-se que se utilize como nome dos arquivos VHDL algo como circuitoX.vhd e para os arquivos de simulação tb_circuitoX.vwf. Todos os arquivos devem preferencialmente ficar em um único projeto e QAR.

- Use preferencialmente o Overleaf para gerar o relatório. Mas o uso de MS-Word, Libreoffice e Google Docs também é permitida.

- A entrega será feita através do Moodle da disciplina. Observe o prazo de entrega.

|

AE6 - Conversor de binário para BCD

| AE6 - Conversor de binário para BCD

|

- Atividades

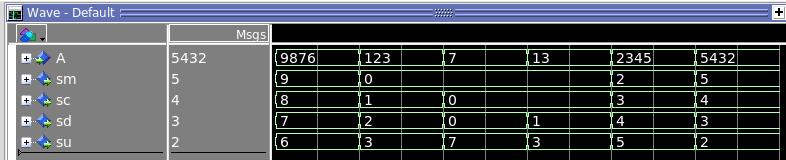

Neste laboratório remoto, os alunos deverão implementar uma ou mais soluções do para um circuito conversor de binário para BCD (bin2bcd) com entrada binária variando de 0 a 999.

- Baseado no exemplo do conversor de binário para BCD - Binary-coded decimal de dois dígitos decimais (00 a 99), mostrado em aula, projete um conversor para 3 dígitos (000 a 999).

- Escreva o código em VHDL, que dada uma entrada C (entre 0 e 999), fornece nas saídas os dígitos da centena (sc), dezena (sd) e unidade (su).

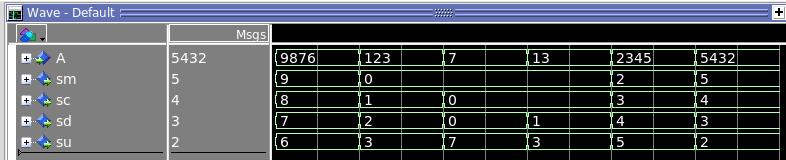

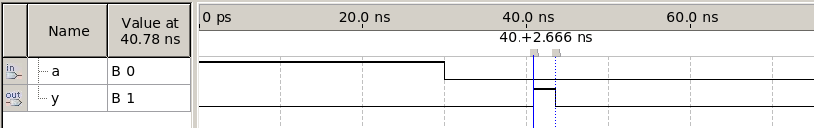

Figura AE6(a) - Exemplo de simulação funcional

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

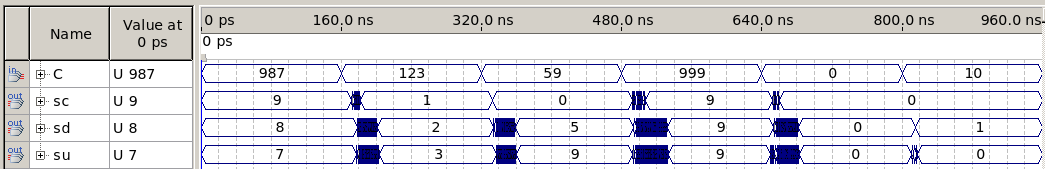

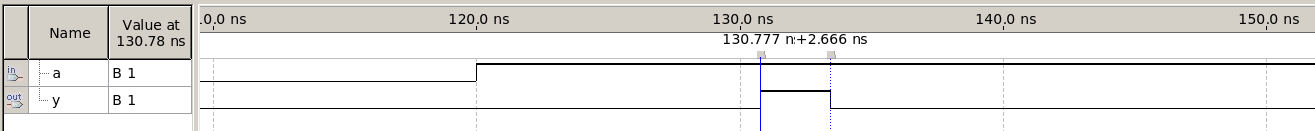

Figura AE6(b) - Exemplo de simulação temporal

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Anote a quantidade de elementos lógicos do circuito.

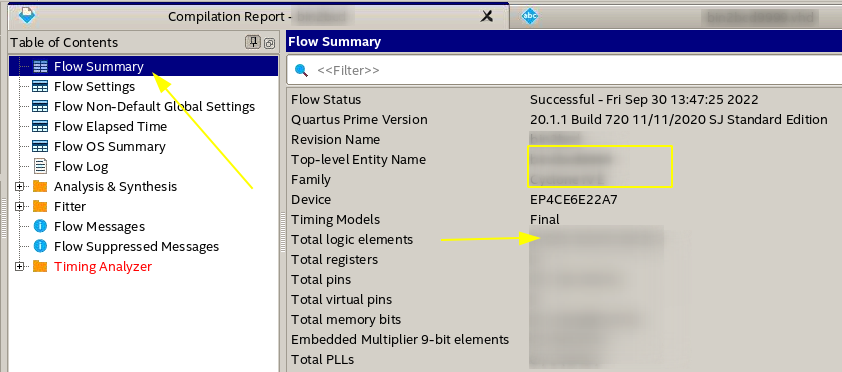

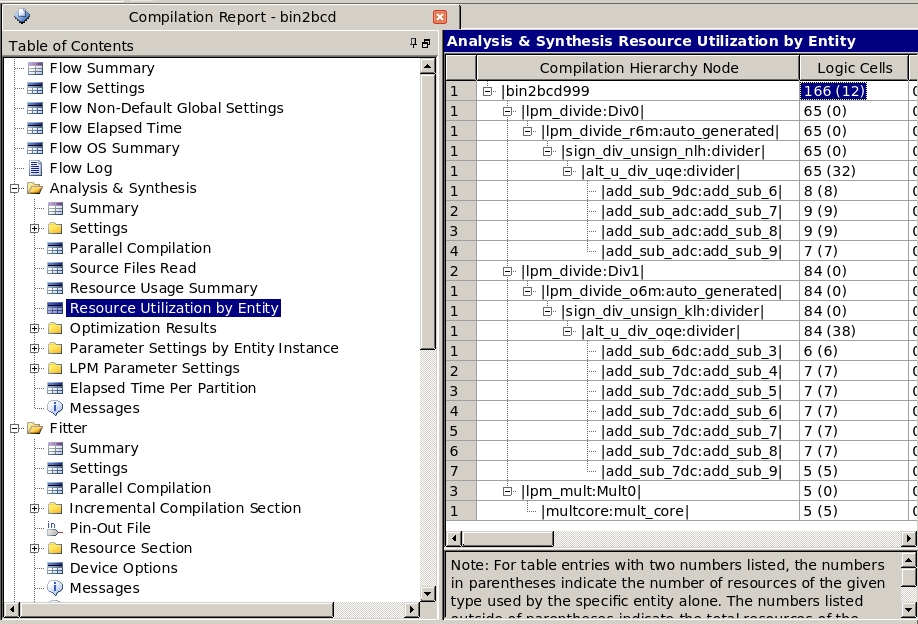

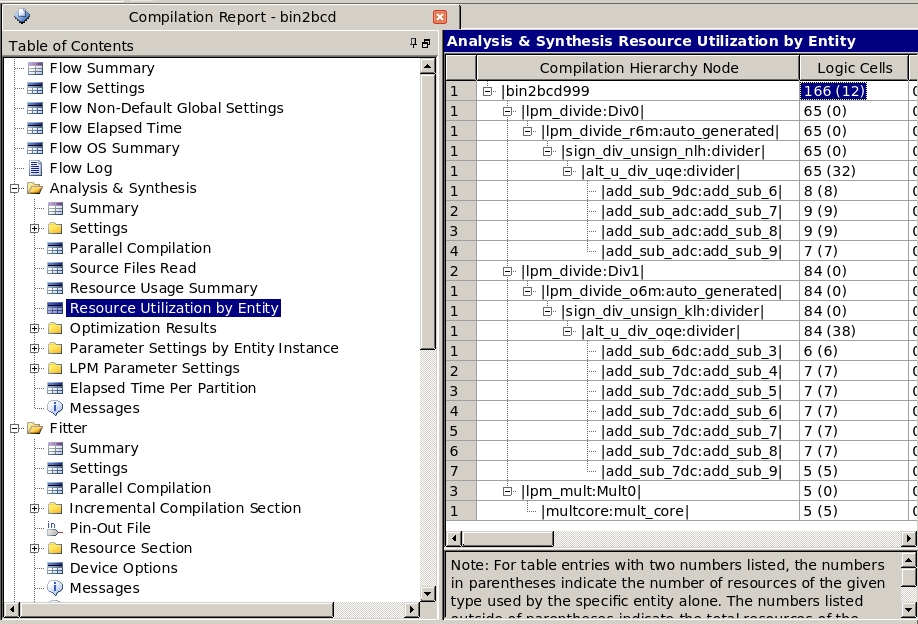

Figura AE6(c) - Exemplo de número de elementos (166)

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura AE6(d) - Exemplo de número de elementos (166)

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

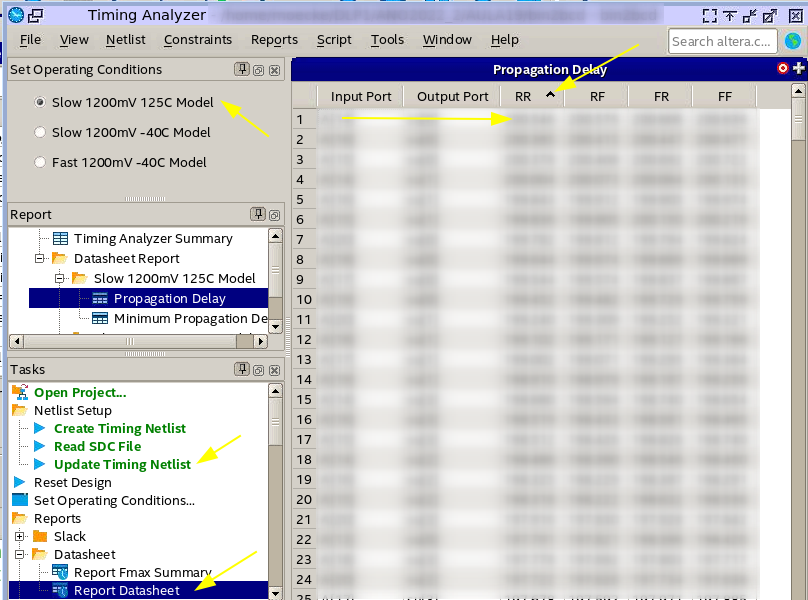

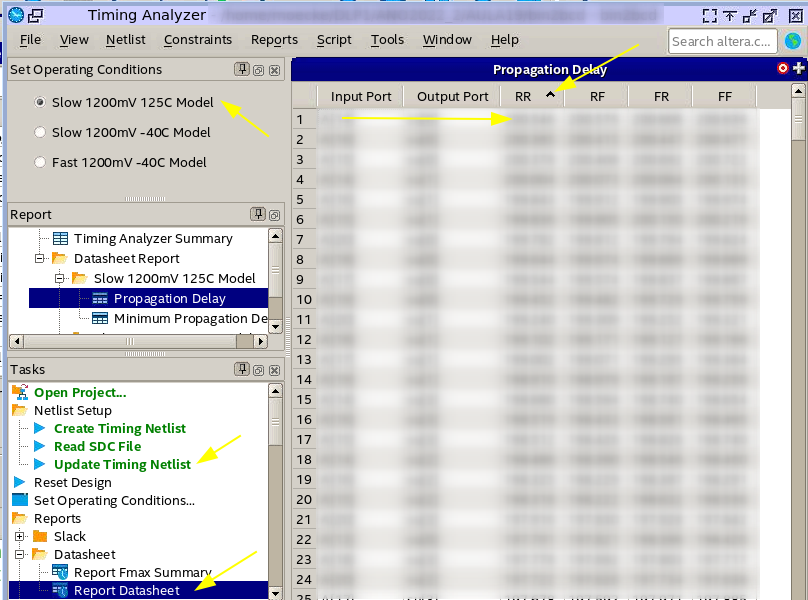

- Anote o tempo máximo de propagação do circuito.

Figura AE6(e) - Exemplo de tempo máximo de propagação (60,588 ns)

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Procure reduzir essa quantidade, aproveitando resultados intermediários e evitando a realização de uma nova divisão pelo uso do operador REM.

- Analise o tempo de propagação e área ocupada (número de elementos lógicos) e tente otimizar um ou os dois parâmetros. Se realizar diversas versões, pode anotar os valores de todas elas e fornecer todas as versões, mas foque no melhor desempenho.

- O aluno apresentar dois projetos como resultado sendo um para o menor tempo máximo de propagação e outro para menor área ocupada (número de elementos lógicos).

- Faça uma simulação que mostre que o circuito projetado funciona.

- O arquivo QAR entregue deve ser plenamente compilável e permitir após a Análise e Síntese e execução do arquivo de simulação VWF apresentar o resultado final.

- Para fins de uniformização na comparação dos resultados utilizem o menor dispositivo da família CYCLONE (EP1C3T100A8).

- Neste laboratório não é necessário fornecer as imagens RTL e Technology Map usadas para obter e melhorar os circuitos, nem a imagem da simulação que mostra que a versão entregue funciona.

- Se desejar você pode incluir os arquivos com as imagens de simulação e RTL de comprovação na entrega.

- Entregas

- Envie dois arquivos QAR contendo todos os arquivos necessário para compilar e simular os projetos .

- Poste no comentário da atividade: 1) O número de elementos lógicos de cada versão entregue. 2) O tempo máximo de propagação de cada versão entregue.

- A entrega será feita através do Moodle da disciplina. Observe o prazo de entrega de 14 dias.

- NÃO é necessário entregar um relato simples em PDF, mas pode ser feito se desejar.

- Caso faça o relato ele deve ter a identificação (autor, título, data), conter informações essenciais para mostrar que o circuito funciona e relatar os resultados obtidos para os parâmetros solicitados. Nesta caso aproveite para descrever como conseguiu reduzir o tempo de propagação e o número de elementos lógicos.

- Use preferencialmente o Overleaf para gerar o documento. Mas o uso de MS-Word, Libreoffice e Google Docs também é permitida.

- Bônus

- 0,2 pontos na avaliação A1 - O aluno que apresentar a solução funcionando e fique em primeiro lugar no parâmetro menor área ocupada, com comprovação por simulação.

- 0,2 pontos na avaliação A1 - O aluno que apresentar a solução funcionando e fique em primeiro lugar no parâmetro menor tempo máximo de propagação entre entradas e saída, com comprovação por simulação.

- 0,1 pontos na avaliação A1 - O aluno que apresentar a solução funcionando e fique em segundo lugar no parâmetro menor área ocupada, com comprovação por simulação.

- 0,1 pontos na avaliação A1 - O aluno que apresentar a solução funcionando e fique em segundo lugar no parâmetro menor tempo máximo de propagação entre entradas e saída, com comprovação por simulação.

|

AE7 - Estudo dos atributos de objetos e de síntese

| AE7 - Estudo dos atributos de objetos e de síntese

|

- Atividades

Neste laboratório remoto, os alunos deverão ser realizar as seguintes atividades:

- Estudar o Exemplo 4.5 - Registros redundantes

Avaliar a quantidade de elementos lógicos utilizadas para as diferentes versões conforme a tabela abaixo. Anote os dados de número de elementos logicos, guarde o RTL e Technology Map de cada versão. Após realizar as 8 versões, compare os resultados e documente em um relato simples, evitando duplicar as figuras que forem iguais. Analise os resultados escrevendo algum paragrafo de conclusão sobre este estudo.

| Atributo de síntese

|

keep

|

preserve

|

noprune

|

| versão 0

|

false

|

false

|

false

|

| versão 1

|

true

|

false

|

false

|

| versão 2

|

false

|

true

|

false

|

| versão 3

|

true

|

true

|

false

|

| versão 4

|

false

|

false

|

true

|

| versão 5

|

true

|

false

|

true

|

| versão 6

|

false

|

true

|

true

|

| versão 7

|

true

|

true

|

true

|

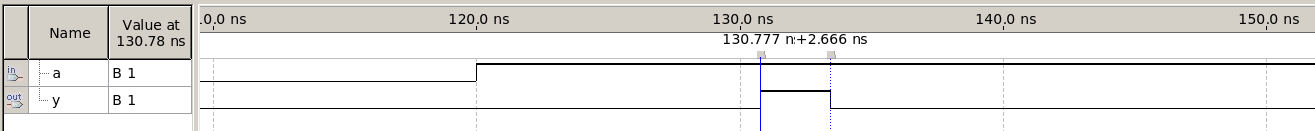

- Desafio 1 - Gerador de pulsos

Projetar um circuito gerador de pulsos que a cada transição de decida ou de subida do sinal de entrada A, gere um pulso na saída Y. Neste caso, haverá BÔNUS de 0,2 pontos na avaliação A1 para o aluno que obtiver o circuito que funcione com o menor número de elementos lógicos. Para fins de uniformização na comparação dos resultados utilizem o menor dispositivo da família CYCLONE (EP1C3T100A8).

Anote os dados de número de elementos lógicos, guarde o RTL e Technology Map do circuito. Também guarde a imagem da simulação que demonstre que o circuito funciona corretamente. Meça o tempo de duração do pulso na subida do sinal A e também na descida. Analise o resultado escrevendo um parágrafo de conclusão sobre este estudo, considerando as diferentes versões que tentou realizar.

Para medir a duração dos pulsos use os cursores do simulador.

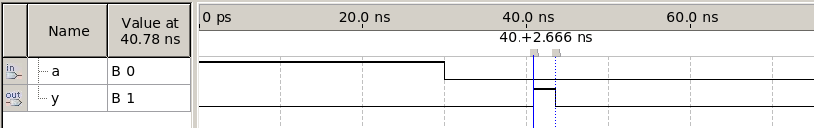

Figura AE7(a) - Exemplo de simulação temporal para medir duração do pulso de ~2.7 ns

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura AE7(b) - Exemplo de simulação temporal para medir duração do pulso de ~2.7 ns

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Entregas

- Envie dois arquivos QAR contendo todos os arquivos necessário para compilar os projetos e para simular (somente segundo projeto).

- Envie um relato simples em PDF, incluindo as imagens capturadas (inclua legenda em cada figura) e escreva para cada imagem um texto comentando o que representa.

- O relato deve ter a identificação (autor, título, data). Não é necessário uma introdução e uma conclusão geral da atividade, nem a descrição dos procedimentos feita na página wiki não precisa incluída no relatório.

- Use preferencialmente o Overleaf para gerar o documento. Mas o uso de MS-Word, Libreoffice e Google Docs também é permitida.

- A entrega será feita através do Moodle da disciplina. Observe o prazo de entrega de 14 dias.

- Bônus

- 0,2 pontos na avaliação A1 - O primeiro aluno que apresentar a solução do desafio 1 funcionando, com comprovação por simulação.

- 0,1 pontos na avaliação A1 - O segundo aluno que apresentar a solução do desafio 1 funcionando, com comprovação por simulação.

- 0,2 pontos na avaliação A1 - O aluno que apresentar a solução do desafio 1 funcionando e fique em primeiro lugar no parâmetro menor número de elementos lógicos, com comprovação por simulação.

- 0,1 pontos na avaliação A1 - O aluno que apresentar a solução do desafio 1 funcionando e fique em segundo lugar no parâmetro menor número de elementos lógicos, com comprovação por simulação.

|

AE8 - Estudo dos Arrays

| AE8 - Estudo dos Arrays

|

- Atividade

- Altere o "Exemplo 3.5: Array de Integers 1D x 1D" de modo a armazenar 6 valores inteiros com range -128 a 127, e obtenha 3 saídas, indicado pelos 3 endereços de entrada.

entity array_1Dx1D_integer is

port (

row : in integer range 1 to 3;

slice : out integer range 0 to 15

);

end entity;

architecture teste of array_1Dx1D_integer is

type a1Dx1D_integer is array (1 to 3) of integer range 0 to 15;

constant table : a1Dx1D_integer := (15, 5, 7);

begin

slice <= table(row);

end architecture;

- Analise o RTL, TechMap, numero de elementos lógicos utilizados, número de pinos utilizados e o tempo de máximo de propagação.

- Faça um desenho (pode ser manual) que represente o ARRAY declarado.

- Quantos bits são necessários para representar esse ARRAY?

- Realize a simulação funcional para verificar que o circuito funciona

- Altere o "Exemplo 3.6: Array de bits 1D x 1D" de modo a armazenar 6 vetores de 8 bits e obtenha 3 saídas, indicado pelos 3 endereços de entrada. Insira na matriz os mesmo bits que representam os valores do exemplo anterior.

entity array_1Dx1D_bit is

port (

row : in integer range 1 to 3;

column : in integer range 0 to 4; --3 bits

slice1 : out bit;

slice2 : out bit_vector(1 to 2);

slice3 : out bit_vector(1 to 4);

slice4 : out bit_vector(1 to 3)

);

end entity;

architecture teste of array_1Dx1D_bit is

type a1Dx1D_bit is array (1 to 3) of bit_vector(1 to 4);

constant table : a1Dx1D_bit :=

(('1', '1', '1', '1'), --15

('0', '1', '0', '1'), -- 5

('0', '1', '1', '1')); -- 7

begin

--slice1 <= table(row)(column);

--slice2 <= table(row)(1 to 2);

--slice3 <= table(row)(1 to 4);

--slice4 <= table(1 TO 3)(column);

--slice4 <= table(1)(column) & table(2)(column) & table(3)(column);

--gen : for i in 1 to 3 generate

-- slice4(i) <= table(i)(column);

--end generate;

end architecture;

- Analise o RTL, TechMap, numero de elementos lógicos utilizados, número de pinos utilizados e o tempo de máximo de propagação.

- Faça um desenho (pode ser manual) que represente o ARRAY declarado.

- Quantos bits são necessários para representar esse ARRAY?

- Realize a simulação funcional para verificar que o circuito funciona

- Altere o "Exemplo 3.7: Array de bits 2D" de modo a armazenar os bits do exemplo anterior e obtenha 3 vetores de saída, indicados pelos 3 endereços da colunas de entrada. Insira na matriz os mesmo bits que representam os valores do exemplo anterior.

entity array_2D_bits is

port (

row : in integer range 0 to 3;

column : in integer range 0 to 4; --3 bits

slice1 : out bit;

slice2 : out BIT_VECTOR(1 to 2);

slice3 : out BIT_VECTOR(1 to 4);

slice4 : out BIT_VECTOR(1 to 3)

);

end entity;

architecture teste of array_2D_bits is

type a2D_bits is array (1 to 3, 1 to 4) of bit;

constant table : a2D_bits := (('0', '0', '0', '1'),

('1', '0', '0', '1'), ('1', '1', '0', '1')

);

begin

--slice1 <= table(row, column);

--slice2 <= table(row, 1 TO 2);

--slice3 <= table(row, 1 TO 4);

--slice4 <= table(1 TO 3, column);

--slice4 <= table(1, column) & table(2, column) & tabl

--gen : for i in 1 to 3 generate

-- slice4(i) <= table(i, column);

--end generate;

end architecture;

- Analise o RTL, TechMap, numero de elementos lógicos utilizados, número de pinos utilizados e o tempo de máximo de propagação.

- Faça um desenho(pode ser manual) que represente o ARRAY declarado.

- Quantos bits são necessários para representar esse ARRAY?

- Realize a simulação funcional para verificar que o circuito funciona

- Ao final salve o projeto em um arquivo QAR (sugestão AE8.QAR)

- Procure comparar os resultados obtidos nos três circuitos.

- Dica

- Para acessar linhas ou colunas de uma matriz 1D x 1D ou 2D veja o código abaixo:

--Acessando uma linha de uma matriz

gen1 : for j in 1 to 4 generate

slice3(j) <= table(row, j);

end generate;

-- Acessando uma coluna de uma matriz

gen2 : for i in 1 to 3 generate

slice4(i) <= table(i, column);

end generate;

- Entregas

- Envie o arquivo QAR contendo todos os arquivos necessário para compilar e simular.

- Entregue um PDF contendo relato simples dos resultados, imagens e análise desses resultados e um conclusão.

- A entrega será feita através do Moodle da disciplina. Observe o prazo de entrega.

|

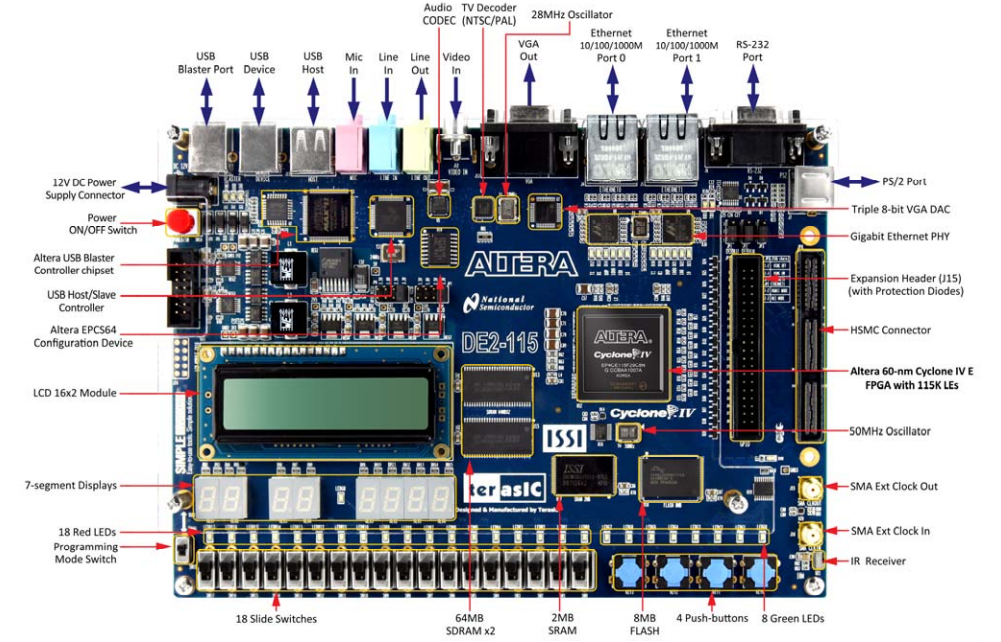

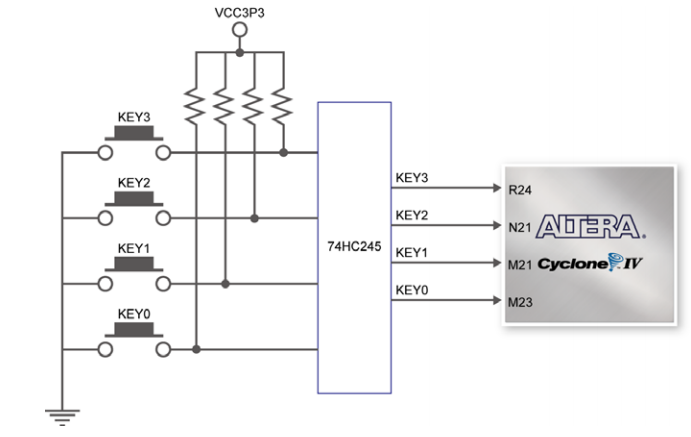

AE9 - Calculadora básica implementada no kit DE2-115

| AE9 - Calculadora básica implementada no kit DE2-115

|

- Objetivos

- Estudar as limitações dos operadores aritméticos de (+, -, *, / e REM)

- Desenvolver soluções para sinalizar erro, evitar erro ou aplicar saturação na saída

- Analisar a área ocupado pelo circuito e também o máximo tempo de propagação

- Programar o kit DE2-115 para atuar como calculadora básica de 4 operações

- Procedimento de laboratório

- Passo 1

- Adaptar o "Exercício: Multiplicador/Divisor/Somador/Subtrator" para uma calculadora de 4 operações com números com sinal.

- Defina para as entradas a e b um total de 8 bits

- Incluir a seleção do resultado a ser mostrado nos leds verdes.

- Unifique os 3 tipos de erro em uma única saída e use como sinalização de erro o led que fica entre os displays de sete segmentos.

- Usar as chaves deslizantes para as entradas a e b, e sinalizar nos led acima das chaves o estado das chaves.

- Usar as chaves de contato momentâneo "PUSH BUTTON" para escolher a operação (+, -, *, /)

- Usar os leds Vermelhos para mostrar os resultados da operação selecionada. No caso da divisão mostrar o quociente seguido do resto nestes leds.

- Fazer a simulação funcional para se assegurar que a calculadora funciona.

- Passo 2

- Passo 3 - Circuito com overflow

- Realizar os seguintes testes, acionando as chaves e observando o resultado nos LEDs:

- Carregar valores nas chaves de entrada e observar o resultado ao acionar os PUSH BUTTON.

- De preferencia coloque valores que produzam erros de soma, subtração e divisão também. Use os mesmos valores que você usou na simulação.

- Passo 4 - Circuito com saturação e sinalização de erro

- Repita o Passo 3, com o circuito que inclui a saturação e o bit de erro.

- Relatório Técnico

- Documentar o experimento em um relatório técnico que contenha no mínimo:

- identificação (título, disciplina, data, autores);

- introdução;

- descrição do procedimento realizado;

- resultados obtidos (com imagens dos itens importantes) e análise dos resultados;

- conclusão.

- apêndice (se desejar pode ser disponibilizados vídeos do funcionamento do circuito nos Passos 3 e 5

- O relatório deve também responder as questões levantadas e mostrar que os objetivos apresentados na introdução foram atendidos.

|

AE10 - Simulação funcional com o ModelSim

| AE10 - Simulação funcional com o ModelSim

|

- Objetivos

- Conhecer o simulador ModelSim

- Realizar simulação funcional com o ModelSim

- Conhecer a integração do Quartus com ModelSim

- Conhecer simulação usando wave-create e force

- Criar arquivos de script .do para os passos da simulação e para formatação do wave

- Procedimento de laboratório

- PASSO 1 - Inciando o Modelsim e editando um arquivo VHDL

- PASSO 1a: Execute o software o Modelsim (considerando aqui a instalação padrão na nuvem do IFSC)

/opt/altera/13.0sp1/modelsim_ae/bin/vsim

- PASSO 1b: Resete o Layout do Modelsim (caso tenha feito alguma modificação e não saiba como retornar ao original) (Layout > Reset).

- PASSO 1c: Mude para a pasta onde está o projeto, usando a barra de menu (File > Change Directory... [Escolha a pasta]. Ou via linha de comando na janela de transcript.

cd /home/nome_usuario/nome_pasta/.../AE10

- PASSO 1d: Confira se está na pasta correta

pwd

- Confira o conteúdo da pasta

ls

- PASSO 1e: Crie um novo arquivo VHDL [File > New > Source > VHDL] e digite o código abaixo e salve no arquivo n_flip_flop.vhd na pasta AE10

------------------------------------------------------

-- FILE : n_flip_flop.vhd

-- AUTOR: Marcos Moecke

-- DATA : 22 de dezembro de 2021

------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY n_flip_flop IS

GENERIC (N : NATURAL := 4);

PORT

(

clk : IN std_logic;

rst : IN std_logic;

d : IN std_logic_vector(N - 1 DOWNTO 0);

q : OUT std_logic_vector(N - 1 DOWNTO 0)

);

END;

ARCHITECTURE ifsc_v1 OF n_flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

q <= (OTHERS => '0');

ELSIF (clk'EVENT AND clk = '1') THEN

q <= d;

END IF;

END PROCESS;

END;

- PASSO 1f: Compile o arquivo vhd do projeto. (Compile > Compile... selecione [n_Flip_Flop.vhd] e clique em [Compile]). Responda a [Create Library?] com [Yes]. Em seguida clique em [Done]. Ou

vlib work

vcom -work work n_flip_flop.vhd

- PASSO 2 - Simulação funcional com o Modelsim

- PASSO 2a: Inicie a simulação (Simulation > Start Simulation... na aba [Design] selecione a Entity [n_Flip_Flop] no Package work e clique em [OK]. Ou

vsim work.n_flip_flop

- PASSO 2b: Inicie a criação dos sinais de entrada da Entity. Clique_direito sobre o nome da Entity na janela Library, e em seguida selecione [Create Wave]. Ou

wave create -pattern none -portmode in -language vhdl -range N 1 /n_flip_flop/d

wave create -pattern none -portmode in -language vhdl /n_flip_flop/clk

wave create -pattern none -portmode in -language vhdl /n_flip_flop/rst

wave create -pattern none -portmode out -language vhdl -range 1 N /n_flip_flop/q

Será aberta uma janela [Wave] na qual irão ser mostrados as 3 portas de entrada da Entity e a porta de saída. Clique sobre o sinal da porta de saída q e [Delete], pois esse sinal não será editado. Aproveite para arrastar com o mouse os sinais na janela Wave para ficarem na seguinte ordem: rst, clk, d.

- PASSO 2c: Crie o sinal de rst como um pulso de valor '1' entre 20 e 30 ps.

Clique_direito sobre o sinal rst e selecione [Edit > Create/Modify Waveform] e escolha [Patterns = Constant], [Start Time = 0] [End Time = 3000] [Time Unit = ps] e clique em [Next], [Value = 0] e clique em [Finish]. Ou

wave modify -driver freeze -pattern constant -value 0 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/rst

Clique_direito sobre o sinal rst e selecione [Edit > Create/Modify Waveform] e escolha [Patterns = Constant], [Start Time = 20] [End Time = 30] [Time Unit = ps] e clique em [Next], [Value = 1] e clique em [Finish]. Ou

wave modify -driver freeze -pattern constant -value 1 -starttime 20ps -endtime 30ps Edit:/n_flip_flop/rst

- PASSO 2d: Crie o sinal de clk com um período de 100 ps, iniciando em '1'.

Clique_direito sobre o sinal clk e selecione [Edit > Create/Modify Waveform] e escolha [Patterns = Clock], [Start Time = 0] [End Time = 3000] [Time Unit = ps] e clique em [Next], [Initial Value = 1], [Clock Period = 100ps], [Duty Cycle = 50] e clique em [Finish]. Ou

wave modify -driver freeze -pattern clock -initialvalue 1 -period 100ps -dutycycle 50 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/clk

- PASSO 2e: Crie o sinal de d como sendo uma contagem crescente entre "0000" e "1111"

Clique_direito sobre o sinal d e selecione [Edit > Create/Modify Waveform] e escolha [Patterns = Counter], [Start Time = 0] [End Time = 1000] [Time Unit = ps] e clique em [Next], [Start Value = 0000], [End Value = 1111], [Time Period = 120ps], [Counter Type = Range], [Count Direction = Up], [Step Count = 1], [Repeat = Forever] e clique em [Finish]. Ou

wave modify -driver freeze -pattern counter -startvalue 0000 -endvalue 1111 -type Range -direction Up -period 120ps -step 1 -repeat forever -range 4 1 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/d

- PASSO 2f: Insira o sinal de saída q na janela Wave.

Clique sobre o sinal q na janela Objects e solte-o na janela Wave. Ao final desses passos a janela Wave deverá estar conforme mostrado abaixo:

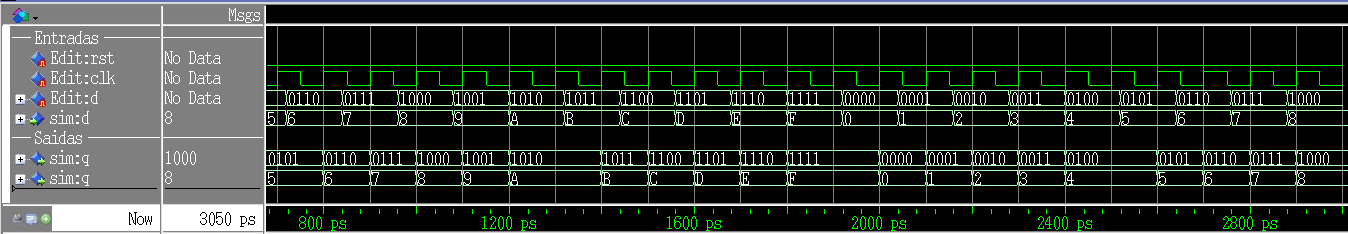

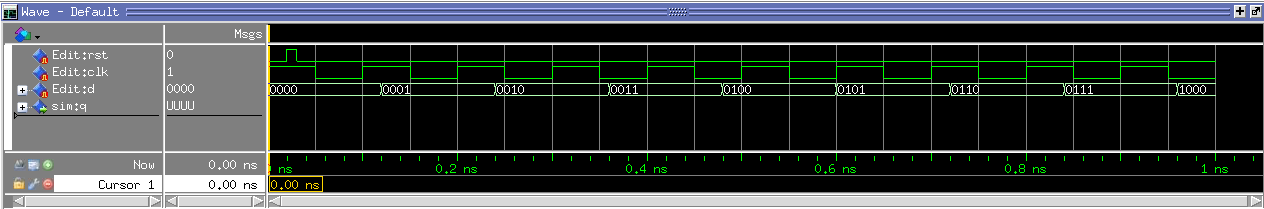

Figura AE10a - Edição do Waveform de 4 FF 1000ns no Modelsim

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- PASSO 2g: Realize a simulação de 1000 ps

- Opção 1: Clique 10 vezes sobre o icone [Run] ou [F9]

- Opção 2: Digite 10 vezes o comando run na janela Transcript (cada run dura o tempo indicado ao lado esquerdo do icone [Run]

- Opção 3: Digite o comando run 1000 ps

- Dica se desejar fazer a simulação durante todo o tempo descrito nos sinais criados (3000 ps) é possível utilizar o comando

run -all

- PASSO 2h: Análise da simulação

Selecione com o shift_clique_esquerdo do mouse os sinas d e q (barramentos de 4 bits) e em seguida clique_direito e selecione [radix > unsigned]. A janela Wave deverá estar conforme mostrado abaixo:

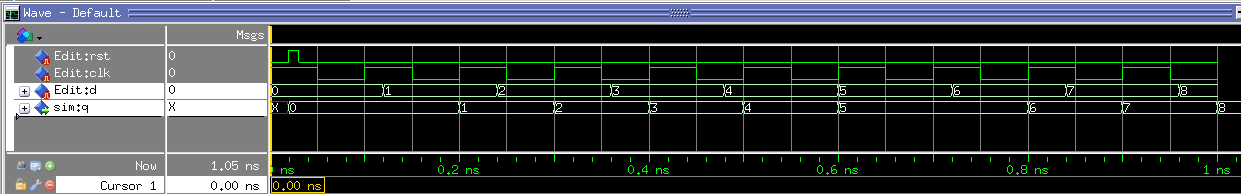

Figura AE10b - Simulação funcional de 4 FF 1000ns no Modelsim

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Note que a saída q está com (Forcing Unknown - (X em vermelho) entre 0 e 20 ps. Isso ocorre pois antes de aplicar o RESET o Flip Flop tem valor desconhecido. Por isso é sempre importante aplicar um RESET logo ao iniciar a simulação de um circuito sequencial.

- Note que as mudanças na saída q ocorrem sempre na transição de subida do sinal do CLOCK. Mudanças que ocorrem na entrada do sinal d não afetam a saída.

- Experimente mudar o sinal de entrada d com períodos diferentes (e.g. 60ps) e repita a simulação.

- Inclua um pequeno pulso de RESET na instante 530ps.

- PASSO 3 - Criação de um arquivo de testbench

Use os comandos da janela de transcript para criar um arquivo tb_nFF.do que permite repetir de forma automática o teste realizado.

################################

# FILE : tb_FF_create1.do

# AUTOR: Marcos Moecke

# DATA : 14 de agosto de 2019

################################

#criacao da library work

vlib work

#compilacao da entity nome.vhd (nao necessita ser compilado no quartus II)

vcom -work work n_flip_flop.vhd

#simulacao na entity nome.vhd

vsim work.n_flip_flop

#inclusao de um divisor

add wave -noupdate -divider Entradas

#edicao do sinal rst

wave create -pattern none -portmode in -language vhdl /n_flip_flop/rst

wave modify -driver freeze -pattern constant -value 0 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/rst

wave modify -driver freeze -pattern constant -value 1 -starttime 20ps -endtime 30ps Edit:/n_flip_flop/rst

#edicao do sinal clock

wave create -pattern none -portmode in -language vhdl /n_flip_flop/clk

wave modify -driver freeze -pattern clock -initialvalue 1 -period 100ps -dutycycle 50 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/clk

#edicao do sinal d

wave create -pattern none -portmode in -language vhdl -range N 1 /n_flip_flop/d

wave modify -driver freeze -pattern counter -startvalue 0000 -endvalue 1111 -type Range -direction Up -period 120ps -step 1 -repeat forever -range 4 1 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/d

#inclusao do sinal de saida q (como UNSIGNED)

add wave -position end -radix hexadecimal sim:/n_flip_flop/d

#inclusao de um divisor

add wave -noupdate -divider Saidas

#inclusao do sinal de saida q (como BINARY)

add wave -position end sim:/n_flip_flop/q

#inclusao do sinal de saida q (como UNSIGNED)

add wave -position end -radix hexadecimal sim:/n_flip_flop/q

#Definir o zoom a ser mostrado na tela

WaveRestoreZoom {500 ps} {3000 ps}

#execucao da simulacao inteira

run -all

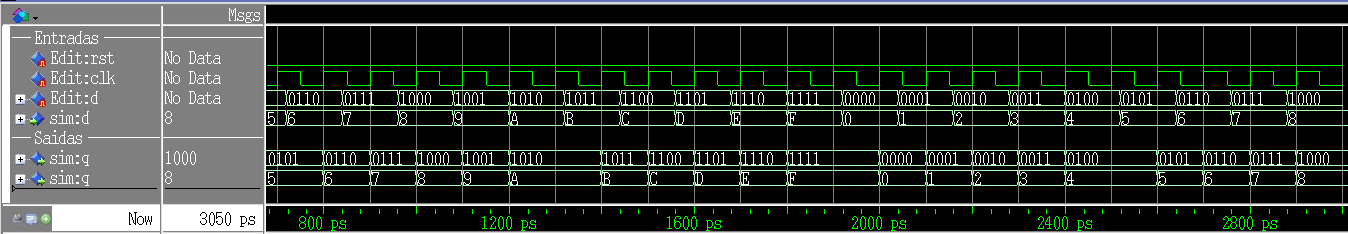

Figura AE10c - Simulação funcional no Modelsim

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Se desejar reiniciar a simulação use o comando

restart

E em seguida execute a simulação pelo tempo que desejar

run 1200 ps

Uma segunda opção de criação do testbench é salvando o formato e criação do WAVE em um arquivo wave.do e executar esse script dentro do testbench.

###############################################

## FILE : wave.do

## AUTOR: Marcos Moecke

## DATA : 22 de dezembro de 2021

###############################################

onerror {resume}

quietly WaveActivateNextPane {} 0

add wave -noupdate -divider Entradas

wave clipboard store

wave create -pattern none -portmode in -language vhdl /n_flip_flop/rst

wave create -pattern none -portmode in -language vhdl /n_flip_flop/clk

wave create -pattern none -portmode in -language vhdl -range N 1 /n_flip_flop/d

wave modify -driver freeze -pattern constant -value 0 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/rst

wave modify -driver freeze -pattern constant -value 1 -starttime 20ps -endtime 30ps Edit:/n_flip_flop/rst

wave modify -driver freeze -pattern clock -initialvalue 1 -period 100ps -dutycycle 50 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/clk

wave modify -driver freeze -pattern counter -startvalue 0000 -endvalue 1111 -type Range -direction Up -period 120ps -step 1 -repeat forever -range 3 0 -starttime 0ps -endtime 3000ps Edit:/n_flip_flop/d

add wave -noupdate -radix unsigned /n_flip_flop/d

add wave -noupdate -divider Saidas

add wave -noupdate /n_flip_flop/q

add wave -noupdate -radix unsigned /n_flip_flop/q

TreeUpdate [SetDefaultTree]

WaveRestoreCursors {{Cursor 1} {1000 ps} 0}

quietly wave cursor active 1

configure wave -namecolwidth 150

configure wave -valuecolwidth 100

configure wave -justifyvalue left

configure wave -signalnamewidth 1

configure wave -snapdistance 10

configure wave -datasetprefix 0

configure wave -rowmargin 4

configure wave -childrowmargin 2

configure wave -gridoffset 0

configure wave -gridperiod 1

configure wave -griddelta 40

configure wave -timeline 0

configure wave -timelineunits ps

update

WaveRestoreZoom {0 ps} {3000 ps}

view wave

WaveCollapseAll -1

wave clipboard restore

###############################################

## FILE : tb_nFF_create2.do

## AUTOR: Marcos Moecke

## DATA : 22 de dezembro de 2021

###############################################

vlib work

vcom -reportprogress 300 -work work /home/moecke/DLP29006/ANO2021_2/AE10/n_flip_flop.vhd

vsim work.n_flip_flop

do wave.do

run -all

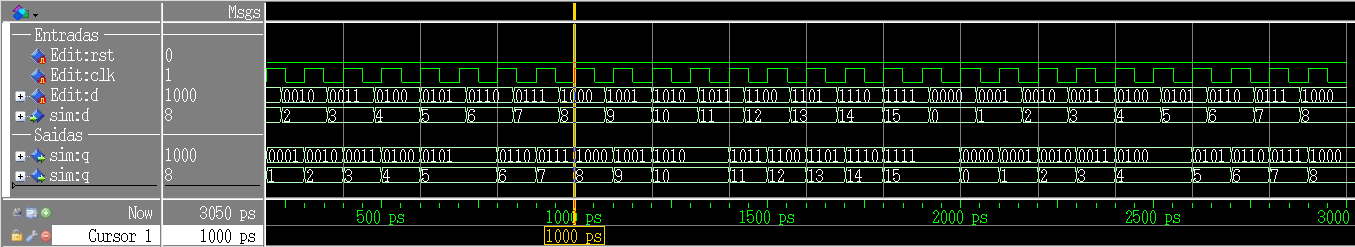

Figura AE10d - Simulação funcional no Modelsim

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- PASSO 4 - Simulação utilizando a interface gráfica com comandos force

- Realize a simulação seguindo os passos descritos durante a aula. Percebe que a vantagem é você ir construindo passo a passo as entradas a medida que vai analisando as saídas. Após realizar a simulação que deseja sempre é possível criar os sinais através de um script tb_nFF_force.do, conforme feito em aula.

- PASSO 5 - Conhecendo a integração do ModelSim com o Quartus II

- Siga os passos descritos na aula para abrir o Modelsim a partir do Quartus II. Para que os arquivos .do sejam incluídos no QAR é necessário adicioná-los ao projeto no Quartus II.

- Entregas

- Nesta atividade, não será necessário fazer entrega de nenhum relatório, no entanto está disponível no Moodle o link caso queiram enviar alguma documentação e o QAR da AE10

|

AE11 - Laboratório de programação de FPGA - Timer 00 a 99

| AE11 - Laboratório de programação de FPGA - Timer 00 a 99

|

- Objetivos

- Desenvolver sistemas utilizando blocos já desenvolvidos.

- Apreender a conectar os circuitos através de sinais.

- Perceber a necessidade de realizar projeto hierárquico.

- Perceber o componente hardware real na definição final das entradas e saídas do sistema.

- Procedimento de laboratório

- Passo 1 - Projete um contador BCD de 00 a 99 configurável com saída em 2 mostradores de 7 segmentos (versão 1)

- Projete um decodificador de BCD para sete segmentos BCD2SSD usando a instrução case.

entity bin2ssd is

port (

bin_in : in std_logic_vector(3 downto 0);

ssd_out : out std_logic_vector(0 to 6)

);

end entity;

- Modifique o contador de 00 a 99 para ser configurável para contar qualquer valor entre 01 até 99.

entity contador_bcd_00_99 is

generic (max_dezena : natural := 5; max_unidade : natural := 9);

port (

clk, rst : in std_logic;

bcd_dezena, bcd_unidade : out std_logic_vector(3 downto 0)

);

end entity;

- Conecte em cada saída bcd (bcd_dezena e bcd_unidade) um circuito conversor de bcd para ssd.

entity contador_ssd_00_99 is

generic (max_dezena : natural := 5; max_unidade : natural := 9);

port (

clk, rst : in std_logic;

bcd_unidade : buffer std_logic_vector(3 downto 0);

bcd_dezena : buffer std_logic_vector(3 downto 0);

ssd_unidade : out std_logic_vector(0 to 6);

ssd_dezena : out std_logic_vector(0 to 6)

);

end entity;

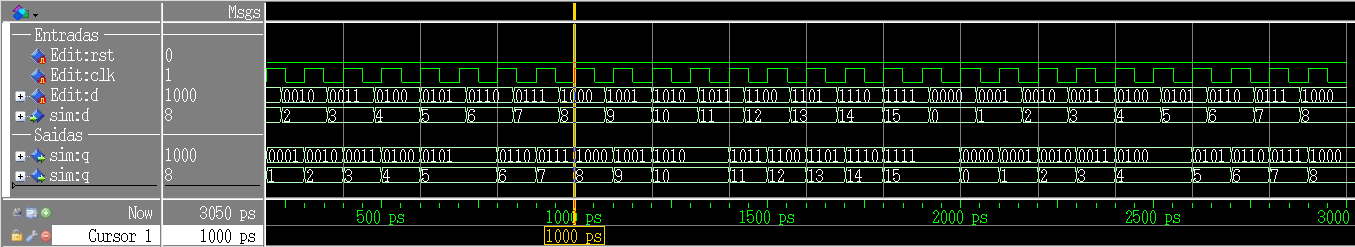

- Passo 2 - Simule o contador BCD

- Efetue a simulação funcional (Usando Modelsim) fazendo a contagem de 00 a 11 e também de 00 a 23 (para hora), de 00 a 59 (para minutos e segundos), e de 00 a 99.

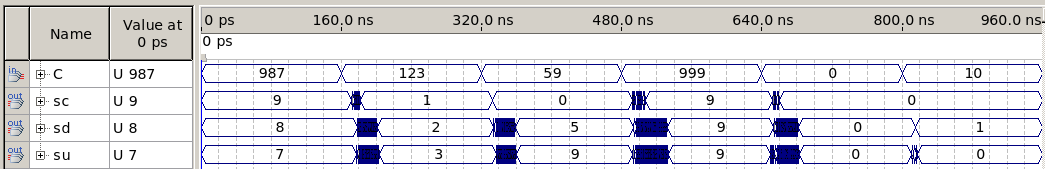

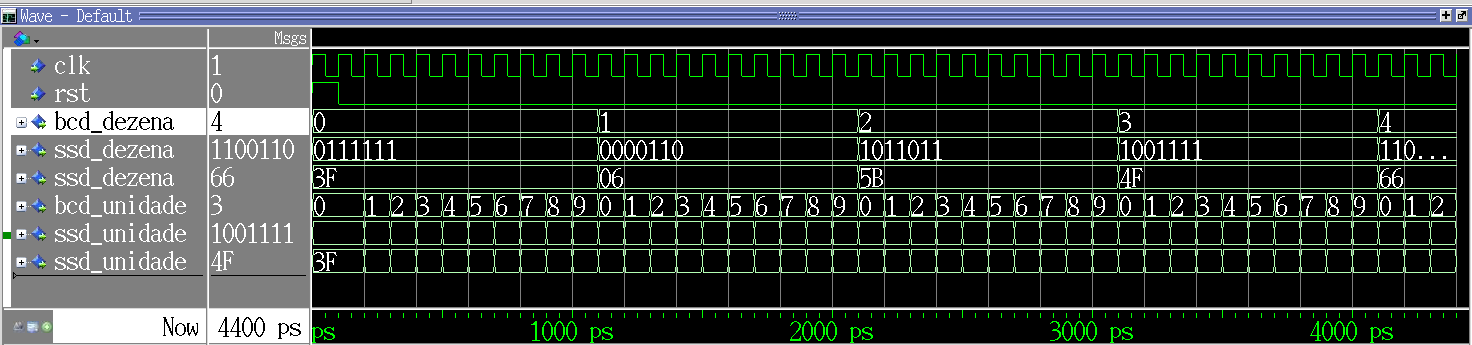

Figura AE11a - Simulação do contador ssd 00 a 99 no Modelsim

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Passo 3 - Implemente o contador BCD no kit Mercúrio IV

- Após verificar que o circuito funciona "simulado", configurar o FPGA do kit Mercúrio IV para implementar este circuito.

- Utilize os mostradores ssd DISP0_D e DISP1_D. Analise o tipo de mostrador que o kit possui catodo comum ou anodo comum (ler Display de 7 segmentos).

- Se desejar observar os valores de bcd_dezena e bcd_unidade, use uma linha da matriz de leds.

- Use como clock uma chave do tipo push-botton (por exemplo KEY11 do kit Mercúrio IV)

- As informações necessárias para configurar o dispositivo e seus pinos estão em Preparando para gravar o circuito lógico no FPGA.

- Se quiser usar algum led na matriz de led do kit Mercúrio é necessário colocar '0' da coluna do Led e '1' na linha correspondente, ou seja utilizar um segundo pino para acender o led.

- Passo 4 - Implemente o contador BCD no kit Mercúrio IV com antirepique

- Observe o comportamento do mostrador numérico. Talvez a cada clique da chave o contador conte mais que um devido ao repique da chave. Neste caso, elimine o repique da chave CLK, inserindo no código um circuito anti-repique, com um tempo de anti-repique de 10ms, já utilizado na AE4 - Programação do kit Mercurio IV.

- Entregas

- Enviar pelo Moodle o arquivo qar contendo todos os arquivos do projeto, incluindo os .do para efetuar a simulação.

- Enviar as imagens das simulações feitas.

- Fazer um vídeo demonstrando que o circuito não funciona (repique) e outro que funciona (com antirepique)

|

AE12 - Laboratório de programação de FPGA - Relógio Digital de 24 horas

| AE12 - Laboratório de programação de FPGA - Relógio Digital de 24 horas

|

- Objetivos

- Desenvolver sistemas utilizando componentes já desenvolvidos.

- Usar a técnica de projeto hierárquico para realizar sistemas.

- Perceber o componente hardware real na definição final das entradas e saídas do sistema.

- Procedimento de laboratório

- Passo 1 - Projete um relógio de 24 horas com as saídas numéricas usando mostradores de 7 segmentos

entity relogio24h IS

-- O valor do fclk2 corresponde a metade do periodo do clock de entrada em Hz

generic (fclk2 : natural := 50); -- ao simular o circuito utilize um valor baixo para acelerar a simulaçao

-- generic (fclk2 : natural := 50000000); -- ao implementar no hardware use o valor do clock em Hz

port

(

clk50MHz: in STD_LOGIC;

rst: in STD_LOGIC;

ligar: in STD_LOGIC;

ssd_DS, ssd_DM, ssd_DH : out STD_LOGIC_VECTOR(6 downto 0);

ssd_US, ssd_UM, ssd_UH : out STD_LOGIC_VECTOR(6 downto 0)

);

end entity;

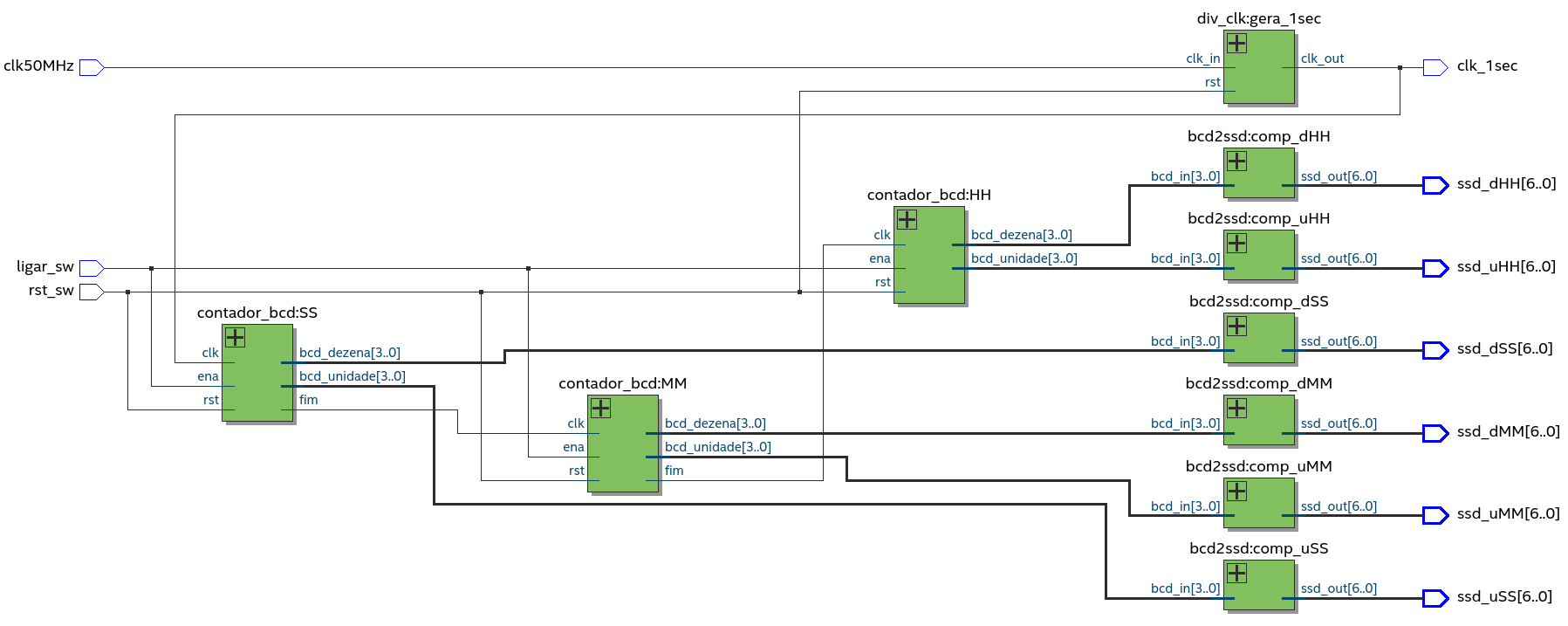

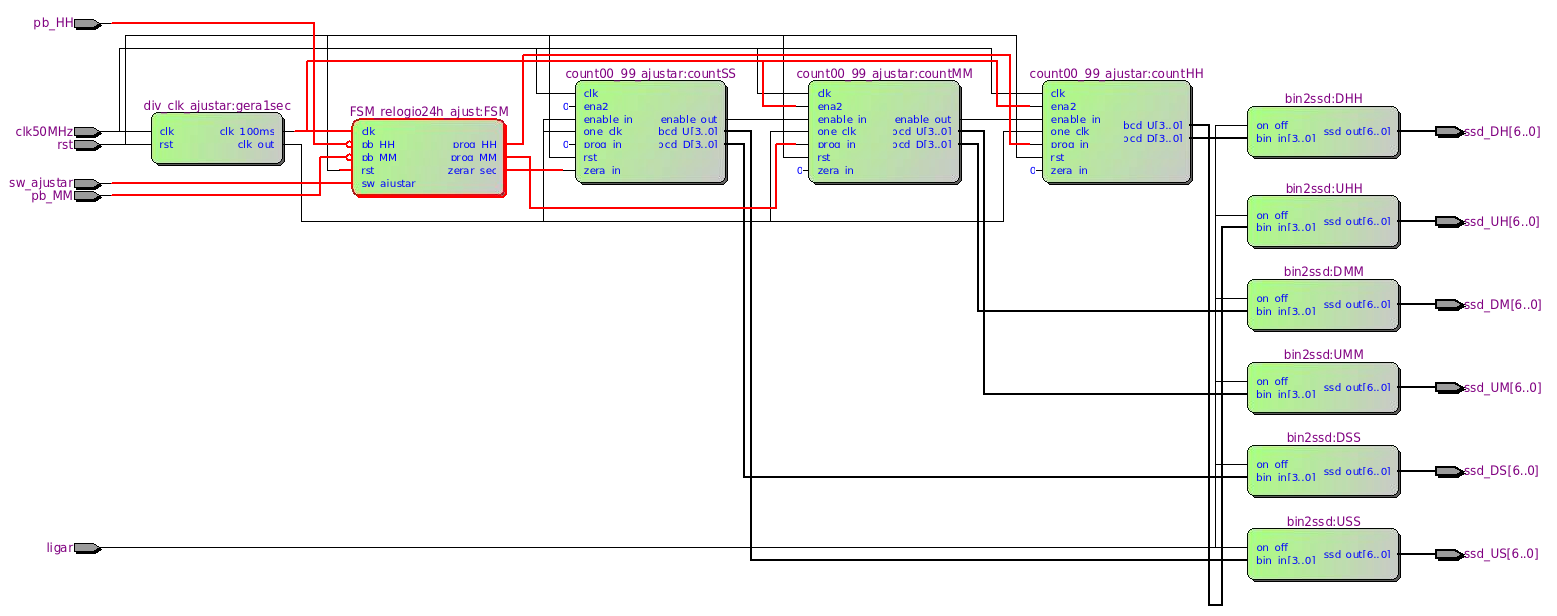

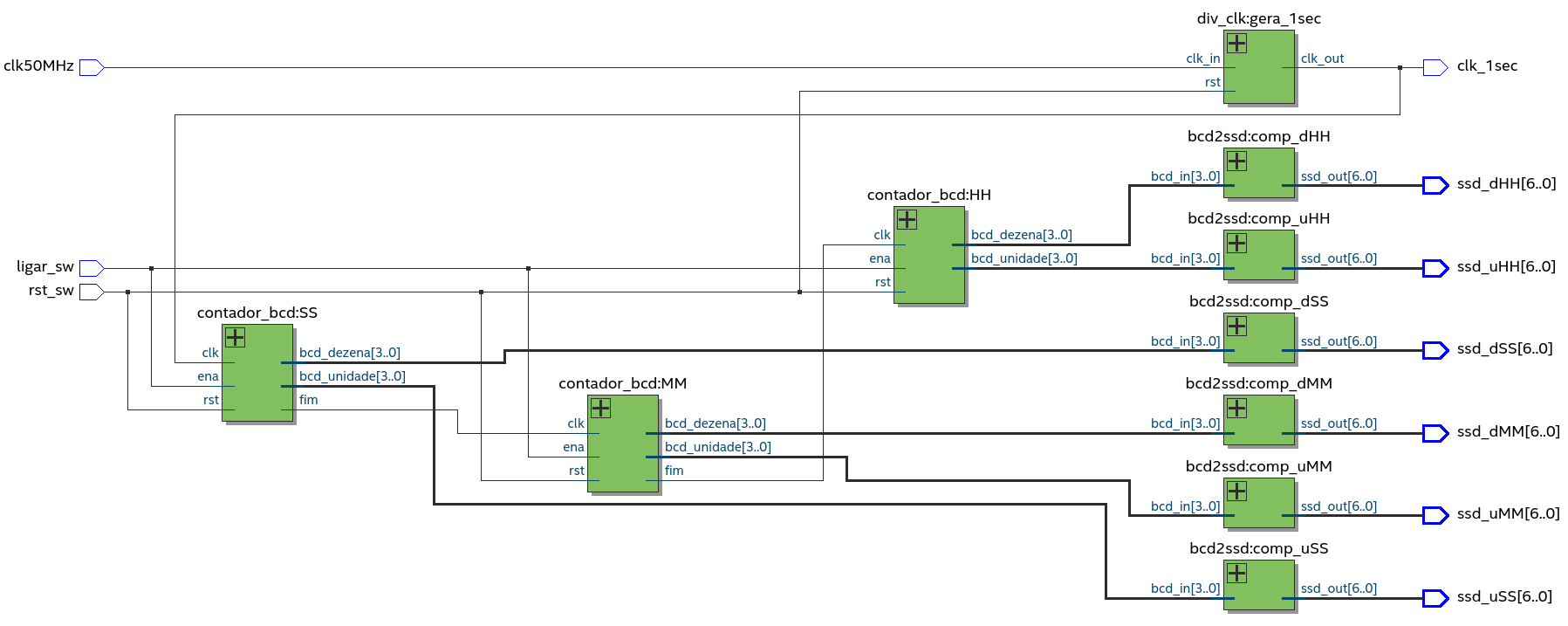

O projeto deve ser dividido em pelo menos os seguintes componentes (ver exemplo do RTL abaixo)

Figura AE12.a - RTL do Relógio Digital de 24 horas

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Componente 1 - Divisor de Clock, com o valor da divisão configurável pelo parâmetro fclk2. O sinal de saída será usado como "enable" ou "clock" a cada 1 segundo para o componente count00_99.

component div_clk is

generic (fclk2 : natural := 50); -- frequecia para simulacao

port (

clk,rst : in std_logic;

clk_out : out std_logic

);

end component;

- Componente 2 - Contador de 00 a 99 com saída em BCD, com o valor final configurável pelos parâmetros D e U

component count00_99 is

generic (D : natural := 9; U : natural := 9);

port (

clk,rst : in std_logic;

enable_in : in std_logic;

enable_out : out std_logic;

bcd_U : out std_logic_vector(3 downto 0);

bcd_D : out std_logic_vector(3 downto 0)

);

end component;

Esse contador precisa ser modificado para permitir que o clock seja síncrono em todos os flip-flops. Para isso é necessário usar um sinal de enable_in para habilitar a contagem durante um período de clock. Também será necessário gerar o sinal de enable_out para habilitar a contagem do próximo contador.

- Componente 3 - Conversor de BIN para SSD, com um parâmetro configurável ac_ccn para selecionar Anodo ou Catodo Comum.

component bin2ssd is

generic (ac_ccn : natural := 0);

port (

bin_in : in std_logic_vector(3 downto 0);

ssd_out : out std_logic_vector(6 downto 0)

);

end component;

- OBS

- O valor ac_ccn será utilizado para configurar o circuito entre ativo alto para display de catodo comum (ac_ccn=0), ou ativo baixo para display de anodo comum (ac_ccn=1).

- Se quiser, faça um componente com um count00_99 e dois bin2ssd e replique 3 vezes o componente.

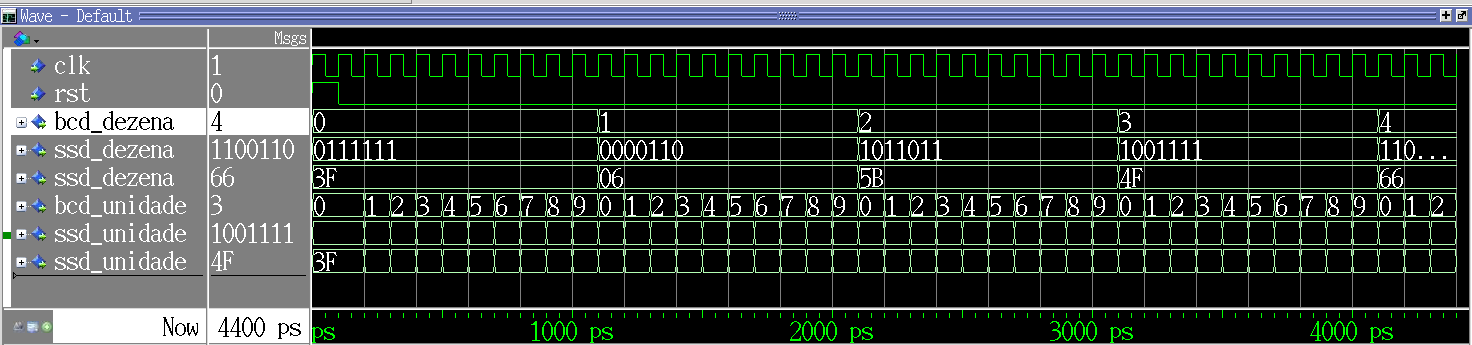

- Passo 2 - Simule os componentes e o relógio completo

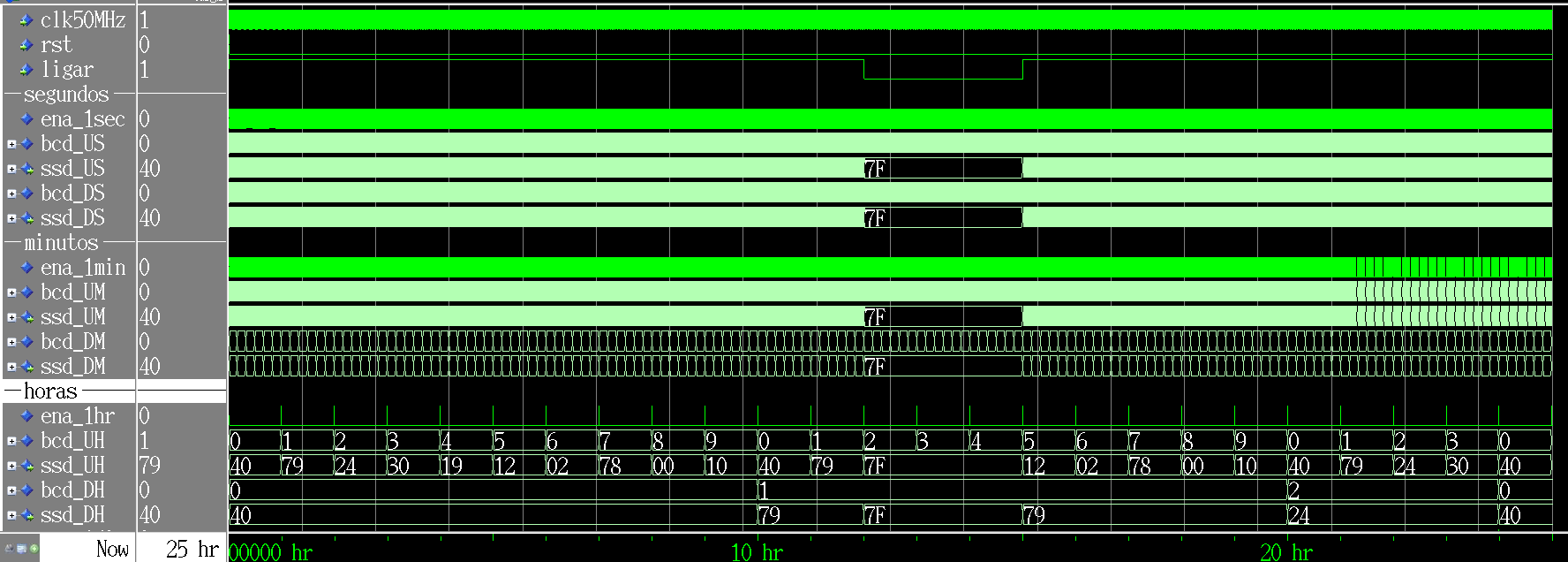

- Simulação do timer com ModelSim. Na simulação definir o clk50MHz com duração de 10 ms. Faça uma simulação de pelo menos 60 segundos. O projeto deve ser simulado por componente e após isso ser feita a integração dos componentes (Ver exemplo de teste de simulação abaixo)

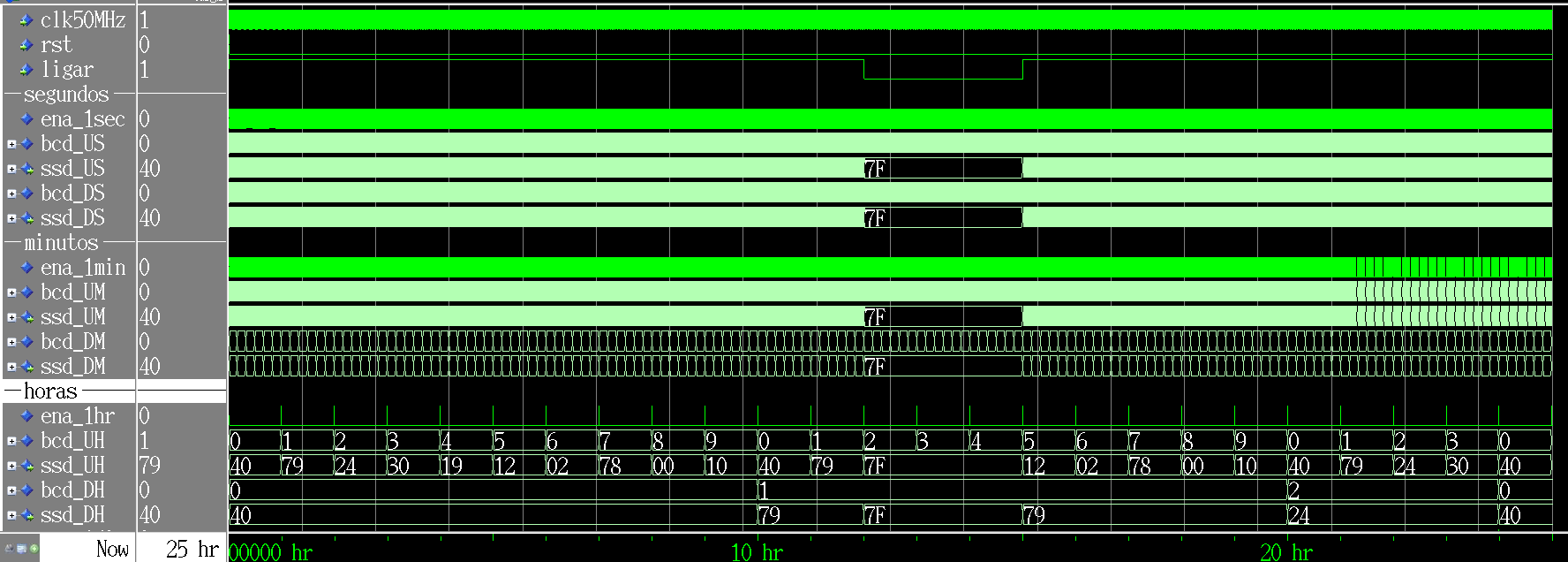

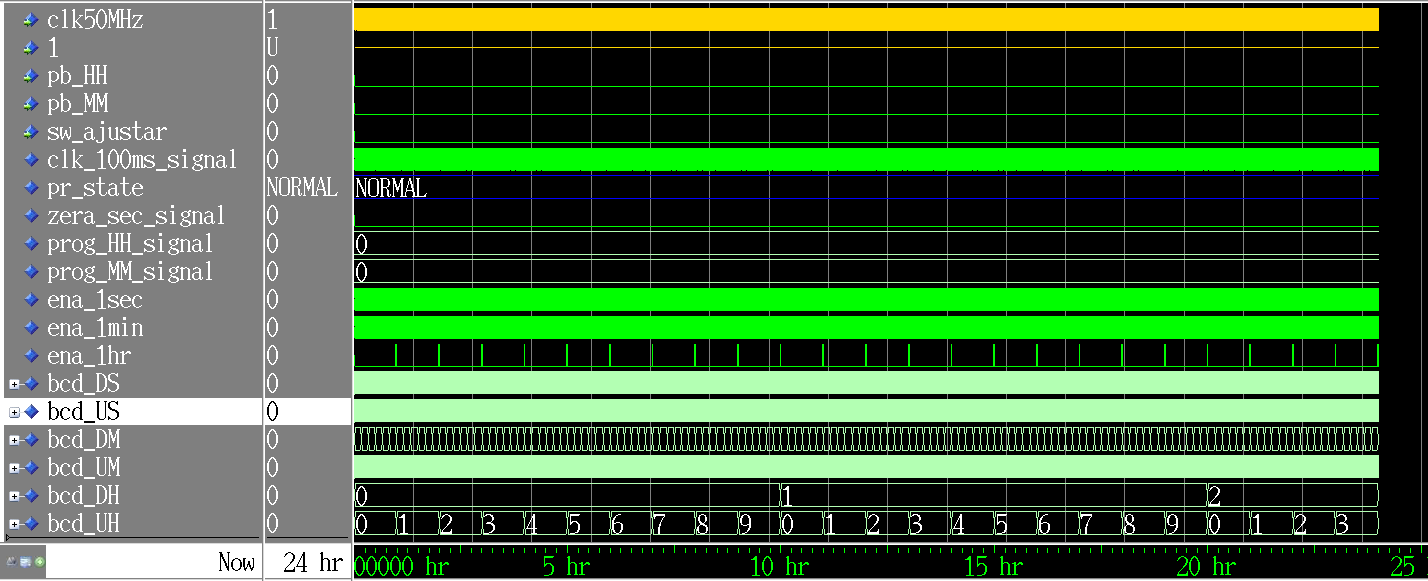

Figura AE12.b - Simulação funcional do Relógio Digital de 24 horas

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura AE12.b - Simulação funcional do Relógio Digital de 24 horas - detalhe enable 1sec

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Após a verificação do funcionamento por simulação funcional, utilizar o lab home office para enviar o hardware para o kit e comunicar ao professor para verificar se funcionou corretamente.

- É recomendável inserir um sinal de RESET em todos os circuitos sequenciais e ao iniciar a simulação do circuito começar com RESET ativo durante 10 ps.

- Passo 3 - Implemente o relógio no kit DE2-115

- Após verificar que a simulação do circuito está funcionando, configurar um FPGA para implementar este circuito. Existem duas opções de kit disponíveis com displays de sete segmentos. As informações necessárias estão em Preparando para gravar o circuito lógico no FPGA. Neste caso iremos usar o kit DE2-115 da TERASIC, pois precisamos de 6 mostradores de 7 segmentos.

- Analise o diagrama esquemático como funcionam as chaves e também o tipo de display. Note que no projeto o signal RST foi descrito como normalmente ALTO, podendo ser necessário acrescentar um inversor para ter o funcionamento correto. O Display de 7 segmentos da DE2-115 é do tipo cátodo comum.

Anote a pinagem que você utilizou:

- Entregas

Nesta atividade devem ser entregues os seguintes arquivos.

- O QAR do projeto com todos os componentes usados.

- A imagem das simulações feitas.

- O arquivo SOF usado na programação do FPGA.

- A imagem do RTL do projeto (e dos componentes), não é necessário expandir os componentes.

|

AE13 - Laboratório de programação de FPGA - Relógio Digital de 24 horas com ajuste

| AE13 - Laboratório de programação de FPGA - Relógio Digital de 24 horas com ajuste

|

- Objetivos

- Desenvolver sistemas utilizando componentes já desenvolvidos.

- Usar a técnica de projeto hierárquico para realizar sistemas para adaptar componentes já usados

- desenvolver uma maquina de estado finita (FSM) para ajustar a hora e minuto do relógio

- Perceber se na implementação do hardware os tempos utilizados para o ajuste estão adequados.

- Procedimento de laboratório

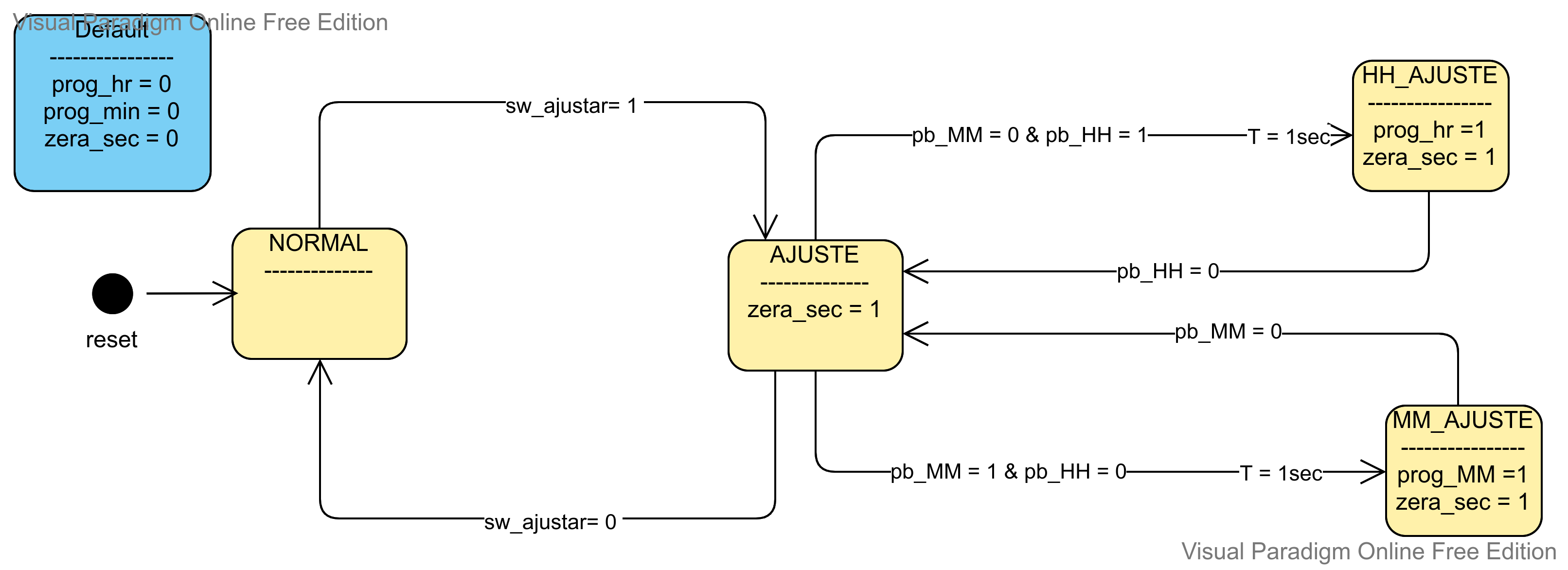

- Passo 1 - Projete uma FSM para o ajuste do minuto e hora do relógio

Essa FSM deve ler uma chave sw_ajustar e dois push botton pb_HH, e pb_MM, os quais devem ser usados para controlar a FSM conforme indicado no diagrama de estados abaixo:

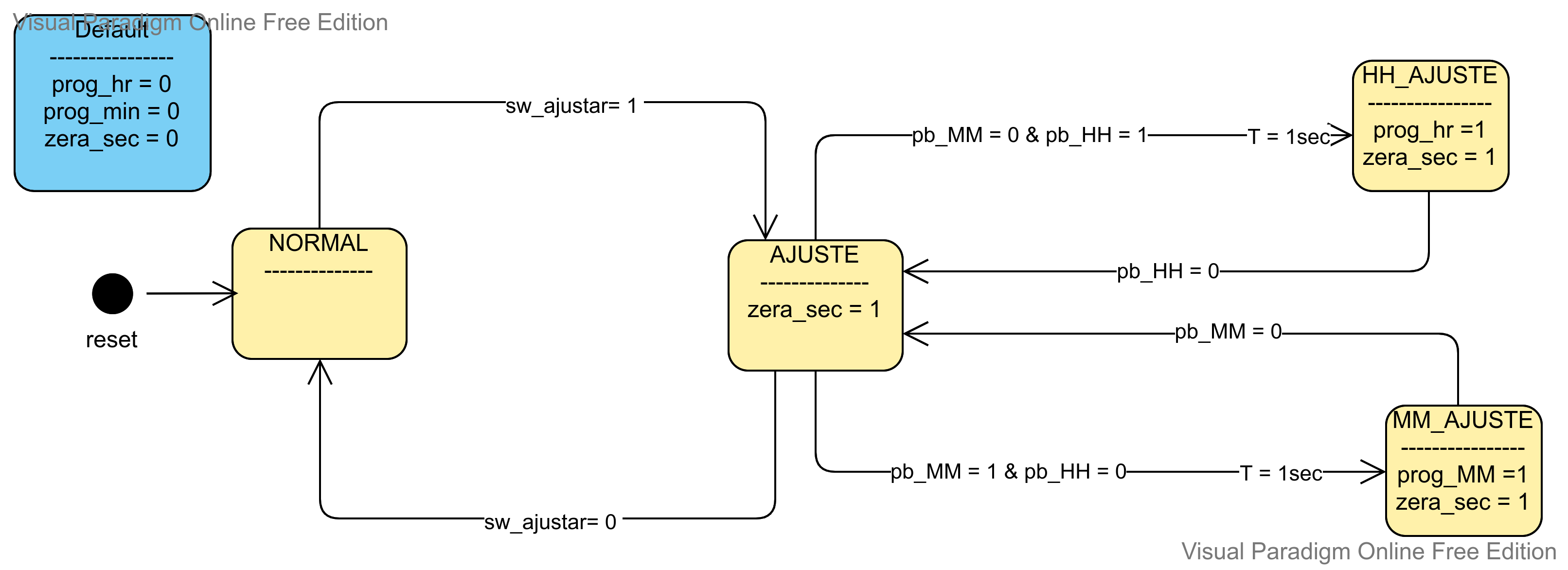

Figura AE13.a - Diagrama de estados da FSM para ajuste do relógio

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Passo 2 - Adapte os componentes utilizados na atividade anterior.

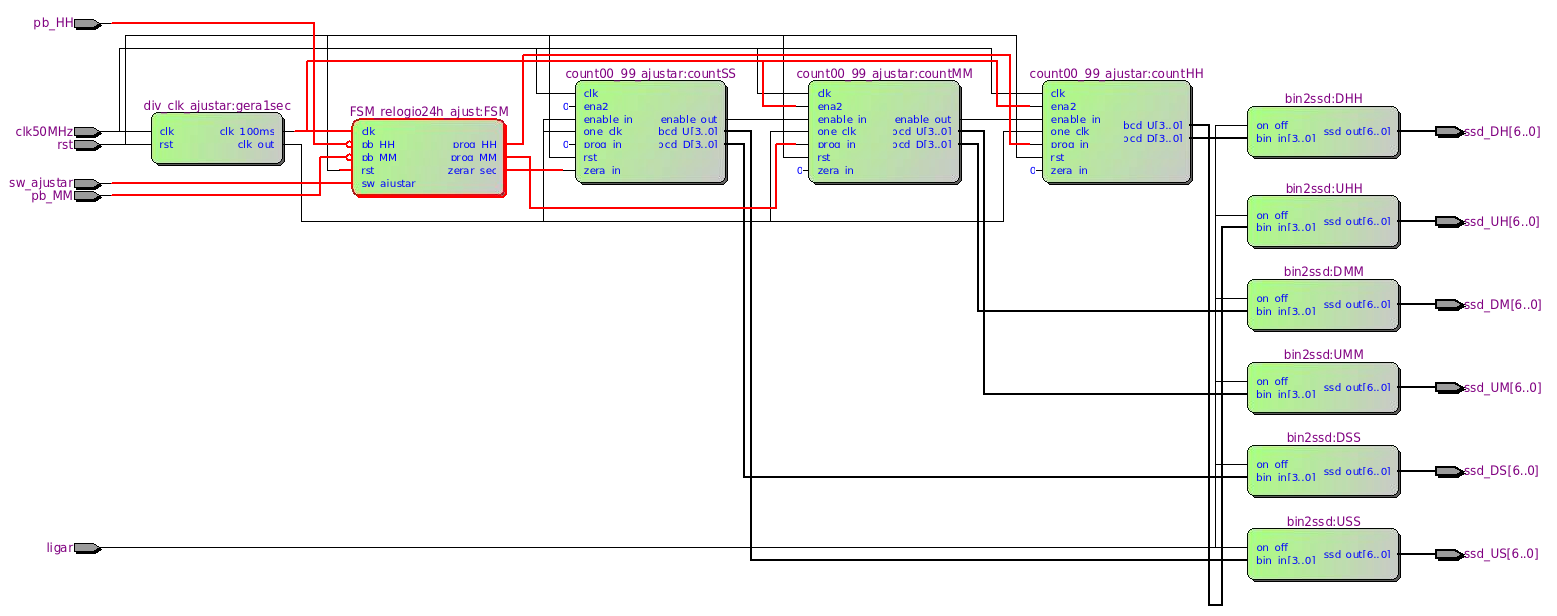

Nessa nova versão do relógio algumas modificações foram realizadas conforme está destacado no RLT a seguir:

Figura AE13.b - RTL do Relógio Digital de 24 horas com ajuste

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Componente 1 - O Divisor de Clock talvez seja necessário criar um novo sinal de saída para ser utilizado no incremento do minuto e hora. Abaixo a sugestão de usar um sinal de clk_100ms

entity div_clk_ajustar is

generic (fclk : natural := 50);

port

(

clk, rst : in std_logic;

clk_100ms : out std_logic;

clk_out : out std_logic

);

end entity;

- Componente 2 - O Contador de 00 a 99 deverá ser modificado para permitir o seu zeramento no caso do contador de segundos, e o incremento rápido no caso dos contadores de minuto e hora. Abaixo a sugestão de usar os sinais de entrada zera_in, prog_in e ena1. A entrada prog_in foi pensada para permitir diferentes modos de programação, por exemplo 1) Incremento de 1 unidade (minuto ou hora) a cada 1 segundo. 2) Incremento de 1 unidade a cada 100 ms. 3) Incremento de 1 unidade a cada acionamento da chave pb (push bottom)

entity count00_99_ajustar is

generic

(

D : natural := 9;

U : natural := 9;

MODO_PROG : natural := 1

);

port

(

clk, rst : in std_logic;

one_clk : in std_logic;

ena2 : in std_logic;

prog_in : in integer range 0 to MODO_PROG;

zera_in : in std_logic;

enable_in : in std_logic;

enable_out : out std_logic;

bcd_U : out std_logic_vector(3 downto 0);

bcd_D : out std_logic_vector(3 downto 0)

);

end entity;

- Componente 3 - O conversor de BIN para SSD não necessita modificações

- Passo 3 - Simule os componentes e o relógio completo

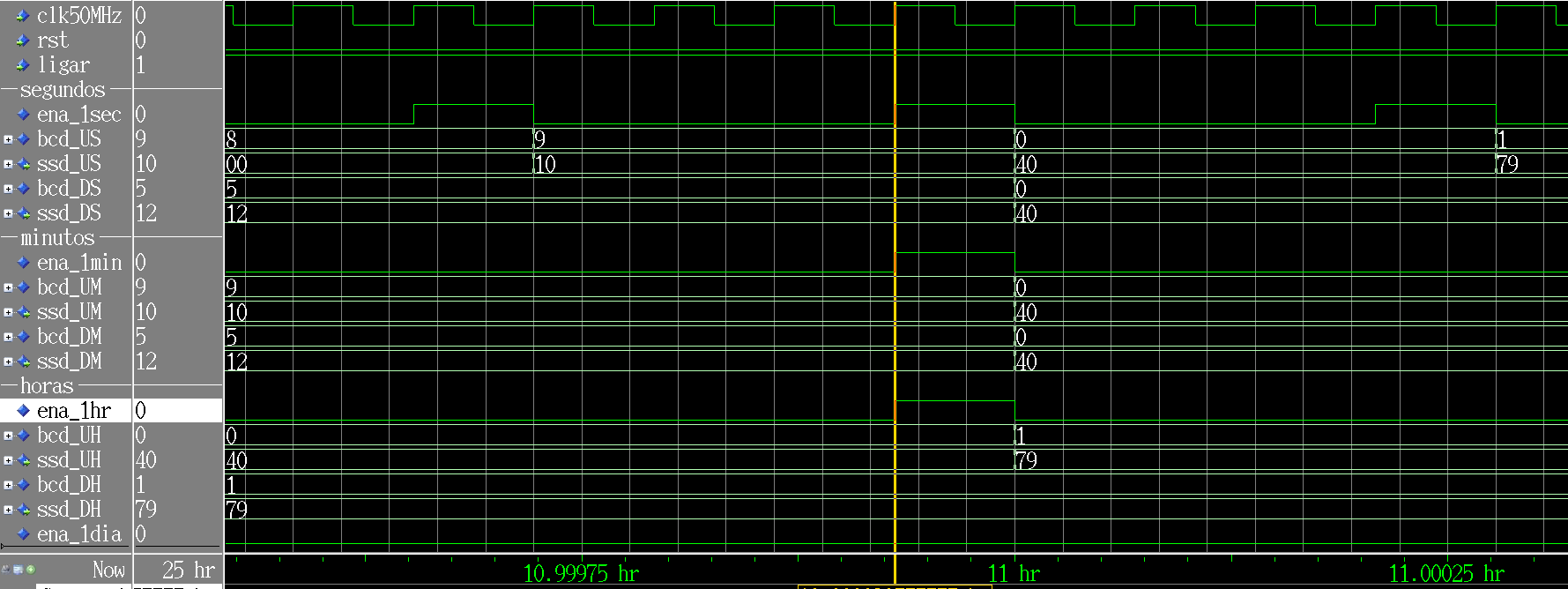

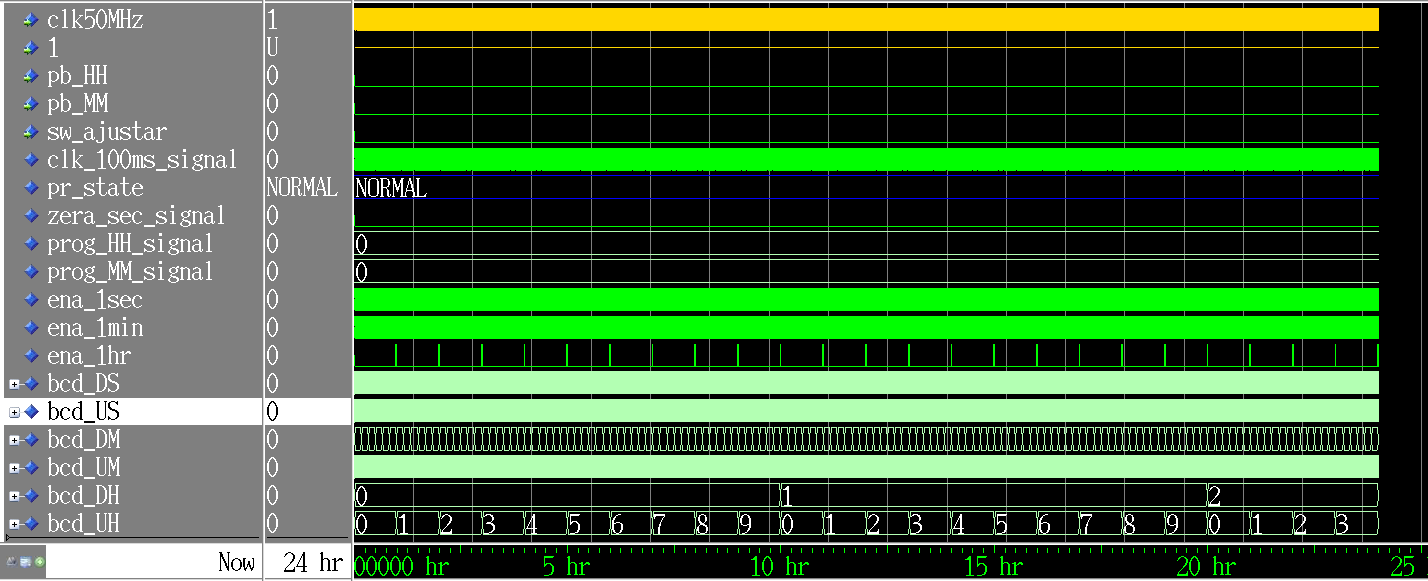

- Mostre que o relógio funciona no modo NORMAL, pelo menos 25 horas de simulação.

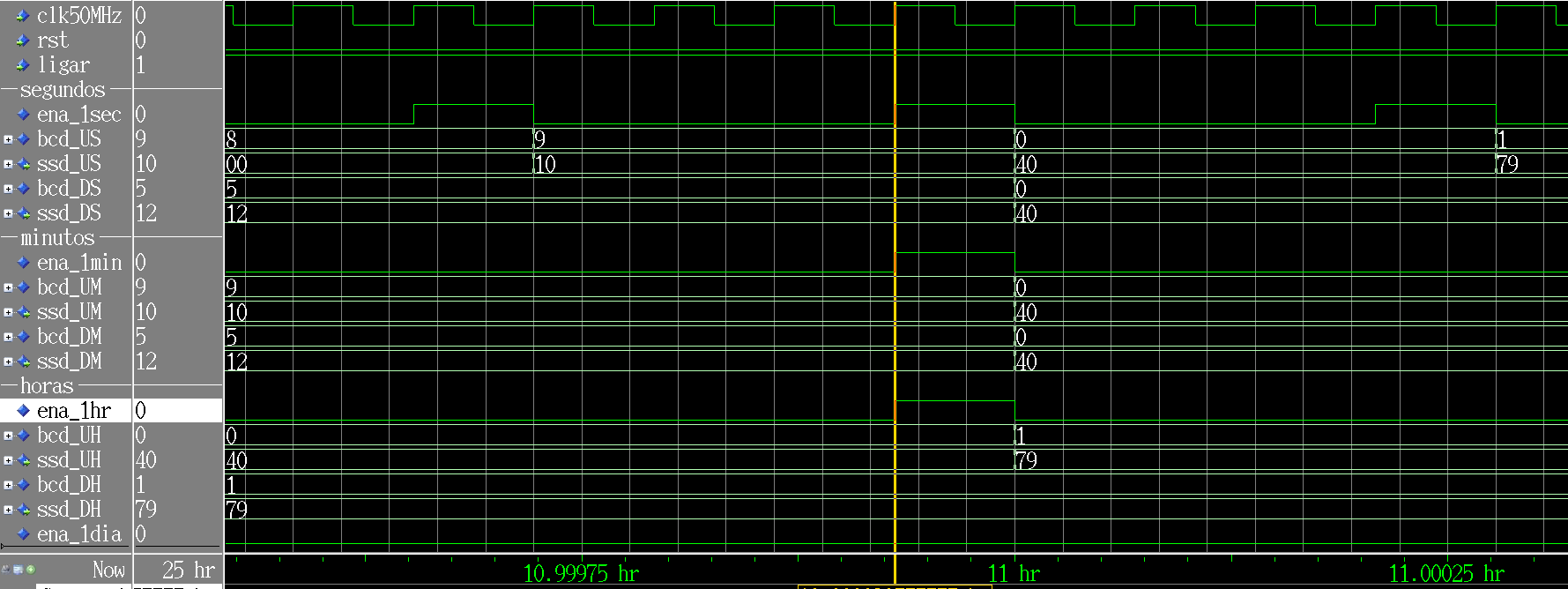

Figura AE13.c - Simulação funcional do Relógio Digital de 24 horas

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

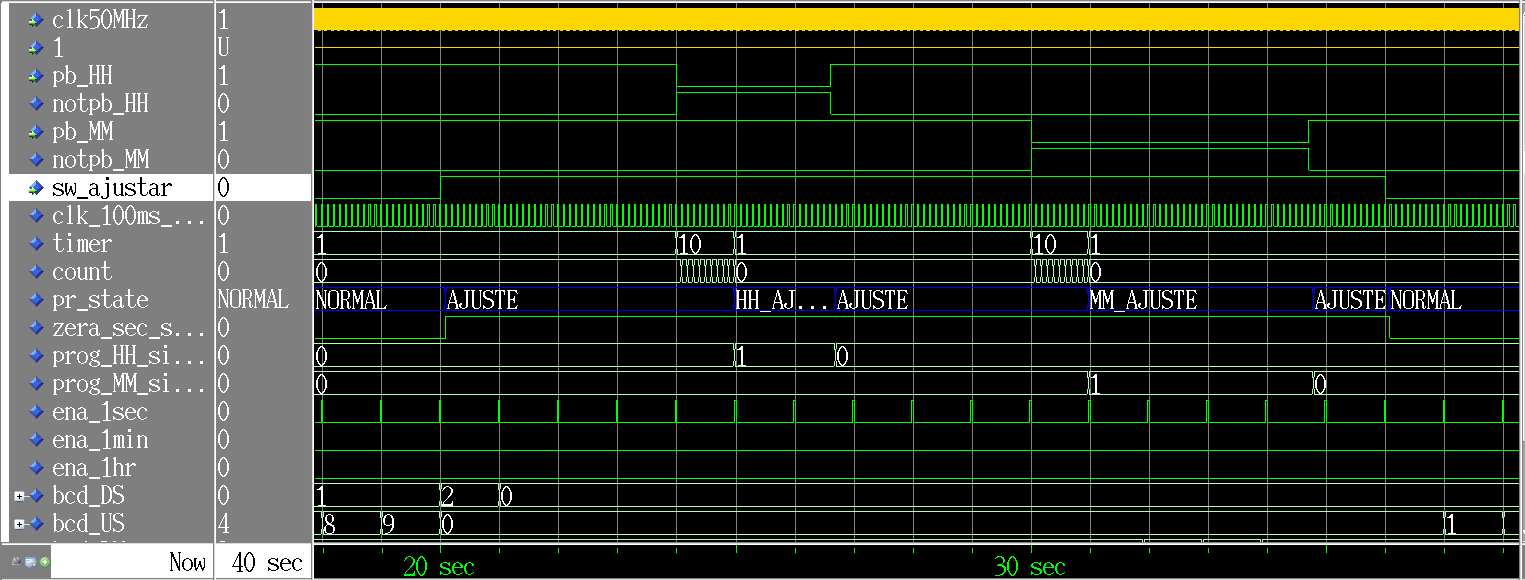

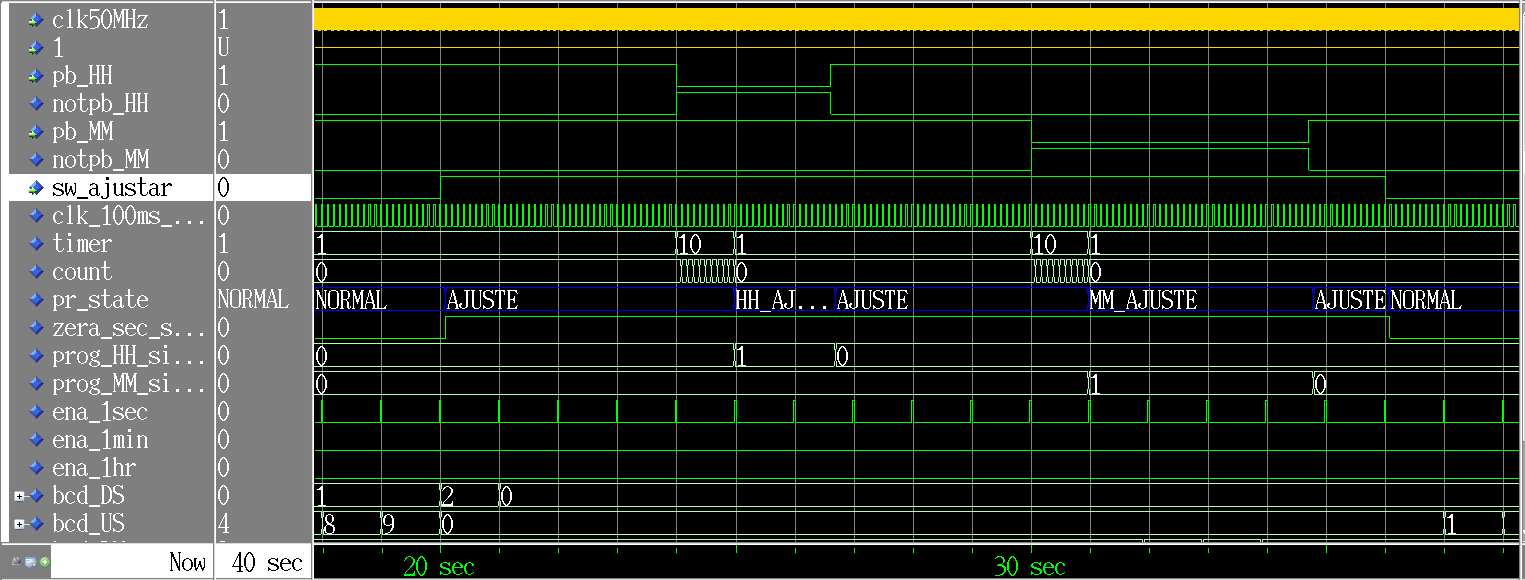

- Mostre o funcionamento do ajuste da hora HH e do minuto MM.

Figura AE13.d - Simulação funcional do Relógio Digital de 24 horas - detalhe enable 1sec

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Passo 4 - Implemente o relógio no kit DE2-115

- Após verificar que a simulação do circuito está funcionando, configurar um FPGA para implementar este circuito. Existem duas opções de kit disponíveis com displays de sete segmentos. As informações necessárias estão em Preparando para gravar o circuito lógico no FPGA. Neste caso iremos usar o kit DE2-115 da TERASIC, pois precisamos de 6 mostradores de 7 segmentos.

- Para controlar a FSM use dois push bottons para os botões de ajuste de hora (pb_HH) e minuto (pb_MM), e uma chave deslizante para entrar no modo ajuste (sw_ajustar). Lembre-se que no kit DE2-115 os push botton tem nível ALTO e passam para BAIXO quando acionadas. Recomenda-se fazer a adaptação de nível na entidade top level onde os componentes estão instanciados.

- Analise o diagrama esquemático como funcionam as chaves e também o tipo de display. Note que no projeto o signal RST foi descrito como normalmente ALTO, podendo ser necessário acrescentar um inversor para ter o funcionamento correto. O Display de 7 segmentos da DE2-115 é do tipo cátodo comum.

Anote a pinagem que você utilizou:

- Entregas

Nesta atividade devem ser entregues os seguintes arquivos.

- O QAR do projeto com todos os componentes usados.

- A imagem das simulações feitas.

- O diagrama de estados da FSM. Pode ser feito a mão ou usando um software como o https://online.visual-paradigm.com/pt/

- O arquivo SOF usado na programação do FPGA.

- A imagem do RTL do projeto (e dos componentes), não é necessário expandir os componentes até o nível de implementação.

|

-->

- ↑ 1,0 1,1 1,2 1,3 1,4 1,5 Erro de citação: Marca

<ref> inválida;

não foi fornecido texto para as refs chamadas PEDRONI2010b