DLP2-EngTel (página)

Dispositivos Lógicos Programáveis II

- Professores: Arliones Hoeller e Marcos Moecke

- Encontros: semanalmente nas terças e quinzenalmente nas quintas às 9:40 no Laboratório de Programação.

Material de aula

Principais referências bibliográficas

- Pong P. Chu, RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability. Wiley-IEEE Press, Hoboken, 2006, Pages 1-22, ISBN 0471720925.

- David Money Harris and Sarah L. Harris, Digital Design and Computer Architecture, Morgan Kaufmann, Burlington, 2007, Pages 3-48, ISBN 9780123704979, http://dx.doi.org/10.1016/B978-012370497-9/50002-0.

Notas de aula

Estas notas de aula são baseadas nas dispobilizadas pelo Prof. Pong P. Chu em [1].

- Lecture 01: Complexity Mangement and the Design of Complex Digital Systems

- Lecture 02: Synthesis of VHDL Code

- Lecture 02: Efficient Design of Combinational Circuits

- Lecture 03: Efficient Design of Sequential Circuits

- Lecture 04: Design of Sequential Circuits: Practice

- Lecture 05: Finite State Machines: Principle and Practice

- Lecture 06: Register Transfer Methodology: Principle

- Lecture 07: Register Transfer Methodology: Practice

- Configuração e uso do Signal Tap

- Lecture 08: Hierarchical Design

- Lecture 09: Parameterized Design: Principle

- Lecture 10: Parameterized Design: Practice

- Lecture 11: Clock and Synchronization: Principle and Practice

Atividades extra

Neste tópico serão listadas as atividades extras que os alunos da disciplina deverão realizar ao longo do curso. É importante observar o prazo de entrega, pois os conceitos serão reduzidos conforme o atraso na entrega. Para a entrega no prazo os conceitos possíveis são (A, B, C, D). Entrega com até uma semana de atraso (B, C, D). Entrega com até duas semanas de atraso (C ou D). Entrega com mais de duas semanas de atraso (D). Em virtude do número impar de alunos na turma, os trabalhos em equipes serão sempre 3 diferentes, onde um dos alunos deverá trabalhar sozinho. Ao longo do semestre todos terão o privilégio de trabalhar em equipe consigo mesmo.

- PARA ENTREGAR

- JÁ ENCERRADAS

Recursos de Laboratório

Para uso fora do IFSC dos recursos computacionais com licença educacional, o IFSC disponibiliza para seus alunos o IFSC-CLOUD. Atualmente a forma mais eficiente de acesso é através do Cliente X2GO. O procedimento de instalação/ configuração e uso do Quartus/Modelsim/QSIM está descrito em Acesso ao IFSC-CLOUD#Cliente X2GO (recomendado).

Para a geração de documentação/relatórios técnicos/artigos, está disponibilizada a plataforma Sharelatex do IFSC-CLOUD. Utilize preferencialmente o modelo de artigo no padrão ABNT.

Para estudo de FPGAs o Laboratório de Programação dispõe de kits Mercúrio IV da Macnica-DHW e também DE2-115 da Terasic. Veja como utilizar estes kits em Preparando para gravar o circuito lógico no FPGA, one além de acesso aos manuais dos fabricantes, você tem acesso a uma descrição resumida da pinagem mais utilizada desses kits.

Para depurar seu circuito em uma FPGA de verdade, pode ser interessante utilizar o SignalTapII da Altera, que permite realizar análise lógica dos sinais no seu circuito. Para iniciar o uso da ferramenta, siga este tutorial.

Para determinar os caminhos críticos do projeto (ou os tempos de propagação entre quaisquer nós de um projeto, utilize a Análise de Caminho Crítico com Qaurtus II.

Diário de Aulas

| 29/07: Laboratório: Processadores Embarcados (SoC) |

|---|

|

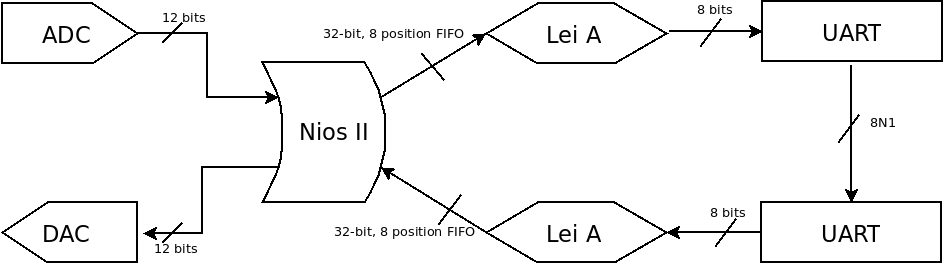

Nesta aula nós seguiremos um tutorial da Altera para construir um System-on-a-Chip (SoC), sintetizando um processador softcore NIOS em uma FPGA e carregando um software nele. Nas próximas aulas nós integraremos nossa própria lógica neste processador. Esta arquitetura de sistema deverá ser empregada em todos os trabalhos ao longo do semestre. A figura abaixo dá uma visão geral do que iremos implementar:

Você precisará destes documentos para desenvolver este tutorial:

Recomenda-se seguir este roteiro:

|

| 06/10: Laboratório: Processadores Embarcados (SoC) |

|---|

|

Retomada da aula de 28/07 Você precisará destes documentos para desenvolver este tutorial:

Recomenda-se seguir este roteiro:

Se o Eclipse SBT do Nios II não inicializar em um sistema Ubuntu 14.04 ou mais recente, você precisa instalar a libGTK2: sudo apt-get install libgtk2.0-0:i386 |

| 07/10: Laboratório: Processadores Embarcados (SoC) |

|---|

|

Continuação da aula de 06/10. Modificar o projeto da aula passada para:

|

| 13/10: Gerenciamento de Complexidade e Visão Geral de Sistemas Digitais Complexos |

|---|

|

| 20/10: Síntese de Código VHDL |

|---|

|

| 21,27/10, 03/11: Eficiência de Circuitos Combinacionais |

|---|

| 04,10,17/11: Eficiência de Circuitos Sequenciais |

|---|

| 18,24/11: Eficiência de Máquinas de Estado |

|---|

| 01,02,08/12: Register Transfer Methodology |

|---|

| 15/12: Projeto Hierárquico |

|---|

| 16/12: Projeto Parametrizado |

|---|

| 22/12,02/02: Clock e Sincronização |

|---|

| 03/12...: Projeto Final |

|---|

08/03: Final ProjectOverviewNeste projeto você implementará um processador de áudio via serial utilizando a placa Mercurio IV da Macnica com uma FPGA Cyclone IV-E. Uma visão geral é apresentada na figura acima, composta dos seguintes blocos:

Material de apoio para o projeto

|