Mudanças entre as edições de "DLP1-EngTel (página)"

| Linha 338: | Linha 338: | ||

*[[DLP29006-Engtelecom(2015-1) - Prof. Marcos Moecke]] | *[[DLP29006-Engtelecom(2015-1) - Prof. Marcos Moecke]] | ||

*[[DLP29006-Engtelecom(2015-2) - Prof. Marcos Moecke]] | *[[DLP29006-Engtelecom(2015-2) - Prof. Marcos Moecke]] | ||

| + | *[[DLP29006-Engtelecom(2016-1) - Prof. Marcos Moecke]] | ||

<!-- | <!-- | ||

*PS2 Interface | *PS2 Interface | ||

Edição das 00h26min de 11 de agosto de 2016

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

- Link curto http://bit.ly/IFSC-DLP29006

- Carga horária, Ementas, Bibliografia, Professores

- Cronograma de atividades

- Plano de Ensino

UNIDADE 8

- Projeto Final - Ver AE3 - Projeto Final de Hardware

Avaliações

- Avaliação A1 - Unidade 2 a 4 (30/05/2016) - Local: Lab Programação.

- Avaliação A2 (parte 1) - Unidade 5 e 6 (04/07/2016) - Local: Lab Programação.

- As avaliações A1 e A2(parte 1) são com consulta a todo tipo de material impresso ou digital. O aluno tem 5 minutos para preparar o computador depois disso a rede será desconectada.

- Avaliação A2 (parte 2) - Unidade 6 (20/07/2016) - Local: Lab Programação.

- A avaliação A2(parte 2) é com consulta apenas as folhas VHDL QUICK REFERENCE CARD e VHDL 1164 PACKAGES QUICK REFERENCE CARD.

- Recuperação R1-2 - Unidade 2 a 6 (25/07/2016) - Local: Lab Programação.

- Ao final das avaliações o aluno deverá enviar para o email moecke AT ifsc.edu.br com os arquivos solicitados.

- Entrega dos diversos trabalhos ao longo do semestre AE1 a AE(N-1).

- Projeto Final AE(N). Tem peso equivalente a duas avaliações.

Atividades extra

Neste tópico serão listadas as atividades extras que os alunos da disciplina deverão realizar ao longo do curso. É importante observar o prazo de entrega, pois os conceitos serão reduzidos conforme o atraso na entrega. Para a entrega no prazo os conceitos possíveis são (A, B, C, D). Entrega com até uma semana de atraso (B, C, D). Entrega com até duas semanas de atraso (C ou D). Entrega com mais de duas semanas de atraso (D).

PARA ENTREGAR

| AE1 - Temas relacionados aos FPGAs (Prazo de entrega do Resumo (500 caracteres/ 1 pagina): 22 Abril 2016, Prazo de entrega do Relatório: 9 Maio 2016) |

|---|

|

| AE2 - Operações Aritméticas Básicas em VHDL (Prazo de entrega: 2 Maio 2016) |

|---|

LIBRARY ieee;

USE ieee.numeric_std.all;

----------------------------------------

ENTITY calcular IS

GENERIC (N: NATURAL := 4);

PORT (

a, b: IN UNSIGNED(N-1 DOWNTO 0); -- N bits

y: OUT UNSIGNED(2*N-1 DOWNTO 0)); -- 2N bits

END ENTITY;

----------------------------------------

ARCHITECTURE arch_op OF calcular IS

BEGIN

y <= a * b;

END ARCHITECTURE;

----------------------------------------

Outras operações matemáticas:

|

| AE3 - Projeto Final de Hardware (prazo final 20/07/2016) |

|---|

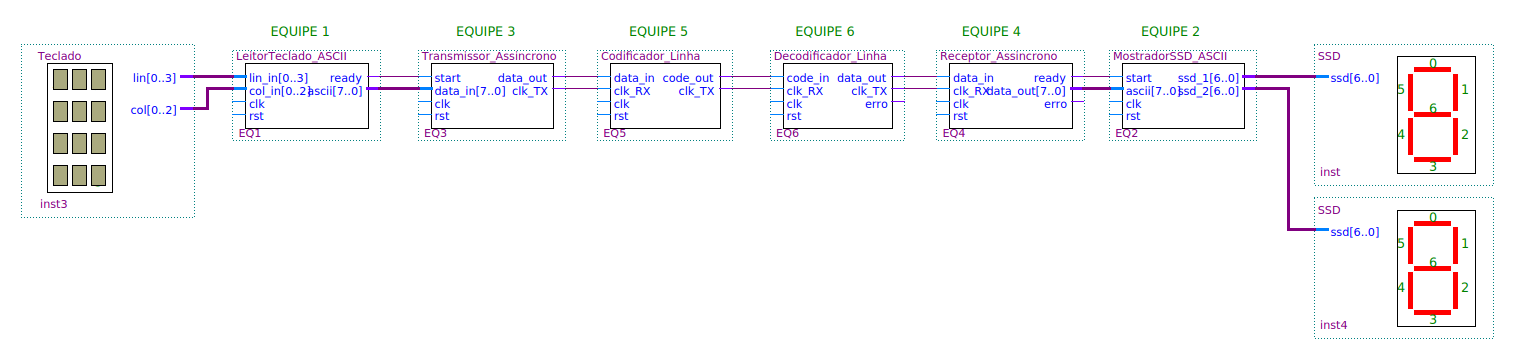

EQ1 - Lucas, Gabriel EQ2 - Maria, Helen e André EQ3 - Leticia, Katharine, Kristhine EQ4 - Gustavo, Tamara EQ5 - Fabiano, Marcos, Iago EQ6 - Anderson, Tiago / Fabiano

|

ESTUDOS SEM ENTREGA DE DOCUMENTAÇÃO

Os exemplos e exercícios essenciais estão destacados em negrito na listagens abaixo.

| EL1 - Resolução dos exercícios do Cap 2 |

|---|

especificado.

---------------------------------------

-- File: mux.vdh

---------------------------------------

-- Declaração das Bibliotecas e Pacotes

--

LIBRARY ieee;

USE _________________________ ;

---------------------------------------

-- Especificação das entradas e saídas e nome da ENTITY

ENTITY mux IS

PORT (

__ , __ : ___ STD_LOGIC_VECTOR (7 DOWNTO 0);

sel : IN ____________________________ ;

___ : OUT STD_LOGIC_VECTOR (7 DOWNTO 0));

END _____ ;

---------------------------------------

ARCHITECTURE example OF _____ IS

BEGIN

PROCESS (a, b, ____ )

BEGIN

IF (sel = "00") THEN

c <= "00000000";

ELSIF (__________) THEN

c <= a;

_____ (sel = "10") THEN

c <= __;

ELSE

c <= (OTHERS => '__');

END ___ ;

END _________ ;

END _________ ;

---------------------------------------

|

| EL2 - Resolução dos exercícios do Cap 3 |

|---|

|

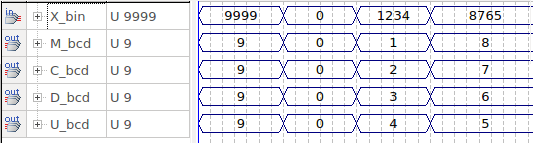

| EL3 - Conversor de Binário para BCD |

|---|

Fig. 20 - Simulação da conversão de binário para BCD

entity bin2bcd is

port (

X_bin : in std_logic_vector(13 downto 0); -- 0000 a 9999

M_bcd : out std_logic_vector(3 downto 0); -- Milhar

C_bcd : out std_logic_vector(3 downto 0); -- Centena

D_bcd : out std_logic_vector(3 downto 0); -- Dezena

U_bcd : out std_logic_vector(3 downto 0)); -- Unidade

end entity;

architecture example of bin2bcd is

--declaração de sinais auxiliares

begin

--descrição do hardware

end architecture;

M_bcd <= std_logic_vector(to_unsigned(M,4)); |

| EL4 - Resolução dos exercícios do Cap 4 |

|---|

|

| EL5 - Resolução dos exercícios do Cap 5 |

|---|

|

| EL6 - Resolução dos exercícios do Cap 6 |

|---|

|

| EL7 - Resolução dos exercícios do Cap 8 e 9 |

|---|

|

ARTIGOS ENTREGUES

- 2016-1

- Arquitetura FPGAs e CPLDs da ALTERA (André Felippe Weber, Helenluciany Cechinel, Maria Luiza Theisges)

- Aplicações de FPGA em Robótica (Letícia Aparecida Coelho, Katharine Schaeffer Fertig, Kristhine Schaeffer Fertig)

- FPGA aplicado a aviônica: Problemas e soluções (Gabriel Cantu, Lucas Lucindo, Thiago Grisolfi)

- Aplicações na Área Espacial (Marcos Vinicios Pinho, Fabiano Kraeamer, Iago Soares)

- Arquitetura FPGAs e CPLDs da XILINK (Anderson Demetrio, Gustavo Constante, Tamara Arrigoni)

- 2015-2

- DLPs: passado, presente e futuro (Walter Cardoso de Freitas Júnior, Gustavo Vieira Zacchi, Giulio Oliveira)

- Transitores CMOS, história e tecnologia (Fernando Müller da Silva, Gustavo Paulo Medeiros da Silva)

- Linguagens de Descrição de Hardware: Tipos e Características (João Vitor Rodrigues, Marcus Vinicius Bunn)

- Fabricantes e ferramentas para programação de DLPs (Ronaldo João Borges, Roicenir Girardi Rostirolla)

- Interface JTAG (Stephany Padilha Guimarães, Lucas Gomes de Farias, Vinicius Bandeira)

- 2015-1

- Formas como PLDs são Programados

- EPROM - EEPROM Dispositivos Lógicos Programáveis

- Aplicações de antifusíveis e PROMs na programação de PDLs

Recursos de Laboratório

Quartus/Modelsim/QSIM

Nos laboratórios do IFSC, os softwares Quartus/Modelsim/QSIM estão disponíveis diretamente na plataforma LINUX. Utilize preferencialmente a versão 13.0sp1 (32 bits), pois ela tem suporte para os FPGAs mais antigos como a familia Cyclone I.

Para uso fora do IFSC dos recursos computacionais com licença educacional, o IFSC disponibiliza para seus alunos o IFSC-CLOUD. Atualmente a forma mais eficiente de acesso é através do Cliente X2GO. O procedimento de instalação/ configuração e uso do Quartus/Modelsim/QSIM está descrito em Acesso ao IFSC-CLOUD#Cliente X2GO (recomendado).

Para a geração de documentação/relatórios técnicos/artigos, está disponibilizada a plataforma Sharelatex do IFSC-CLOUD. Utilize preferencialmente o modelo de artigo no padrão ABNT.

Links auxiliares

- Aritmética com vetores em VDHL

- Preparando para gravar o circuito lógico no FPGA

- Dicas de como eliminar o repique das chaves mecânicas

- Dicas para resolver ERROS de síntese do VHDL no Quartus II

- Materiais da ALTERA para Quartus II 13.1

- Modelo para uso em relatórios

- Configuração e uso do Time Quest Analyser

- Configuração e uso do Signal Tap

- DLP29006-Engtelecom(2015-1) - Prof. Marcos Moecke

- DLP29006-Engtelecom(2015-2) - Prof. Marcos Moecke

- DLP29006-Engtelecom(2016-1) - Prof. Marcos Moecke

Livros/Resumos sobre VHDL

- Regras de codificação em VHDL

- VHDL Handbook - Hardi (apenas VHDL’87 e VHDL’93)

- VHDL Math Tricks of the Trade by Jim Lewis

- VHDL QUICK REFERENCE CARD - Qualis (r2.1)

- VHDL 1164 PACKAGES QUICK REFERENCE CARD - Qualis (r2.2)

- VDHL ref

- Listagem dos packages

- Palavras reservadas

- Atributos predefinidos

- Aritmética em VHDL

Packages não padronizados

- Std logic arith.vhd by Synopsys

- std_logic_arith.vhd by Synopsys

- std_logic_arith.vhd by Mentor Graphics

- std_logic_arith.vhd by Vinaya

- Std logic unsigned.vdh by Synopsys

- std_logic_unsigned.vhd by Synopsys

Simulador Modelsim

- Site Mentor Graphics - Software Version 10.0

- ModelSim InfoHub - Software Version v10.2c

- ModelSim Quick Video Demo - precisa fazer login na Mentor Graphics.

- ModelSim® Tutorial -v10.0d

- ModelSim® Reference Manual -v10.0d

- ModelSim® User’s Manual -v10.0d

- ModelSim® Quick Guide -v10.0d

- ModelSim® SE GUI Reference Manual -v10.2c

Fabricantes de DLPs

- Altera, new Altera

- Xilinx, PLDs

- Lattice

- Microsemi

- Atmel

- Achronix

- Tabula, Who killed the FPGA startup Tabula semiconductor?

- Market share 2013

- INTEL

Fabricantes de kits com DLPS

Leituras recomendadas

- USE OF FIELD PROGRAMMABLE GATE ARRAY TECHNOLOGY IN FUTURE: SPACE AVIONICS, Roscoe C. Ferguson, Robert Tate, NASA.

- Expect a Breakthrough Advantage in NextGeneration FPGAs, Stephen Lim, ALTERA.

- A Reconfigurable Fabric for Accelerating Large-Scale Datacenter Services, Microsoft.

Padrões IEEE para o VDHL

Os padrões IEEE [3]estão disponíveis para consulta se você estiver na rede do IFSC. Para a linguagem VHDL consulte os padrões: 1164,1076

- IEEE Standard Multivalue Logic System for VHDL Model Interoperability (Std_logic_1164)

- IEEE Std 1076.1: Behavioural languages – Part 1-1: VHDL language reference manual

- IEEE Std 1076.1: Behavioural languages – Part 6: VHDL Analog and Mixed-Signal Extensions

- IEEE Std 1076.1.1™-2011 - IEEE Standard for VHDL Analog and Mixed-Signal Extensions—Packages for Multiple Energy Domain Support, REDLINE

- IEEE Standard for VHDL Register Transfer Level (RTL) Synthesis

- IEEE Standard VHDL Analog and Mixed-Signal Extensions

- IEEE Standard VHDL Synthesis Packages

- IEEE Std 1076-2002: IEEE Standard VHDL Language Reference Manual

- IEEE Std 1076.2-1996: IEEE Standard VHDL Mathematical Packages

Packages da IEEE

Referências Bibliográficas: