DLP1-EngTel (página)

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

- Link curto http://bit.ly/IFSC-DLP29006

- Carga horária, Ementas, Bibliografia, Professores

- Cronograma de atividades

- Plano de Ensino

Registro on-line das aulas

Unidade 1

- Aula 1 (11 Ago)

- Introdução aos dispositivos lógicos programáveis:

- Conceito, tipos de PLDs

- SPLD: PAL, PLA e GAL

- CPLDs

| Exemplos de PLDs |

|---|

|

- Ver Dispositivos Lógicos Programáveis - Kamila Rose da Silva, IFSC

- Ver In the befinning - ALTERA

- Ver ALTERA history

- Ver pag. 413 a 422 de [1]

- Ver pag. 495 a 499 de [2]

- Aula 2 (16 Ago)

- Introdução aos dispositivos lógicos programáveis:

- Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, RAM, DSP, Clock, PLL, I/O

- Vizualização no Chip Planner de um projeto. (importante todos alunos terem acesso a IFSC-CLOUD

- Aula 3 (18 Ago)

-

- Fabricantes de DLPs/FPGAs e familias de DLPs atuais.

- Preços

- Historia, processo de produção dos chips.

- A Brief History of the Fabless Semiconductor Industry

- Taiwan Semiconductor Manufacturing Corporation (TSMC), [http://www.globalfoundries.com/ GLOBALFOUNDRIES

- Fabless: The Transformation of the Semiconductor Industry, 2014 - Download free

- 14nm FinFET Technology, Samsung & Globalfounfries, Funcionamento do FinFET, Produção do FinFET, [1]

- Processo de fabricação de um chip

Unidade 2

- Aula 3 (22 Ago) - Introdução ao VHDL e ambienta EDA - QUARTUS

- Estrutura do código VHDL

- Declaração das bibliotecas e pacotes LIBRARY / PACKAGE

library library_name; use library_name.package)name.all;

- ENTITY

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

- ARCHITECTURE

architecture arch_name of entity_name is [declarative_part] begin statement_part end [architecture] [arch_name];

- Exemplo - Declaração de uma porta NAND em VHDL

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

- Exemplo 2.2 (VHDL) - programação de um flip-flop

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

- Após a criação do projeto em VHDL utilizando a descrição de hardware acima, compile o código VHDL.

- Use o RTL Viewer para ver a descrição RTL do circuito.

- Use o Technology Map Viewer para ver a como o circuito foi mapeado para os elementos lógicos disponíveis no dispositivo FPGA selecionado (EP1C3T100A8)

- Abra o Chip Planner e observe no Node Properties como esse circuito é conectado dentro do dispositivo FPGA selecionado

- Aula 4 (23 Ago) - Introdução ao VHDL e ambienta EDA - QUARTUS

- Estrutura do código VHDL

- Exemplo 2.3 (VHDL e QSIM) - programação de um circuito somador com registrador

- Realizar as simulações funcional e temporal do circuito

- Observar o "Technology Map" e o "RTL" do circuito

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END;

ARCHITECTURE circuit OF registered_comp_add IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END;

- Acrescente saídas para o sinal sum e para o sinal comp, de modo a poder observar estes sinais no simulador QSIM e realize novas simulações funcional e temporal.

- Para conhecer melhor o ambiente do simulador QSIM veja Arquivo:Quartus II Simulation.pdf da ALTERA.

- Ver pag. 3 a 24 de [2]

Unidade 3

- Aula 5 (25 Ago)

- Tipos de Dados em VHDL.

- Objetos de VHDL: CONSTANT, SIGNAL, VARIABLE, FILE.

- Palavra chave OTHERS

- Ver pag. 31 a 35 de [2]

- Aula 6 (29 Ago)

- Tipos de Dados em VHDL.

- Bibliotecas padrão IEEE (std_logic_1164, numeric_std).

- ATENÇÃO!!! Não use as bibliotecas que não são padrão (std_logic_arith, std_logic_unsigned, std_logic_signed)

- Classificação dos tipos de dados.

- Tipos de dados: BIT, BIT_VECTOR, BOOLEAN, INTEGER, NATURAL, POSITIVE, CHARACTER, STRING, STD_(U)LOGIG, STD_(U)LOGIG_VECTOR

- Exemplo 3.1 Buffer Tri-state

- Exemplo 3.2 Circuito com Saida "don't care"

- Ver pag. 39 a 51 de [2]

- Tipos de dados: SIGNED e UNSIGNED

- Exemplo 3.3 Multiplicador (un)signed

- Tipos de dados: FIXED e FLOAT (apenas conhecer)

- Resumo dos Tipos predefinidos (Tabela 3.6).

- Tipos definidos pelo usuário:

- Escalares (Inteiros e Enumerados)

- Tipos de Array 1D x 1D, 2D , 1D x 1D x 1D, 3D

- RECORD e SUBTYPE

- Exemplo 3.8: Multiplexador com porta 1D x 1D.

- Ver pag. 51 a 73 de [2]

Unidade 4

- Aula 13 (13 Set)

- Código Concorrente.

- Uso de Operadores

- WHEN, SELECT;

- Exemplo 5.1 + 5.2 mux: com 3 tipos de arquiteturas (com operadores, com WHEN, com SELECT)

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY mux IS

GENERIC (N: INTEGER :=8);

PORT (x0, x1, x2, x3: IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

sel: IN STD_LOGIC_VECTOR(1 DOWNTO 0);

y: OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0));

END mux;

-- Arquitetura para a implementação discreta através de portas AND e OR

ARCHITECTURE Operator_only OF mux IS

signal sel0_8: STD_LOGIC_VECTOR(N-1 DOWNTO 0);

signal sel1_8: STD_LOGIC_VECTOR(N-1 DOWNTO 0);

BEGIN

sel0_8 <= (OTHERS => sel(0));

sel1_8 <= (OTHERS => sel(1));

y <= (NOT sel1_8 AND NOT sel0_8 AND x0) OR

(NOT sel1_8 AND sel0_8 AND x1) OR

(sel1_8 AND NOT sel0_8 AND x2) OR

(sel1_8 AND sel0_8 AND x3);

END operators_only;

- Para selecionar uma entre várias arquiteturas para a mesma ENTITY use a CONFIGURATION.

CONFIGURATION which_mux OF mux IS

FOR Operator_only END FOR;

-- FOR with_WHEN END FOR;

-- FOR with_SELECT END FOR;

END CONFIGURATION;

- Ver pag. 121 a 127 de [2]

- Aula 14 ()

- Código Concorrente.

- Uso de GENERATE

label: FOR identificador IN faixa GENERATE

[Parte_Declarativa

BEGIN]

Instruções_concorrentes

...

END GENERATE [label];

</syntaxhighlight>

- Exemplo 5.4 - Decodificador genérico de endereços.

- Exemplo 5.5 - Instanciação de COMPONENTE com GENERATE.

- Ver pag. 127 a 134 de [2]

- Aula 15 ()

- Código Concorrente.

- Exemplo de uso de operadores e SELECT.

- Exemplo 5.3 - Unidade de Lógica e Aritmética (ALU).

- Alteração do código da ALU:

- Inclusão de um sinal que indica "erro" quando ocorre overflow/underflow nas operações de soma, incremento ou decremento.

- Inclusão de um circuito que satura o sinal no máximo positivo ou negativo nas situações de erro.

- Teste da ALU usando simulação funcional.

- Aula 16 ()

- Código Concorrente.

- Implementação de circuitos aritméticos com operadores.

- Para o uso dos operadores o mais adequado é utilizar o padrão industrial STD_LOGIC_VECTOR. Internamente os valores das portas devem ser convertidos ou para valores INTEGER ou para UNSIGNED/SIGNED. para tal é necessário utilizar a biblioteca numeric_std.

- Também é fundamental considerar a faixa de valores coberta por bits. Para tipos UNSIGNED a faixa é de até , enquanto que para SIGNED a faixa é de até . Assim com 3 bits é possível representar valores entre -4 até 3 com um tipo SIGNED e 0 até 7 com um tipo UNSIGNED.

- Para uso adequado dos operadores também é necessário considerar o tamanho (número de bits) requirido para o resultado em função do tamanho dos operandos.

- Para operações de "+" ou "-": O tamanho do resultado é igual ao tamanho do maior operando.

- Exemplo: r[7..0] = a[7..0] + b[4..0]; a -> 8 bits; b -> 5 bits então r -> 8 bits.

- Para a operações "*": O tamanho do resultado é igual a soma do tamanho dos dois operandos.

- Exemplo: r[12..0] = a[7..0] * b[4..0]; a -> 8 bits; b -> 5 bits então r -> 8+5 = 13 bits.

- Para "/": O tamanho do resultado é igual ao tamanho do numerador.

- Exemplo: r[5..0] = a[5..0] / b[8..0]; a -> 6 bits; b -> 9 bits então r -> 6 bits.

- No caso da operações de "*" e "/" não ocorre overflow, no entanto no caso da "+" e "-", o overflow pode ocorrer e precisa ser tratado. Isso pode ser feito acrescentando um bit adicional a saída para conter o overflow ou então sinalizar a sua ocorrência.

- Aula de exercícios:

- 5.3 - Porta AND e NAND Genérica.

- 5.4 - Gerador de Paridade Genérico.

- Aula 18 a 19 ()

- Código Concorrente.

- Relógio HH:MM:SS

- Aula 20 a 21 ()

- Simulação com Modelsim

- Exemplo do Relógio HH:MM:SS

- Aula 22 ()

- Código Concorrente.

- Aula de exercícios: Escreve um código VHDL genérico que implemente os seguintes circuitos:

- Ex1 - Conversor de Binário para Gray genérico;

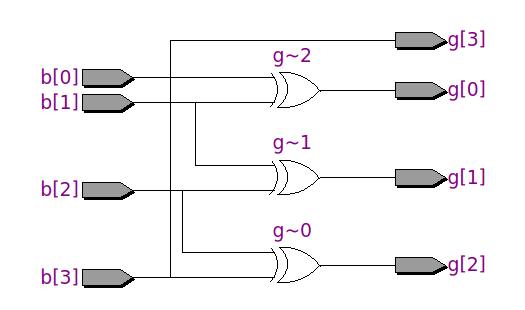

Fig 16. código RTL do conversor binário para Gray - Ex2 - Conversor de Gray para Binário genérico;

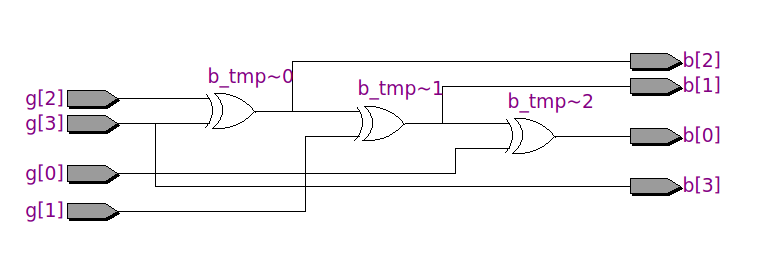

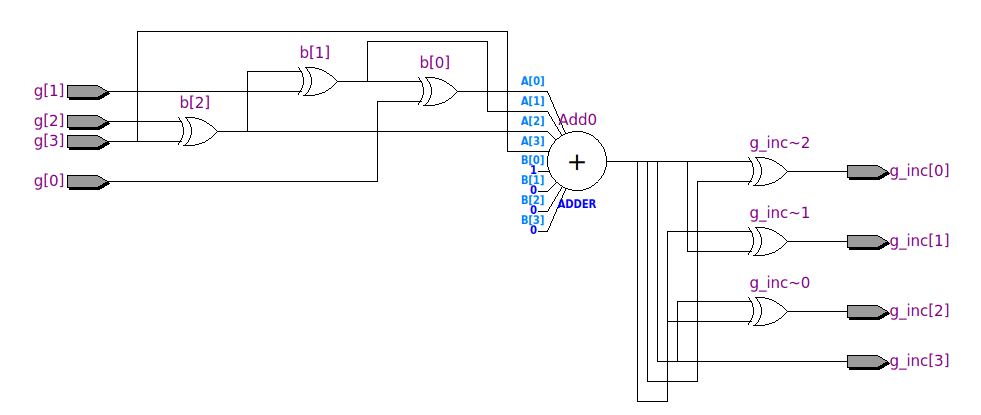

Fig 17. código RTL do conversor Gray para binário - Ex3 - Utilizando os dois circuitos anteriores e um incrementador binário escreva um código VHDL que implemente um incrementador Gray;

Fig 18. código RTL do incrementador de código Gray

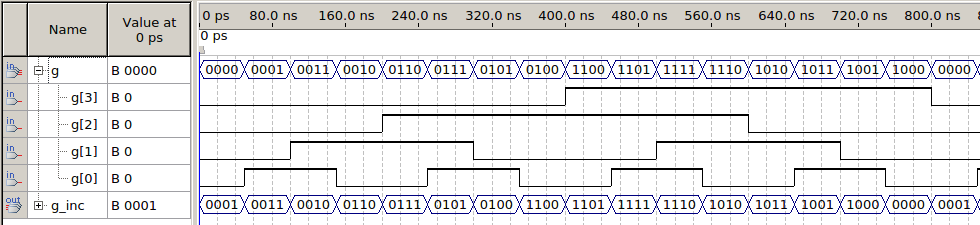

Fig 19. Simulação Funcional do incrementador de código Gray - Ver também Código Gray;

- Aula de exercicios:

- 5.4 - Generic Parity Generator;

- 5.6 - Generic Binary-to-Gray Converter;

- 5.7 - Hamming Weight with GENERATE;

- 5.10/11 - Arithmetic Circuit with INTEGER/STD_LOGIC;

- 5.15/16/17/18 - (Un)signed Multiplier/Divider;

- 5.19 - Frequency Multiplier.

Unidade 5

- Aula 20 ()

- Código Sequencial.

- Diferenças entre código concorrente e sequencial <=> circuitos combinacional e sequencial

- Diferenças entre os objetos SIGNAL e VARIABLE

- Tipos de elementos de memória: Latch x Flip-flop

- Latch D

- Flip-flop tipo D com reset assíncrono e com reset (clear) síncrono

- Seção de código sequencial PROCESS: lista de sensibilidade

[rótulo:] PROCESS [(lista_de_sensibilidade)] [IS]

[parte_declarativa]

BEGIN

afirmação_sequencial;

afirmação_sequencial;

...

END PROCESS [rótulo];

- Instrução IF

[rótulo:] IF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSIF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSE

afirmação_sequencial;

afirmação_sequencial;

...

END IF [rótulo];

- Exemplos: DFFs with Reset and Clear (Variação Ex 6.1), Basic Counter (Ex. 6.2), Shift Register (Ex. 6.3)

- Instrução WAIT: WAIT UNTIL, WAIT FOR (simulação apenas), WAIT ON (não implementada no Quartus II).

- Algumas instruções de WAIT serão utilizadas na criação de TestBench em VHDL para a simulação com o MODELSIM.

- Recomenda-se utilizar a lista de sensibilidade do PROCESS e a instrução IF no lugar do WAIT.

- Ver pag. 161 a 160 de [2]

- Aula 21 ()

- Código Sequencial.

- Instruções do tipo LOOP: LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT

- LOOP incondicional:

[rótulo:] LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

- FOR-LOOP:

[rótulo:] FOR identificador IN faixa LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

- WHILE-LOOP:

[rótulo:] WHILE condição LOOP -- Executa as "afirmações enquanto a "condição" for verdadeira

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

- LOOP com EXIT:

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

EXIT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, termina o "LOOP"

afirmação_sequencial;

...

END LOOP [rótulo];

- LOOP com NEXT:

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

NEXT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, não executa as linhas até a linha "END LOOP"

-- e incrementa o "identificador".

afirmação_sequencial;

...

END LOOP [rótulo];

- Exemplos: Carry-Ripple Adder (FOR-LOOP) (Ex 6.4),

- Ver pag. 161 a 164 de [2]

- Aula 22 ()

- Código Sequencial.

- Instrução CASE

[rótulo:] CASE expressão IS

WHEN valor => atribuições; -- valor único

...

WHEN valor1 | valor2 | ... | valorN => atribuições; -- lista de valores

...

WHEN valor1 TO valor2 => atribuições; -- faixa de valores

...

END CASE;

- Exemplos:

- Leading Zeros (LOOP com EXIT) (Ex 6.5)

- Contador de 0 a 9 segundos com saída SSD (Ex 6.6)

- Projeto ruim com CASE incompleto (Ex. 6.7)

- Exercícios do Capitulo 6

- Ver pag. 164 a 176 de [2]

- Aula 23 (20/10)

- Código Sequencial.

- Exercícios do Capítulo 6.

- Uso do ModelSim - salvamento do wave.do

- Divisão dos exercícios entre duplas de alunos.

Ex 6.3 - Mateus, Paula, Andrey

Ex 6.5 - Bruno, Murilo, Kleiton

Ex 6.6 - Henrique, Matias

Ex 6.7 - Natália, Luísa

Ex 6.10a (incrementando de 00 até XX - Jessica e Letícia

Ex 6.10a (decrementando de XX até 00 - Layssa e Alline

Ex 6.11 - Gabriel S, Gustavo W,

Ex.6.15 - Daniel, Nelson, Gabriel W

- Durante a aula os alunos foram orientados na resolução dos exercícios, e simulação usando o Modelsim.

- Os alunos devem enviar o arquivo QAR contendo o projeto e simulação para o email do professor.

- Discuta com os colegas como resolveram o Exercício proposto para eles. Cada aluno deverá saber solucionar todos os exercícios.

Unidade 6

- Aula 26 ()

- Projeto a nível de Sistema.

- O PACKAGE e PACKAGE BODY: onde declarar e como usar.

- O COMPONENT: declaração (cópia da ENTITY) e instanciação.

- Associação dos nomes das portas aos sinais. PORT -> PORT MAP:

- Mapeamento por posição e nominal.

- Métodos de declaração de COMPONENT.

- Exemplo: Registrador Circular Ex. 8.2, usando como componente básico o mux junto com o DFF.

- Ver pag. 201 a 208 de [2]

- Resolução dos exercícios:

- Aula 27 ()

- Projeto a nível de Sistema.

- Criação de COMPONENT redimensionáveis. GENERIC -> GENERIC MAP

- Exemplo: Porta E com N entradas.

- Exemplo: Detector de Paridade Ex. 8.3

- Instanciação de COMPONENT com GENERATE.

- Exemplo: Alterar o exercício 8.2 realizando a instanciação dos componentes com FOR GENERATE. Instanciar duas vezes o Registrador Circular com 8 e 16 bits, sendo os 8 primeiros bits de entrada comuns aos dois registradores.

- Exercício: Registrador de deslocamento M x N Ex. 8.4

- Ver pag. 208 a 213 de [2]

- Aula 28 ()

- Projeto a nível de Sistema.

- Uso da instrução CONFIGURATION.

- Ligação direta: ARCHITECTURE-ENTITY.

- Ligação da instanciação dos componentes: COMPONENT-ENTITY(ARCHITECTURE).

- Exercício 28.1: Inserir as duas soluções de ARCHITECTURE do exercício EX 6.10 (Timer de dois digitos) em uma única ENTITY. Utilizar CONFIGURATION para fazer a ligação com a arquitetura desejada.

entity counter60seg is

generic (fclk: integer := 2); -- valor usado para simulação.

-- generic (fclk: integer := 50_000_000); -- valor usado para implementação com clk de 50 MHz.

port (

clk, rst : in std_logic;

ssd_un, ssd_dz: out std_logic_vector(6 downto 0));

end entity ;

architecture version1 of counter60seg is

...

begin

...

end architecture ;

architecture version2 of counter60seg is

...

begin

...

end architecture ;

configuration counter60seg_cfg of counter60seg is

for version1 end for;

-- for version2 end for;

end configuration;

- Exercício 8.2: Componentização do circuito conversor de binário para display de sete segmentos. Também modifique a descrição vhdl de modo que a interface dos componentes sejam do tipo std_logic ou std_logic_vector.

entity bin2ssd is

port (

bin: in std_logic_vector(3 downto 0);

ssd: out std_logic_vector(6 downto 0));

end entity ;

architecture with_case of bin2ssd is

...

begin

...

end architecture ;

- Aula 29 e 30 ()

- Projeto hierárquico em equipes do circuito lançador de foguete.

- Subsistema 1a - Contador incrementador (de 00 a 99) -

- Subsistema 1b - Contador decrementador (de 99 a 00) -

- Subsistema 2a - Contador em anel -

- Subsistema 2a - Shift register -

- Subsistema 3a - Mostrador SSD com case - Daniel e Nelson

- Subsistema 3b - Mostrador SSD com with select - Natalia e Luisa

- Integração e implementação na DE2-115

- Integração e implementação na DE2-115

- Integração e implementação na Mercurio IV

- Aula 31(7/11)

- Resolução de exercícios do capitulo 6

- Ex 6.5 Shift register - Bruno e Murilo

- Ex 6.3 Mux NxM - Matheus, Paulo e Andrey

- Ex 6.15 Serializador - Daniel e Nelson

- Aula 32 (8/11)

- Projeto hierárquico em equipes do circuito lançador de foguete.

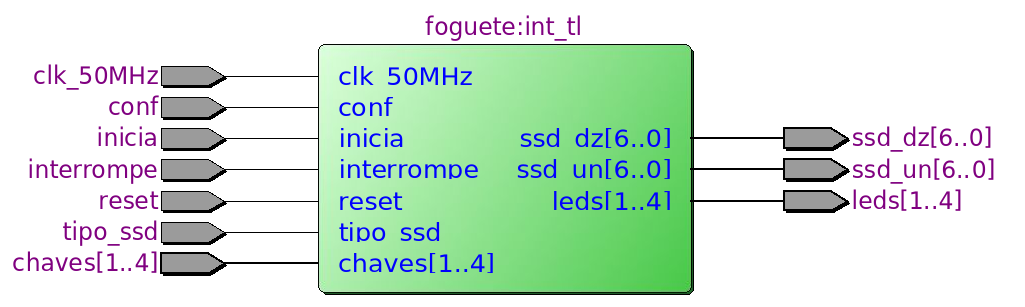

Fig.1 - RTL do Top Level do projeto do simulador de lançamento de foguete.

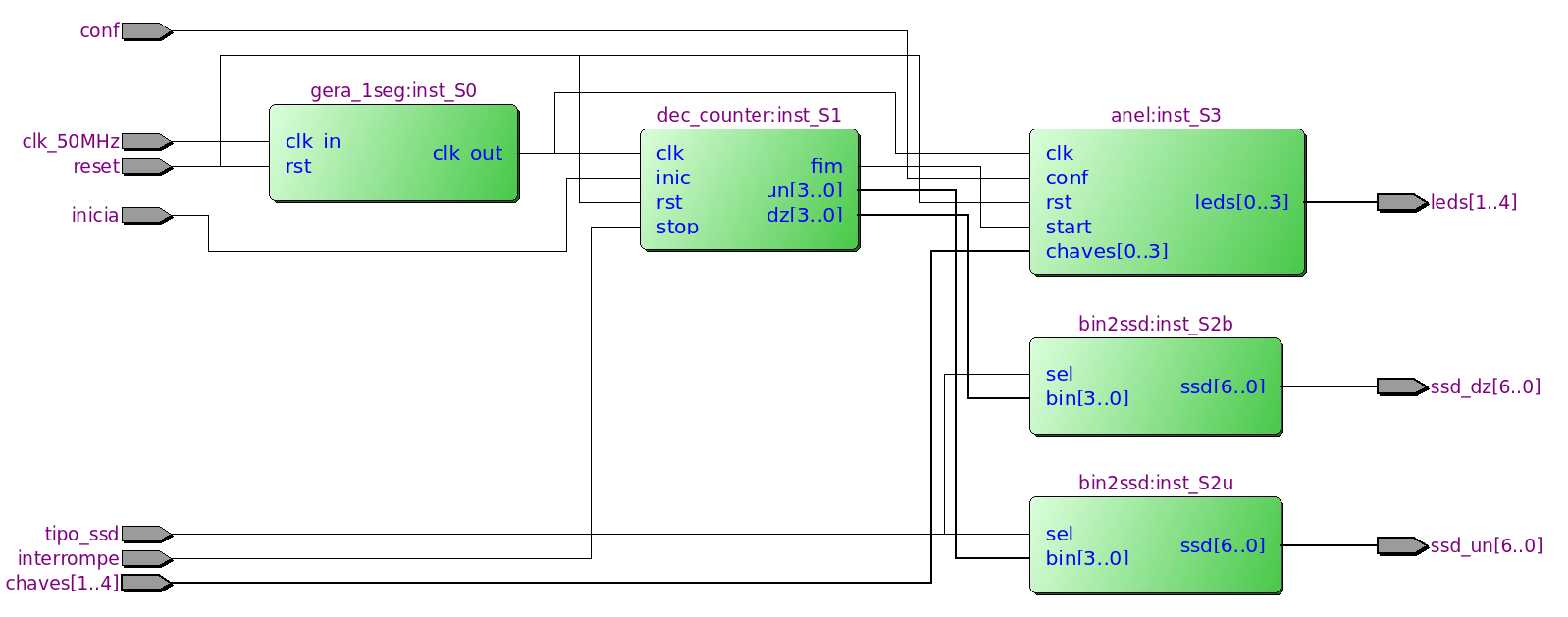

Fig.2 - RTL dos componentes do simulador de lançamento de foguete.

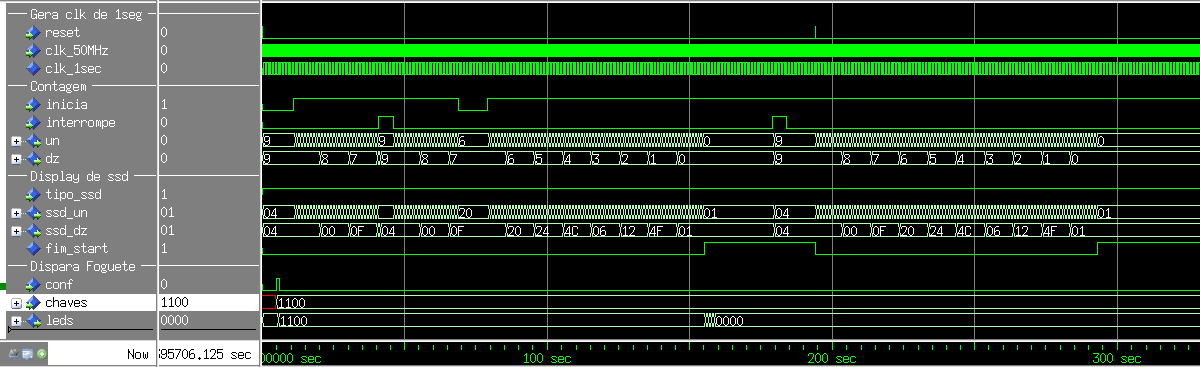

Fig.3 - Simulação no ModelSim do lançamento de foguete.

Avaliações

- Avaliação A1 - Unidade 2 a 4 (13/10/2016) - Local: Lab Redes II.

- Avaliação A2 - Unidade 5 a 7 (XX/XX/2016) - Local: Lab Redes II.

- As avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues VHDL QUICK REFERENCE CARD e VHDL 1164 PACKAGES QUICK REFERENCE CARD. Dica use também como fonte de consulta os templates do Quartus.

- Recuperação R1-2 - Unidade 2 a 7 (XX/XX/2016) - Local: Lab Redes II.

- Ao final das avaliações o aluno deverá enviar para o email moecke AT ifsc.edu.br com os arquivos solicitados.

- Entrega dos Atividades Extraclasse ao longo do semestre AE1 a AE(N-1). Os prazos serão indicados aqui na Wiki

- Projeto Final APF (XX/XX/2016).

Atividades extraclasse

Neste tópico serão listadas as atividades extraclasse que os alunos/equipes deverão realizar ao longo do semestre.

PARA ENTREGAR

AE1 - Temas relacionados aos DLPS (Prazo de entrega do resumo (500 caracteres/ 1 pagina): 09 setembro 2016 até as 23:59), Prazo de entrega do artigo: 07 de outubro de 2016

- Formar equipes com 2 ou 3 alunos, e em conjunto façam uma pesquisa sobre um tema relacionado a DLPs.

- TEMA 1 - FPGA x Microprocessador - Vantagens e desvantagens (Daniel e Nelson)

- TEMA 2 - Analisadores lógicos em FPGA (Mateus, Paula e Andrey)

- TEMA 3 - Simuladores de VHDL (Modelsim e QSIM) (Bruno e Murilo)

- TEMA 4 - Processamento de vídeo em FPGA(Mathias, Lucas e Henrique)

- TEMA 5 - FPGA na industria automotiva (Natalia e Luisa)

- TEMA 6 - Aplicações em redes neurais (Jessica, Leticia e Gabriel S,)

- TEMA 7 - Aplicação de Tecnologia de Segurança usando FPGA e SoCs(Kleiton, Gustavo W. e Gabriel W.)

- TEMA 8 - Aplicações em Imagens Médicas (João, Alline e Layssa)

- INSPIRAÇÃO para temas:

- https://www.altera.com/about/company/history.html

- https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html

- https://www.altera.com/products/fpga/new-to-fpgas/resource-center/overview.html

- http://www.extremetech.com/extreme/184828-intel-unveils-new-xeon-chip-with-integrated-fpga-touts-20x-performance-boost

- https://www.altera.com/products/fpga/overview.html

- https://www.altera.com/products/cpld/max-series.html

- https://www.altera.com/solutions/industry.html

- http://www.xilinx.com/training/fpga/fpga-field-programmable-gate-array.htm

- http://www.springer.com/cda/content/document/cda_downloaddocument/9781461435938-c2.pdf

- Architecture of FPGAs (Xilinx, Altera, Atmel, Lattice, etc). [2], [3]

- http://ieeexplore.ieee.org/search/searchresult.jsp?queryText=fpga&newsearch=true

- http://ieeexplore.ieee.org/search/searchresult.jsp?queryText=vhdl&newsearch=true

- Escrever um artigo com 4 a 6 páginas A4. O artigo deve ser completo, incluindo todas as referências utilizadas. Dê um título coerente ao artigo. Seja criativo.

- Para a geração de documentação/relatórios técnicos/artigos, está disponibilizada a plataforma Sharelatex do IFSC-CLOUD. Utilize preferencialmente o modelo de artigo no padrão ABNT. Outro modelo de artigo que pode ser utilizado é o da Elsevier. Consulte também Uso do ShareLaTeX na IFSC-CLOUD.

- Envie o resumo em pdf para (moecke AT ifsc.edu.br), com o ASSUNTO: DLP29006 - AE1 - Temas relacionados aos DLPS - resumo.

- Envie o artigo em pdf para (moecke AT ifsc.edu.br), com o ASSUNTO: DLP29006 - AE1 - Temas relacionados aos DLPS - artigo.

AE2 - Uso de código concorrente - ALU modificada (Prazo de entrega 30/09/2016)

- Implemente em VHDL uma Unidade de Lógica e Aritmética que tem como entrada os sinais A e B e que execute as seguintes instruções lógicas e aritméticas conforme o opcode de entrada:

- Unidade Lógica

Instrução

Operação

opcode

GRUPO

Complemento de A

Y = not A

00000

1

Complemento de B

Y = not B

00001

2

And

Y = A nand B

00010

3

Nand

Y = A and B

00011

4

Or

Y = A nor B

00100

1

Nor

Y = A or B

00101

2

Xor

Y = A xor B

00110

3

Xnor

Y = A xnor B

00111

4

- Unidade Aritmética

- (onde os valores de A e B podem ser positivos ou negativos)

Instrução

Operação

opcode

GRUPO

Transfere A

Y = A

01000

1

Transfere B

Y = B

10001

2

complemento-2 de A

Y = -A

01001

3

complemento-2 de B

Y = -B

10001

4

Incrementa A

Y = A + 1

01010

1

Decrementa A

Y = A - 1

01011

2

Incrementa B

Y = B + 1

10010

3

Decrementa B

Y = B - 1

10011

4

Soma A e B

Y = A + B

11000

1,2,3,4

Subtrai B de A

Y = A - B

11001

1,3

Subtrai A de B

Y = B - A

11010

2,4

LSB da Multiplicação de A e B

Y = A * B

11011

1,2

MSB da Multiplicação de A e B

Y = A * B

11100

3,4

Dobra o valor A

Y = A * 2

01100

1

Dobra o valor B

Y = B * 2

10100

2

Metade do valor A

Y = A / 2

01101

3

Metade do valor B

Y = B / 2

10101

4

Divisão de A / B

Y = A / B

11101

1,2,3,4

Resto da Divisão de A / B

Y = A REM B

11110

1,2,3,4

- A ENTITY deverá ter a seguinte interface:

ENTITY alu IS

GENERIC (N: INTEGER := 4); --word bits

PORT (

A, B: IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

opcode: IN STD_LOGIC_VECTOR(4 DOWNTO 0);

Y: OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0));

END ENTITY;

- Proponha uma ARCHITECTURE que implemente a ALU (Dica: utilize o tipo de dado tipo integer).

- Escolha no FACEBOOK um dos GRUPOS de instruções indicados pelos números 1, 2, 3 e 4 na coluna GRUPO.

- Na multiplicação LSB são os N bits menos significativos do resultado, e MSB são os N bits mais significativos do resultado. Por exemplo se o resultado tem 10 bits "1001001011" MSB = "10010" e LSB = "01011".

- Anote o número de Elementos Lógicos (ou ALUTs) utilizados [Compilation Report > Flow Summary].

- Verifique o código RTL gerado [Tools > Netlist Viewers > RTL Viewer]

- Faça a simulação funcional no QSIM com 8 pares de valores (use os valores mínimos e máximos e outros pares de valores representáveis) e verifique se o resultado das operações está correto. Teste cada instrução (opcode) em separado.

- Analise os resultados obtidos para entradas com 4 bits. Verifique os casos em que há overflow.

- Escreva um relatório contendo o código VHDL, a figura do circuito RTL, as simulações funcionais solicitadas e uma análise dos resultados obtidos. Relate o número de elementos lógicos utilizados.

- Envie o artigo em pdf e o qar para (moecke AT ifsc.edu.br), com o ASSUNTO: DLP29006 - AE2 - Uso de código concorrente - ALU modificada.

ARTIGOS ENTREGUES

- 2016-2

- 2016-1

- Arquitetura FPGAs e CPLDs da ALTERA (André Felippe Weber, Helenluciany Cechinel, Maria Luiza Theisges)

- Aplicações de FPGA em Robótica (Letícia Aparecida Coelho, Katharine Schaeffer Fertig, Kristhine Schaeffer Fertig)

- FPGA aplicado a aviônica: Problemas e soluções (Gabriel Cantu, Lucas Lucindo, Thiago Grisolfi)

- Aplicações na Área Espacial (Marcos Vinicios Pinho, Fabiano Kraeamer, Iago Soares)

- Arquitetura FPGAs e CPLDs da XILINK (Anderson Demetrio, Gustavo Constante, Tamara Arrigoni)

- 2015-2

- DLPs: passado, presente e futuro (Walter Cardoso de Freitas Júnior, Gustavo Vieira Zacchi, Giulio Oliveira)

- Transitores CMOS, história e tecnologia (Fernando Müller da Silva, Gustavo Paulo Medeiros da Silva)

- Linguagens de Descrição de Hardware: Tipos e Características (João Vitor Rodrigues, Marcus Vinicius Bunn)

- Fabricantes e ferramentas para programação de DLPs (Ronaldo João Borges, Roicenir Girardi Rostirolla)

- Interface JTAG (Stephany Padilha Guimarães, Lucas Gomes de Farias, Vinicius Bandeira)

- 2015-1

ESTUDOS SEM ENTREGA DE DOCUMENTAÇÃO

Os exemplos e exercícios essenciais estão destacados em negrito na listagens abaixo.

EL1 - Resolução dos exercícios do Cap 3

- Resolva os exercícios do capítulo 3 (1, 2, 9, 11, 12, 13, 14-17, 18, 20, 22, 23-30) pag. 81 a 89

EL2 - Resolução dos exercícios do Cap 4

- Resolva os exercícios do capítulo 4 (4-8, 9, 10-11, 13, 15-16, 17 ) pag. 115 a 120

EL3 - Resolução dos exercícios do Cap 5

- Resolva os exercícios do capítulo 5 (1, 2, 3, 4, 6, 7, 8-9, 10-11, 14-16, 17-18, 19 ) pag. 144 a 150

Recursos de Laboratório

Quartus/Modelsim/QSIM

Nos laboratórios do IFSC, os softwares Quartus/Modelsim/QSIM estão disponíveis diretamente na plataforma LINUX. Utilize preferencialmente a versão 13.0sp1 (32 bits), pois ela tem suporte para os FPGAs mais antigos como a familia Cyclone I.

Para uso fora do IFSC dos recursos computacionais com licença educacional, o IFSC disponibiliza para seus alunos o IFSC-CLOUD. Atualmente a forma mais eficiente de acesso é através do Cliente X2GO. O procedimento de instalação/ configuração e uso do Quartus/Modelsim/QSIM está descrito em Acesso ao IFSC-CLOUD#Cliente X2GO (recomendado).

Para a geração de documentação/relatórios técnicos/artigos, está disponibilizada a plataforma Sharelatex do IFSC-CLOUD. Utilize preferencialmente o modelo de artigo no padrão ABNT.

Links auxiliares

- Aritmética com vetores em VDHL

- Preparando para gravar o circuito lógico no FPGA

- Palavras reservadas do VHDL

- Dicas de como eliminar o repique das chaves mecânicas

- Dicas para resolver ERROS de síntese do VHDL no Quartus II

- Materiais da ALTERA para Quartus II 13.1

- Modelo para uso em relatórios

- Configuração e uso do Time Quest Analyser

- Configuração e uso do Signal Tap

- Calculadora de Complemento de 2

- DLP29006-Engtelecom(2015-1) - Prof. Marcos Moecke

- DLP29006-Engtelecom(2015-2) - Prof. Marcos Moecke

- DLP29006-Engtelecom(2016-1) - Prof. Marcos Moecke

Livros/Resumos sobre VHDL

- Regras de codificação em VHDL

- VHDL Handbook - Hardi (apenas VHDL’87 e VHDL’93)

- VHDL Math Tricks of the Trade by Jim Lewis

- VHDL QUICK REFERENCE CARD - Qualis (r2.1)

- VHDL 1164 PACKAGES QUICK REFERENCE CARD - Qualis (r2.2)

- VDHL ref

- VHDL Golden Reference Guide

- Listagem dos packages

- Palavras reservadas

- Atributos predefinidos

- Aritmética em VHDL

Packages não padronizados

- Std logic arith.vhd by Synopsys

- std_logic_arith.vhd by Synopsys

- std_logic_arith.vhd by Mentor Graphics

- std_logic_arith.vhd by Vinaya

- Std logic unsigned.vdh by Synopsys

- std_logic_unsigned.vhd by Synopsys

Simulador Modelsim

- Site Mentor Graphics - Software Version 10.0

- ModelSim InfoHub - Software Version v10.2c

- ModelSim Quick Video Demo - precisa fazer login na Mentor Graphics.

- ModelSim® Tutorial -v10.0d

- ModelSim® Reference Manual -v10.0d

- ModelSim® User’s Manual -v10.0d

- ModelSim® Quick Guide -v10.0d

- ModelSim® SE GUI Reference Manual -v10.2c

Fabricantes de DLPs

Fabricantes de kits com DLPS

Leituras recomendadas

- USE OF FIELD PROGRAMMABLE GATE ARRAY TECHNOLOGY IN FUTURE: SPACE AVIONICS, Roscoe C. Ferguson, Robert Tate, NASA.

- Expect a Breakthrough Advantage in NextGeneration FPGAs, Stephen Lim, ALTERA.

- A Reconfigurable Fabric for Accelerating Large-Scale Datacenter Services, Microsoft.

Padrões IEEE para o VDHL

Os padrões IEEE [4]estão disponíveis para consulta se você estiver na rede do IFSC. Para a linguagem VHDL consulte os padrões: 1164,1076

- IEEE Standard Multivalue Logic System for VHDL Model Interoperability (Std_logic_1164)

- IEEE Std 1076.1: Behavioural languages – Part 1-1: VHDL language reference manual

- IEEE Std 1076.1: Behavioural languages – Part 6: VHDL Analog and Mixed-Signal Extensions

- IEEE Std 1076.1.1™-2011 - IEEE Standard for VHDL Analog and Mixed-Signal Extensions—Packages for Multiple Energy Domain Support, REDLINE

- IEEE Standard for VHDL Register Transfer Level (RTL) Synthesis

- IEEE Standard VHDL Analog and Mixed-Signal Extensions

- IEEE Standard VHDL Synthesis Packages

- IEEE Std 1076-2002: IEEE Standard VHDL Language Reference Manual

- IEEE Std 1076.2-1996: IEEE Standard VHDL Mathematical Packages

Packages da IEEE

Referências Bibliográficas:

- ↑ 1,0 1,1 1,2 PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,00 2,01 2,02 2,03 2,04 2,05 2,06 2,07 2,08 2,09 2,10 2,11 2,12 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335