Preparando para gravar o circuito lógico no FPGA

Ir para navegação

Ir para pesquisar

Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit DE0-Nano.

- Mude a família e dispositivo a ser usado (Assignments > Devices), [Family = Cyclone IV E] e selecione EP4CE22F17C6

- Para ver as pinagens completa das Interfaces de entrada e saída da DE2-115 no Manual.

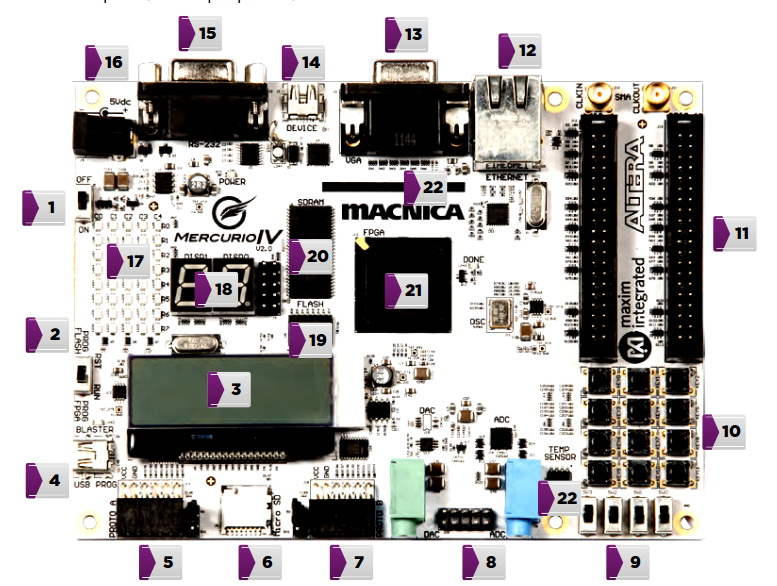

- Pinagem dos dispositivos de entrada e saída do kit MERCURIO IV

- pinagem do kit DE0-Nano

- pinagem do kit DSP

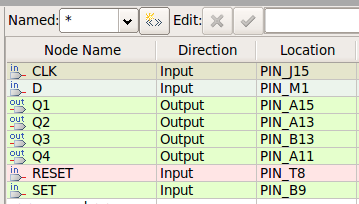

- Atribua os pinos conforme a necessidade do projeto

- Exemplo de atribuição de pinagem

- Defina como alta impedância o estado dos pinos não utilizados no projeto. [Assignments > Devices > Device and Pin Options... > Category:Unused Pins > Reserve all unused pins: [As input tri-stated] > OK].

- Compile o projeto.

Preparando para gravar o circuito lógico no FPGA

Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit MERCURIO IV.

- Mude a família e dispositivo a ser usado (Assignments > Devices), [Family = Cyclone IV E] e selecione EP4CE30F23C7.

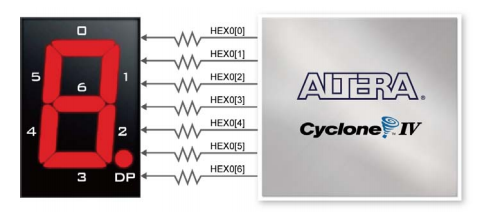

- Utilize o display HEX0 do kit para mostrar a contagem:

- Utilize os leds de LED0 a LED3 (verdes) para mostrar a contagem em binário.

- Utilize a chave KEY0 para gerar o sinal de CLK.

- Atribua os pinos conforme a pinagem do kit MERCURIO IV.

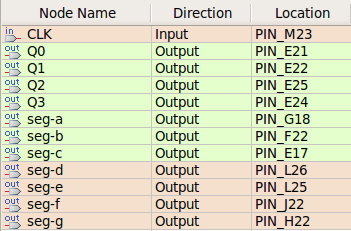

- Ao final da configuração dos pinos, o Pin Planner deverá mostrar a seguinte pinagem:

- Defina como alta impedância o estado dos pinos não utilizados no projeto. (Assignments > Devices), [Device and Pin Options...], escolha a (Category=Unused Pins), e selecione Reserve all unused pins: As input tri-stated. [OK].

- Compile o projeto. Note que agora a numeração dos pinos também aparece no diagrama esquemático.