Mudanças entre as edições de "Preparando para gravar o circuito lógico no FPGA"

| Linha 15: | Linha 15: | ||

| align="center" | [http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=165&No=593&PartNo=1 DE0-Nano] | | align="center" | [http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=165&No=593&PartNo=1 DE0-Nano] | ||

| align="center" | TERASIC | | align="center" | TERASIC | ||

| − | | align="center" | Cyclone® IV - ALTERA | + | | align="center" | Cyclone® IV E - ALTERA |

| align="center" | EP4CE22F17C6 | | align="center" | EP4CE22F17C6 | ||

| align="center" | [[Media:ManualDE0Nano.pdf | User Manual]] | | align="center" | [[Media:ManualDE0Nano.pdf | User Manual]] | ||

| Linha 24: | Linha 24: | ||

| align="center" | [http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&No=502 DE2-115] | | align="center" | [http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&No=502 DE2-115] | ||

| align="center" | TERASIC | | align="center" | TERASIC | ||

| − | | align="center" | Cyclone® IV - ALTERA | + | | align="center" | Cyclone® IV E - ALTERA |

| align="center" | EP4CE115F29C7 | | align="center" | EP4CE115F29C7 | ||

| align="center" | [[Media:ManualDE2-115.pdf | User Manual]] | | align="center" | [[Media:ManualDE2-115.pdf | User Manual]] | ||

| Linha 33: | Linha 33: | ||

| align="center" | [http://www.macnicadhw.com.br/products/mercurion-4-devkit-board;jsessionid=D98DEAF9F3E3E352079DB96CED5C4096 MERCÚRIO IV] | | align="center" | [http://www.macnicadhw.com.br/products/mercurion-4-devkit-board;jsessionid=D98DEAF9F3E3E352079DB96CED5C4096 MERCÚRIO IV] | ||

| align="center" | MACNICA | | align="center" | MACNICA | ||

| − | | align="center" | Cyclone® IV - ALTERA | + | | align="center" | Cyclone® IV E - ALTERA |

| align="center" | EP4CE30F23C7 | | align="center" | EP4CE30F23C7 | ||

| align="center" | [[Media:ManualMercurio.pdf | Manual do Usuário]] | | align="center" | [[Media:ManualMercurio.pdf | Manual do Usuário]] | ||

Edição das 10h33min de 13 de agosto de 2015

Escolha do kit com o FPGA

Para realizar a implementação de um sistema digital em um FPGA, os fabricantes de chips disponibilizam kits de desenvolvimento/educacionais nos quais além do FPGA componentes periféricos diversos estão disponíveis para o desenvolvedor. Entre as características comuns desses kits está a presença de: Leds, Chaves, Displays, Conectores ligados diretamente a um conjunto de pinos do chip FPGA, Conversores A/D e D/A, entre outros. Para conhecer a característica de cada kit, recomenda-se que o desenvolvedor analise o manual do fabricante. Nos laboratórios de Telecomunicações do IFSC estão disponíveis para os professores/alunos alguns kits, cujo uso é destinado prioritariamente para as disciplinas dos Cursos Técnicos e de Engenharia de Telecomunicações. Após selecionar o kit, deverá ser feita a atribuição da pinagem do FPGA conforme as conexões previamente existentes no kit escolhido. A pinagem de cada kit pode ser encontrada nos respectivos manuais. Para facilitar a configuração da pinagem mais utilizada consulte a página correspondente a seguir:

| Kit | Fabricante do Kit | Família FPGA | Device | Documentos disponíveis | Arquivo qsf | Pinagem do kit | Disponíveis no IFSC |

|---|---|---|---|---|---|---|---|

| DE0-Nano | TERASIC | Cyclone® IV E - ALTERA | EP4CE22F17C6 | User Manual | qsf | Pinagem do kit DE0-Nano | 4 |

| DE2-115 | TERASIC | Cyclone® IV E - ALTERA | EP4CE115F29C7 | User Manual | qsf | Interfaces de entrada e saída da DE2-115 | 10 |

| MERCÚRIO IV | MACNICA | Cyclone® IV E - ALTERA | EP4CE30F23C7 | Manual do Usuário | qsf | Pinagem dos dispositivos de entrada e saída do kit MERCURIO IV | 20 |

Configuração da USB para programação do FPGA via JTAG

A configuração da interface USB do computador para a programação do FPGA via JTAG é realizada no computador na qual o kit FPGA será conectado. A maioria dos kits atuais já tem a interface USB-Blaster e o procedimento de configuração é o descrito no procedimento de configuração da USB para programação do FPGA via JTAG.

- OBS: Essa configuração necessita ser feita apenas uma única vez no computador que será usado. É necessário ter acesso de administrado/root para fazer a configuração

Gravação do Projeto no FPGA

Após escolher o kit a ser usado no projeto, é necessário informar ao Quartus II a família e o dispositivo (device) que será utilizado

- para DE0-Nano {Assignments > Device... > Device family (Family: [Cyclone IV E], Name filter: [EP4CE22F17C6] ) > [OK]}

- para DE2-115 {Assignments > Device... > Device family (Family: [Cyclone IV E], Name filter: [EP4CE115F29C7] ) > [OK]}

- para MERCÚRIO IV {Assignments > Device... > Device family (Family: [Cyclone IV E], Name filter: [EP4CE30F23C7] ) > [OK]}

Para evitar que saídas de circuitos da placa sejam ligadas ao terra através do FPGA, defina como alta impedância o estado dos pinos não utilizados no projeto.

- {Assignments > Device... > Device and Pin Options... > Category: Unused Pins > Reserve all unused pins: [As input tri-stated] > [OK] > [OK]}

Atribua os pinos conforme a necessidade do projeto. Existem diferentes maneira de fazer esta atribuição:

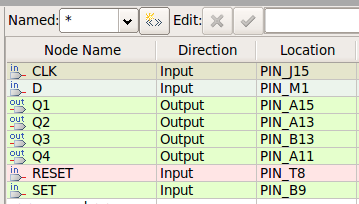

- Uso do Pin Planner {Assignments > Pin Planner} no modo tabela. Digite o número do pino na coluna {Location}. Apenas posições válidas são aceitas.

- Uso do Pin Planner {Assignments > Pin Planner} na interface gráfica. Araste o {Node name} para a posição desejada no leiaute do FPGA.

- Uso do Assignments Editor {Assignments > Assignment Editor}

- Uso do Import Assignments {Assignments > Assignment Editor}. Permite reutilizar pinagens definidas para o mesmo chip com os mesmos nomes em outro projeto. Será necessário ter acesso ao arquivo .qsf desse projeto.

- Para ilustrar o processo, ao final da configuração dos pinos, o Pin Planner {Assignments > Pin Planner} deverá mostrar a correta pinagem conforme exemplificado na figura abaixo:

Uma vez completada a pinagem, compile o projeto para que o Quartus faça o Fitter (Place & Route). Após a compilação a mensagem de warning "Critical Warning (XXXXX): No exact pin location assignment(s) for XX pins of XX total pins" não deverá mais ser mostrada. Caso seja mostrada verifique qual o pino que não foi configurado corretamente e corrija.

Programando o FPGA

Depois de realizar as etapas anteriores:

- Escolhido corretamente o kit.

- Definidos e configurados os pinos do FPGA.

- Pinos não usados estão configurados como tri-state.

- O compilador não apresenta warning sobre "pin location assignment".

A programação do FPGA é feita seguindo o procedimento de programação do FPGA através da USB-Blaster.

Consulte também

Antes de modificar esta pagina

- Faça as contribuições utilizando a página de discussões