Experimento 1 para Circuitos Lógicos: mudanças entre as edições

Ir para navegação

Ir para pesquisar

| Linha 18: | Linha 18: | ||

Após salvar o arquivo como portasAnd.bdf em uma pasta vazia com nome Exp1, e crie um projeto portasAnd.qpf utilizando a família family='''Cyclone ''' com o dispositivo device='''EP1C3T100A8'''. Após isso compile o projeto. | Após salvar o arquivo como portasAnd.bdf em uma pasta vazia com nome Exp1, e crie um projeto portasAnd.qpf utilizando a família family='''Cyclone ''' com o dispositivo device='''EP1C3T100A8'''. Após isso compile o projeto. | ||

= | =Gerar formas de onda para entrada de simulação usando o QSIM - Quartus II= | ||

*Abra o simulador(New > University Program VWF). | *Abra o simulador(New > University Program VWF). | ||

*Defina o tempo de simulação (Edit > Set End Time ...) = 200 ns. | *Defina o tempo de simulação (Edit > Set End Time ...) = 200 ns. | ||

| Linha 26: | Linha 26: | ||

[[Arquivo:Exp1_input.png|1010 px]] | [[Arquivo:Exp1_input.png|1010 px]] | ||

=Obter o diagrama funcional das saídas usando o QSIM - Quartus II= | |||

*Selecione o Quartus II como simulador (Simulation > Options > Quartus II Simulator > OK). | *Selecione o Quartus II como simulador (Simulation > Options > Quartus II Simulator > OK). | ||

*Indique como a simulação será feita (Simulation > Run Functional Simulation). | *Indique como a simulação será feita (Simulation > Run Functional Simulation). | ||

| Linha 32: | Linha 33: | ||

[[Arquivo:Exp1_output.png|1010 px]] | [[Arquivo:Exp1_output.png|1010 px]] | ||

=Obtenção da tabela verdade de circuitos lógicos= | |||

*Realize testes com outras entradas para o preenchimento da Tabela Verdade. | *Realize testes com outras entradas para o preenchimento da Tabela Verdade. | ||

*Salve os resultados obtidos para a confecção do relatório do experimento. | *Salve os resultados obtidos para a confecção do relatório do experimento. | ||

| Linha 72: | Linha 74: | ||

|- | |- | ||

|} | |} | ||

=compreender o funcionamento da porta AND= | |||

*Verificar que as saídas AB, ABC, ABCD se comportam, respectivamente como portas AND de 2, 3 e 4 entradas. | |||

Edição das 13h57min de 3 de junho de 2014

- Objetivos

- Utilizar o diagrama esquemático do Quartus II para inserir um circuito com Portas AND;

- Gerar formas de onda para entrada de simulação usando o QSIM;

- Obter o sinal de saída simulado usando o QSIM - diagrama funcional;

- Compreender o funcionamento da porta AND;

- Entender a tabela verdade de circuitos lógicos;

- Obter as imagens e dados para a confecção de relatório técnico;

- Material necessário

- CI 74X08 AND(disponível na biblioteca da ALTERA)

- Computador com software Quartus II da Altera.

1 Diagrama Esquemático

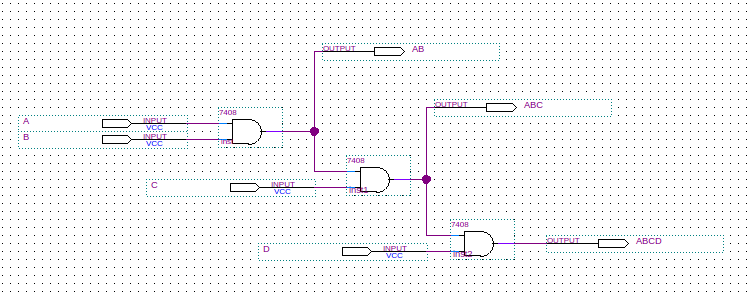

Abra o Quartus II (versão 13.1) e insira o diagrama esquemático com portas AND, conforme a figura abaixo.

Após salvar o arquivo como portasAnd.bdf em uma pasta vazia com nome Exp1, e crie um projeto portasAnd.qpf utilizando a família family=Cyclone com o dispositivo device=EP1C3T100A8. Após isso compile o projeto.

2 Gerar formas de onda para entrada de simulação usando o QSIM - Quartus II

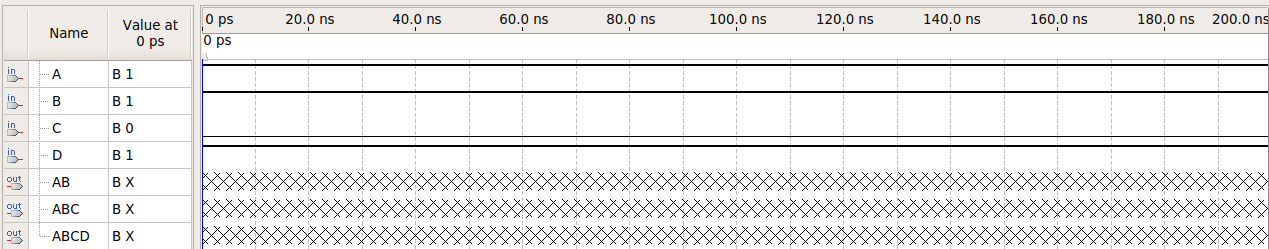

- Abra o simulador(New > University Program VWF).

- Defina o tempo de simulação (Edit > Set End Time ...) = 200 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

- Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome entrada.vwf.

3 Obter o diagrama funcional das saídas usando o QSIM - Quartus II

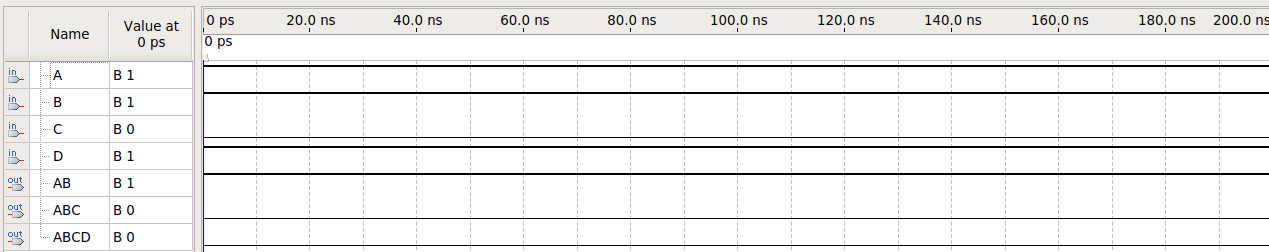

- Selecione o Quartus II como simulador (Simulation > Options > Quartus II Simulator > OK).

- Indique como a simulação será feita (Simulation > Run Functional Simulation).

- Após o término da simulação verifique se o resultado obtido corresponde a respostas do circuito implementado. Salve o sinal de saída como resultadoF.vwf.

4 Obtenção da tabela verdade de circuitos lógicos

- Realize testes com outras entradas para o preenchimento da Tabela Verdade.

- Salve os resultados obtidos para a confecção do relatório do experimento.

| A | B | C | D | L0= AB | L1= ABC | L2= ABCD |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | |||

| 0 | 0 | 0 | 1 | |||

| 0 | 0 | 1 | 0 | |||

| 0 | 0 | 1 | 1 | |||

| 0 | 1 | 0 | 0 | |||

| 0 | 1 | 0 | 1 | |||

| 0 | 1 | 1 | 0 | |||

| 0 | 1 | 1 | 1 | |||

| 1 | 0 | 0 | 0 | |||

| 1 | 0 | 0 | 1 | |||

| 1 | 0 | 1 | 0 | |||

| 1 | 0 | 1 | 1 | |||

| 1 | 1 | 0 | 0 | |||

| 1 | 1 | 0 | 1 | |||

| 1 | 1 | 1 | 0 | |||

| 1 | 1 | 1 | 1 |

5 compreender o funcionamento da porta AND

- Verificar que as saídas AB, ABC, ABCD se comportam, respectivamente como portas AND de 2, 3 e 4 entradas.