Mudanças entre as edições de "Usuário:Kamila.r"

| Linha 56: | Linha 56: | ||

#Porta AND: | #Porta AND: | ||

| − | + | * Utilizar o '''diagrama esquemático''' do Quartus II para inserir um circuito; | |

| − | + | * Gerar formas de onda para entrada de simulação usando o QSIM; | |

| − | + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | |

| − | + | * Compreender o funcionamento da porta AND; | |

| − | + | * Entender a tabela verdade de circuitos lógicos; | |

| − | + | * Obter as imagens e dados para a confecção de relatório técnico; | |

# Portas OR, NOT e NOR | # Portas OR, NOT e NOR | ||

| − | + | * Utilizar o '''diagrama esquemático''' do Quartus II para inserir um circuito; | |

| − | + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | |

| − | + | * Obter o sinal de saída simulado usando o QSIM - '''diagrama temporal''' (uso de cursores para medições); | |

| − | + | * Compreender o funcionamento das porta OR, NOT e NOR; | |

| − | + | * Entender a tabela verdade de circuitos lógicos; | |

# Porta NAND e teorema de De Morgan:: | # Porta NAND e teorema de De Morgan:: | ||

| − | + | * Utilizar o '''diagrama esquemático''' do Quartus II para inserir um circuito; | |

| − | + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | |

| − | + | * Compreender o funcionamento da porta NAND; | |

| − | + | * Utilizar portas NAND para a implementação de portas OR, NOR, NOT e AND | |

| − | + | * Entender a equivalência de circuitos; | |

# Programar o FPGA: | # Programar o FPGA: | ||

| − | + | * Utilizar o '''diagrama esquemático''' do Quartus II para inserir um circuito; | |

| − | + | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | |

| − | + | * Compreender o funcionamento das portas XOR e XNOR; | |

| − | + | * Definir a pinagem de saída | |

| − | + | * Programar o FPGA para implementar um comparador de palavras (ou gerador de paridade); | |

| − | + | * Entender o preenchimento da tabela verdade seguindo o resultado apresentado pelo circuito; | |

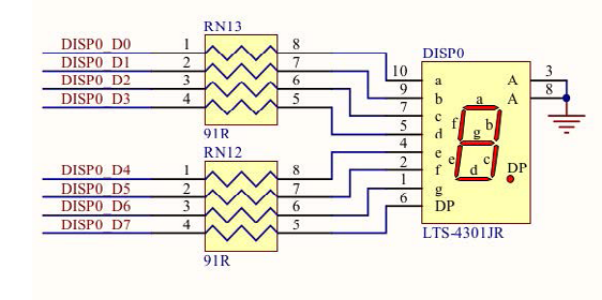

# Sistema de numeração binário: | # Sistema de numeração binário: | ||

| − | + | * Compreender o funcionamento do display de sete segmentos; | |

| − | + | * Compreender o funcionamento do codificador binário para sete segmentos; | |

| − | + | * Programar o FPGA; | |

# Decodificador de 3 para 8, 1 para 2, 2 para 3 (binario para one-hot): | # Decodificador de 3 para 8, 1 para 2, 2 para 3 (binario para one-hot): | ||

| Linha 99: | Linha 99: | ||

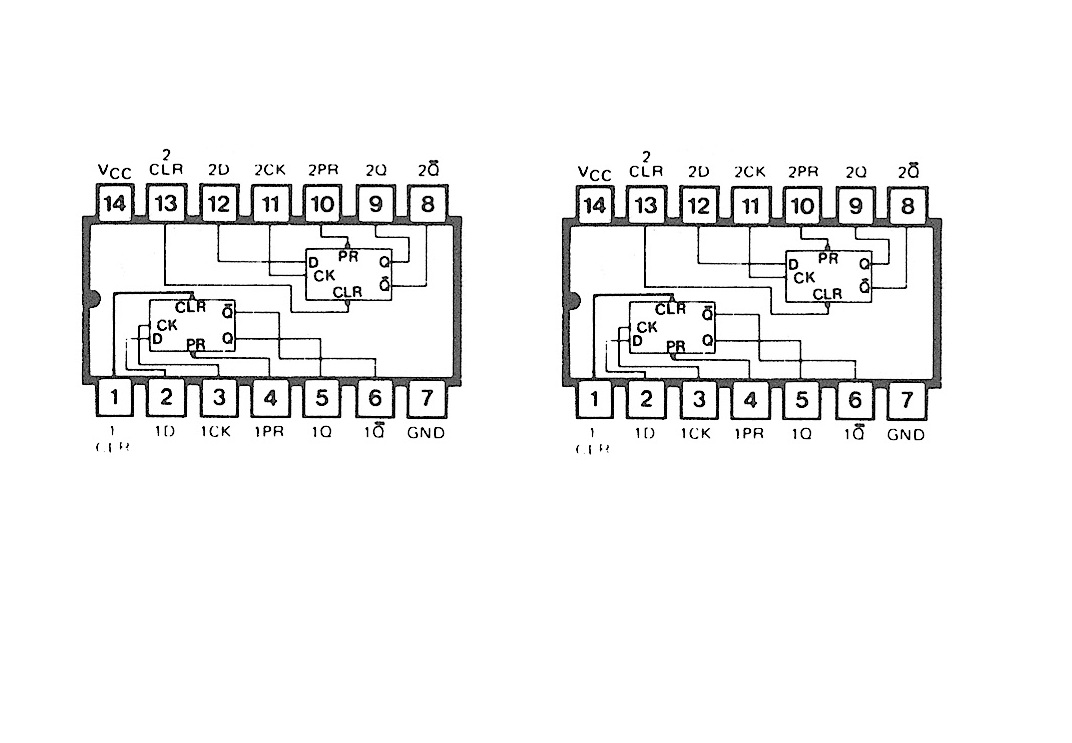

# Tipos de Flip-Flops e Latch: | # Tipos de Flip-Flops e Latch: | ||

| − | + | * Compreender o funcionamento de Flip-Flops D, RS, JK e Latch RS e D | |

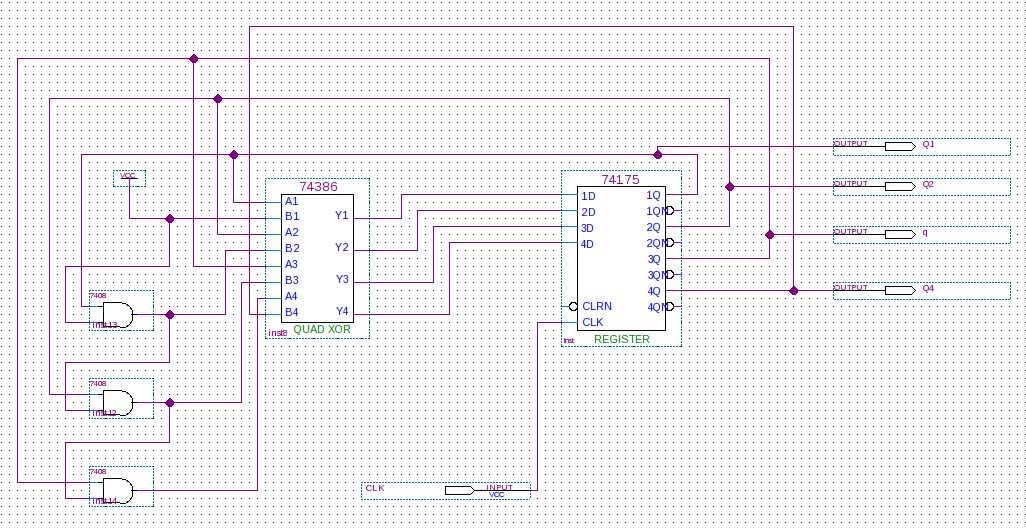

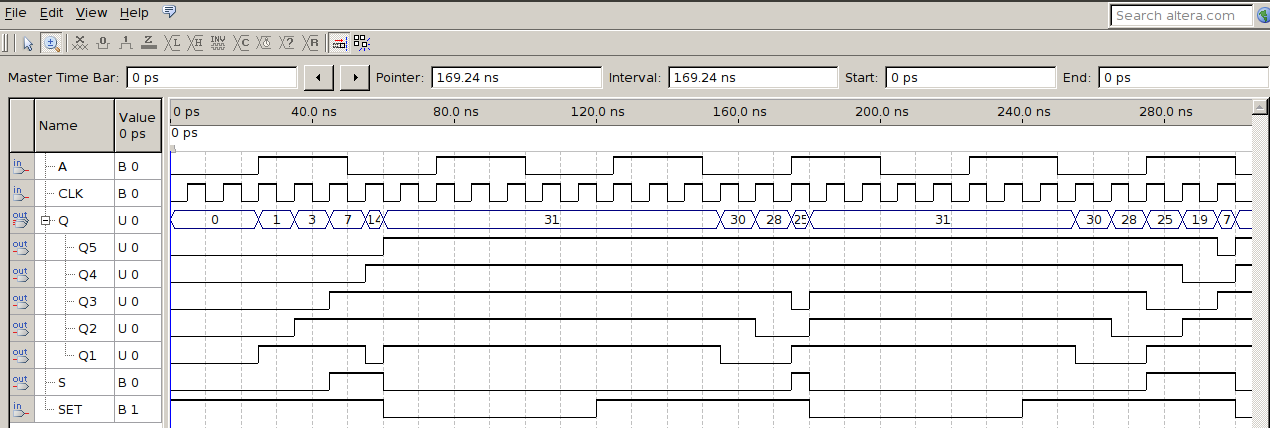

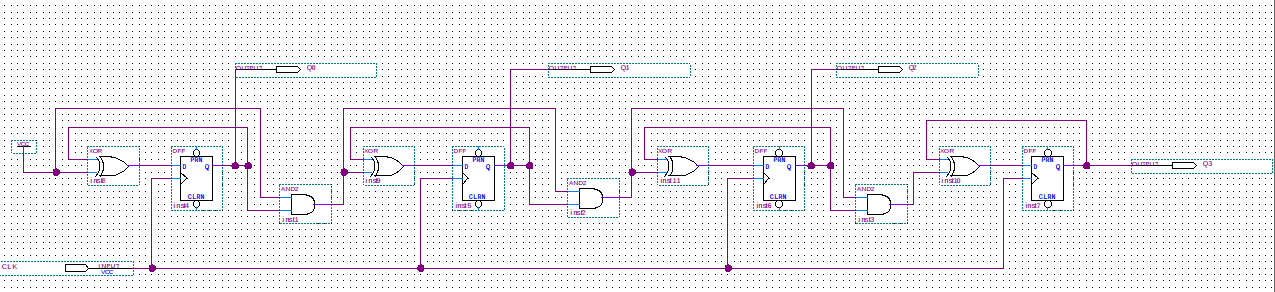

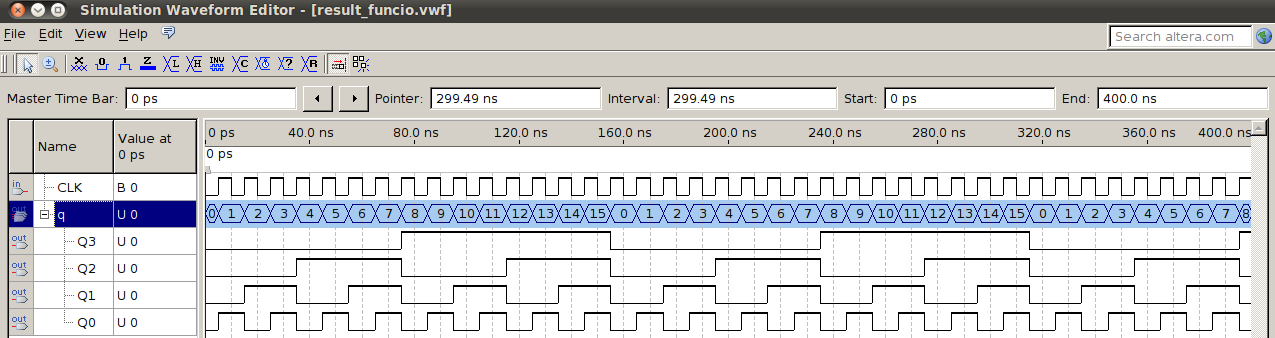

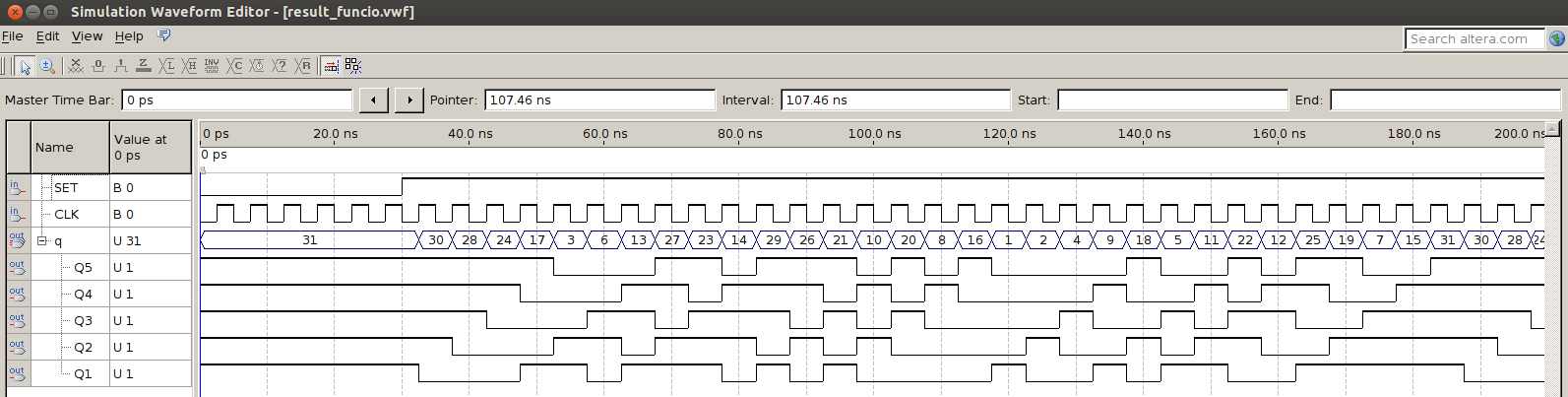

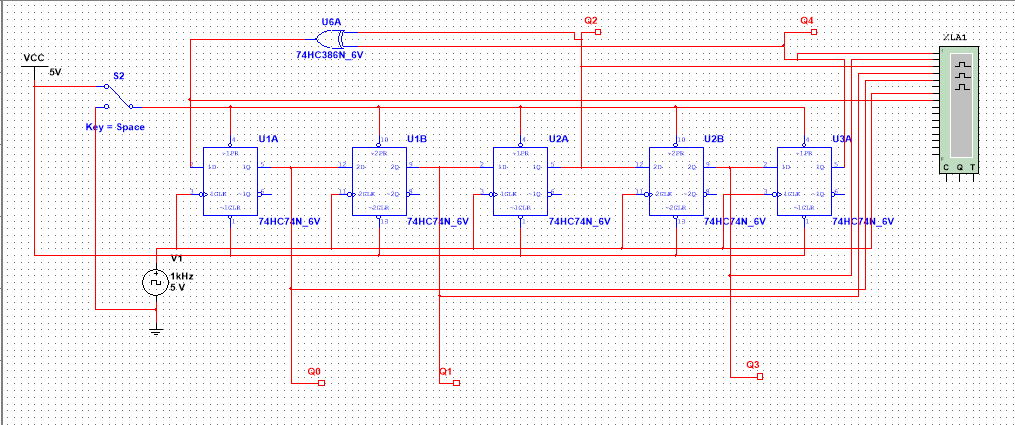

# Contador UP/DOWN: | # Contador UP/DOWN: | ||

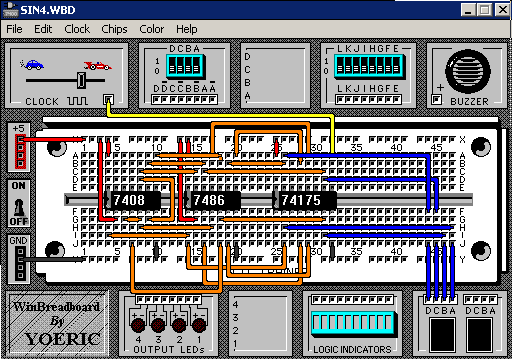

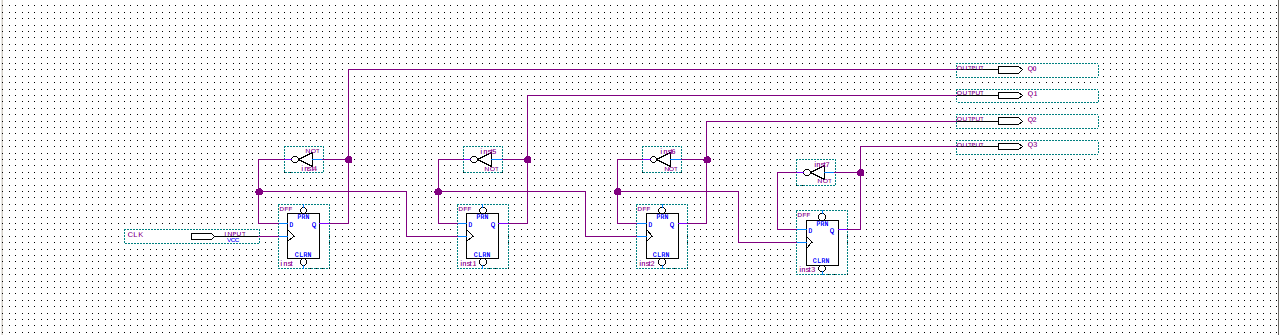

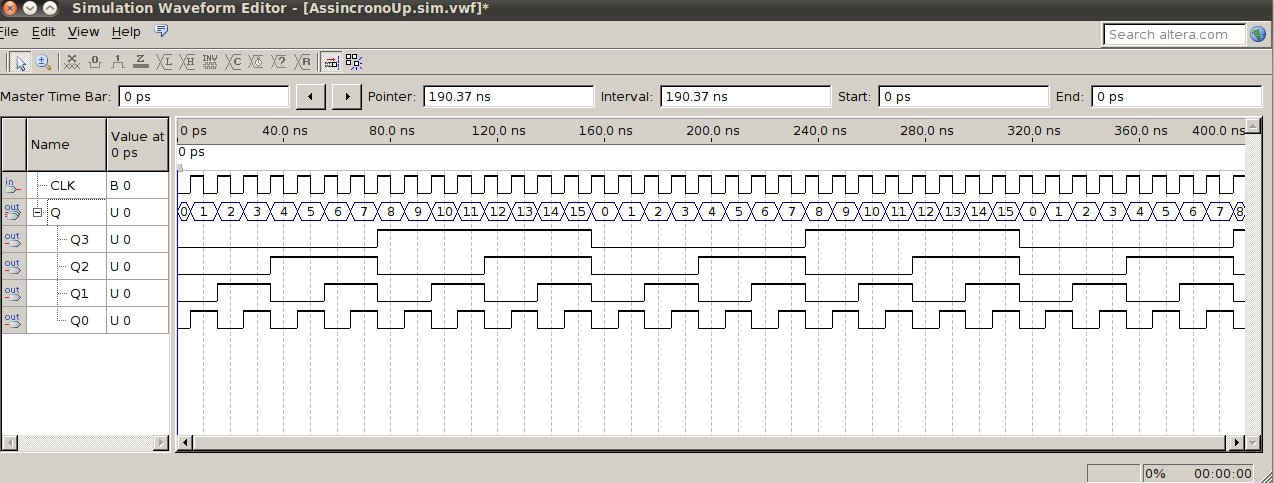

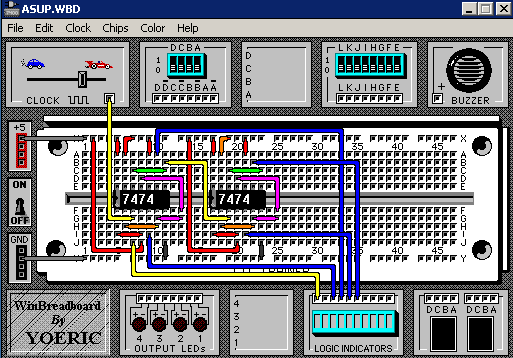

| − | + | * Inserir diagrama esquemático de um circuito lógico com o Quartus II (circuito discreto); | |

| − | + | * Fazer a simulação funcional de um circuito com o QSIM; | |

| − | + | * Gerar formas de onda para entrada de simulação; | |

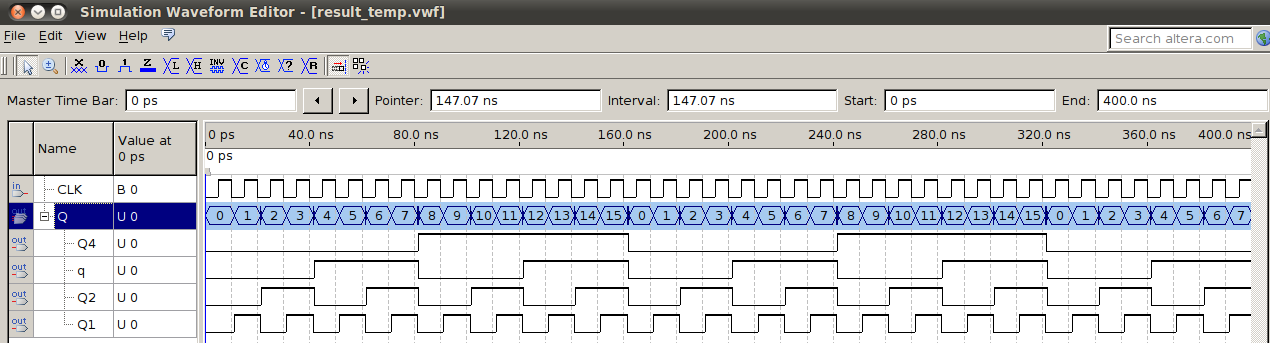

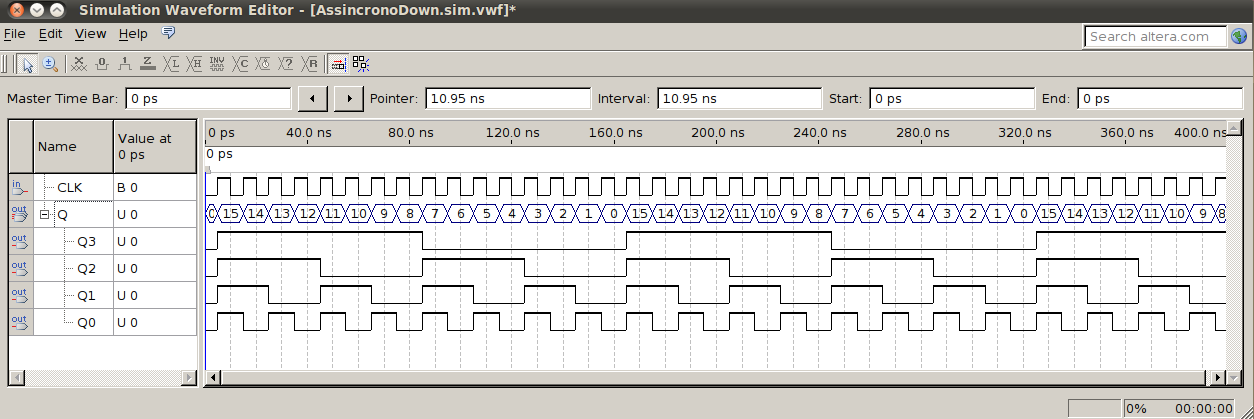

| − | + | * Fazer a simulação temporal do circuito com o QSIM; | |

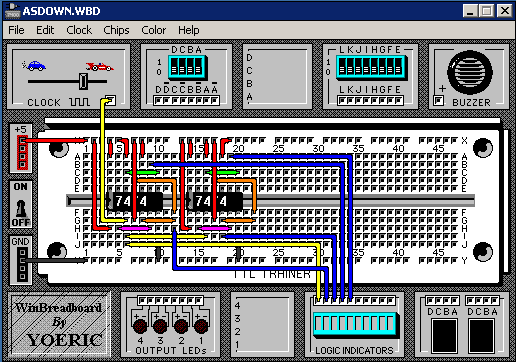

| − | + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; | |

| − | + | * Verificar os resultados obtidos; | |

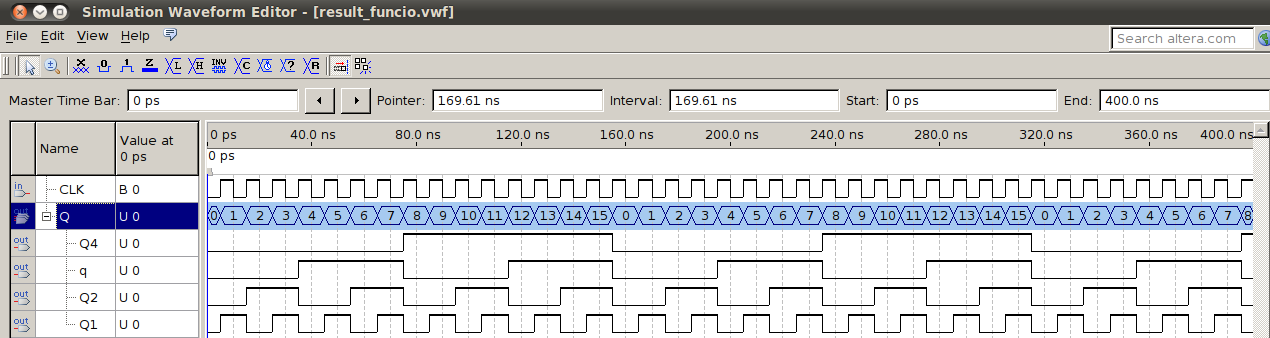

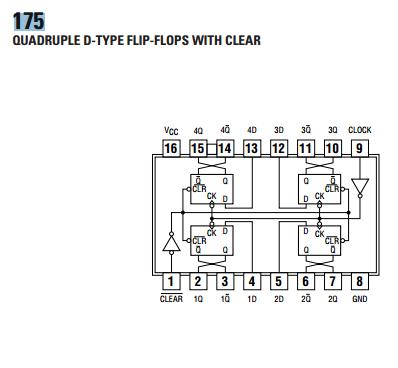

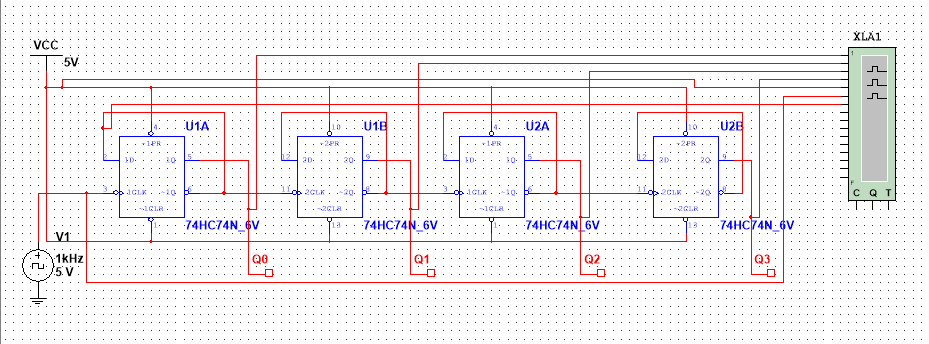

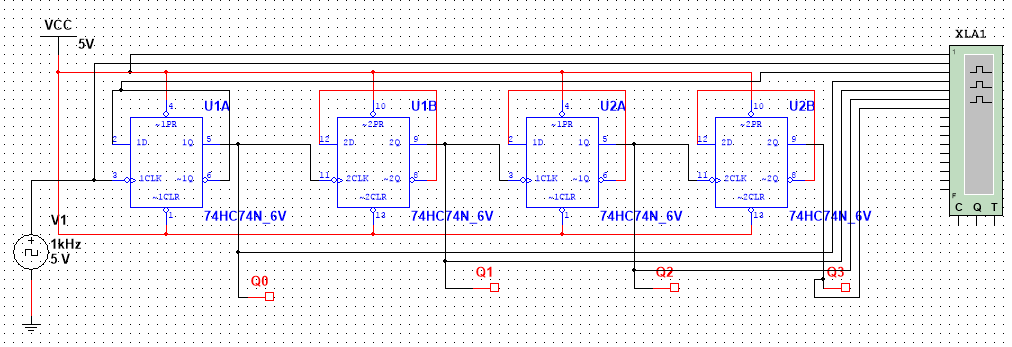

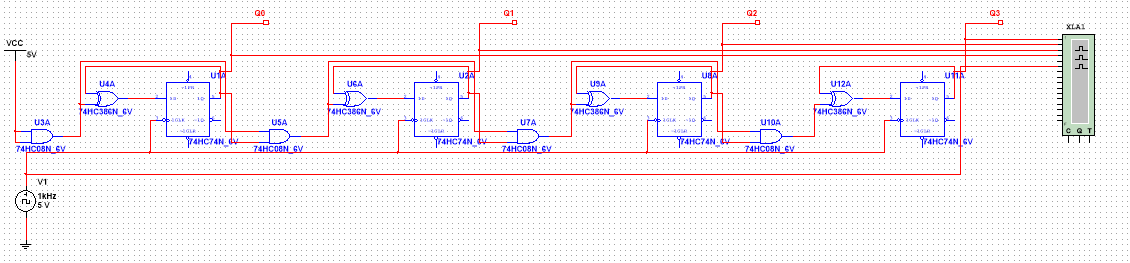

# Contadores comerciais: (74XX) | # Contadores comerciais: (74XX) | ||

| − | + | * Inserir diagrama esquemático de um circuito lógico com o Quartus II; | |

| − | + | * Fazer a simulação funcional de um circuito com o QSIM; | |

| − | + | * Gerar formas de onda para entrada de simulação; | |

| − | + | * Fazer a simulação temporal do circuito com o QSIM; | |

| − | + | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; | |

| − | + | * Verificar os resultados obtidos; | |

# Registrador de descolamento: | # Registrador de descolamento: | ||

Edição das 10h23min de 8 de maio de 2014

Para publicação: Modernização das aulas de Laboratório de Circuitos Lógicos

Semanário do Bolsista 2014: Implementação

- Horários

- (4h) SEG 15:30 às 19:30

- (4h) TER 7:30 às 9:40 - 17:30 às 19:20

- (4h) QUA 7:30 às 9:40 - 17:30 às 19:20

- (4h) QUI 9:30 às 11:40 - 17:30 às 19:20

- (4h) SEX 7:30 às 9:40 - 17:30 às 19:20

- Semana 01

- 01-04 Abril:

- Definição dos passos iniciais do trabalho

- Leitura dos Manuais do Protolab

- Sondagem junto aos professores sobre o tipo de experimentos utilizados em Eletrônica Digital

- Formatação da máquina linux e transferência dos arquivos Kamila e Lacip

- Estudo dos manuais com experimentos

- Download do software QuartusII V13

- Definição de proposta: fazer um formulário para os professores da área de circuitos lógicos indicando os circuitos disponíveis no Manual 8810 para que eles possam selecionar por grau de importância e/ou necessidade quais os mais utilizados e que deveriam ser propostos também no Quartus

- Semana 02

- 07-11 Abril:

- Solicitado ao suporte a instalação da nova versão do Quartus

- Elaboração do questionário dos professores

- Em conversa com a professora Elen e o professor Eduardo, ambos recomendaram que os roteiros a serem desenvolvidos deveriam partir dos circuitos mais simples, com algumas portas lógicas, para melhor entendimento do funcionamento delas e uma interação inicial mais simples com o software

- Semana 03

- 14-17 Abril:

- Término do formulário dos professores

- Estudo das biografias do TOKHEIM

- Software Quartus V13 foi instalado

- Testes com a nova versão

- Desenvolvimento de uma relação de experimentos para propor aos professores da área de CIL

- Semana 04

- 22-30 Abril:

- Fomulário Professores fase: Implementação

- Seleção e estudos dos experimentos:

- Gate AND Exp 2(Com testes de atraso de propagação) - Módulo 8810

- Gate OR Exp 5(Com testes de atraso de propagação) - Módulo 8810

- Gate NOT Exp 6 - Módulo 8810

- Gate NAND Exp 9 - Módulo 8810

- Gate NOR Exp 16 - Módulo 8810

- Gate NXOR Exp 20 - Módulo 8810

- De Morgan Exp 24 - Módulo 8810

- R-S Flip-Flops - TOKEIM

- D Flip-Flops - TOKEIM

- J-K Flip-Flops - TOKEIM

- LATCH D Flip-Flops - TOKEIM

- Contador UP - TOKEIM

- Contador DOWN - TOKEIM

- Registrador de descolamento - TOKEIM

- Decodificadores Exp 3- Módulo 8810

- Codificadores Exp 6 - Módulo 8810

- Multiplexadores Exp 2 - Módulo 8810

- Demultiplexadores Exp 2 - Módulo 8810

- Comparadores Digitais TODAS - Módulo 8810

- (...)

- Semana 05

- 05-09 Maio:

- Definir os objetivos de cada experimento mencionado na lista:

- Porta AND:

- Utilizar o diagrama esquemático do Quartus II para inserir um circuito;

- Gerar formas de onda para entrada de simulação usando o QSIM;

- Obter o sinal de saída simulado usando o QSIM - diagrama funcional;

- Compreender o funcionamento da porta AND;

- Entender a tabela verdade de circuitos lógicos;

- Obter as imagens e dados para a confecção de relatório técnico;

- Portas OR, NOT e NOR

- Utilizar o diagrama esquemático do Quartus II para inserir um circuito;

- Obter o sinal de saída simulado usando o QSIM - diagrama funcional;

- Obter o sinal de saída simulado usando o QSIM - diagrama temporal (uso de cursores para medições);

- Compreender o funcionamento das porta OR, NOT e NOR;

- Entender a tabela verdade de circuitos lógicos;

- Porta NAND e teorema de De Morgan::

- Utilizar o diagrama esquemático do Quartus II para inserir um circuito;

- Obter o sinal de saída simulado usando o QSIM - diagrama funcional;

- Compreender o funcionamento da porta NAND;

- Utilizar portas NAND para a implementação de portas OR, NOR, NOT e AND

- Entender a equivalência de circuitos;

- Programar o FPGA:

- Utilizar o diagrama esquemático do Quartus II para inserir um circuito;

- Obter o sinal de saída simulado usando o QSIM - diagrama funcional;

- Compreender o funcionamento das portas XOR e XNOR;

- Definir a pinagem de saída

- Programar o FPGA para implementar um comparador de palavras (ou gerador de paridade);

- Entender o preenchimento da tabela verdade seguindo o resultado apresentado pelo circuito;

- Sistema de numeração binário:

- Compreender o funcionamento do display de sete segmentos;

- Compreender o funcionamento do codificador binário para sete segmentos;

- Programar o FPGA;

- Decodificador de 3 para 8, 1 para 2, 2 para 3 (binario para one-hot):

- Multiplexadores:

- Demultiplexadores:

- Tipos de Flip-Flops e Latch:

- Compreender o funcionamento de Flip-Flops D, RS, JK e Latch RS e D

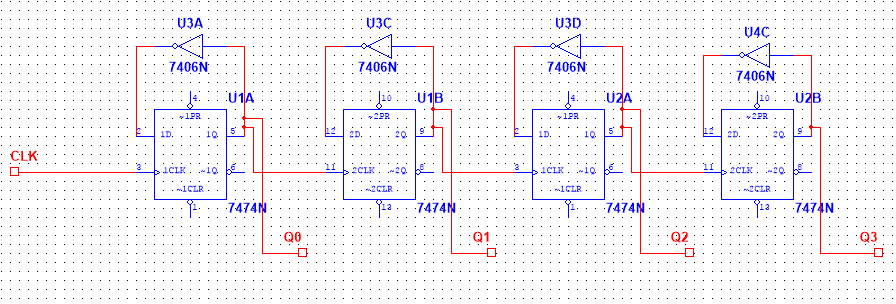

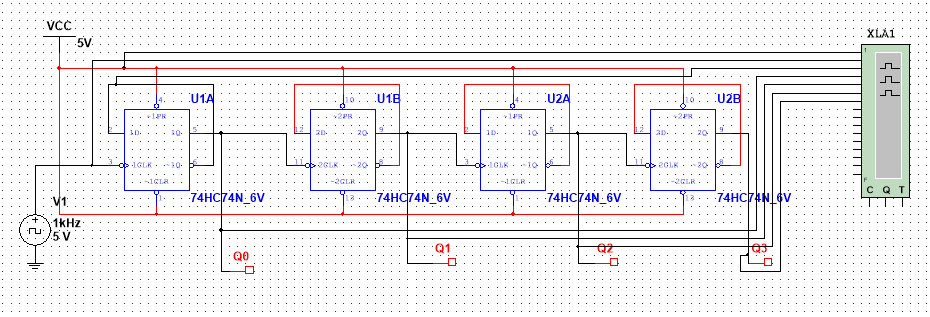

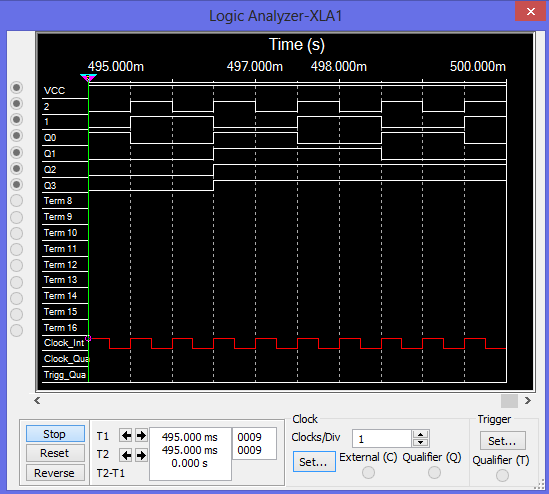

- Contador UP/DOWN:

- Inserir diagrama esquemático de um circuito lógico com o Quartus II (circuito discreto);

- Fazer a simulação funcional de um circuito com o QSIM;

- Gerar formas de onda para entrada de simulação;

- Fazer a simulação temporal do circuito com o QSIM;

- Preparar o circuito lógico para gravação em um kit de desenvolvimento;

- Verificar os resultados obtidos;

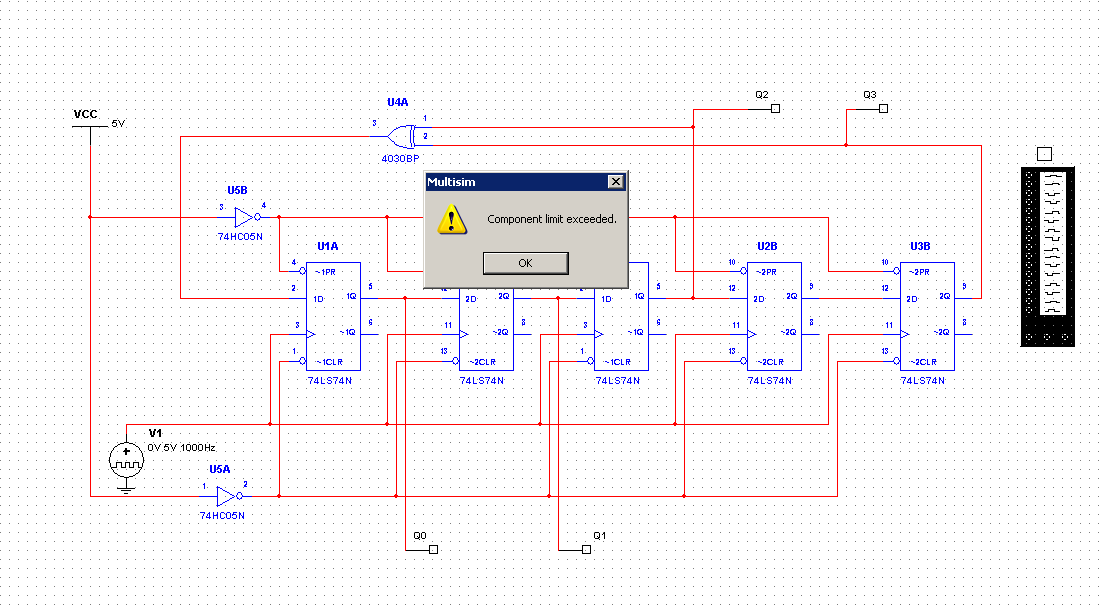

- Contadores comerciais: (74XX)

- Inserir diagrama esquemático de um circuito lógico com o Quartus II;

- Fazer a simulação funcional de um circuito com o QSIM;

- Gerar formas de onda para entrada de simulação;

- Fazer a simulação temporal do circuito com o QSIM;

- Preparar o circuito lógico para gravação em um kit de desenvolvimento;

- Verificar os resultados obtidos;

- Registrador de descolamento:

- Comparadores Digitais:

- Somador/Subtrator/Complemento de 2; (4 e 8 bits)

- Projeto de circuito para detectar Overflow;

- Multiplicador

| 2013: Pesquisa |

|---|

Diário do Bolsista 2013: Pesquisa

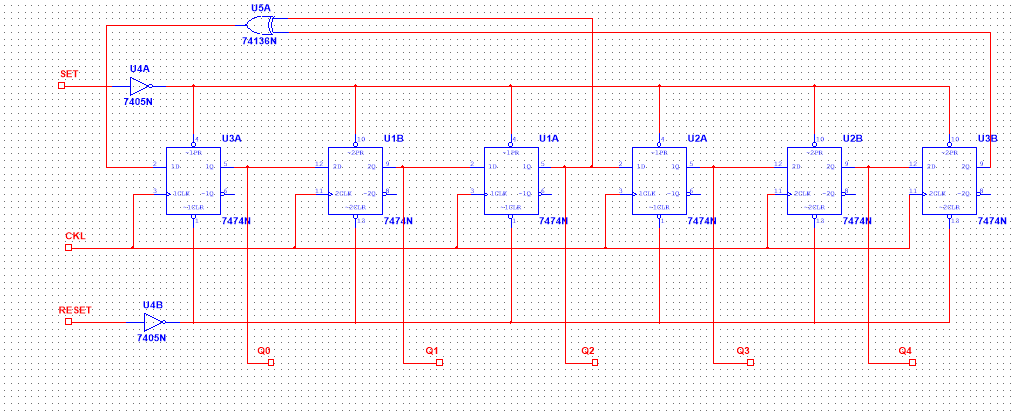

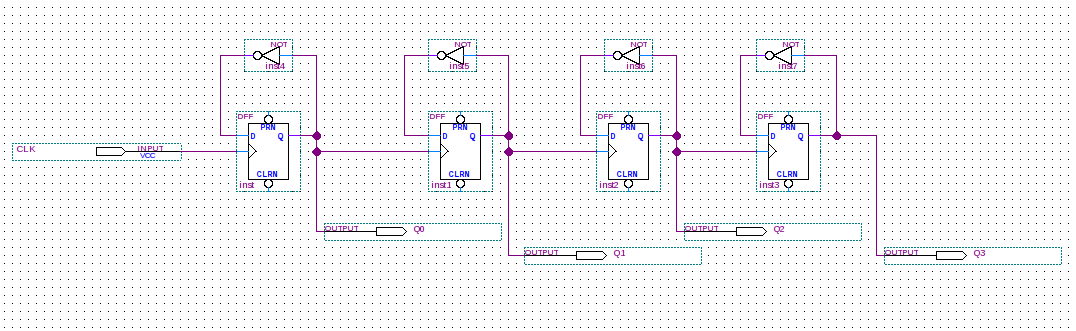

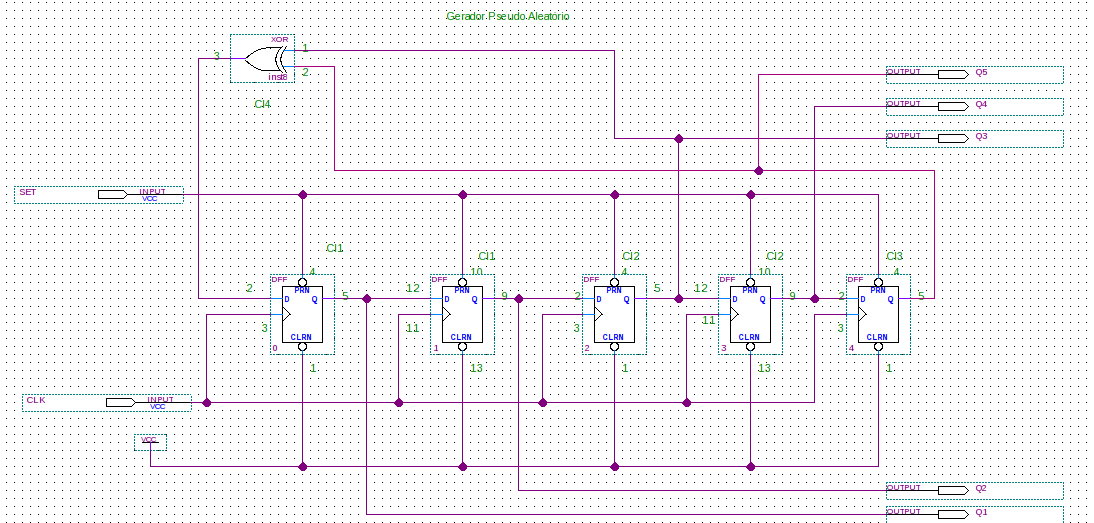

Obs.:O clock é ligado a saída (Q'), apresentei essa solução já que não encontrei uma porta(dff, etc) que houvesse duas saídas Q e Q'

Apostila de Eletrônica Digital Marcos Moecke

|

| Roteiros |

|---|

| Métodos de pesquisa e aplicação |

|---|

|

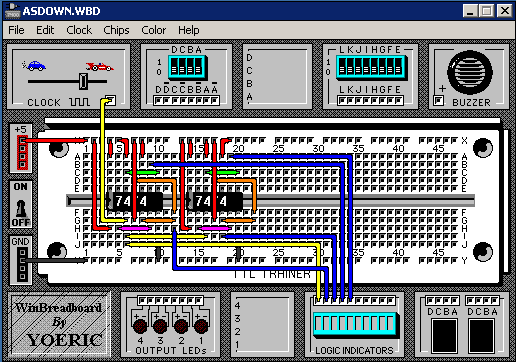

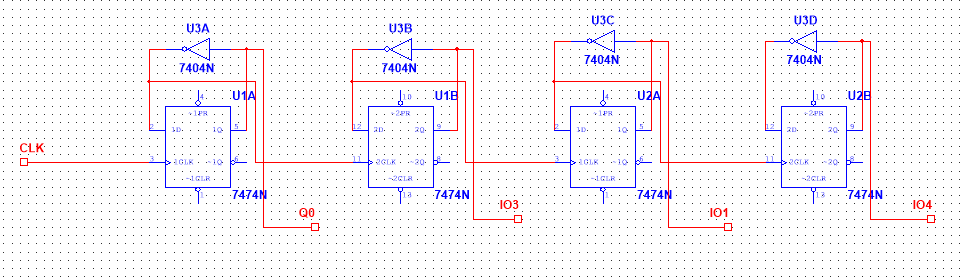

Contador Assíncrono Crescente:

Contador Assíncrono Decrescente:

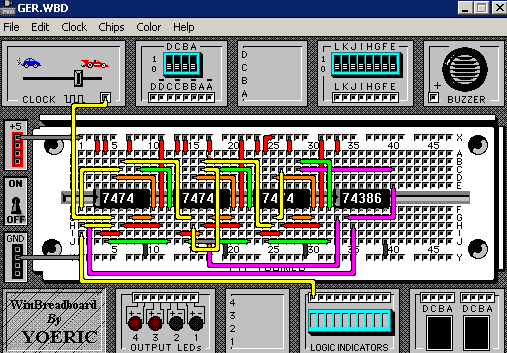

Contador assíncrono decrescente Contador Síncrono:

Gerador de Sequência Pseudoaleatória:

XXXX |