Mudanças entre as edições de "Usuário:Kamila.r"

Ir para navegação

Ir para pesquisar

| Linha 45: | Linha 45: | ||

;16maio2013; | ;16maio2013; | ||

*Implementar o contador Síncrono (0-15), Assíncrono crescente (0-15) e decrescente(15-0), Gerador de sequencia pseudoaleatória (5 bits). Simular no QSIM, funcional e temporal. Perceber as diferenças. | *Implementar o contador Síncrono (0-15), Assíncrono crescente (0-15) e decrescente(15-0), Gerador de sequencia pseudoaleatória (5 bits). Simular no QSIM, funcional e temporal. Perceber as diferenças. | ||

| + | |||

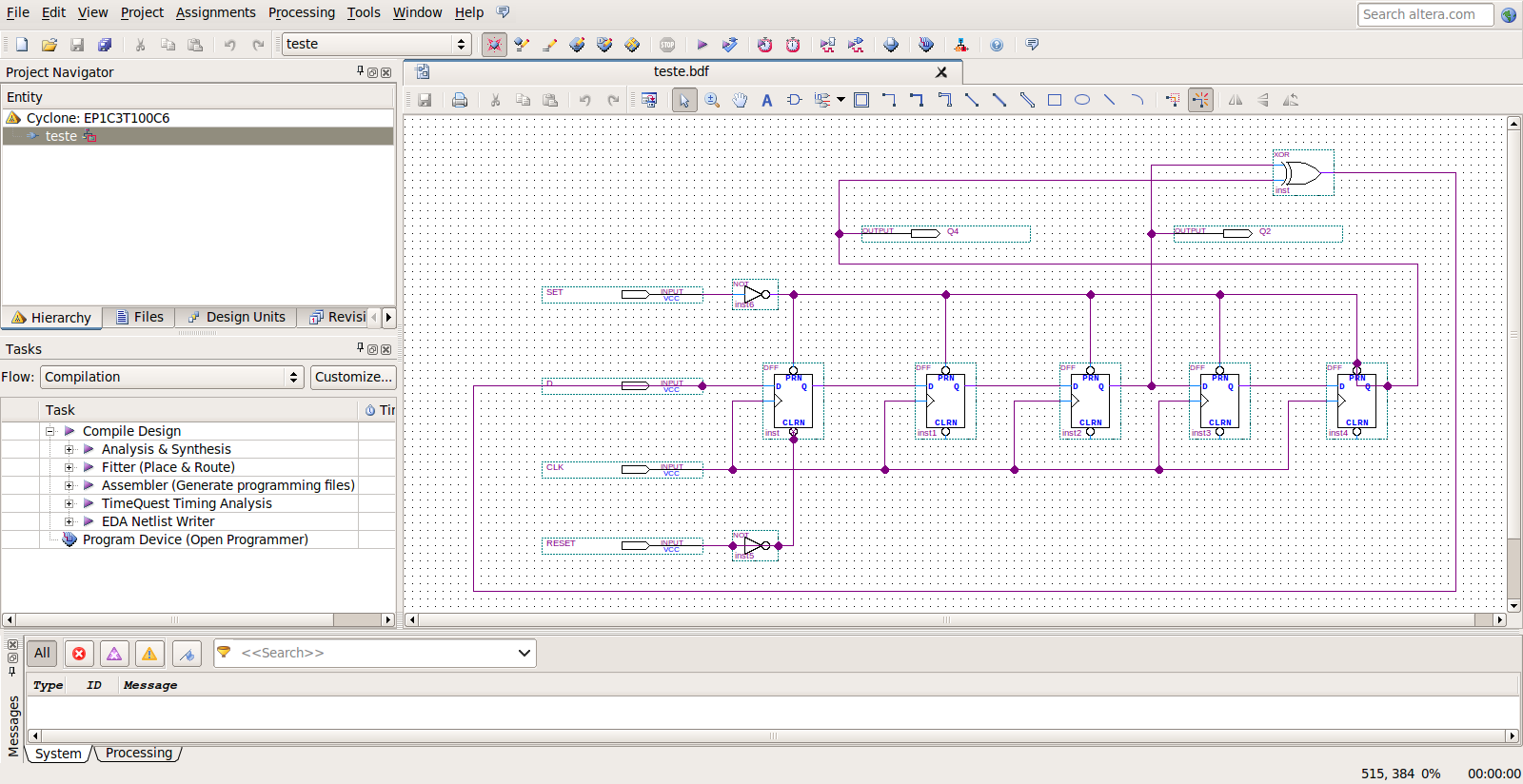

| + | *Primeiro teste: Registrador de sequência pseudoaleatória | ||

| + | |||

| + | [[Imagem:kamila1.png|900px]] | ||

| + | |||

*Registrar o tempo que demora para fazer a montagem. Testes funcionais e temporais. | *Registrar o tempo que demora para fazer a montagem. Testes funcionais e temporais. | ||

Edição das 09h57min de 17 de maio de 2013

Use no projeto está pagina para as edições enquanto não devem ser visiveis para o público.

Bolsistas:Modernização das aulas de Laboratório de Circuitos Lógicos

Para publicar utilizaremos a página Modernização das aulas de Laboratório de Circuitos Lógicos

Diário do Bolsista

- 02mai2013

- Ler a tela de ajuda da wiki. Praticar pequenas edições na wiki nesta Área de rascunho.

- 07mai2013;

- Discussão sobre as etapas do projeto. Planejamento. Esclarecimento de dúvidas.

- Assistir as aulas de CIL29003 (para rever a disciplina sob outro enfoque).

- Agendada um reunião semanal nas terças-feiras 9h40-11h30.

- Definido o local de trabalho.

- Ler PEDRONI, Volnei A. Eletrônica Digital Moderna e VHDL: Princípios Digitais, Eletrônica Digital, Projeto Digital, Microeletrônica e VHDL. 1 ed. [S.l.]:Elsevier, 2010. 648 p. ISBN 978-8535234657. (Cap 18)

- 08maio2013;

- Iniciando os estudos sobre Dispositivos Lógicos Programáveis (PEDRONI, Volnei A.) cáp 18.

- Ler página CIL-EngTel (página).

- 09maio2013;

- Término da leitura do capítulo referente a Dispositivos Lógicos Programáveis.

- Início da pesquisa na internet sobre FPGAs e CPLDs (estrutura e funcionamento).

- Aula de CIL, no laboratório.

- 10maio2013;

- Início da pesquisa sobre as melhores faculdades de tecnologia do mundo (com foco em eletrônica), projetos e afins.

- Vídeos sobre programação, teste e aplicação produtos ALTERA (YouTube).

- 13maio2013;

- Leitura de tópicos importantes do capítulo 13 da seguinte bibliografia: TOCCI, Ronald J.; WIDMER, Neal S.; MOSS, Gregory L. Sistemas digitais: Princípios e Aplicações. 10 ed. [S.l.]:Pearson Prentic Hall, 2007.

- Obs.: Resumo no final do capítulo é claro e objetivo, para futuras dúvidas sobre a arquitetura dos DLPs, consultá-lo.

- 14maio2013;

- Ver as opções existentes no projeto FPGA para todos, modulos periféricos

- Ver o funcionamento de um display de sete segmentos. (ver Pedroni p.235 a diferença entre Catodo comum e Anodo comum).

- Contactar o aluno Ernani da 3ª fase da engtelecom (também com o aluno Gustavo/Profa Deise). Quais módulos estão disponíveis.

- 15maio2013;

- Aula de CIL.

- Exercício de aula: fazer um gerador de sequência pseudoaleatória com 5 FF.

- 16maio2013;

- Implementar o contador Síncrono (0-15), Assíncrono crescente (0-15) e decrescente(15-0), Gerador de sequencia pseudoaleatória (5 bits). Simular no QSIM, funcional e temporal. Perceber as diferenças.

- Primeiro teste: Registrador de sequência pseudoaleatória

- Registrar o tempo que demora para fazer a montagem. Testes funcionais e temporais.

- 17maio2013;

- Verificar a diferença em relação ao uso do protoboard virtual (JBB) e real. Documentar usando o simulador de protoboard.

- Registrar o tempo que demora para fazer a montagem. Testes funcionais e temporais.

- Registrar o processo de escolha dos componentes, aquisição (almoxtele), montagem, equipamentos necesários e TODOS componentes (protoboard, fio, alicate, fonte, etc.)

- XXjun

- Selecionar 2 alunos voluntários da engtelecom, 2 CST, 2 técnico integrado e pedir que eles façam os procedimentos. -> Questionário dificuldades e vantagens.