Mudanças entre as edições de "DLP1-EngTel (página)"

| Linha 9: | Linha 9: | ||

;Aula 1 (23 Mar): | ;Aula 1 (23 Mar): | ||

*[[DLP1-EngTel (Plano de Ensino) | Apresentação da disciplina]] | *[[DLP1-EngTel (Plano de Ensino) | Apresentação da disciplina]] | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

*Introdução aos dispositivos lógicos programáveis: | *Introdução aos dispositivos lógicos programáveis: | ||

Edição das 00h24min de 11 de agosto de 2016

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

- Link curto http://bit.ly/IFSC-DLP29006

- Carga horária, Ementas, Bibliografia, Professores

- Cronograma de atividades

- Plano de Ensino

Registro on-line das aulas

Unidade 1

- Aula 1 (23 Mar)

- Introdução aos dispositivos lógicos programáveis:

- Conceito, tipos de PLDs

- SPLD: PAL, PLA e GAL

- CPLDs

- Aula 2 (28 Mar)

- Introdução aos dispositivos lógicos programáveis:

- Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, RAM, DSP, Clock, PLL, I/O

- Fabricantes de DLPs

- Vizualização no Chip Planner de um projeto. (importante todos alunos terem acesso a IFSC-CLOUD

- Ver pag. 418 a 429 de [1]

Unidade 2

- Aula 3 e 4 (30-31 Mar) - Introdução ao VHDL e ambienta EDA - QUARTUS

- Exemplo de programação de um full adder.

- Utilize os arquivos full_adder.qar

- Estrutura do código VHDL

- Libraries, Entity, Architecture

- Exemplo 2.2 (VHDL) - programação de um flip-flop

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

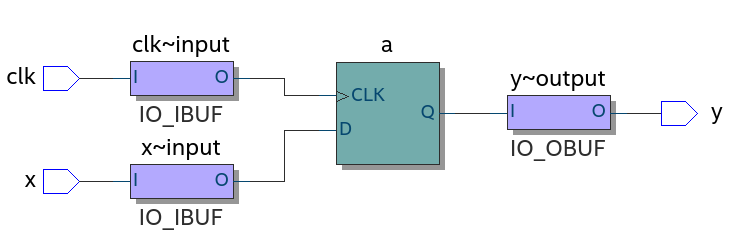

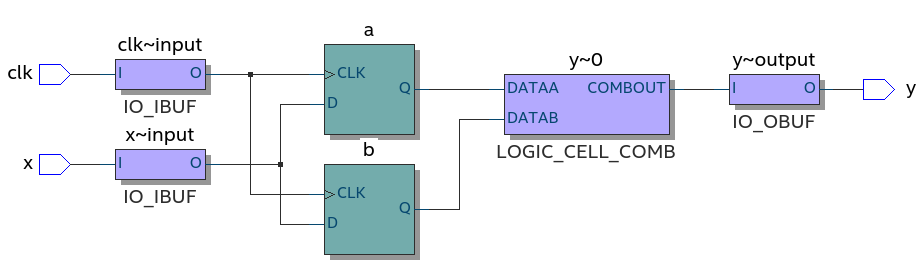

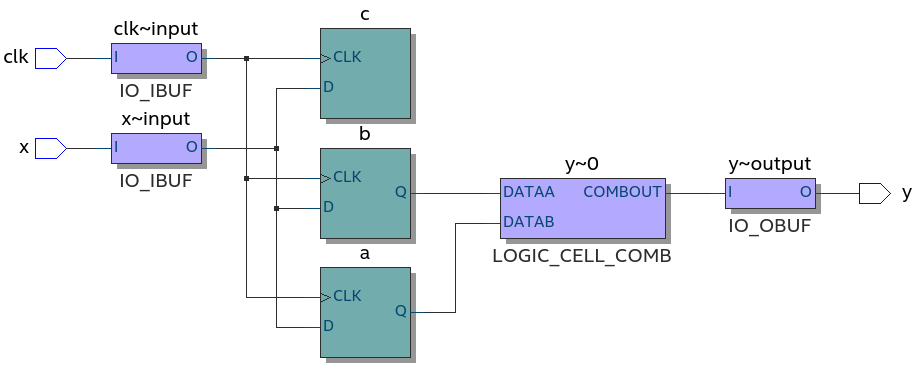

- Após a criação do projeto em VHDL utilizando a descrição de hardware acima, compile o código VHDL.

- Use o RTL Viewer para ver a descrição RTL do circuito.

- Use o Technology Map Viewer para ver a como o circuito foi mapeado para os elementos lógicos disponíveis no dispositivo FPGA selecionado (EP1C3T100A8)

- Abra o Chip Planner e observe no Node Properties como esse circuito é conectado dentro do dispositivo FPGA selecionado

- Exemplo 2.3 (VHDL e QSIM) - programação de um circuito somador com registrador

- Realizar as simulações funcional e temporal do circuito

- Observar o "Technology Map" e o "RTL" do circuito

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END;

ARCHITECTURE circuit OF registered_comp_add IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END;

- Acrescente saídas para o sinal sum e para o sinal comp, de modo a poder observar estes sinais no simulador QSIM e realize novas simulações funcional e temporal.

- Para conhecer melhor o ambiente do simulador QSIM veja Arquivo:Quartus II Simulation.pdf da ALTERA.

- Ver pag. 3 a 24 de [2]

- Aula 5 (4 Abr)

- Introdução ao VHDL.

- Exemplo de decodificador de endereço genérico

ENTITY address_decoder IS

GENERIC (N: NATURAL := 2);

PORT (

address: IN NATURAL RANGE 0 TO 2**N-1;

ena: BIT;

word_line: OUT BIT_VECTOR(2**N-1 DOWNTO 0));

END ENTITY;

ARCHITECTURE ad_arch1 OF address_decoder IS

BEGIN

gen: FOR i IN address'RANGE GENERATE

word_line(i) <= '1' WHEN ena='0' ELSE

'0' WHEN i=address ELSE

'1';

END GENERATE;

END ARCHITECTURE;

ARCHITECTURE ad_arch2 OF address_decoder IS

signal word_tmp: BIT_VECTOR(2**N-1 DOWNTO 0);

BEGIN

word_line <= (others => '1') WHEN ena='0' ELSE word_tmp;

gen: FOR i IN address'RANGE GENERATE

word_tmp(i) <= '0' WHEN i=address ELSE '1';

END GENERATE;

END ARCHITECTURE;

CONFIGURATION ad_conf OF address_decoder is

FOR ad_arch1 END FOR;

END CONFIGURATION;

- Utilize Family = Cyclone e Device = EP1C4F400C6

- Observe que o uso de um valor GENERIC permite criar diferentes tamanhos de hardware de forma muito simples.

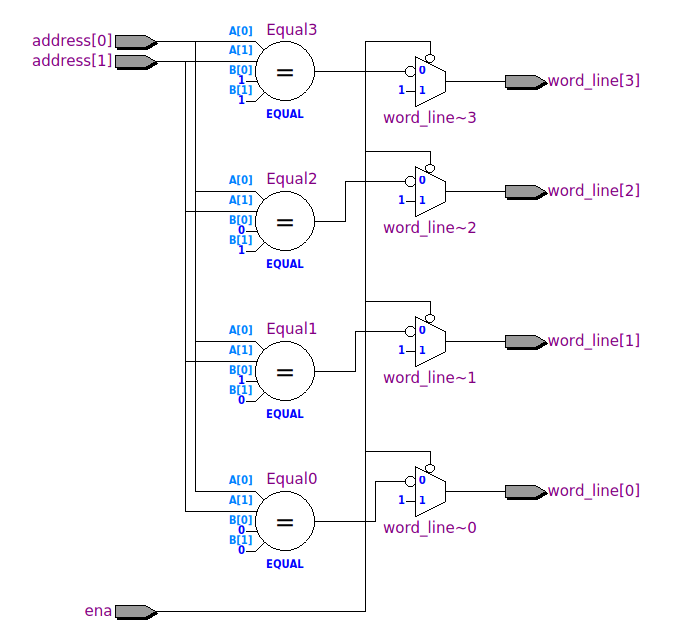

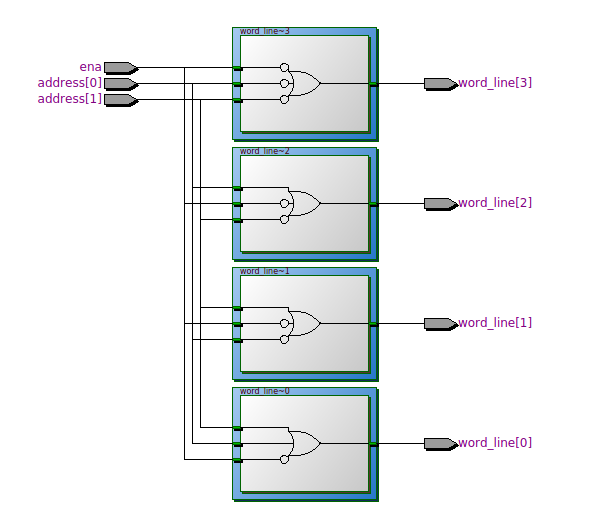

- Usando N = 2, verifique o RTL e o TECHNOLOGY MAP obtido para as duas ARCHITECTURES {ad_arch1, ad_arch2}. A função do CONFIGURATION é definir qual das ARCHITECTURE será associada a ENTITY.

- Comente a linha (word_line <= (others => '1') WHEN ena='0' ELSE word_tmp;) e veja o RTL obtido.

- Verifique o RTL gerado para os casos de N = 2, 3, 4, 8. Perceba que o número de pinos necessário cresce exponencialmente com N. Use o [Processing > Compilation Report] e anote o número de pinos usados, o número de elementos lógicos e o tempo de propagação do caminho crítico (TimeQuest Timing Analyser > Datasheet Report > Propagation Delay).

- Restrinja o tempo de propagação entre entrada(s) e saída(s). Para isso é necessário acrescentar ao projeto um arquivo .sdc (Synopsys Design Constraints File). No exemplo abaixo é inserida um restrição de máximo atraso (set_max_delay) entre todas as portas de entradas para todas as portas de saída de 15 ns. Para inserir esta restrição crie um arquivo sdc1.sdc com o seguinte conteúdo:

set_max_delay -from [get_ports *] -to [get_ports *] 15

- Experimente restringir o tempo máximo atraso em 11ns, 8ns, 6ns e observe o resultado da compilação. Observe o Chip Planner e também o tempo de propagação.

- Ver pag. 22 a 30 de [2]

Unidade 3

- Aula 6 (6 Abr)

- Tipos de Dados em VHDL.

- Objetos de VHDL: CONSTANT, SIGNAL, VARIABLE, FILE.

- Palavra chave OTHERS

- Bibliotecas padrão.

- ATENÇÃO!!! Não use as bibliotecas que não são padrão (std_logic_arith, std_logic_unsigned, std_logic_signed)

- Ver pag. 31 a 39 de [2]

- Aula 7 (11 Abr)

- Tipos de Dados em VHDL.

- Classificação dos tipos de dados.

- Tipos de dados: BIT, BIT_VECTOR, BOOLEAN, INTEGER, NATURAL, POSITIVE, CHARACTER, STRING, STD_(U)LOGIG, STD_(U)LOGIG_VECTOR

- Exemplo 3.1 Buffer Tri-state

- Exemplo 3.2 Circuito com Saida "don't care"

- Ver pag. 39 a 51 de [2]

- Aula 8 (13 Abr)

- Tipos de Dados em VHDL.

- Tipos de dados: SIGNED e UNSIGNED

- Exemplo 3.3 Multiplicador (un)signed

- Tipos de dados: FIXED e FLOAT (apenas conhecer)

- Resumo dos Tipos predefinidos (Tabela 3.6).

- Tipos definidos pelo usuário:

- Escalares (Inteiros e Enumerados)

- Tipos de Array 1D x 1D, 2D , 1D x 1D x 1D, 3D

- RECORD e SUBTYPE

- Exemplo 3.8: Multiplexador com porta 1D x 1D.

- Ver pag. 51 a 73 de [2]

- Aula 9 (14 Abr)

- Qualificação de tipos, conversão de tipos (automática, casting e funções de conversão).

- Resumo das funções de conversão de tipos (Tabela 3.10) e ver Aritmética com vetores em VDHL

- Exemplo 3.9: Multiplicador com sinal

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY signed_multiplier IS

PORT (

a, b: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END ENTITY;

ARCHITECTURE type_conv_arch OF signed_multiplier IS

BEGIN

y <= std_LOGIC_VECTOR(SIGNED(a) * SIGNED(b));

END ARCHITECTURE;

- Exercício:

- Implementar em VHDL um circuito que efetue a operação , utilizando portas do tipo INTEGER para valores de entrada e com sinal e ocupando 4 bits, utilize na saída 8 bits. Determine o número de elementos lógicos e verifique o código RTL obtido. Compare com os colegas.

- Repita o circuito com as mesmas características, utilizando no entanto portas do tipo STD_LOGIC_VECTOR com 4 bits nas entradas e 8 bits na saída.

- Faça a simulação funcional do circuito. Teste o circuito no minimo com , e . Note que para valores maiores de entrada e pode ocorrer overflow devido a limitação do número de bits da saída.

- Ver pag. 73 a 78 de [2]

- Aula 10 e 11 (18 e 20 Abr)

- Operadores em VHDL.

- Operadores predefinidos: Atribuição, Lógicos, Aritméticos, Comparação, Deslocamento, Concatenação, "Matching".

- Sobrecarga de operadores

- Atributos em VHDL.

- Atributos predefinidos: tipo escalar e enumerados; tipo array; de sinal;

- Exemplo 4.2 (Simulação funcional)

- Atributos definidos pelo usuário;

- Atributos de síntese:

- Aula 12 (25 Abr)

- Atributos em VHDL.

- Atributos de síntese:

ENTITY redundant_registers IS

PORT (

clk, x: IN BIT;

y: OUT BIT);

END ENTITY;

ARCHITECTURE arch OF redundant_registers IS

SIGNAL a, b, c: BIT;

-- NORMAL -- 1 LE

--ATTRIBUTE preserve: BOOLEAN;

--ATTRIBUTE preserve OF a, b, c: SIGNAL IS TRUE; -- 2 LE

--ATTRIBUTE noprune: BOOLEAN;

--ATTRIBUTE noprune OF a, b, c: SIGNAL IS TRUE; --3 LE

--ATTRIBUTE keep: BOOLEAN;

--ATTRIBUTE keep of a,b,c: SIGNAL IS TRUE;

BEGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

a <= x;

b <= x;

c <= x;

END IF;

END PROCESS;

y <= a AND b;

END ARCHITECTURE;

Após a compilação do código acima, observe o número de elementos lógicos obtidos, observe o Technology Map dos circuitos gerados e verifique a localização dos FFs no Chip Planner.

Fig 12. Technology Map do Circuito sem Attribute

Fig 13. Technology Map do Circuito com Attribute Preserve (or Keep)

Fig 14. Technology Map do Circuito com Attribute Noprune

- Group

- Alias

- Exemplo de uso no pacote numeric_std.vhd

function ADD_UNSIGNED (L, R: UNSIGNED; C: STD_LOGIC) return UNSIGNED is

constant L_LEFT: INTEGER := L'LENGTH-1;

alias XL: UNSIGNED(L_LEFT downto 0) is L;

alias XR: UNSIGNED(L_LEFT downto 0) is R;

variable RESULT: UNSIGNED(L_LEFT downto 0);

variable CBIT: STD_LOGIC := C;

begin

for I in 0 to L_LEFT loop

RESULT(I) := CBIT xor XL(I) xor XR(I);

CBIT := (CBIT and XL(I)) or (CBIT and XR(I)) or (XL(I) and XR(I));

end loop;

return RESULT;

end ADD_UNSIGNED;

- Exercício 4.17: Discussão de possibilidades de implementação

- Ver pag. 108 a 119, 140 a 142 de [2]

- Tempo livre para implementar/testar o [EL3 - Conversor de Binário para BCD].

Unidade 4

- Aula 13 (27 Abr)

- Código Concorrente.

- Uso de Operadores

- WHEN, SELECT;

- Exemplo 5.1 + 5.2 mux: com 3 tipos de arquiteturas (com operadores, com WHEN, com SELECT)

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY mux IS

GENERIC (N: INTEGER :=8);

PORT (x0, x1, x2, x3: IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

sel: IN STD_LOGIC_VECTOR(1 DOWNTO 0);

y: OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0));

END mux;

-- Arquitetura para a implementação discreta através de portas AND e OR

ARCHITECTURE Operator_only OF mux IS

signal sel0_8: STD_LOGIC_VECTOR(N-1 DOWNTO 0);

signal sel1_8: STD_LOGIC_VECTOR(N-1 DOWNTO 0);

BEGIN

sel0_8 <= (OTHERS => sel(0));

sel1_8 <= (OTHERS => sel(1));

y <= (NOT sel1_8 AND NOT sel0_8 AND x0) OR

(NOT sel1_8 AND sel0_8 AND x1) OR

(sel1_8 AND NOT sel0_8 AND x2) OR

(sel1_8 AND sel0_8 AND x3);

END operators_only;

- Para selecionar uma entre várias arquiteturas para a mesma ENTITY use a CONFIGURATION.

CONFIGURATION which_mux OF mux IS

FOR Operator_only END FOR;

-- FOR with_WHEN END FOR;

-- FOR with_SELECT END FOR;

END CONFIGURATION;

- Ver pag. 121 a 127 de [2]

- Aula 14 (28 Abr)

- Código Concorrente.

- Uso de GENERATE

label: FOR identificador IN faixa GENERATE

[Parte_Declarativa

BEGIN]

Instruções_concorrentes

...

END GENERATE [label];

</syntaxhighlight>

- Exemplo 5.4 - Decodificador genérico de endereços.

- Exemplo 5.5 - Instanciação de COMPONENTE com GENERATE.

- Ver pag. 127 a 134 de [2]

- Aula 15 (2 Mai)

- Código Concorrente.

- Exemplo de uso de operadores e SELECT.

- Exemplo 5.3 - Unidade de Lógica e Aritmética (ALU).

- Alteração do código da ALU:

- Inclusão de um sinal que indica "erro" quando ocorre overflow/underflow nas operações de soma, incremento ou decremento.

- Inclusão de um circuito que satura o sinal no máximo positivo ou negativo nas situações de erro.

- Teste da ALU usando simulação funcional.

- Aula 16 (4 Mai)

- Código Concorrente.

- Implementação de circuitos aritméticos com operadores.

- Para o uso dos operadores o mais adequado é utilizar o padrão industrial STD_LOGIC_VECTOR. Internamente os valores das portas devem ser convertidos ou para valores INTEGER ou para UNSIGNED/SIGNED. para tal é necessário utilizar a biblioteca numeric_std.

- Também é fundamental considerar a faixa de valores coberta por bits. Para tipos UNSIGNED a faixa é de até , enquanto que para SIGNED a faixa é de até . Assim com 3 bits é possível representar valores entre -4 até 3 com um tipo SIGNED e 0 até 7 com um tipo UNSIGNED.

- Para uso adequado dos operadores também é necessário considerar o tamanho (número de bits) requirido para o resultado em função do tamanho dos operandos.

- Para operações de "+" ou "-": O tamanho do resultado é igual ao tamanho do maior operando.

- Exemplo: r[7..0] = a[7..0] + b[4..0]; a -> 8 bits; b -> 5 bits então r -> 8 bits.

- Para a operações "*": O tamanho do resultado é igual a soma do tamanho dos dois operandos.

- Exemplo: r[12..0] = a[7..0] * b[4..0]; a -> 8 bits; b -> 5 bits então r -> 8+5 = 13 bits.

- Para "/": O tamanho do resultado é igual ao tamanho do numerador.

- Exemplo: r[5..0] = a[5..0] / b[8..0]; a -> 6 bits; b -> 9 bits então r -> 6 bits.

- No caso da operações de "*" e "/" não ocorre overflow, no entanto no caso da "+" e "-", o overflow pode ocorrer e precisa ser tratado. Isso pode ser feito acrescentando um bit adicional a saída para conter o overflow ou então sinalizar a sua ocorrência.

- Aula de exercícios:

- 5.3 - Porta AND e NAND Genérica.

- 5.4 - Gerador de Paridade Genérico.

- Aula 17 (9 Mai)

- Código Concorrente.

- Aula de exercícios: Escreve um código VHDL genérico que implemente os seguintes circuitos:

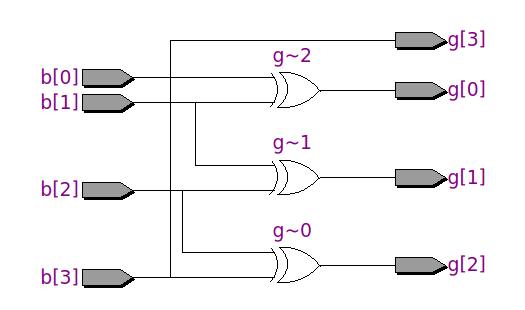

- Ex1 - Conversor de Binário para Gray genérico;

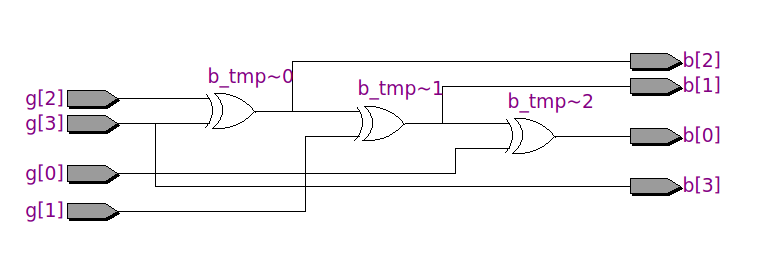

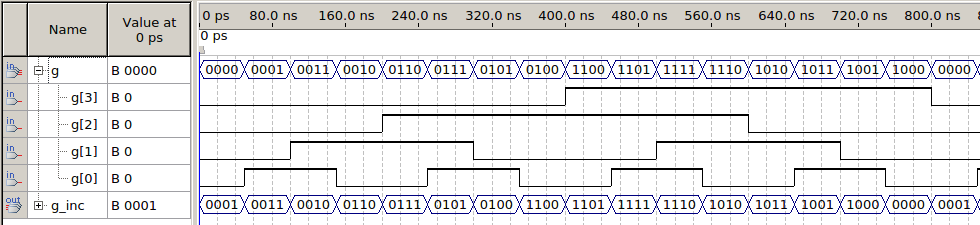

Fig 16. código RTL do conversor binário para Gray - Ex2 - Conversor de Gray para Binário genérico;

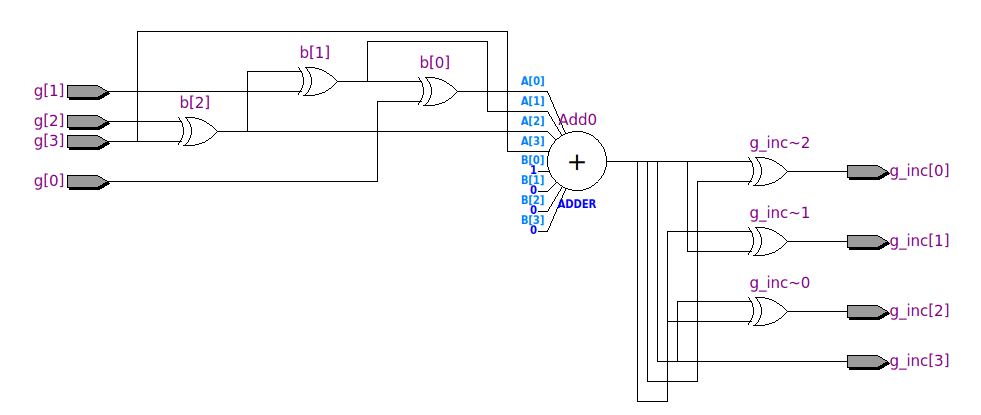

Fig 17. código RTL do conversor Gray para binário - Ex3 - Utilizando os dois circuitos anteriores e um incrementador binário escreva um código VHDL que implemente um incrementador Gray;

Fig 18. código RTL do incrementador de código Gray

Fig 19. Simulação Funcional do incrementador de código Gray - Ver também Código Gray;

- Aula 18 e 19 (11 e 12 Maio)

- Código Concorrente.

- Aula de exercicios:

- 5.4 - Generic Parity Generator;

- 5.6 - Generic Binary-to-Gray Converter;

- 5.7 - Hamming Weight with GENERATE;

- 5.10/11 - Arithmetic Circuit with INTEGER/STD_LOGIC;

- 5.15/16/17/18 - (Un)signed Multiplier/Divider;

- 5.19 - Frequency Multiplier.

Unidade 5

- Aula 20 (16 Mai)

- Código Sequencial.

- Diferenças entre código concorrente e sequencial <=> circuitos combinacional e sequencial

- Diferenças entre os objetos SIGNAL e VARIABLE

- Tipos de elementos de memória: Latch x Flip-flop

- Latch D

- Flip-flop tipo D com reset assíncrono e com reset (clear) síncrono

- Seção de código sequencial PROCESS: lista de sensibilidade

[rótulo:] PROCESS [(lista_de_sensibilidade)] [IS]

[parte_declarativa]

BEGIN

afirmação_sequencial;

afirmação_sequencial;

...

END PROCESS [rótulo];

- Instrução IF

[rótulo:] IF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSIF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSE

afirmação_sequencial;

afirmação_sequencial;

...

END IF [rótulo];

- Exemplos: DFFs with Reset and Clear (Variação Ex 6.1), Basic Counter (Ex. 6.2), Shift Register (Ex. 6.3)

- Instrução WAIT: WAIT UNTIL, WAIT FOR (simulação apenas), WAIT ON (não implementada no Quartus II).

- Algumas instruções de WAIT serão utilizadas na criação de TestBench em VHDL para a simulação com o MODELSIM.

- Recomenda-se utilizar a lista de sensibilidade do PROCESS e a instrução IF no lugar do WAIT.

- Ver pag. 161 a 160 de [2]

- Aula 21 (18 Mai)

- Código Sequencial.

- Instruções do tipo LOOP: LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT

- LOOP incondicional:

[rótulo:] LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

- FOR-LOOP:

[rótulo:] FOR identificador IN faixa LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

- WHILE-LOOP:

[rótulo:] WHILE condição LOOP -- Executa as "afirmações enquanto a "condição" for verdadeira

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

- LOOP com EXIT:

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

EXIT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, termina o "LOOP"

afirmação_sequencial;

...

END LOOP [rótulo];

- LOOP com NEXT:

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

NEXT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, não executa as linhas até a linha "END LOOP"

-- e incrementa o "identificador".

afirmação_sequencial;

...

END LOOP [rótulo];

- Exemplos: Carry-Ripple Adder (FOR-LOOP) (Ex 6.4),

- Ver pag. 161 a 164 de [2]

- Aula 22 (23 Mai)

- Código Sequencial.

- Instrução CASE

[rótulo:] CASE expressão IS

WHEN valor => atribuições; -- valor único

...

WHEN valor1 | valor2 | ... | valorN => atribuições; -- lista de valores

...

WHEN valor1 TO valor2 => atribuições; -- faixa de valores

...

END CASE;

- Exemplos:

- Leading Zeros (LOOP com EXIT) (Ex 6.5)

- Contador de 0 a 9 segundos com saída SSD (Ex 6.6)

- Projeto ruim com CASE incompleto (Ex. 6.7)

- Exercícios do Capitulo 6

- Ver pag. 164 a 176 de [2]

- Aula 23 (25 Mai)

- Código Sequencial.

- Exercícios do Capítulo 6.

Ex 6.2 - Katharine Fertig, Lucas Lucindo, Anderson Demétrio

Ex 6.5 - Fabiano Kraemer, Thiago Grisolfi,

Ex 6.7 - Kristhine Schaeffer Fertig, Tamara Arrigoni

EX 6.10 - Gustavo Constante, Gabriel Cantu

Ex 6.11 - Lucas Lucindo, Marcos Pinho, André Felippe Weber

Ex.6.14 - Iago Soares, Helen Cechinel

Ex.6.15 - Maria Luiza Theisges, Leticia Coelho

- Durante a aula os alunos foram orientados na resolução dos exercícios, e simulação usando o QSIM.

- Os alunos devem enviar o arquivo QAR contendo o projeto e simulação para o email do professor.

- Discuta com os colegas como resolveram o Exercicio proposto para eles. Cada aluno deverá saber solucionar todos os exercícios.

- Aula 24 (30 Mai)

- Avaliação A1

- Aula 25 (1 Jun)

- Correção da Avaliação A1 - Unidades 2, 3 e 4

- Resolução dos exercícios:

- EX 6.10 (Timer de dois digitos) Versão realizada por Gustavo Constante (5 processos) e Gabriel Cantu (processo único). Comparação das diferenças entre as implementações, f_{max}, e número de elementos.

- Ex.6.15 (Serializador de dados) Versão realizada por Maria Luiza Theisges

Unidade 6

- Aula 26 (6 Jun)

- Projeto a nível de Sistema.

- O PACKAGE e PACKAGE BODY: onde declarar e como usar.

- O COMPONENT: declaração (cópia da ENTITY) e instanciação.

- Associação dos nomes das portas aos sinais. PORT -> PORT MAP:

- Mapeamento por posição e nominal.

- Métodos de declaração de COMPONENT.

- Exemplo: Registrador Circular Ex. 8.2

- Ver pag. 201 a 208 de [2]

- Resolução dos exercícios:

- Ex 6.7 (Ordenador Binário) Tamara Arrigoni

- Aula 27 (8 Jun)

- Projeto a nível de Sistema.

- Criação de COMPONENT redimensionáveis. GENERIC -> GENERIC MAP

- Exemplo: Porta E com N entradas.

- Exemplo: Detector de Paridade Ex. 8.3

- Instanciação de COMPONENT com GENERATE.

- Exemplo: Registrador de deslocamento M x N Ex. 8.4

- Ver pag. 208 a 213 de [2]

- Aula 28 (13 Jun)

- Projeto a nível de Sistema.

- Uso da instrução CONFIGURATION.

- Ligação direta: ARCHITECTURE-ENTITY.

- Ligação da instanciação dos componentes: COMPONENT-ENTITY(ARCHITECTURE).

- Exercício 28.1: Inserir as duas soluções de ARCHITECTURE do exercício EX 6.10 (Timer de dois digitos) em uma única ENTITY. Utilizar CONFIGURATION para fazer a ligação com a arquitetura desejada.

entity counter60seg is

generic (fclk: integer := 2); -- valor usado para simulação.

-- generic (fclk: integer := 50_000_000); -- valor usado para implementação com clk de 50 MHz.

port (

clk, rst : in std_logic;

ssd_un, ssd_dz: out std_logic_vector(6 downto 0));

end entity ;

architecture version1 of counter60seg is

-- Versão proposta por Gabriel Cantu (processo único)

...

begin

...

end architecture ;

architecture version2 of counter60seg is

-- Versão proposta por Gustavo Constante (5 processos)

...

begin

...

end architecture ;

configuration counter60seg_cfg of counter60seg is

for version1 end for;

-- for version2 end for;

end configuration;

- Exercício 28.2: Componentização do circuito conversor de binário para display de sete segmentos. Também modifique a descrição vhdl de modo que a interface dos componentes sejam do tipo std_logic ou std_logic_vector.

entity bin2ssd is

port (

bin: in std_logic_vector(3 downto 0);

ssd: out std_logic_vector(6 downto 0));

end entity ;

architecture with_case of bin2ssd is

...

begin

...

end architecture ;

- Aula 29 (15 Jun)

- Projeto a nível de Sistema.

FUNCTION e PROCEDURE (são chamados de subprogramas), e podem ser construidos em um PACKAGE, ENTITY, ARCHITECTURE, ou PROCESS.

A instrução ASSERT é útil para verificar as entradas de um subprograma. Seu propósito não é criar circuito, mas assegurar que certos requisitos são atendidos durante a sintese e/ou simulação. Pode ser condicional ou incondicional (condição_booleana = FALSE). A sintaxe da instrução é:

[rótulo:] assert condição_booleana

[report mensagem]

[severity nivel_severidade];

A mensagem pode ser criada usando STRINGs que podem ser concatenadas.

O nível de severidade pode ser NOTE (para passar informação para o compilador/simulator), WARNING (para informar que algo não usual ocorreu), ERROR (para informar que alguma condição não usual "sério" ocorreu), ou FAILURE (para informar que uma condição não aceitável ocorreu). Normalmente o compilador para quando ocorre um ERROR ou FAILURE. NOTE é o valor "default".

- A FUNCTION: declaração, uso, mapeamento posicional x nominal, PURE x IMPURE.

function nome_funçao (lista_parametros_entrada) return tipo_saida is

declarações

begin

afirmações sequenciais

end function;

- Uso de FUNCTION e ASSERT.

- Exemplo: Declaração em ARCHITECTURE Ex.9.1

- Exemplo: Declaração em PACKAGE Ex. 9.2

- Exemplo: Declaração em ENTITY Ex. 9.3

Abaixo segue um exemplo de cálculo do log2 de um número inteiro. Pode ser usado para determinar o número de bits necessário para um número natural.

function log2c (n : integer) return integer is

variable m , p : integer;

begin

m := 0;

p : = 1;

while p < n loop

m : = m + 1;

p := p * 2;

end loop;

return m;

end log2c;

Unidade 7

- Aula 30 (16 Jun)

- Simulação com o ModelSim X Qsim

- Simular o circuito utilizando QSIM e ModelSim.

- Executar Modelsim a partir do Quartus II. Simulação usando comandos gráficos.

- Criação de arquivo wave.do (para armazenamento dos sinais e formatos).

- Criação do arquivo tb_circuito.do (para compilar, simular, definir os estimulos e executar 48 hr de simulação).

- Análise dos gráficos temporais e correção do hardware implementado.

- Complementos:

- ModelSim® Tutorial -v10.0d

- ModelSim® Reference Manual -v10.0d

- ModelSim® User’s Manual -v10.0d

- ModelSim® Quick Guide -v10.0d

- ModelSim® SE GUI Reference Manual -v10.2c

- Resolução de exercícios: Comparação do uso do QSIM e Modelsim para simular o Ex.6.14 (Relógio Digital) Helen Cechinel

- Aula 31 (20 Jun)

-

- Uso de PROCEDURE.

procedure nome_procedimento (lista_parametros_entrada, lista_parametros_saída) is

declarações

begin

afirmações sequenciais

end procedure;

/opt/altera/13.0sp1/modelsim_ase/bin/vsim

- Para usar o ModelSim 10.1d no LabProg abra um terminal e digite:

/opt/altera/13.0/quartus/modelsim_ase/linux/vsim

- Ler também Using ModelSim to Simulate Logic Circuits in VHDL Designs

- Ver também Performing a Functional Simulation with the ModelSim-Altera Software, e Performing a Timing Simulation with the ModelSim-Altera Software.

- Seguindo o tutorial da ALTERA para o MODELSIM - exemplo de um somador serial de 8 bits (projeto hierárquico com componentes: shift register, full adder e FSM)

- Resolução dos exercícios:

- Ex 6.2 (Contador Gray) Katharine Fertig

- Ex 6.5 (Registrador de deslocamento com Carga) Fabiano Kraemer, Thiago Grisolfi

- Ex 6.11 (Medidor de Frequências) Lucas Lucindo, Marcos Pinho, André Felippe Weber

UNIDADE 8

- Projeto Final - Ver AE3 - Projeto Final de Hardware

Avaliações

- Avaliação A1 - Unidade 2 a 4 (30/05/2016) - Local: Lab Programação.

- Avaliação A2 (parte 1) - Unidade 5 e 6 (04/07/2016) - Local: Lab Programação.

- As avaliações A1 e A2(parte 1) são com consulta a todo tipo de material impresso ou digital. O aluno tem 5 minutos para preparar o computador depois disso a rede será desconectada.

- Avaliação A2 (parte 2) - Unidade 6 (20/07/2016) - Local: Lab Programação.

- A avaliação A2(parte 2) é com consulta apenas as folhas VHDL QUICK REFERENCE CARD e VHDL 1164 PACKAGES QUICK REFERENCE CARD.

- Recuperação R1-2 - Unidade 2 a 6 (25/07/2016) - Local: Lab Programação.

- Ao final das avaliações o aluno deverá enviar para o email moecke AT ifsc.edu.br com os arquivos solicitados.

- Entrega dos diversos trabalhos ao longo do semestre AE1 a AE(N-1).

- Projeto Final AE(N). Tem peso equivalente a duas avaliações.

Atividades extra

Neste tópico serão listadas as atividades extras que os alunos da disciplina deverão realizar ao longo do curso. É importante observar o prazo de entrega, pois os conceitos serão reduzidos conforme o atraso na entrega.

Para a entrega no prazo os conceitos possíveis são (A, B, C, D). Entrega com até uma semana de atraso (B, C, D). Entrega com até duas semanas de atraso (C ou D). Entrega com mais de duas semanas de atraso (D).

PARA ENTREGAR

AE1 - Temas relacionados aos FPGAs (Prazo de entrega do Resumo (500 caracteres/ 1 pagina): 22 Abril 2016, Prazo de entrega do Relatório: 9 Maio 2016)

- Formar equipes com 2 ou 3 alunos, e em conjunto façam uma pesquisa sobre um dos temas abaixo, relacionados aos DLPs.

- TEMA 1 - Arquitetura FPGAs e CPLDs da ALTERA (Maria, Helen André)

- TEMA 2 - Aplicações de FPGA (Katharine, Kristhine, Leticia)

- TEMA 3 - Aplicações em Avionic (Lucas, Gabriel, Thiago)

- TEMA 4 - Aplicações na Área Espacial (Fabiano, Marcos, Iago).

- TEMA 5 - Arquitetura FPGAs e CPLDs da XILINK (Gustavo, Tamara, Anderson).

- INSPIRAÇÃO para temas:

- https://www.altera.com/products/fpga/new-to-fpgas/resource-center/overview.html

- http://www.extremetech.com/extreme/184828-intel-unveils-new-xeon-chip-with-integrated-fpga-touts-20x-performance-boost

- http://www.xilinx.com/training/fpga/fpga-field-programmable-gate-array.htm

- http://www.springer.com/cda/content/document/cda_downloaddocument/9781461435938-c2.pdf

- Architecture of FPGAs (Xilinx, Altera, Atmel, Lattice, etc). [6], [7]

- Escrever um relatório na forma de artigo com 4 a 6 paginas A4.

- Para a geração de documentação/relatórios técnicos/artigos, está disponibilizada a plataforma Sharelatex do IFSC-CLOUD. Utilize preferencialmente o modelo de artigo no padrão ABNT.

- Envie o artigo em pdf para (moecke AT ifsc.edu.br), com o ASSUNTO: DLP29006 - AE1 - Temas relacionados aos FPGAs.

- O artigo deve ser completo, incluindo todas as referências utilizadas.

- Dê um título coerente ao artigo. Seja criativo...

- Veja alguns artigos de semestres anteriores em: ARTIGOS DE SEMESTRES ANTERIORES

AE2 - Operações Aritméticas Básicas em VHDL (Prazo de entrega: 2 Maio 2016)

- Formar equipes com 2 ou 3 alunos.

- Escreva um código VHDL para cada uma das operações matemáticas indicadas abaixo. Para facilitar os testes, utilize como base o seguinte código, no qual é realizada o cálculo da multiplicação de números UNSIGNED de N=4 bits:

LIBRARY ieee;

USE ieee.numeric_std.all;

----------------------------------------

ENTITY calcular IS

GENERIC (N: NATURAL := 4);

PORT (

a, b: IN UNSIGNED(N-1 DOWNTO 0); -- N bits

y: OUT UNSIGNED(2*N-1 DOWNTO 0)); -- 2N bits

END ENTITY;

----------------------------------------

ARCHITECTURE arch_op OF calcular IS

BEGIN

y <= a * b;

END ARCHITECTURE;

----------------------------------------

Outras operações matemáticas:

y <= a + b; -- se entrada tem N bits saída deve ter N bits.

y <= a - b; -- se entrada tem N bits saída deve ter N bits.

y <= a * b; -- se entrada tem N bits saída deve ter 2*N bits.

y <= a / b; -- se entrada tem N bits saída deve ter N bits.

</syntaxhighlight>

- Para as operações de soma (a+b) e de multiplicação (a*b) com entradas SIGNED de 8 bits compare o hardware necessário para implementar os circuitos utilizando as seguintes famílias de FPGA [CYCLONE & STRATIX II & MAX 3000]. Utilize sempre o menor Device de cada família, que possua os elementos e pinos suficientes para o circuito proposto.

- Para as 4 operações compilar cada circuito utilizando N = 8, 16 e 32, e utilizando os sinais de entrada e saída do tipo SIGNED e depois também com o tipo UNSIGNED, utilizando a família de FPGA = CYCLONE.

- Teste cada um dos circuitos e anote em uma tabela todos os resultados de: número de pinos, número de elementos lógicos/ALUT (indicando os Normais | Aritméticos), multiplicadores usados, maior atraso de propagação, e caminho crítico.

- Esses dados estão disponíveis nos seguintes relatórios: (Fitter > Resource Section > Resource Usage), (TimeQuest Timing Analyser > Datasheet Report > Propagation Delay)

- Escreva um relatório técnico na forma de artigo com 4 a 6 paginas A4. O relatório além das tabelas com os dados, as figuras dos circuitos RTL com entrada de 8 bits (4 figuras), simulações funcionais com entrada de 8 bits (4 figuras) e uma análise textual dos resultados obtidos. Os QAR dos projetos para SIGNED e para UNSIGNED também devem ser enviados (2 arquivos).

- Para a geração de documentação/relatórios técnicos/artigos, está disponibilizada a plataforma Sharelatex do IFSC-CLOUD. Utilize preferencialmente o modelo de artigo no padrão ABNT.

- Envie o artigo em pdf para (moecke AT ifsc.edu.br), com o ASSUNTO: DLP29006 - AE2 - Operações Aritméticas Básicas em VHDL.

AE3 - Projeto Final de Hardware (prazo final 20/07/2016)

- Deverá ser realizado um projeto em hardware em equipes de 2 ou 3 alunos, sendo o tema de cada projeto de livre escolha da equipe.

- EQUIPES PARA O PROJETO FINAL.

EQ1 - Lucas, Gabriel

EQ2 - Maria, Helen e André

EQ3 - Leticia, Katharine, Kristhine

EQ4 - Gustavo, Tamara

EQ5 - Fabiano, Marcos, Iago

EQ6 - Anderson, Tiago / Fabiano

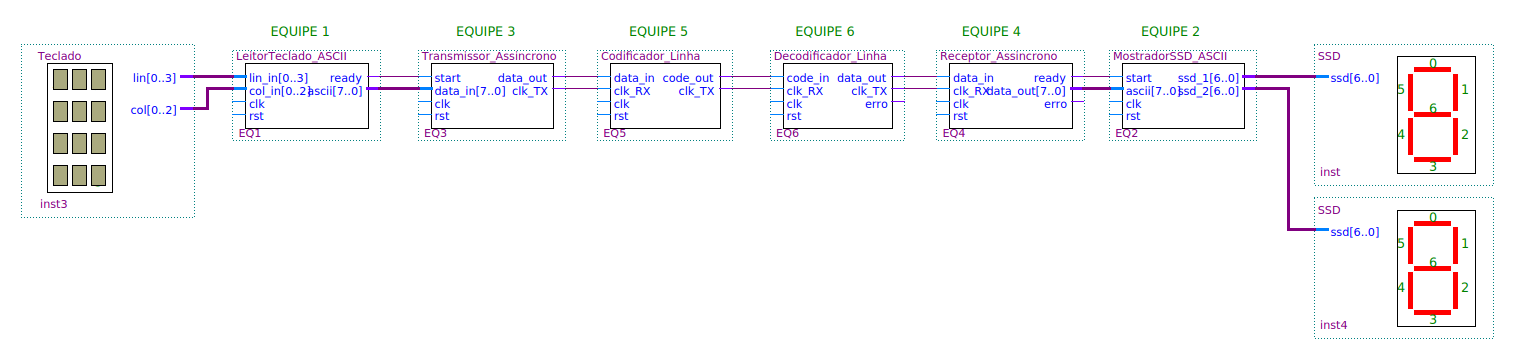

- EQ1, EQ2 - Leitor de Teclado ASCII com Debouncer; Display SSD ASCII

- EQ3, EQ4 - Serializador e Deserializador Assincrono

- EQ5, EQ6 - Codificador de linha e Decodificador decodificador (CMI, Manchester Diferencial, (duas entre Manchester, RZ, 5B/6B, NRZI, etc)

- Cada projeto deverá ser implementado utilizando um kit DE2-115 ou Mercúrio IV.

- Os projetos deverão ser divididos em componentes. No nível hierárquico de nível 0 (top level) será permitida apenas a instanciação de componentes.

- Lembre-se que as chaves push-bottom produzem repiques - Dicas de como eliminar o repique das chaves mecânicas

- As equipes deverão trabalhar de forma que o projeto todo possa ser integrado ao final do cronograma conforme mostrado na figura abaixo:

- No mínimo os pares indicados EQ1-EQ2, EQ3-EQ4, EQ5-EQ6 deverão ser integrados.

- Prazos:

- Definição da TOP ENTITY de cada subprojeto e integração dos componentes dos pares e projeto (29/Jun)

- Desenvolvimento dos subprojetos e simulação.

- Teste na placa

- Integração pares (18/Jul)

- Integração projeto (21/Jul)

- Entrega da Documentação Final (25/Jul)

- Apresentação das Equipes (27/Jul)

- Os projetos/alunos serão analisados em 5 quesitos:

- 1 - Implementação do projeto, atendimento as especificações e requisitos do sistema.

- 2 - Documentação do projeto e especificações iniciais.

- 3 - Avaliação do aluno durante o desenvolvimento do projeto.

- 4 - Integração do projeto com as outras equipes.

- 5 - Apresentação do projeto para a turma (15 minutos por equipe)

- Para a geração de documentação/relatórios técnicos/artigos, está disponibilizada a plataforma Sharelatex do IFSC-CLOUD. Utilize preferencialmente o modelo de artigo no padrão ABNT. Veja também o Modelo para uso em relatórios.

- O relatório técnico deverá:

- No desenvolvimento buscar descrever: as especificação do Sistema, a descrição do Sistema, a Interface do Usuário, a Descrição dos Hardware

- Nos resultados descrever: as simulações feitas usando MODELSIM, os resultados práticos, as medições feitas, os problemas encontrados resolvidos ou não.

- Envie o artigo em pdf para (moecke AT ifsc.edu.br), com o ASSUNTO: DLP29006 - AE3 - Projeto Final.

ESTUDOS SEM ENTREGA DE DOCUMENTAÇÃO

Os exemplos e exercícios essenciais estão destacados em negrito na listagens abaixo.

EL1 - Resolução dos exercícios do Cap 2

- Resolva os exercícios do capítulo 2 (1, 2, 3) pag. 28 a 30

- Exercise 2.1

- Multiplexer:

- Complete o código VHDL abaixo para que ele seja correspondente a um multiplexador que selecione a entrada A quando sel ="01", B quando sel ="10", coloque "0...0" na saída quando sel ="00" e mantenha a saída em alta impedância "Z...Z" quando sel="11".

- Compile o código e em seguida faça a simulação, para verificar se o circuito funciona conforme

especificado.

- Anote as mensagens de warning do compilador.

---------------------------------------

-- File: mux.vdh

---------------------------------------

-- Declaração das Bibliotecas e Pacotes

--

LIBRARY ieee;

USE _________________________ ;

---------------------------------------

-- Especificação das entradas e saídas e nome da ENTITY

ENTITY mux IS

PORT (

__ , __ : ___ STD_LOGIC_VECTOR (7 DOWNTO 0);

sel : IN ____________________________ ;

___ : OUT STD_LOGIC_VECTOR (7 DOWNTO 0));

END _____ ;

---------------------------------------

ARCHITECTURE example OF _____ IS

BEGIN

PROCESS (a, b, ____ )

BEGIN

IF (sel = "00") THEN

c <= "00000000";

ELSIF (__________) THEN

c <= a;

_____ (sel = "10") THEN

c <= __;

ELSE

c <= (OTHERS => '__');

END ___ ;

END _________ ;

END _________ ;

---------------------------------------

EL2 - Resolução dos exercícios do Cap 3

- Resolva os exercícios do capítulo 3 (1, 2, 9, 11, 12, 13, 14-17, 18, 20, 22, 23-30) pag. 81 a 89

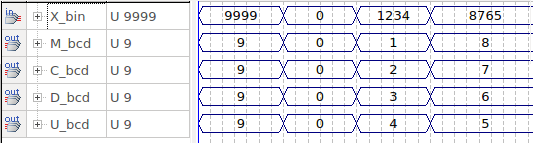

EL3 - Conversor de Binário para BCD

- Considere um número decimal entre 0000 e 9999. Usando operadores predefinidos, obtenha na saída os digitos decimais separados.

- Escreva o código VHDL e analise o número de elementos lógicos necessários.

- Faça a simulação funcional do circuito.

Fig. 20 - Simulação da conversão de binário para BCD

- Compare sua implementação com os outros estudantes e analise as diferenças, observe o código RTL, o número de elementos lógicos e também o tempo de propagação.

- Para separar os dígitos decimais do número de entrada pense nos operadores de "+", "-", "*", "/", "REM" e "MOD".

- Para facilitar os testes e a troca de informações entre as equipes, a ENTITY deverá ter o seguinte formato:

entity bin2bcd is

port (

X_bin : in std_logic_vector(13 downto 0); -- 0000 a 9999

M_bcd : out std_logic_vector(3 downto 0); -- Milhar

C_bcd : out std_logic_vector(3 downto 0); -- Centena

D_bcd : out std_logic_vector(3 downto 0); -- Dezena

U_bcd : out std_logic_vector(3 downto 0)); -- Unidade

end entity;

architecture example of bin2bcd is

--declaração de sinais auxiliares

begin

--descrição do hardware

end architecture;

- Note que com X_bin 14 bits é possível representar números sem sinal entre 0 e . No entanto, os testes devem ser limitados a números entre 0000 e 9990, pois não há especificação para valores maiores que 9999.

- Existe um algoritmo Double Dabble que possibilita fazer essa conversão com menos hardware.

- Dica para converter de INTEGER para STD_LOGIC_VECTOR de 4 bits.

M_bcd <= std_logic_vector(to_unsigned(M,4));

EL4 - Resolução dos exercícios do Cap 4

- Resolva os exercícios do capítulo 4 (4-8, 9, 10-11, 13, 15-16, 17 ) pag. 115 a 120

EL5 - Resolução dos exercícios do Cap 5

- Resolva os exercícios do capítulo 5 (1, 2, 3, 4, 6, 7, 8-9, 10-11, 14-16, 17-18, 19 ) pag. 144 a 150

EL6 - Resolução dos exercícios do Cap 6

- Resolva os exercícios do capítulo 6 (1, 2, 3-4, 5, 6-7, 9*, 10-11, 12*, 13*, 14, 15) pag. 172 a 176.

EL7 - Resolução dos exercícios do Cap 8 e 9

- Resolva os exercícios da capítulo 8 (1-7, 9*) pag. 219 a 220.

- Resolva os exercícios da capítulo 9 (1-3, 6-9) pag. 238 a 239.

ARTIGOS ENTREGUES

- 2016-1

- Arquitetura FPGAs e CPLDs da ALTERA (André Felippe Weber, Helenluciany Cechinel, Maria Luiza Theisges)

- Aplicações de FPGA em Robótica (Letícia Aparecida Coelho, Katharine Schaeffer Fertig, Kristhine Schaeffer Fertig)

- FPGA aplicado a aviônica: Problemas e soluções (Gabriel Cantu, Lucas Lucindo, Thiago Grisolfi)

- Aplicações na Área Espacial (Marcos Vinicios Pinho, Fabiano Kraeamer, Iago Soares)

- Arquitetura FPGAs e CPLDs da XILINK (Anderson Demetrio, Gustavo Constante, Tamara Arrigoni)

- 2015-2

- DLPs: passado, presente e futuro (Walter Cardoso de Freitas Júnior, Gustavo Vieira Zacchi, Giulio Oliveira)

- Transitores CMOS, história e tecnologia (Fernando Müller da Silva, Gustavo Paulo Medeiros da Silva)

- Linguagens de Descrição de Hardware: Tipos e Características (João Vitor Rodrigues, Marcus Vinicius Bunn)

- Fabricantes e ferramentas para programação de DLPs (Ronaldo João Borges, Roicenir Girardi Rostirolla)

- Interface JTAG (Stephany Padilha Guimarães, Lucas Gomes de Farias, Vinicius Bandeira)

- 2015-1

Recursos de Laboratório

Quartus/Modelsim/QSIM

Nos laboratórios do IFSC, os softwares Quartus/Modelsim/QSIM estão disponíveis diretamente na plataforma LINUX. Utilize preferencialmente a versão 13.0sp1 (32 bits), pois ela tem suporte para os FPGAs mais antigos como a familia Cyclone I.

Para uso fora do IFSC dos recursos computacionais com licença educacional, o IFSC disponibiliza para seus alunos o IFSC-CLOUD. Atualmente a forma mais eficiente de acesso é através do Cliente X2GO. O procedimento de instalação/ configuração e uso do Quartus/Modelsim/QSIM está descrito em Acesso ao IFSC-CLOUD#Cliente X2GO (recomendado).

Para a geração de documentação/relatórios técnicos/artigos, está disponibilizada a plataforma Sharelatex do IFSC-CLOUD. Utilize preferencialmente o modelo de artigo no padrão ABNT.

Links auxiliares

- Aritmética com vetores em VDHL

- Preparando para gravar o circuito lógico no FPGA

- Dicas de como eliminar o repique das chaves mecânicas

- Dicas para resolver ERROS de síntese do VHDL no Quartus II

- Materiais da ALTERA para Quartus II 13.1

- Modelo para uso em relatórios

- Configuração e uso do Time Quest Analyser

- Configuração e uso do Signal Tap

- DLP29006-Engtelecom(2015-1) - Prof. Marcos Moecke

- DLP29006-Engtelecom(2015-2) - Prof. Marcos Moecke

Livros/Resumos sobre VHDL

- Regras de codificação em VHDL

- VHDL Handbook - Hardi (apenas VHDL’87 e VHDL’93)

- VHDL Math Tricks of the Trade by Jim Lewis

- VHDL QUICK REFERENCE CARD - Qualis (r2.1)

- VHDL 1164 PACKAGES QUICK REFERENCE CARD - Qualis (r2.2)

- VDHL ref

- Listagem dos packages

- Palavras reservadas

- Atributos predefinidos

- Aritmética em VHDL

Packages não padronizados

- Std logic arith.vhd by Synopsys

- std_logic_arith.vhd by Synopsys

- std_logic_arith.vhd by Mentor Graphics

- std_logic_arith.vhd by Vinaya

- Std logic unsigned.vdh by Synopsys

- std_logic_unsigned.vhd by Synopsys

Simulador Modelsim

- Site Mentor Graphics - Software Version 10.0

- ModelSim InfoHub - Software Version v10.2c

- ModelSim Quick Video Demo - precisa fazer login na Mentor Graphics.

- ModelSim® Tutorial -v10.0d

- ModelSim® Reference Manual -v10.0d

- ModelSim® User’s Manual -v10.0d

- ModelSim® Quick Guide -v10.0d

- ModelSim® SE GUI Reference Manual -v10.2c

Fabricantes de DLPs

Fabricantes de kits com DLPS

Leituras recomendadas

- USE OF FIELD PROGRAMMABLE GATE ARRAY TECHNOLOGY IN FUTURE: SPACE AVIONICS, Roscoe C. Ferguson, Robert Tate, NASA.

- Expect a Breakthrough Advantage in NextGeneration FPGAs, Stephen Lim, ALTERA.

- A Reconfigurable Fabric for Accelerating Large-Scale Datacenter Services, Microsoft.

Padrões IEEE para o VDHL

Os padrões IEEE [8]estão disponíveis para consulta se você estiver na rede do IFSC. Para a linguagem VHDL consulte os padrões: 1164,1076

- IEEE Standard Multivalue Logic System for VHDL Model Interoperability (Std_logic_1164)

- IEEE Std 1076.1: Behavioural languages – Part 1-1: VHDL language reference manual

- IEEE Std 1076.1: Behavioural languages – Part 6: VHDL Analog and Mixed-Signal Extensions

- IEEE Std 1076.1.1™-2011 - IEEE Standard for VHDL Analog and Mixed-Signal Extensions—Packages for Multiple Energy Domain Support, REDLINE

- IEEE Standard for VHDL Register Transfer Level (RTL) Synthesis

- IEEE Standard VHDL Analog and Mixed-Signal Extensions

- IEEE Standard VHDL Synthesis Packages

- IEEE Std 1076-2002: IEEE Standard VHDL Language Reference Manual

- IEEE Std 1076.2-1996: IEEE Standard VHDL Mathematical Packages

Packages da IEEE

Referências Bibliográficas:

- ↑ 1,0 1,1 1,2 PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,00 2,01 2,02 2,03 2,04 2,05 2,06 2,07 2,08 2,09 2,10 2,11 2,12 2,13 2,14 2,15 2,16 2,17 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335