Mudanças entre as edições de "Circuito Somador e Subtrator - Pedroni"

Ir para navegação

Ir para pesquisar

| Linha 48: | Linha 48: | ||

! colspan="1" style="background: #efefef;" | Report Path | ! colspan="1" style="background: #efefef;" | Report Path | ||

! colspan="1" style="background: #efefef;" | Report Timing | ! colspan="1" style="background: #efefef;" | Report Timing | ||

| + | ! colspan="1" style="background: #efefef;" | Caminho crítico | ||

| + | ! colspan="1" style="background: #efefef;" | Logic Block | ||

|- | |- | ||

| − | | 4 || 34 || 142.03 ||3.035 | + | | 4 || 34 || 142.03 ||3.035 || 3.267 || deserial0|dout[0]-internal[3] || S |

|- | |- | ||

| − | | 32 || 234 || 185.14 || 5.481 | + | | 32 || 234 || 185.14 || 5.481 || 5.713 || deserial0|dout[0]-internal[31] || S |

|- | |- | ||

| − | | 128 || | + | | 128 || 882 || 306.90 || 13.062 || 13.294 || deserial1-dout[0]-internal[127] || Auto |

|- | |- | ||

|} | |} | ||

Edição das 10h04min de 11 de abril de 2016

Estrutura

- Realiza a soma simples através do operador '+'.

VHDL

| Código |

|---|

--Book: Pedroni/491

--8 bits

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity add_sub is

generic (n: natural := 4);

port(

a,b: in std_logic_vector (n-1 downto 0);

--sub : out std_logic_vector (n-1 downto 0));

sum : out std_logic_vector (n-1 downto 0));

end entity;

architecture add_sub of add_sub is

signal sum_sig : signed (n-1 downto 0);

--signal sub_sig : signed (n-1 downto 0);

begin

--Convert to signed and add_sub

sum_sig <= signed(a) + signed(b);

--sub_sig <= signed(a) - signed(b);

--Return to std_logic_vector

sum <= std_logic_vector (sum_sig);

--sub <= std_logic_vector (sub_sig);

end architecture;

|

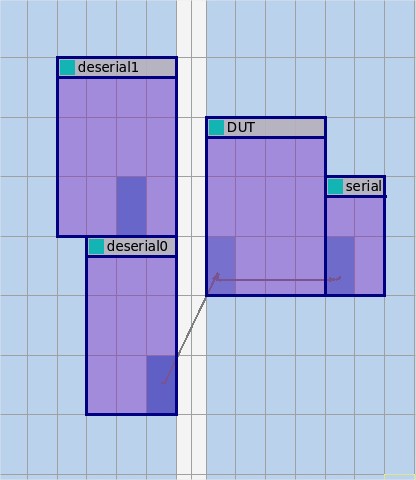

- Chip planner:

Simulações

| Nº Bits | ALMs | Potência (mW) | Report Path | Report Timing | Caminho crítico | Logic Block |

|---|---|---|---|---|---|---|

| 4 | 34 | 142.03 | 3.035 | 3.267 | dout[0]-internal[3] | S |

| 32 | 234 | 185.14 | 5.481 | 5.713 | dout[0]-internal[31] | S |

| 128 | 882 | 306.90 | 13.062 | 13.294 | deserial1-dout[0]-internal[127] | Auto |