DI2022802 2022 1 AULA02

1 Contadores

Os contadores são circuitos que utilizam flip-flops e são aplicados, principalmente, em contagens diversas, divisão de frequência, medição de frequência e de tempo, divisão de formas de onda e conversão de analógico para digital. Estes circuitos sequenciais são divididos em duas categorias:

- Contadores assíncronos; e

- Contadores síncronos.

A principal diferença entre eles é que o síncrono utiliza um sinal de clock comum a todos os flip-flops e o assíncrono possuí um sinal de clock que é dividido até o último flip-flops.

1.1 Contadores Assíncronos

Estes contadores também são conhecidos como seriais ou contadores por pulsação (ripple counter). Tal nome advém do fato dos flip-flops (FF) do contador não serem disparados diretamente pelo sinal de clock. Cada FF é disparado pela saída do FF anterior. Esta característica torna estes contadores limitados em termos de velocidade, pois o tempo de ativação (tempo de resposta) é dado aproximadamente pela soma dos tempos de atraso de propagação de cada FF.

1.1.1 Contador assíncrono crescente

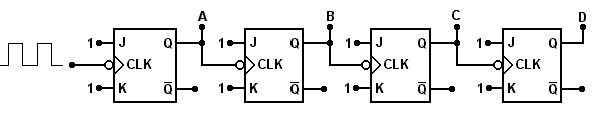

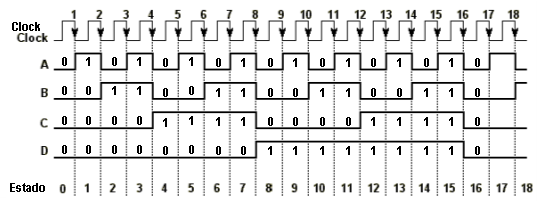

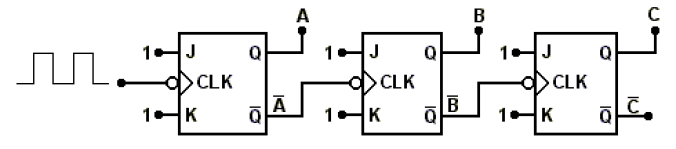

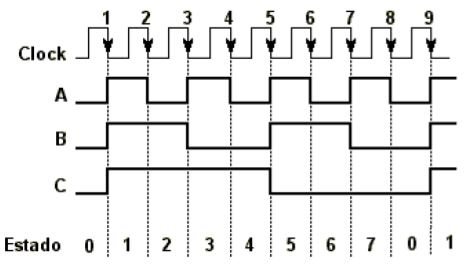

Um circuito típico de um contador assíncrono crescente construído com FF do tipo JK é mostrado na Figura 1. Os FF JK estão com ambas entradas J e K permanentemente em nível alto, estando configuradas portanto como FF tipo T. Cada FF é disparado pela saída do FF anterior. A Figura 2 mostra o diagrama de tempo para esse contador.

Figura 1 - Contador assíncrono crescente.

O contador tem como conteúdo, estado interno, a contagem do número de transições negativas do clock, de forma que quando ocorre uma transição o conteúdo é incrementado de uma unidade. O conteúdo do contador é dado pelo número binário DCBA, onde A é o bit LSB (bit menos significativo) e D é o bit MSB (bit mais significativo). O modulo (MOD) de um contador é o seu número de estados distintos, portanto, o módulo de um contador com N FF pode ser no máximo o número de possíveis saídas (). A Tabela 1 mostra os estados de contagem de um contador assíncrono com 4 FF (4 bits). Podemos perceber que após 16 transições de clock o contador reinicia a contagem. Por isso, este contador é de MOD-16, ou seja, tem 16 estados distintos (0000b até 1111b).

Figura 2 - Diagrama de tempo do contador assíncrono crescente.

Nos contadores assíncronos, a frequência do clock é dividida por 2 em cada FF, ou seja: na saída A temos clock/2, e na saída D temos clock/16. Portanto, os contadores assíncronos são divisores de frequência e no último FF a frequência de clock é dividida pelo módulo do contador.

| Clock | D | C | B | A | Decimal | Estado |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 2 | 0 | 0 | 1 | 0 | 2 | 2 |

| 3 | 0 | 0 | 1 | 1 | 3 | 3 |

| 4 | 0 | 1 | 0 | 0 | 4 | 4 |

| 5 | 0 | 1 | 0 | 1 | 5 | 5 |

| 6 | 0 | 1 | 1 | 0 | 6 | 6 |

| 7 | 0 | 1 | 1 | 1 | 7 | 7 |

| 8 | 1 | 0 | 0 | 0 | 8 | 8 |

| 9 | 1 | 0 | 0 | 1 | 9 | 9 |

| 10 | 1 | 0 | 1 | 0 | 10 | 10 |

| 11 | 1 | 0 | 1 | 1 | 11 | 11 |

| 12 | 1 | 1 | 0 | 0 | 12 | 12 |

| 13 | 1 | 1 | 0 | 1 | 13 | 13 |

| 14 | 1 | 1 | 1 | 0 | 14 | 14 |

| 15 | 1 | 1 | 1 | 1 | 15 | 15 |

| 16 | 0 | 0 | 0 | 0 | 0 | 0 |

| 17 | 0 | 0 | 0 | 1 | 1 | 1 |

| 18 | 0 | 0 | 1 | 0 | 2 | 2 |

Figura 1b - Contador assíncrono crescente (animação).

Vale ressaltar que os FFs estão configurados com J=1 e K=1 que dá a característica de contador "natural", ou seja, a cada pulso de clock a saída é complementada (0->1 e 1->0). Cada FF anterior gera o clock do próximo FF assim realizando a contagem conforme mostra o diagrama da Figura 2 e a Tabela 1. Lembrando que no primeiro FF vai o sinal de clock.

- Contador na prática

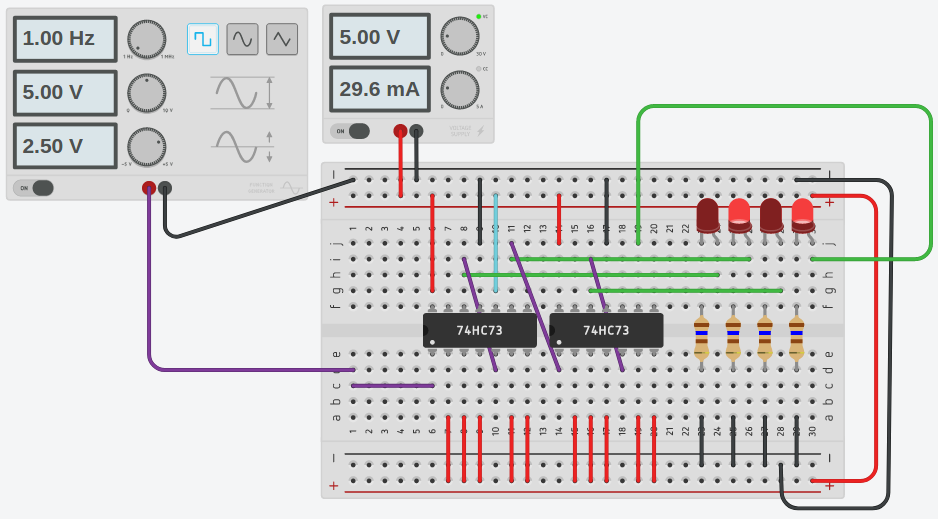

A Figura 3 mostra o circuito realístico utilizando o 7473 (duplo flip-flop JK) montado e simulado com a página do Tinkercad.

Figura 3 - Contador assíncrono crescente realístico.

Na Figura 3 podemos visualizar um Gerador de função configurado para uma frequência de 1Hz com 5V de amplitude e um componente CC de 2,5V, que transforma a onda quadrada em sinal de clock oscilando entre 0V e 5V - respectivamente 0 e 1 lógicos. Também temos uma Fonte de energia e uma placa de ensaio pequena. Quanto às ligações (fios) em vermelho são 5V (nível lógico alto), as em verde foram utilizadas para conectar às saídas, às ligações em preto são 0V (nível lógico baixo) e às ligações em roxo foram utilizadas para o clock. Lembrando que o clock sempre vem das saídas anteriores, exceto o clock do primeiro flip-flop que vem do Gerador de função. A Figura 4 mostra o diagrama de pinos do 7473.

Figura 4 - Diagrama de pinos do 7473 (duplo flip-flop JK).

No Diagrama de pinos podemos observar que o sinal do clock (pinos CLK) é por borda de descida e que o clear (pinos CLR) é ativo baixo.

1.1.2 Contadores com módulo <

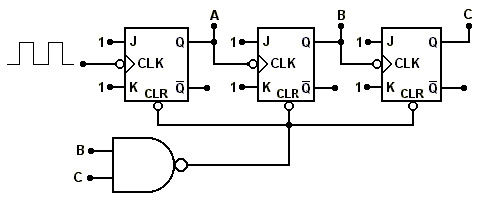

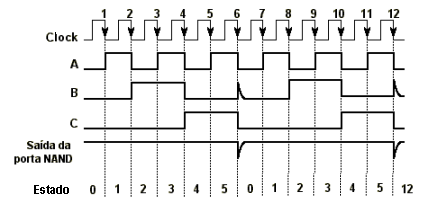

Para obter um contador com módulo menor do que é necessário adicionar um circuito decodificador para reiniciar a contagem antes de chegar ao valor máximo (ou mínimo). A Figura 5 mostra um contador MOD-6. Se não houvesse a porta NAND ligada nas entradas CLR dos FF o módulo do contador seria 8. A sequência de estados do contador MOD-6 é mostrada nas Figura 6 e Tabela 2. Note que na transição do 6º clock o estado do contador passa temporariamente pelo estado (110b), o qual faz com que a saída da porta NAND passe para o estado BAIXO, causando o CLR nos FF, e consequentemente levando o contador para o estado (000b).

Figura 5 - Contador assíncrono com módulo < .

Figura 6 - Diagrama de tempo do contador com módulo < .

| Clock | C | B | A | Decimal | Estado |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 2 | 0 | 1 | 0 | 2 | 2 |

| 3 | 0 | 1 | 1 | 3 | 3 |

| 4 | 1 | 0 | 0 | 4 | 4 |

| 5 | 1 | 0 | 1 | 5 | 5 |

| 6* | 1 | 1 | 0 | 6 | 6 |

| 6 | 0 | 0 | 0 | 0 | 0 |

| 7 | 0 | 0 | 1 | 1 | 1 |

| 8 | 0 | 1 | 0 | 2 | 2 |

*Não atingível.

A Figura 6b mostra a animação do contador MOD-6. Percebam que foi utilizado uma porta AND ao invés de NAND porque o R (reset) é ativo alto. Então quando a contagem chega a 110b que é 6d a porta AND é ativada e sua saída da reset em todos os FFs recomeçando a contagem de 0. Cuidado com o bit mais significativo e menos significativo.

Figura 6b - Contador assíncrono com MOD-6 (animação).

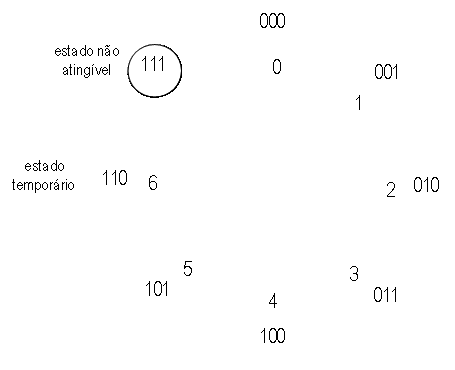

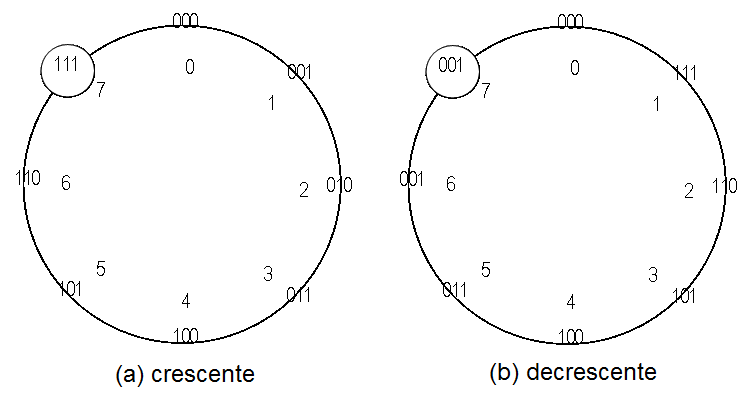

O diagrama de transição de estados do contador de 3 bits MOD-6 é mostrado na Figura 7. No diagrama de transição as linhas contínuas indicam a passagem pelos estados estáveis (000b 101b) e as linhas tracejadas indicam a passagem pelos estados temporários (110b). O estado (111b) embora possível não é atingível.

Figura 7 - Diagrama de transição de estados de um contador MOD-6.

Para a construção de um contador módulo X menor que o módulo máximo, o procedimento deve seguir as etapas:

- Determinar o menor número N de FF tal que .

- Exemplo: MOD-12 N = 16.

- Conectar a porta NAND nas entradas assíncronas de todos os FF. Se , não é necessário conectar nada a entrada;

- Conectar as saídas que estarão em ALTO na contagem X, na porta NAND.

- Exemplo: 12 = 1100b D = 1 e C = 1, conectar D e C a porta NAND.

1.1.3 Contadores de década

Os contadores de década (ou decádico) são contadores que possuem 10 estados distintos, não importando a sequência de contagem. Quando um contador decádico realiza a contagem em sequência binária crescente de 0000b a 1001b (0 a 9), ele é chamado de contador BCD. A Figura 8 mostra o CI 7490.

Figura 8 - Circuito Integrado Contador 7490.

O circuito integrado TTL 7490 consiste num contador de década, divisor por 2 e por 5, com saídas BCD. Cada circuito integrado exige uma corrente de 32 mA e a máxima frequência de contagem é 18 MHz. A contagem ocorre nas transições negativas do sinal de clock. Este circuito é encontrado em versões mais rápidas nas subfamílias TTLs correspondentes. Datasheet 7490 - Contador Decádico

O circuito do contador pode ser simulado no 'falstad'. A Figura 8b mostra o circuito com o contador (a esquerda), no centro o decodificador - que transforma a contagem binária em contagem decimal num display de 7 segmentos a direita.

Figura 8b - Circuito contador 'falstad'.

1.1.4 Contador assíncrono decrescente

Os contadores que contam progressivamente a partir do zero são denominados contadores crescentes (ou ascendentes). Já os contadores que contam do valor máximo até zero são chamados decrescentes (ou descendentes). A Figura 8 mostra a configuração para um contador decrescente construído com FF do tipo JK. A configuração é semelhante à do contador crescente, com a única diferença de cada FF é disparado pela saída Q\ no lugar de Q.

Figura 8 - Contador assíncrono decrescente.

A Figura 9 mostra o diagrama de tempo das saídas do contador, enquanto que a Tabela 3 mostra a contagem das transições do clock e os estados correspondentes ao contador. O diagrama de estados do contador decrescente é mostrado na Figura 10 (b), enquanto que o diagrama do contador crescente é mostrado na Figura 10 (a). Note que nos dois diagramas o contador passa por todos os estados.

Figura 9 - Diagrama de tempo do contador assíncrono decrescente.

| Clock | C | B | A | Decimal | Estado |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 7 | 1 |

| 2 | 1 | 1 | 0 | 6 | 2 |

| 3 | 1 | 0 | 1 | 5 | 3 |

| 4 | 1 | 0 | 0 | 4 | 4 |

| 5 | 0 | 1 | 1 | 3 | 5 |

| 6 | 0 | 1 | 0 | 2 | 6 |

| 7 | 0 | 0 | 1 | 1 | 7 |

| 8 | 0 | 0 | 0 | 0 | 0 |

| 9 | 1 | 1 | 1 | 7 | 1 |

| 10 | 1 | 1 | 0 | 6 | 2 |

Figura 10 - Diagrama de transição de estados do contador MOD-8.

1.1.5 Contador assíncrono ascendente-descendente

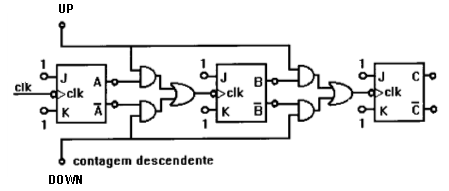

O contador assíncrono ascendente-descendente, também chamado de reversível, é uma combinação dos contadores anteriormente vistos. Ele possui os FF conectados conforme mostra a Figura 11. Nesta configuração a lógica de portas permite que o contador tenha dois modos de operação distintos:

- Modo de contagem ascendente: UP = 1 e DOWN = 0. Os FF B e C são disparados pelas saídas não complementares do FF anterior (Q)

- Modo de contagem descendente: UP = 0 e DOWN = 1. Os FF B e C são disparados pelas saídas complementares do FF anterior (Q\)

Figura 11 - Contador assíncrono ascendente-descendente.

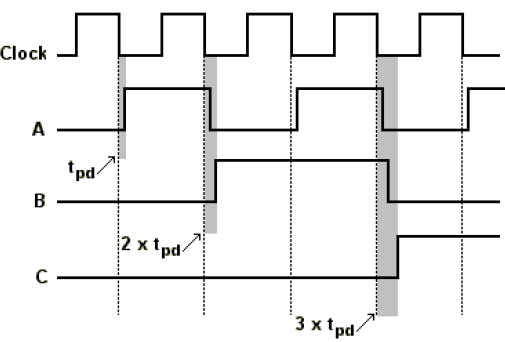

1.2 Atrasos de Propagação de Contadores Assíncronos

Em um contador assíncrono cada FF é disparado pela saída de um FF anterior. Essa característica traz como desvantagem o acumulo dos tempos de atraso de propagação. Isso pode ser visto na Figura 12. Ao passar por um FF, o sinal de clock sofre um atraso de propagação e esse efeito é somado até o último FF, gerando um atraso total de , onde N é o número de FF.

Figura 12 - Contador assíncrono ascendente-descendente.

Para que um contador assíncrono funcione de modo confiável é necessário que o atraso total de propagação seja menor que o período de clock usado: , ou ainda, em termos de frequência máxima, que .

2 Exercício de Fixação

[1] Se um contador crescente tá mostrando 0111111b qual o próximo número da contagem?

[2] Quantos FFs eu preciso para contar até:

- 10

- 20

- 50

- 250

- 1000

- 1000000

[3] Qual a combinação (de bits) que deve chegar na saída para que eu conte até 100?

[4] Pra que serve Set e Reset nos FFs?

[5] Qual a diferença em termos de ligações para um contador contar crescente ou decrescente com FFs por borda de descida?

[6] Qual a diferença em termos de ligações para um contador contar crescente ou decrescente com FFs por borda de subida?

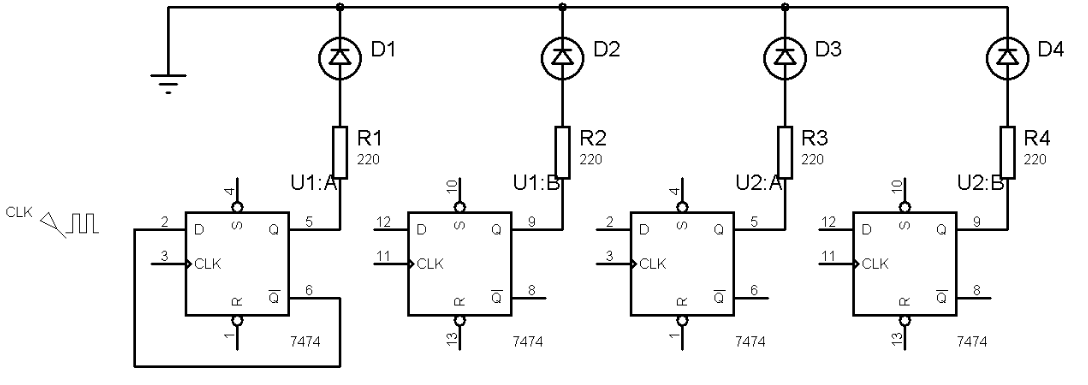

[7] Complete o circuito abaixo para que funcione como contador assíncrono crescente.

[8] Utilizando o mesmo circuito, faça as modificações necessárias para que funcione como contador assíncrono decrescente.

3 VHDL

- Código VHDL

- Descreve o funcionamento de FF tipo JK.

library ieee;

use ieee.std_logic_1164.all;

ENTITY ff_jk is

port(j,k,clk: in bit;

q: out bit);

END ff_jk;

ARCHITECTURE teste of ff_jk is

BEGIN

process(clk)

variable temp : bit :='0';

begin

if( falling_edge(clk) ) then

if (j='1' and k='0') then

temp:='1';

elsif (j='0' and k='1') then

temp:='0';

elsif (j='1' and k='1') then

temp:= not temp;

else

temp:=temp;

end if;

q<=temp;

end if;

end process;

END teste;

4 Referências

[1] Apostila do CURSO DE ELETRÔNICA DIGITAL. CEFET/SC: São José, 2011.

[2] https://pdf1.alldatasheetpt.com/datasheet-pdf/view/50911/FAIRCHILD/7473.html

[3] https://www.tinkercad.com/