Mudanças entre as edições de "SST20707-2013-2"

(→Slides) |

(→Slides) |

||

| Linha 41: | Linha 41: | ||

*[[Media:Sst-lab3_componentes.pdf|Componentes em VHDL]] | *[[Media:Sst-lab3_componentes.pdf|Componentes em VHDL]] | ||

*[[Media:sst-lab4_mux_decode.pdf|Mux e Decode]] | *[[Media:sst-lab4_mux_decode.pdf|Mux e Decode]] | ||

| + | *[[Media:sst-lab5_flipflop.pdf|Circuitos Seqüênciais]] | ||

= 16/08: Apresentação = | = 16/08: Apresentação = | ||

Edição das 08h20min de 11 de outubro de 2013

Síntese de Sistemas de Telecomunicações: Diário de Aula 2013-2

Professor: Roberto de Matos

Encontros: 3ª feira 9:40 e 6ª feira 7:30

Atendimento paralelo: 4ª feira das 13:30 às 15:20.

Assuntos trabalhados

- Introdução aos dispositivos lógicos programáveis

- Introdução à tecnologia FPGA

- Introdução a linguagem VHDL

Apoio Desenvolvimento

Slides

- Slides de Introdução

- Fluxo de Projeto Quartus

- Introdução à Linguagem VHDL

- Componentes em VHDL

- Mux e Decode

- Circuitos Seqüênciais

16/08: Apresentação

- Apresentação do professor.

- Apresentação dos alunos: Nome, perfil, preferências, etc.

- Apresentação da disciplina: conteúdo, bibliografia e avaliação.

- Aula Introdutória:

- Por que dispositivos lógicos programáveis?

- Histórico

20/08: Desenvolvimento com PLDs

- Famílias de Componentes Lógicos Programáveis

- Arquitetura dos FPGAS

- Introdução ao Fluxo de Projeto do Quartus

23/08: Laboratório Quartus

- Fluxo de projeto esquemáticos com Quartus e Modelsim (Porta AND)

- Exercício: Projeto, Simulação e Teste do meio-somador

27/08: Introdução à Linguagem VHDL

- Finalização do fluxo de projeto do Meio somador no Quartus e Modelsim, utilização a entrada de esquemático.

- Apresentação da Linguagem VHDL

- Conceitos de entidade (entity) e arquitetura (architecture)

30/08: Projetando com VHDL

- Estudo de caso: Meio Somador em VHDL

03/09: Projetando com VHDL

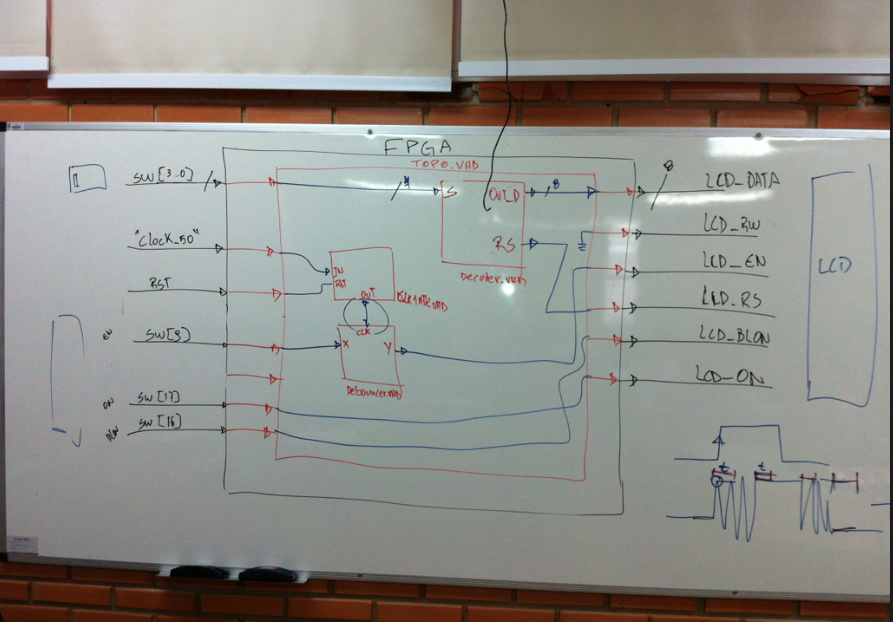

- Exercício: Manipulação do LCD utilizando VHDL

06/09: Código Concorrente (WHEN, SELECT)

WHEN

- Sintaxe Simplificada:

signal_name <=

value_expr_1 when boolean_expr_1 else

value_expr_2 when boolean_expr_2 else

value_expr_3 when boolean_expr_3 else

...

value_expr_n

</syntaxhighlight>

- Exemplo:

x <= a when (s="00") else

b when (s="01") else

c when (s="10") else

d;

</syntaxhighlight>

SELECT

- Sintaxe Simplificada:

with select_expression select

signal_name <= value_expr_1 when choice_1,

value_expr_2 when choice_2,

value_expr_3 when choice_3,

...

value_expr_n when choice_n;

</syntaxhighlight>

- Exemplo:

with s select

x <= "0001" when "00",

"0010" when "01",

"0011" when "10",

"0100" when others;

</syntaxhighlight>

10/09: Componentes (COMPONENT, PORT MAP)

- Sintaxe Simplificada:

--Declaração----------------------------------------------------------

COMPONENT component_name [IS]

[GENERIC (

const_name: const_type := const_value;

...);]

PORT (

port_name: port_mode signal_type;

...);

END COMPONENT [component_name];

--Instanciação----------------------------------------------------------

label: [COMPONENT] component_name [GENERIC MAP (generic_list) ] PORT MAP (port_list);

</syntaxhighlight>

- Exemplo:

--Declaração----------------------------------------------------------

COMPONENT nand_gate IS

PORT ( a, b: IN STD_LOGIC;

c: OUT STD_LOGIC);

END COMPONENT;

--Instanciação---------------------------------------------------------

nand1: nand_gate PORT MAP (x, y, z); --mapeamento posicional

nand2: nand_gate PORT MAP (a=>x, b=>y, c=>z); --mapeamento nominal

</syntaxhighlight>

- Exemplo GENERIC:

--Declaração----------------------------------------------------------

COMPONENT xor_gate IS

GENERIC (N: INTEGER := 8);

PORT ( a: IN STD_LOGIC(1 TO N);

b: OUT STD_LOGIC);

END COMPONENT;

--Instanciação----------------------------------------------------------

xor1: xor_gate GENERIC MAP (16) PORT MAP (x, y); --map. posicional

xor2: xor_gate GENERIC MAP (N=>16) PORT MAP (a=>x, b=>y); --map. nominal

</syntaxhighlight>

13/09: Componentes (continuação)

- Exercício utilizando o "decodificador" LCD e o debouncer.

- Arquivos de apoio.

17/09: Não houve aula

- Palestra Sinapse da Inovação

20/09: Componentes (continuação)

- Exercício de componentes utilizando o exemplo do LCD Decode.

24/09: Suspensa

- Convocação do professores pela Direção de Ensino

27/09: Projeto MUX 4x1

- Projeto e simulação do MUX estrutural e comportamental.

01/10: Projeto do Decode de 7 Segmentos

- Projeto e simulação do Decode de 7 segmentos para a escrita de "IFSC"

05/10: Apresentação do 1º Projeto

Documentação do Projeto:

- Deve ser preparado um arquivo compactado (*.zip, *.rar) contendo o seguinte:

- Arquivo *.qar com todos os VHDL do projeto (topo_upc.vhd, op_or.vhd, op_xor.vhd, op_soma.vhd, op_id.vhd, mux_4x1.vhd, decode_7seg.vhd);

- Arquivos *.do de todos os módulos (test_X.do e wave_X.do, sendo X é a identificação do módulo testado);

- Relatório

- O Relatório deve conter o seguinte:

- Identificação do autor

- Tabela verdade para cada componente;

- Diagrama de blocos com sinais de entrada e saída para cada componente;

- Diagramas de forma de ondas extraídos diretamente do ModelSim para cada componente;

- Descrição das ferramentas utilizadas e fluxo de projeto;

Avaliação

- O trabalho deverá ser desenvolvido individualmente.

- O trabalho deverá chegar na caixa de entrada do email do professor com o assunto SST-UCP_Nome_Aluno até o dia 18/10/2013 às 23:59h, impreterivelmente.

- A apresentação e demonstração do funcionamento por intermédio de simulação e prototipação será realizada em data a ser definida.

- Durante a apresentação, os alunos deverão estar aptos a responder quaisquer perguntas. Respostas insatisfatórias ou a ausência do aluno acarretará em anulação da nota do trabalho.

- As explicações durante a demonstração do projeto funcionando são fundamentais para a avaliação.

- Trabalhos copiados resultarão em nota zero para todos os alunos envolvidos. Poderá ser utilizado a ferramenta MOSS como auxílio na identificação de situações de plágio.

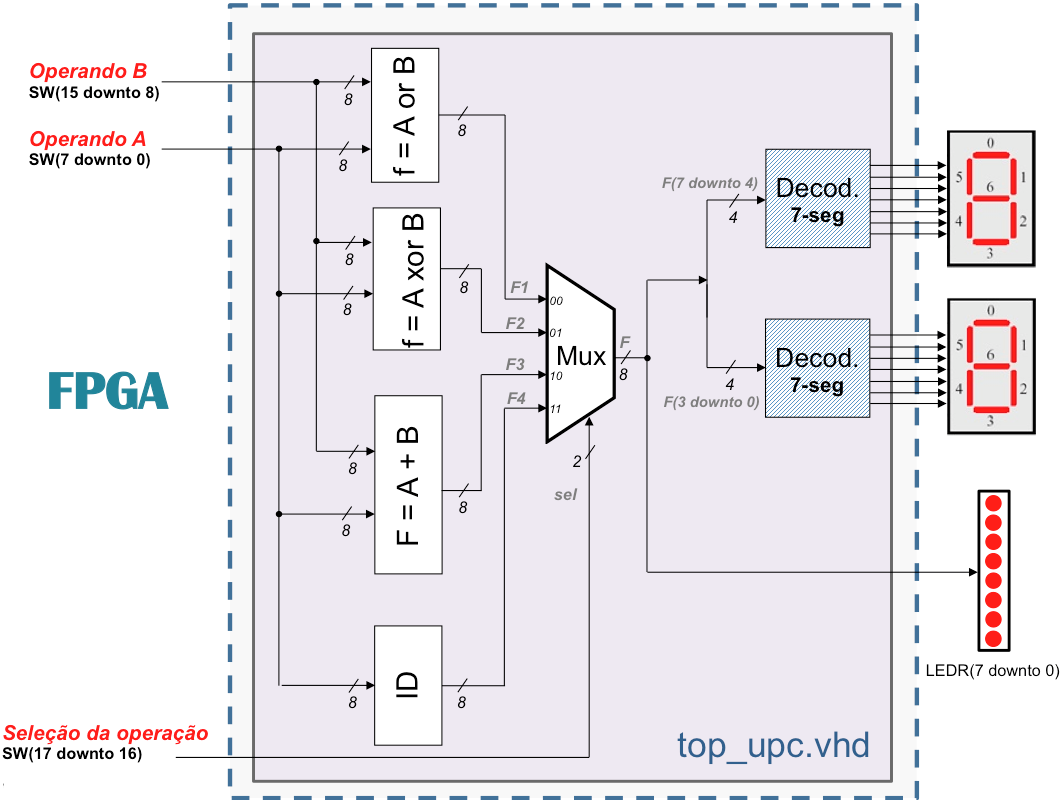

Objetivo

Desenvolver um projeto hierárquico com módulos em VHDL que implementem uma Unidade de Processamento Combinacional (UPC) capaz de realizar as funções lógicas OU e XOR, a função aritmética de SOMA e a geração do ID baseado na matrícula sobre dois operandos de 8 bits e apresentar o resultado em dois displays de 7 segmentos e 8 LEDs da DE2-115.

- A UPC terá o seguinte funcionamento:

- Entrar com o operando A nas chaves SW (15-8) e o operando B nas chaves SW (7-0)

- Entrar com a escolha da operação (OP) a ser executada nas chaves (17-16)

- Disponibilizar na saída (Diplays e LEDs) o resultado da operação.

- Requisitos:

- O projeto deverá ser desenvolvido fora horário de aula.

- Todos os módulos devem ser implementados como componentes e instanciados no arquivo topo.

- O componente MUX deve ter a implementação de duas arquiteturas: Estrutural e Comportamental.

- Deve haver somente um componente Decode e duas instanciações.

- Componente ID: A operação ID deve manipular os quatro últimos números da matrícula do aluno (------XYH-L). Quando o valor da entrada A for o XY (hexadecimal) e a operação selecionada for o ID os displays devem mostrar o valor HL. Qualquer outro valor de entrada deve gerar o valor FF no display.

Cronograma

- 04/10: Apresentação dos objetivos do trabalho.

- 11/10: Aula para retirada de dúvidas. Observação: O projeto já deve estar encaminhado, lembrem que nesse dia, já se passou metade do prazo para entrega.

- 18/10: Prazo final para entrega do trabalho.

Horários do Laboratório

- Previsão (precisa confirmar disponibilidade dos Labs):

- Segunda: 10:00h às 20:00h

- Terça: 14:00h às 20:00h

- Quarta: 16:00h às 18:00h

- Quinta: 14:00h às 20:00h