Mudanças entre as edições de "SST20707-2013-2"

| Linha 37: | Linha 37: | ||

*[[Media:Sst-lab3_componentes.pdf|Componentes em VHDL]] | *[[Media:Sst-lab3_componentes.pdf|Componentes em VHDL]] | ||

| − | = 1ª Aula: Apresentação = | + | = 1ª Aula: Apresentação (16/08/2013) = |

* Apresentação do professor. | * Apresentação do professor. | ||

* Apresentação dos alunos: Nome, perfil, preferências, etc. | * Apresentação dos alunos: Nome, perfil, preferências, etc. | ||

| Linha 45: | Linha 45: | ||

** Histórico | ** Histórico | ||

| − | = 2ª Aula: Desenvolvimento com PLDs = | + | = 2ª Aula: Desenvolvimento com PLDs (20/08/2013) = |

* Famílias de Componentes Lógicos Programáveis | * Famílias de Componentes Lógicos Programáveis | ||

* Arquitetura dos FPGAS | * Arquitetura dos FPGAS | ||

* Introdução ao Fluxo de Projeto do Quartus | * Introdução ao Fluxo de Projeto do Quartus | ||

| − | = 3ª Aula: Laboratório Quartus = | + | = 3ª Aula: Laboratório Quartus (23/08/2013)= |

* Fluxo de projeto esquemáticos com Quartus e Modelsim (Porta AND) | * Fluxo de projeto esquemáticos com Quartus e Modelsim (Porta AND) | ||

* Exercício: Projeto, Simulação e Teste do [http://en.wikipedia.org/wiki/Adder_(electronics) meio-somador] | * Exercício: Projeto, Simulação e Teste do [http://en.wikipedia.org/wiki/Adder_(electronics) meio-somador] | ||

| − | = 4ª Aula: Introdução à Linguagem VHDL = | + | = 4ª Aula: Introdução à Linguagem VHDL (27/08/2013)= |

* Finalização do fluxo de projeto do Meio somador no Quartus e Modelsim, utilização a entrada de esquemático. | * Finalização do fluxo de projeto do Meio somador no Quartus e Modelsim, utilização a entrada de esquemático. | ||

* Apresentação da Linguagem VHDL | * Apresentação da Linguagem VHDL | ||

* Conceitos de entidade (entity) e arquitetura (architecture) | * Conceitos de entidade (entity) e arquitetura (architecture) | ||

| − | = 5ª Aula: Projetando com VHDL = | + | = 5ª Aula: Projetando com VHDL (30/08/2013)= |

* Estudo de caso: Meio Somador em VHDL | * Estudo de caso: Meio Somador em VHDL | ||

| − | = 6ª Aula: Projetando com VHDL = | + | = 6ª Aula: Projetando com VHDL (03/09/2013)= |

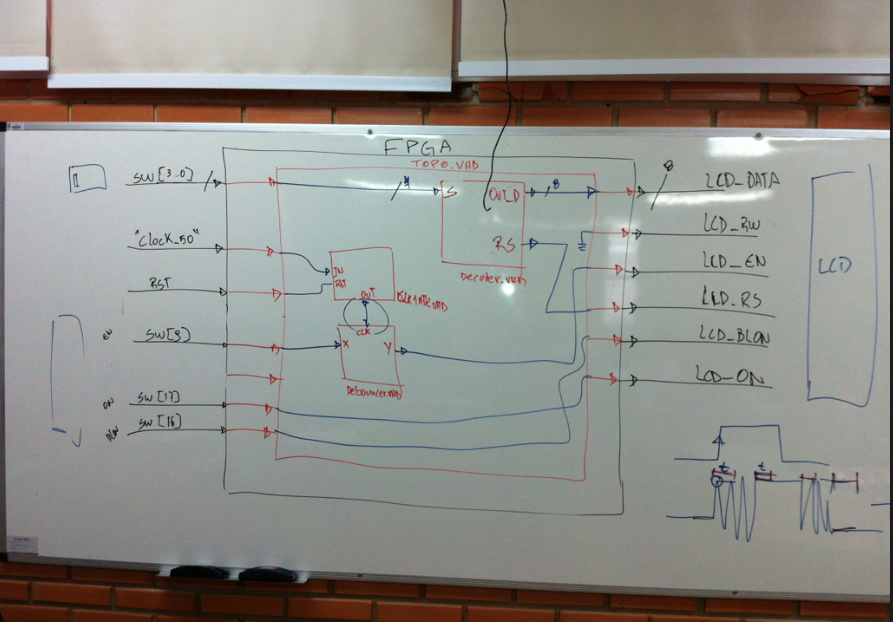

* Exercício: Manipulação do LCD utilizando VHDL | * Exercício: Manipulação do LCD utilizando VHDL | ||

| − | = 7ª Aula: Código Concorrente (WHEN, SELECT) = | + | = 7ª Aula: Código Concorrente (WHEN, SELECT) (06/09/2013) = |

== WHEN == | == WHEN == | ||

| Linha 106: | Linha 106: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | = 8ª Aula: Componentes (COMPONENT, PORT MAP) = | + | = 8ª Aula: Componentes (COMPONENT, PORT MAP) (10/09/2013)= |

*Sintaxe Simplificada: | *Sintaxe Simplificada: | ||

| Linha 163: | Linha 163: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | = 9ª Aula: Componentes (continuação) = | + | = 9ª Aula: Componentes (continuação) (13/09/2013)= |

*Exercício utilizando o "decodificador" LCD e o debouncer. | *Exercício utilizando o "decodificador" LCD e o debouncer. | ||

| Linha 172: | Linha 172: | ||

| − | = 10ª Aula: Não houve aula = | + | = 10ª Aula: Não houve aula (17/09/2013)= |

* Palestra Sinapse da Inovação | * Palestra Sinapse da Inovação | ||

| − | = 11ª Aula: Componentes (continuação) = | + | = 11ª Aula: Componentes (continuação) (20/09/2013)= |

*Exercício de componentes utilizando o exemplo do LCD Decode. | *Exercício de componentes utilizando o exemplo do LCD Decode. | ||

Edição das 19h22min de 26 de setembro de 2013

Síntese de Sistemas de Telecomunicações: Diário de Aula 2013-2

Professor: Roberto de Matos

Encontros: 3ª feira 9:40 e 6ª feira 7:30

Atendimento paralelo: 4ª feira das 13:30 às 15:20.

Assuntos trabalhados

- Introdução aos dispositivos lógicos programáveis

- Introdução à tecnologia FPGA

- Introdução a linguagem VHDL

Apoio Desenvolvimento

Slides

1ª Aula: Apresentação (16/08/2013)

- Apresentação do professor.

- Apresentação dos alunos: Nome, perfil, preferências, etc.

- Apresentação da disciplina: conteúdo, bibliografia e avaliação.

- Aula Introdutória:

- Por que dispositivos lógicos programáveis?

- Histórico

2ª Aula: Desenvolvimento com PLDs (20/08/2013)

- Famílias de Componentes Lógicos Programáveis

- Arquitetura dos FPGAS

- Introdução ao Fluxo de Projeto do Quartus

3ª Aula: Laboratório Quartus (23/08/2013)

- Fluxo de projeto esquemáticos com Quartus e Modelsim (Porta AND)

- Exercício: Projeto, Simulação e Teste do meio-somador

4ª Aula: Introdução à Linguagem VHDL (27/08/2013)

- Finalização do fluxo de projeto do Meio somador no Quartus e Modelsim, utilização a entrada de esquemático.

- Apresentação da Linguagem VHDL

- Conceitos de entidade (entity) e arquitetura (architecture)

5ª Aula: Projetando com VHDL (30/08/2013)

- Estudo de caso: Meio Somador em VHDL

6ª Aula: Projetando com VHDL (03/09/2013)

- Exercício: Manipulação do LCD utilizando VHDL

7ª Aula: Código Concorrente (WHEN, SELECT) (06/09/2013)

WHEN

- Sintaxe Simplificada:

signal_name <=

value_expr_1 when boolean_expr_1 else

value_expr_2 when boolean_expr_2 else

value_expr_3 when boolean_expr_3 else

...

value_expr_n

</syntaxhighlight>

- Exemplo:

x <= a when (s="00") else

b when (s="01") else

c when (s="10") else

d;

</syntaxhighlight>

SELECT

- Sintaxe Simplificada:

with select_expression select

signal_name <= value_expr_1 when choice_1,

value_expr_2 when choice_2,

value_expr_3 when choice_3,

...

value_expr_n when choice_n;

</syntaxhighlight>

- Exemplo:

with s select

x <= a when "00",

b when "01",

c when "10",

d when others;

</syntaxhighlight>

8ª Aula: Componentes (COMPONENT, PORT MAP) (10/09/2013)

- Sintaxe Simplificada:

--Declaração----------------------------------------------------------

COMPONENT component_name [IS]

[GENERIC (

const_name: const_type := const_value;

...);]

PORT (

port_name: port_mode signal_type;

...);

END COMPONENT [component_name];

--Instanciação----------------------------------------------------------

label: [COMPONENT] component_name [GENERIC MAP (generic_list) ] PORT MAP (port_list);

</syntaxhighlight>

- Exemplo:

--Declaração----------------------------------------------------------

COMPONENT nand_gate IS

PORT ( a, b: IN STD_LOGIC;

c: OUT STD_LOGIC);

END COMPONENT;

--Instanciação---------------------------------------------------------

nand1: nand_gate PORT MAP (x, y, z); --mapeamento posicional

nand2: nand_gate PORT MAP (a=>x, b=>y, c=>z); --mapeamento nominal

</syntaxhighlight>

- Exemplo GENERIC:

--Declaração----------------------------------------------------------

COMPONENT xor_gate IS

GENERIC (N: INTEGER := 8);

PORT ( a: IN STD_LOGIC(1 TO N);

b: OUT STD_LOGIC);

END COMPONENT;

--Instanciação----------------------------------------------------------

xor1: xor_gate GENERIC MAP (16) PORT MAP (x, y); --map. posicional

xor2: xor_gate GENERIC MAP (N=>16) PORT MAP (a=>x, b=>y); --map. nominal

</syntaxhighlight>

9ª Aula: Componentes (continuação) (13/09/2013)

- Exercício utilizando o "decodificador" LCD e o debouncer.

- Arquivos de apoio.

10ª Aula: Não houve aula (17/09/2013)

- Palestra Sinapse da Inovação

11ª Aula: Componentes (continuação) (20/09/2013)

- Exercício de componentes utilizando o exemplo do LCD Decode.