Mudanças entre as edições de "PROJETO FINAL - Grupo 2 - SST"

Ir para navegação

Ir para pesquisar

(→VHDL) |

|||

| Linha 27: | Linha 27: | ||

{{Collapse top | Código}} | {{Collapse top | Código}} | ||

| − | + | ||

:<syntaxhighlight lang=vhdl> | :<syntaxhighlight lang=vhdl> | ||

| Linha 318: | Linha 318: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | ||

{{Collapse bottom}} | {{Collapse bottom}} | ||

Edição atual tal como às 13h31min de 19 de junho de 2015

Projeto Final - Grupo 2

Alunos: Kamila, Leonardo Oliveira e Renan;

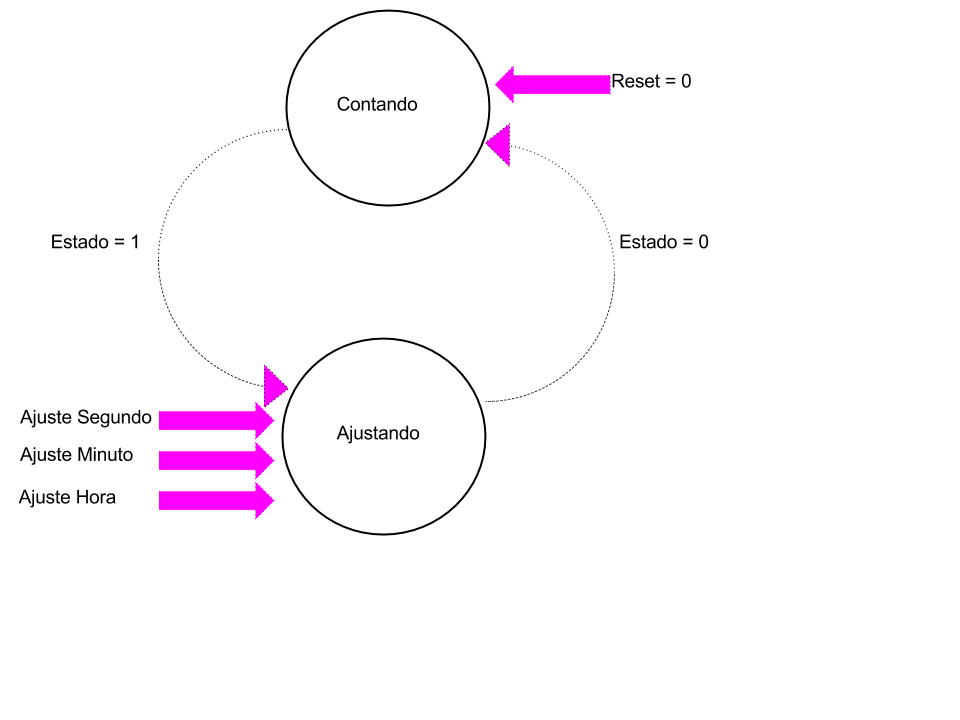

Diagrama de Estados

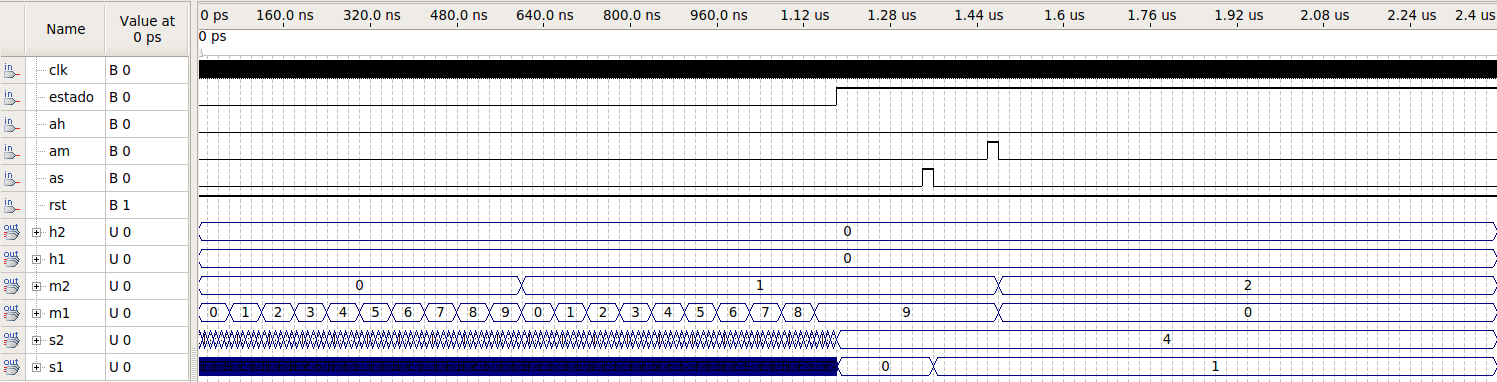

Formas de onda

- Exemplo da forma de onda sem as saídas dos display para visualização em Decimal:

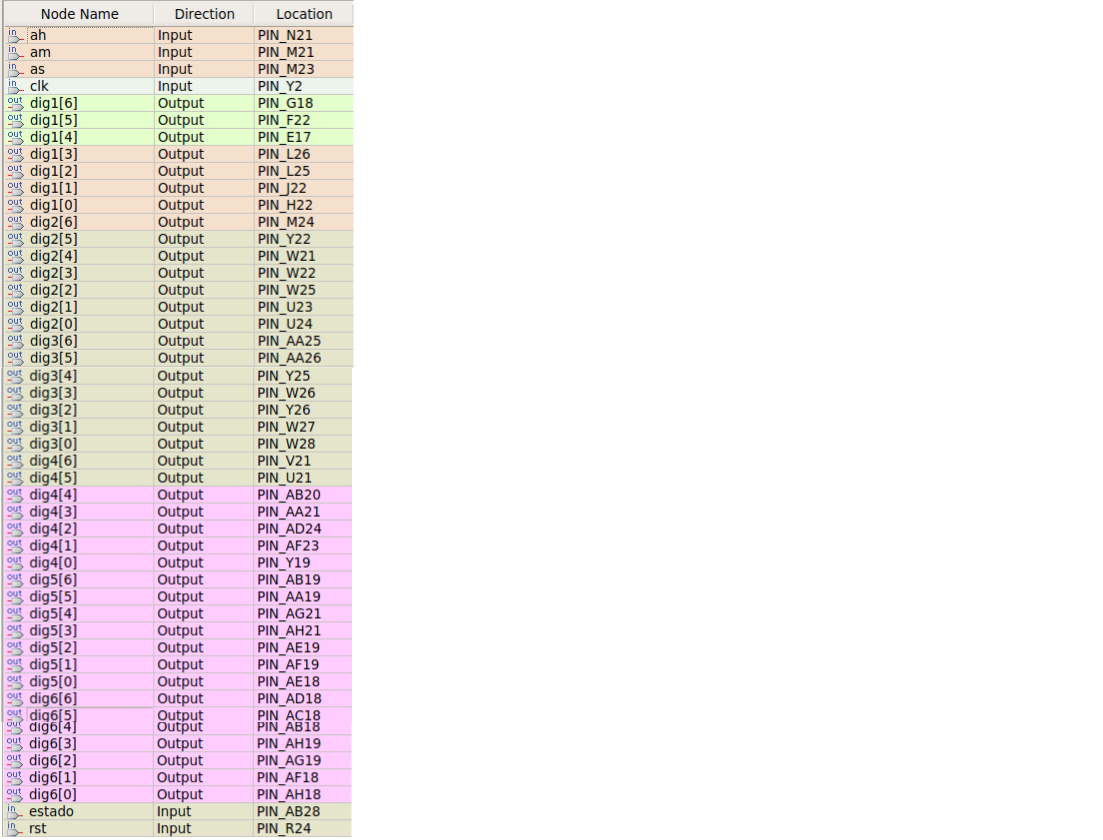

Pinagem DE2-115

VHDL

- Descrição

- A abordagem utilizada foi comportamental.

- O relógio possui 2 estados: st0 e st1. O estado st0 é responsável por realizar a contagem do relógio e permite que sua contagem seja resetada. O estado st1 é responsável pelo ajuste do relógio, quando há a troca de estado, este mantém o relógio parado e através de 3 entradas é possível alterar a hora, o minuto e o segundo.

- As saídas são exibidas em 6 display de 7-segmentos.

- O código possui 2 processos: síncrono e combinacional.

- O primeiro processo define a troca dos estados, que estão atrelados a entrada "Estado" (presente na lista de sensibilidade deste process), quando a entrada "Estado" é '0', assume-se st0 (Contando), quando a entrada "Estado" é '1' assume-se st1 (ajustando).

- O segundo processo define os estados st0 e st1 através de instruções de seleção (case/when). Possui na lista de sensibilidade o clock, reset e os botões de ajuste de hora/minuto/segundo.

- A transição entre os estados "Contando" e "Ajustando" são independentes.

- A saída de ambos os estados obedecem o princípio da Máquina de Mealy, onde as saídas dependem do estado atual e também das entradas.

| Código |

|---|

|