Mudanças entre as edições de "Experimento 13 para Circuitos Lógicos"

Ir para navegação

Ir para pesquisar

| Linha 12: | Linha 12: | ||

#CI [http://www.ti.com/lit/ds/symlink/sn74ls386a.pdf 74X386 XOR](disponível na biblioteca da ALTERA) | #CI [http://www.ti.com/lit/ds/symlink/sn74ls386a.pdf 74X386 XOR](disponível na biblioteca da ALTERA) | ||

#Computador com software Quartus II da Altera. | #Computador com software Quartus II da Altera. | ||

| − | + | ||

==Diagrama Esquemático== | ==Diagrama Esquemático== | ||

*Abra o Quartus II e insira o diagrama esquemático do somador completo, conforme a figura abaixo. | *Abra o Quartus II e insira o diagrama esquemático do somador completo, conforme a figura abaixo. | ||

| Linha 19: | Linha 19: | ||

</center> | </center> | ||

| − | *Salve o arquivo como FullAdder.bdf em uma pasta vazia com nome PROJ2, e crie um projeto FullAdder.qpf utilizando a família family='''Cyclone''' com o dispositivo device='''EP1C3T100A8'''. Após isso | + | *Salve o arquivo como FullAdder.bdf em uma pasta vazia com nome PROJ2, e crie um projeto FullAdder.qpf utilizando a família family='''Cyclone''' com o dispositivo device='''EP1C3T100A8'''. Após isso compile o projeto. |

*Crie um simbolo para este circuito, selecionando na IDE do Quartus II o diagrama esquemático e [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK]. | *Crie um simbolo para este circuito, selecionando na IDE do Quartus II o diagrama esquemático e [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK]. | ||

<center> | <center> | ||

| Linha 140: | Linha 140: | ||

|} | |} | ||

</center> | </center> | ||

| − | |||

Edição das 13h35min de 20 de outubro de 2014

Aritmética binária (Somador/Subtrator/Complemento de 2)

- Objetivos

- Compreender o funcionamento dos circuitos aritméticos somador, subtrator e complemento de 2;

- Obter o sinal de saída simulado usando o QSIM - diagrama funcional;

- Analisar os resultados obtidos para entender e associar os tipos de operações realizadas;

- Verificar os resultados obtidos;

- Materiais necessários

- CI 74X00 NAND(disponível na biblioteca da ALTERA)

- CI 74X04 NOT(disponível na biblioteca da ALTERA)

- CI 74X32 OR(disponível na biblioteca da ALTERA)

- CI 74X386 XOR(disponível na biblioteca da ALTERA)

- Computador com software Quartus II da Altera.

Diagrama Esquemático

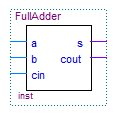

- Abra o Quartus II e insira o diagrama esquemático do somador completo, conforme a figura abaixo.

- Salve o arquivo como FullAdder.bdf em uma pasta vazia com nome PROJ2, e crie um projeto FullAdder.qpf utilizando a família family=Cyclone com o dispositivo device=EP1C3T100A8. Após isso compile o projeto.

- Crie um simbolo para este circuito, selecionando na IDE do Quartus II o diagrama esquemático e [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK].

Simulação funcional com o QSIM

- Abra o editor de forma de onda do simulador QSIM (File > New > University Programa VWF) (v 13.0 e 13.1).

- Defina o tempo de simulação (Edit > Set End Time ...) = 200 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

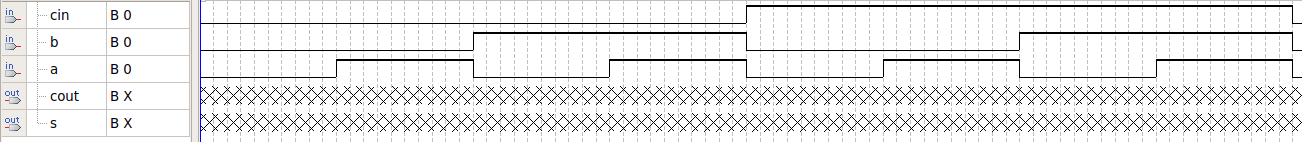

- Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome TesteFA.vwf.

- Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK] (v. 13.0)

- Faça a simulação funcional do circuito lógico usando o sinal criado (Simulation > Run Functional Simulation)

- O resultado da simulação deve corresponder a um somador completo.

- Note que os bits das entradas estão agrupados e definidos como RADIX "Binary". Para isso selecione os sinais [Edit > Grouping] [Group name = IN] > [Radix = Binary] > [OK].

- Note que os bits das saídas estão agrupados e definidos como RADIX = "Decimal sem sinal". Para isso selecione os sinais [Edit > Grouping] [Group name = OUT] > [Radix = Unsigned Decimal] > [OK].

Análise dos resultados

- Analise o resultado preenchendo a tabela-verdade abaixo:

| Entradas | Saídas | |||

|---|---|---|---|---|

| cin | a | b | s | cout |

| 0 | 0 | 0 | ||

| 0 | 0 | 1 | ||

| 0 | 1 | 0 | ||

| 0 | 1 | 1 | ||

| 1 | 0 | 0 | ||

| 1 | 0 | 1 | ||

| 1 | 1 | 0 | ||

| 1 | 1 | 1 | ||

Criar o componente FullAdder

- Selecione na IDE do Quartus II o diagrama esquemático do FullAdder e selecione [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK].

- Note que um novo simbolo estará disponível para uso no diagrama esquemático com o nome FullAdder

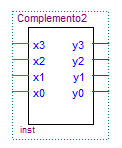

Complemento de 2

Diagrama Esquemático

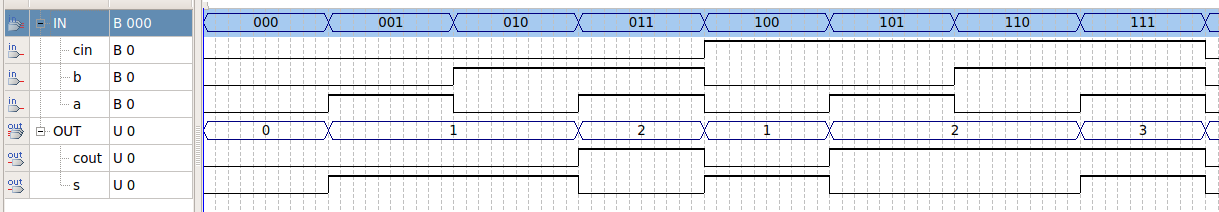

Abra o Quartus II e insira o diagrama esquemático do módulo básico do complementador de 2.

- Salve o arquivo como Complemento2.bdf na mesma pasta do PROJ2.

- Mude o Top Level para este circuito. Após isso faça a Análise e Síntese do projeto.

- Crie um simbolo para este módulo, selecionando na IDE do Quartus II o diagrama esquemático e [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK].

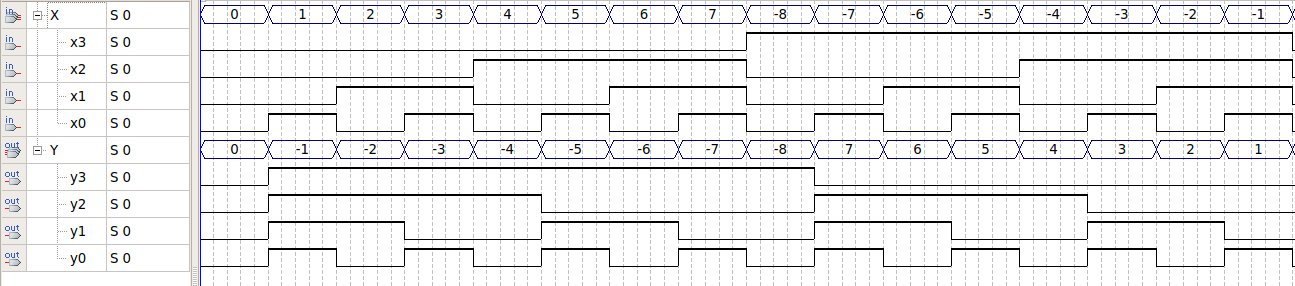

Simulação funcional com o QSIM

- Abra o editor de forma de onda do simulador QSIM (File > New > University Programa VWF).

- Defina o tempo de simulação (Edit > Set End Time ...) = 1000 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

- Gere uma forma de onda dos sinais de entrada semelhante a mostrado na figura abaixo (Use a função [Randon Value] em A e B, e salve com o nome TesteComplemento2.vwf.

- Note que os bits das entradas e saídas estão agrupados em ordem reversa e definidos como RADIX = "Decimal com sinal"

- Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK]

- Faça a simulação funcional do circuito lógico usando o sinal criado (Simulation > Run Functional Simulation)

- O resultado da simulação deve corresponder a um somador completo.

Análise dos resultados

- Analise os resultados preenchendo a tabela abaixo, e conferindo se está correto:

| Entradas | Saídas | x | Entradas | Saídas | ||

|---|---|---|---|---|---|---|

| X >= 0 | Y | OK | x | X < 0 | Y | OK |

| 0 | x | |||||

| 1 | x | -1 | ||||

| 2 | x | -2 | ||||

| 3 | x | -3 | ||||

| 4 | x | -4 | ||||

| 5 | x | -5 | ||||

| 6 | x | -6 | ||||

| 7 | x | -7 | ||||

| 8 | x | -8 | ||||