- Encontro 5 (1 mar)

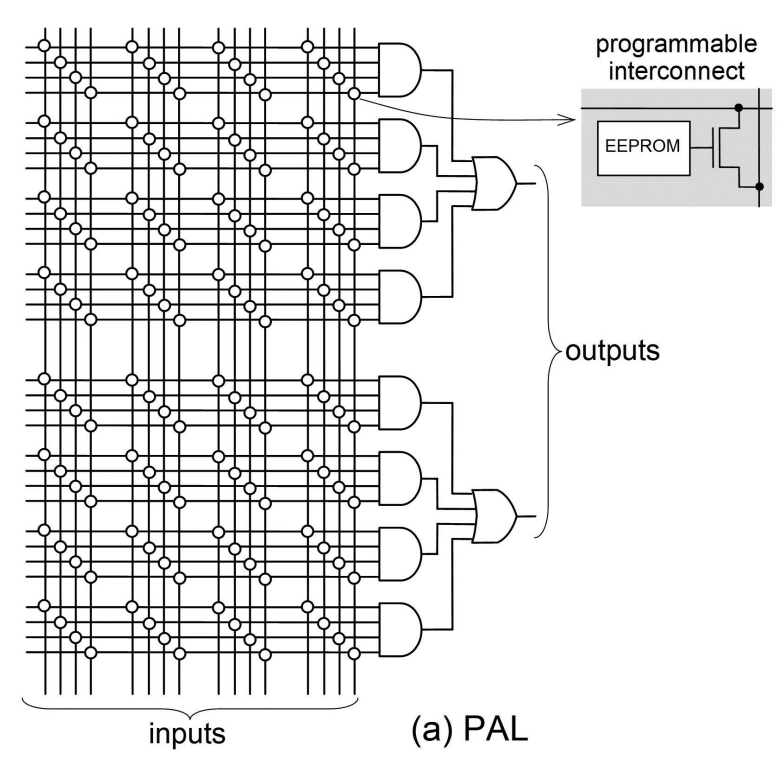

- Introdução aos dispositivos lógicos programáveis:

- Conceito, tipos de PLDs

- SPLD:

- PARA O PRÓXIMO ENCONTRO

- Encontro 6 (5 mar)

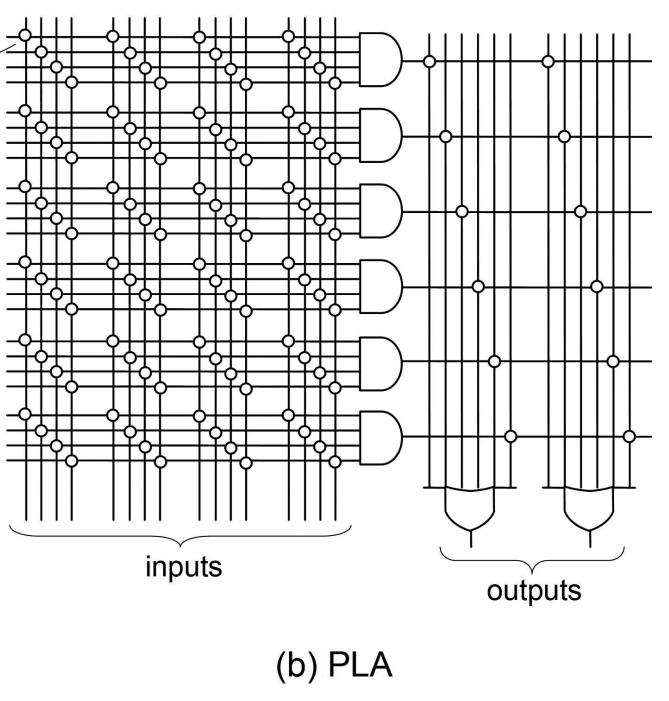

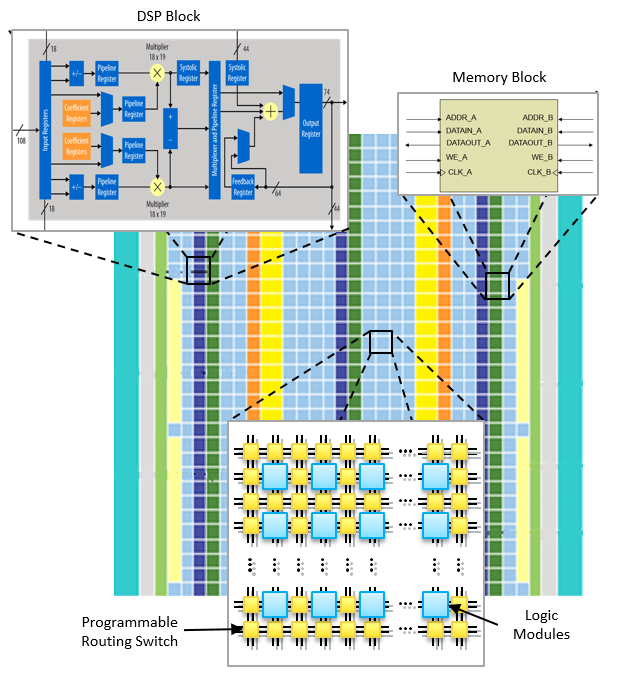

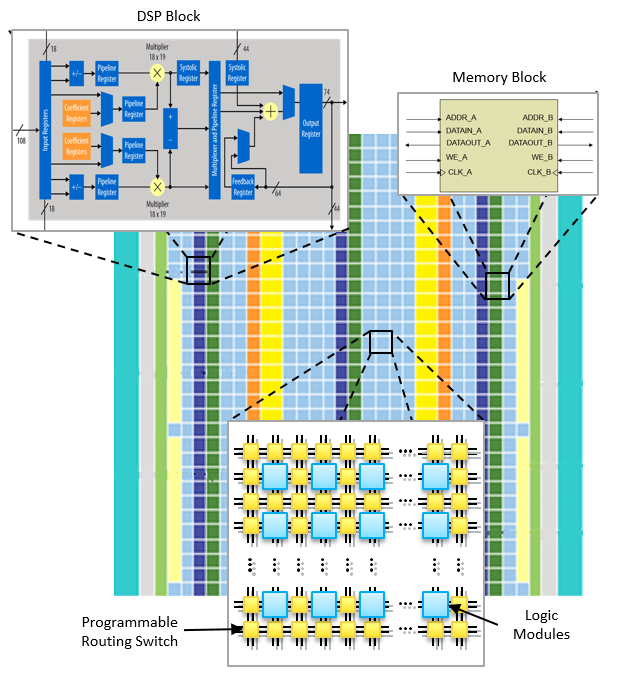

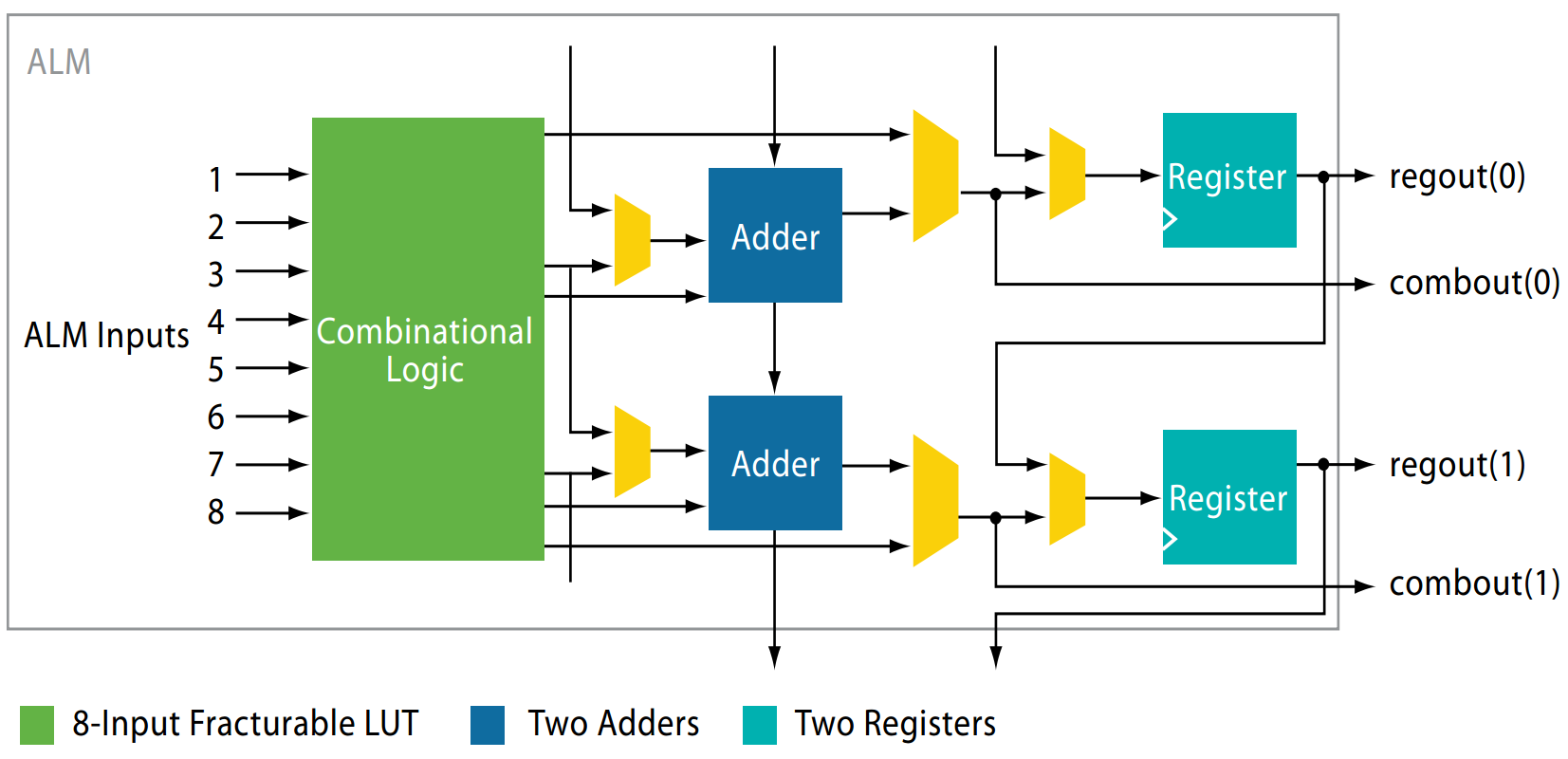

- Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, LUT, Flip_flop D, RAM, DSP, Clock, PLL, DLL, I/O

- FONTE: FPGA Architecture - ALTERA

| Exemplos de FPGA

|

Figura 2.9 - Arquitetura de um FPGA

Fonte: https://www.intel.com/content/www/us/en/docs/programmable/683176/18-1/fpga-overview-opencl-standard.html.

Fonte: https://www.intel.com/content/www/us/en/docs/programmable/683176/18-1/fpga-overview-opencl-standard.html.

Figura 2.10 - Diagrama simplificado da ALM de um FPGA Intel/Altera

Fonte: https://www.intel.com/content/www/us/en/content-details/771003/fpga-architecture-8-input-lut-legacy-white-paper.html.

Fonte: https://www.intel.com/content/www/us/en/content-details/771003/fpga-architecture-8-input-lut-legacy-white-paper.html.

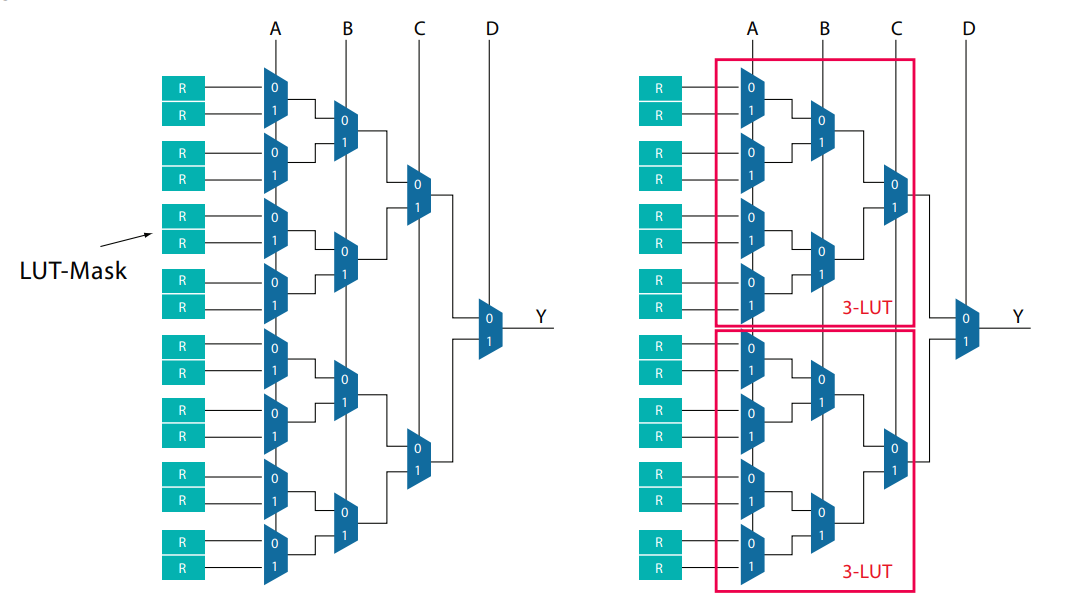

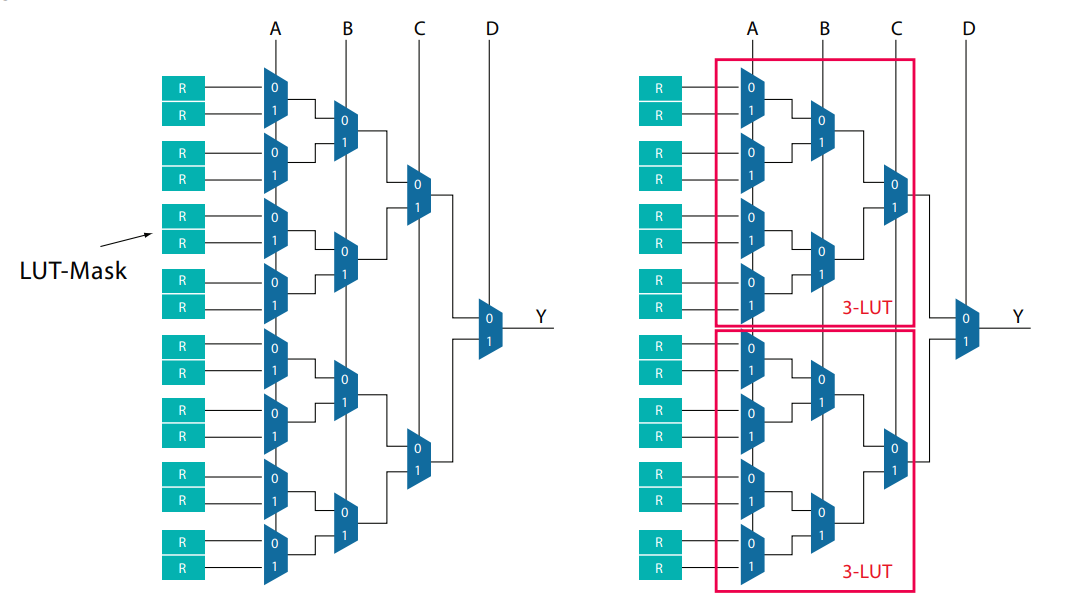

Figura 2.11 - Arquitetura interna de uma LUT

Fonte: FPGA Architecture - ALTERA.

Fonte: FPGA Architecture - ALTERA.

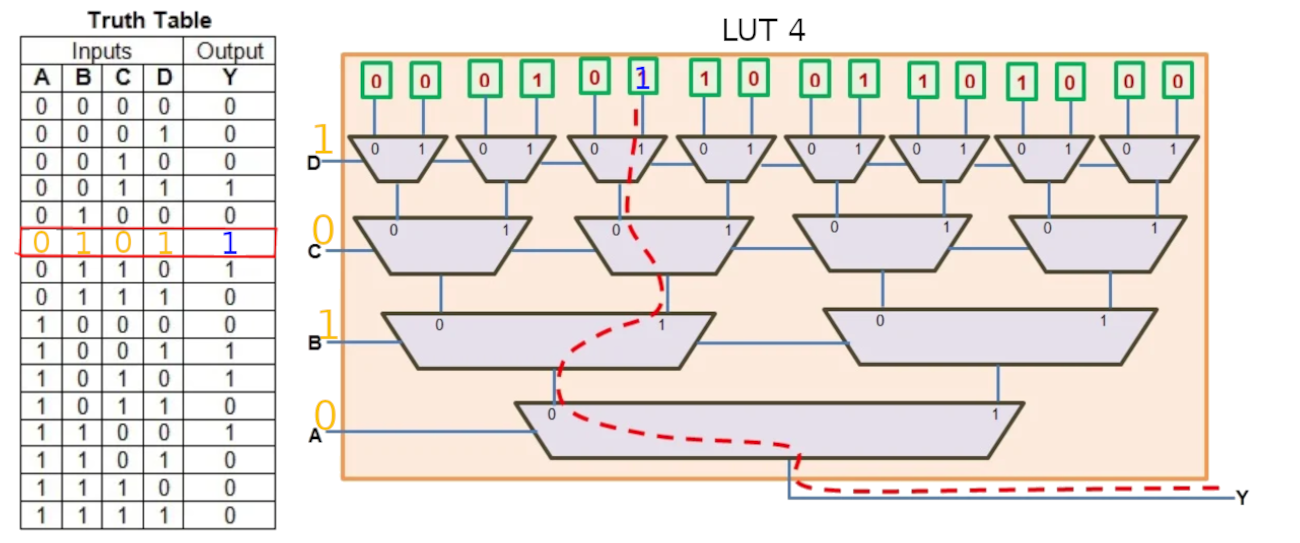

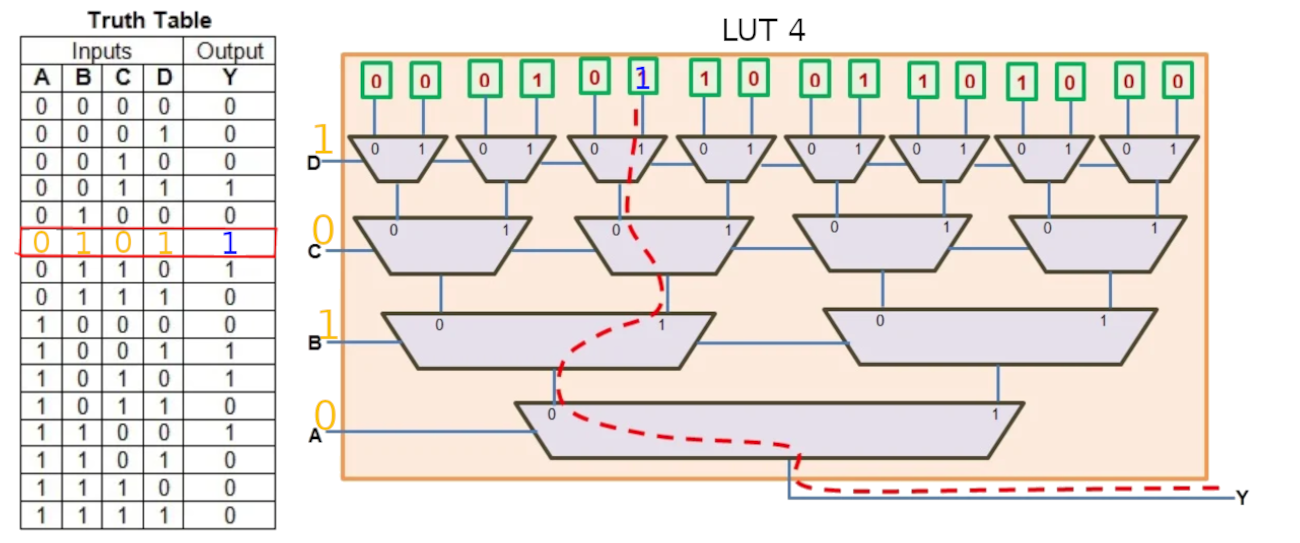

Figura 2.12 - Configuração de uma LUT

Fonte: https://www.allaboutcircuits.com/technical-articles/purpose-and-internal-functionality-of-fpga-look-up-tables/.

Fonte: https://www.allaboutcircuits.com/technical-articles/purpose-and-internal-functionality-of-fpga-look-up-tables/.

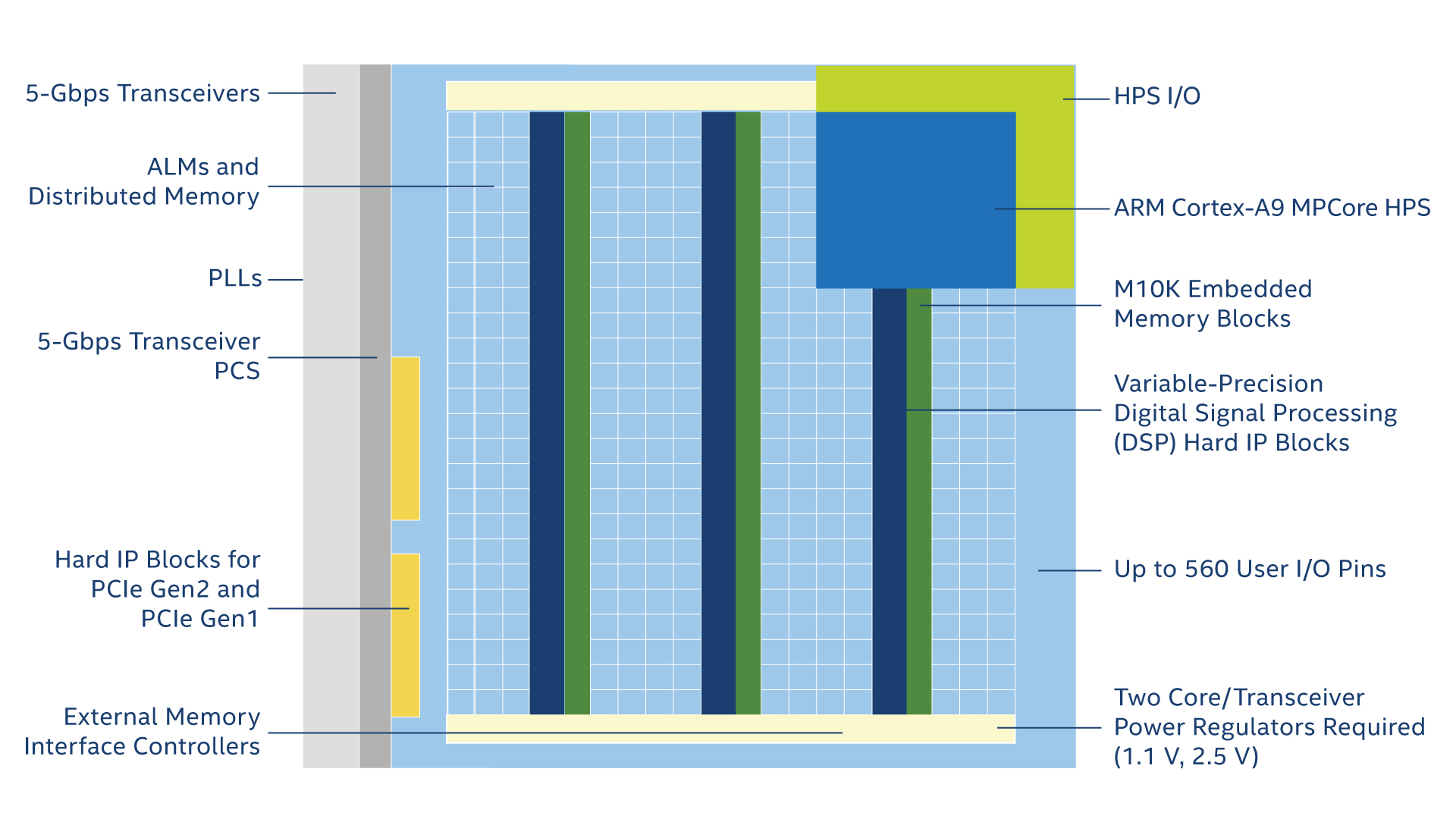

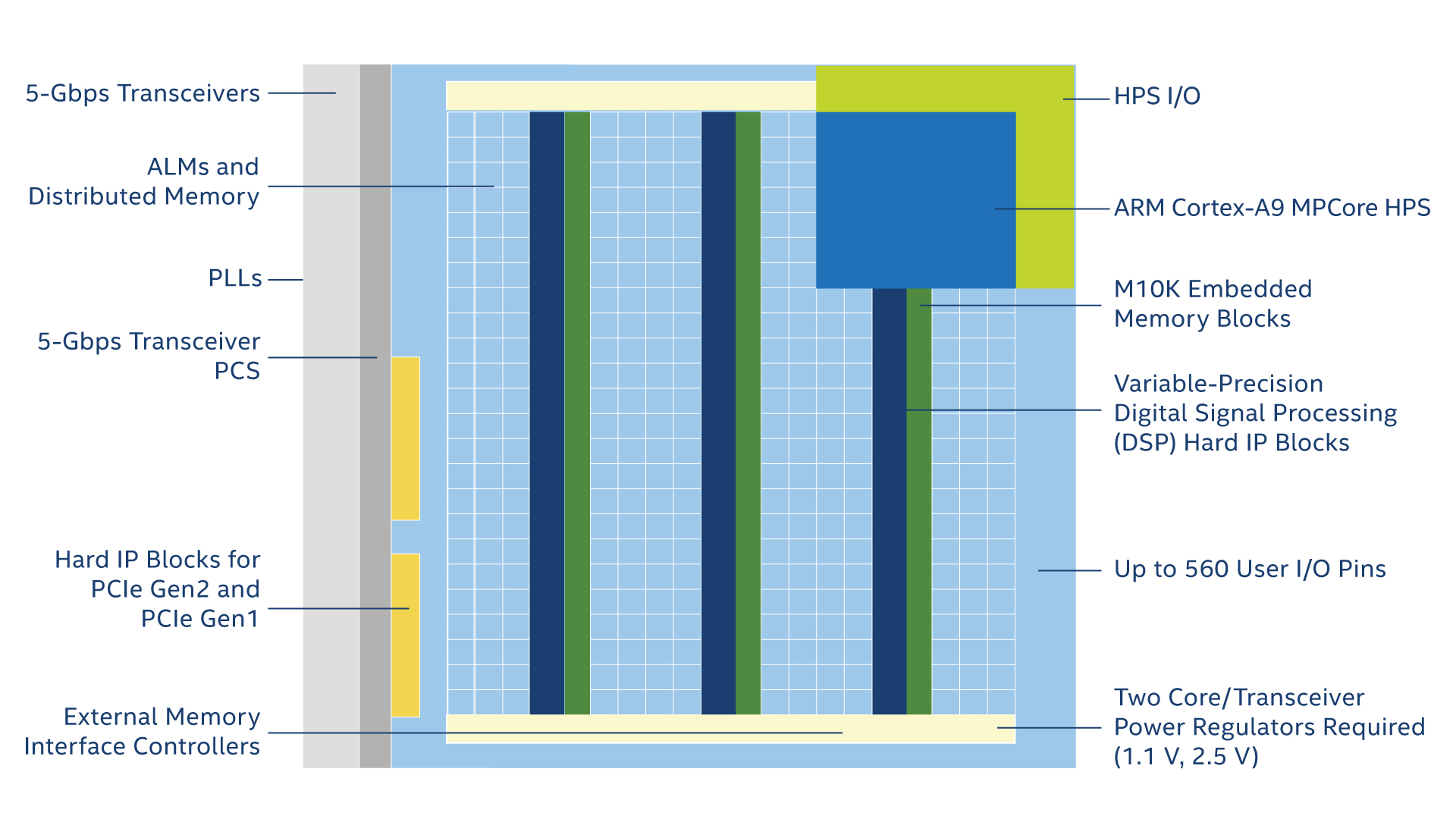

Figura 2.13 - Arquitetura do Cyclone® V Intel/Altera

Fonte: https://www.intel.com.br/content/www/br/pt/products/details/fpga/cyclone/v/article.html.

Fonte: https://www.intel.com.br/content/www/br/pt/products/details/fpga/cyclone/v/article.html.

Figura 2.14 - Leiaute de um FPGA Xilinx genérico

Fonte: https://www.sciencedirect.com/science/article/pii/B9780750678667500032.

Fonte: https://www.sciencedirect.com/science/article/pii/B9780750678667500032.

Figura 2.15 - Roteamento de sinal em um FPGA

Fonte: https://www.sciencedirect.com/science/article/pii/B9780750678667500032.

Fonte: https://www.sciencedirect.com/science/article/pii/B9780750678667500032.

Figura 2.16 - Tecnologias usadas na configuração de FPGAs

Fonte: https://www.sciencedirect.com/topics/computer-science/one-time-programmable.

Fonte: https://www.sciencedirect.com/topics/computer-science/one-time-programmable.

- Ver também SRAM, EEPROM, What Is Flash Memory

- PARA O PRÓXIMO ENCONTRO

- Leia a assista a alguns dos vídeos sobre a historia e processo de produção dos chips.

- Encontro 7 (8 mar)

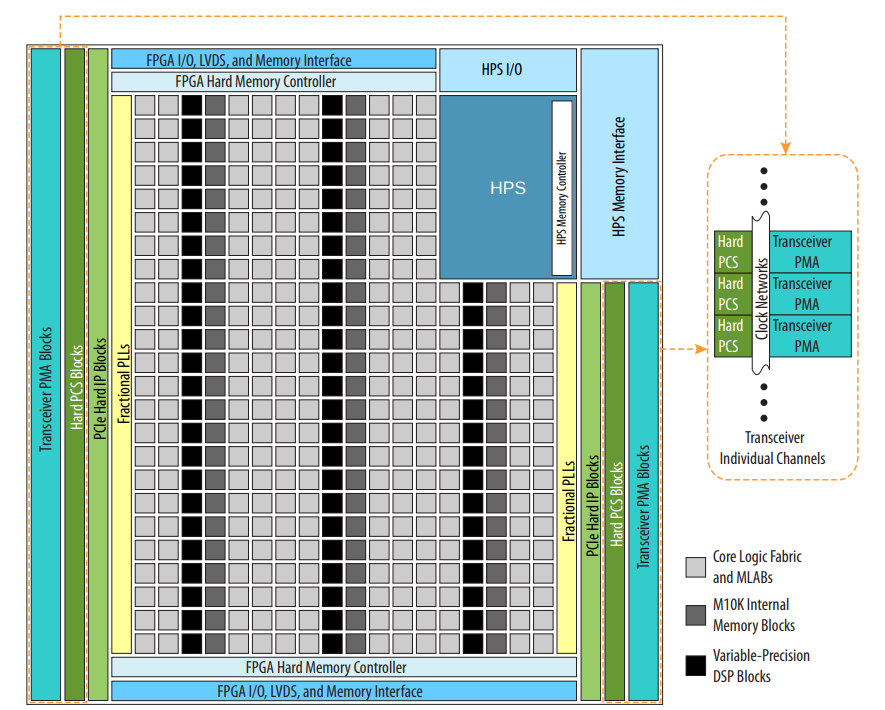

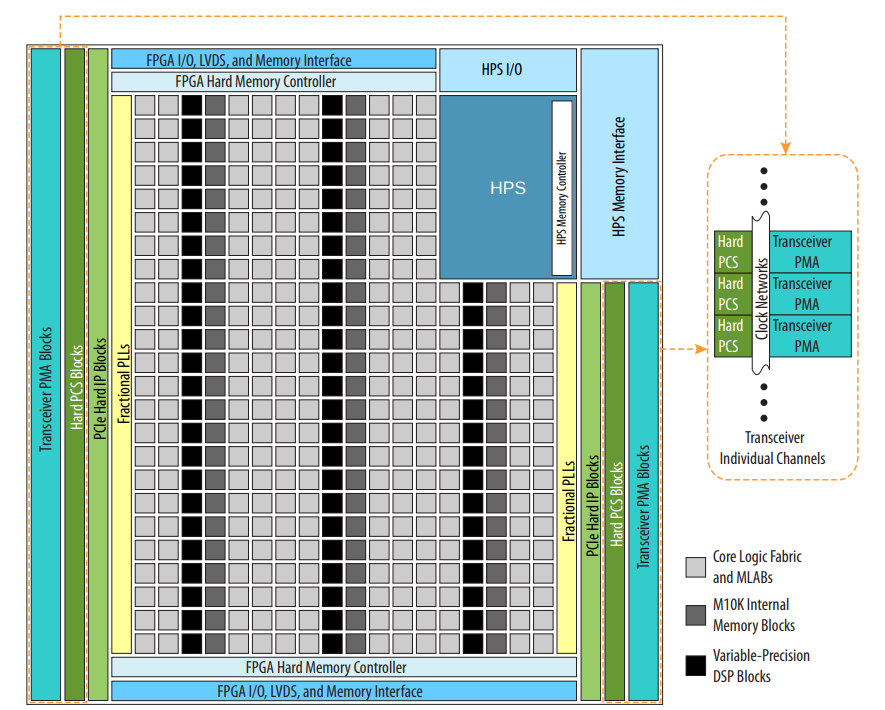

Figura 2.17 - Altera - Visão geral do dispositivo Arria V SX e ST

Fonte: https://br.mouser.com/datasheet/2/612/av_51001-1623623.pdf.

Fonte: https://br.mouser.com/datasheet/2/612/av_51001-1623623.pdf.

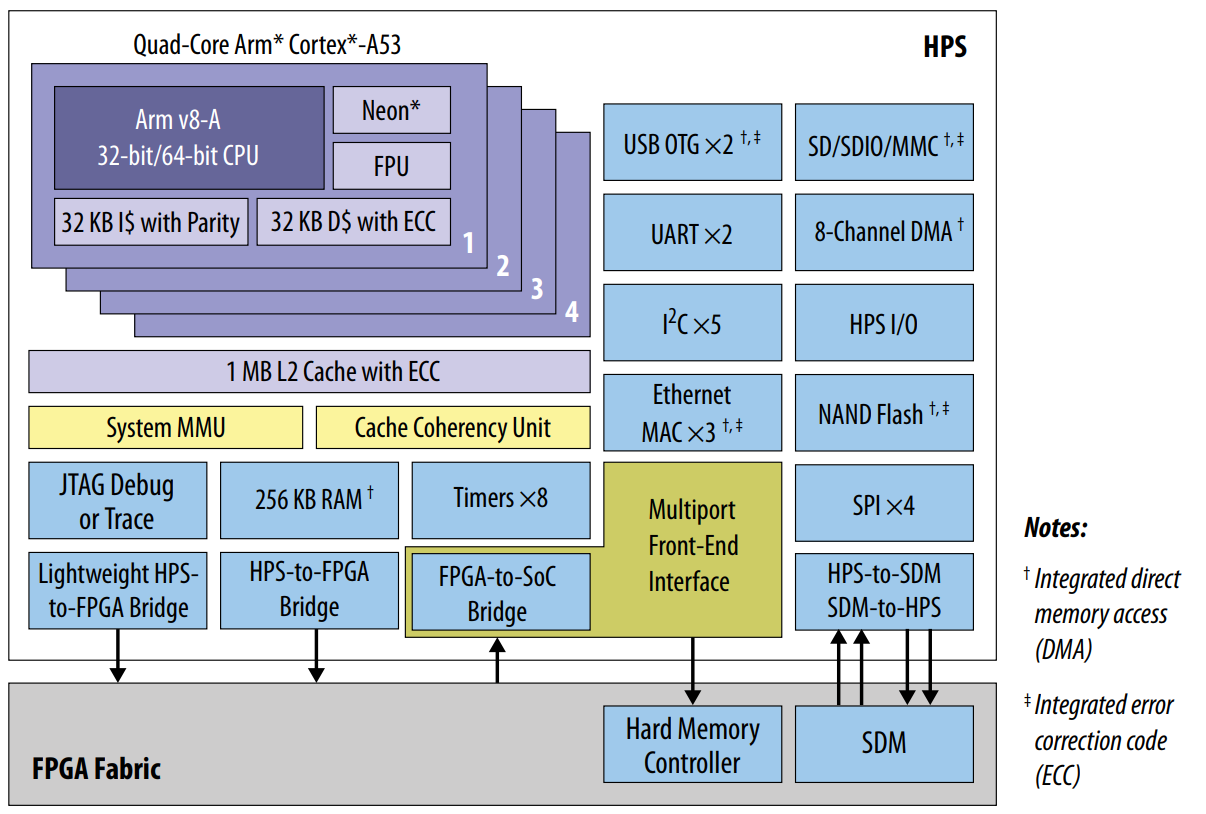

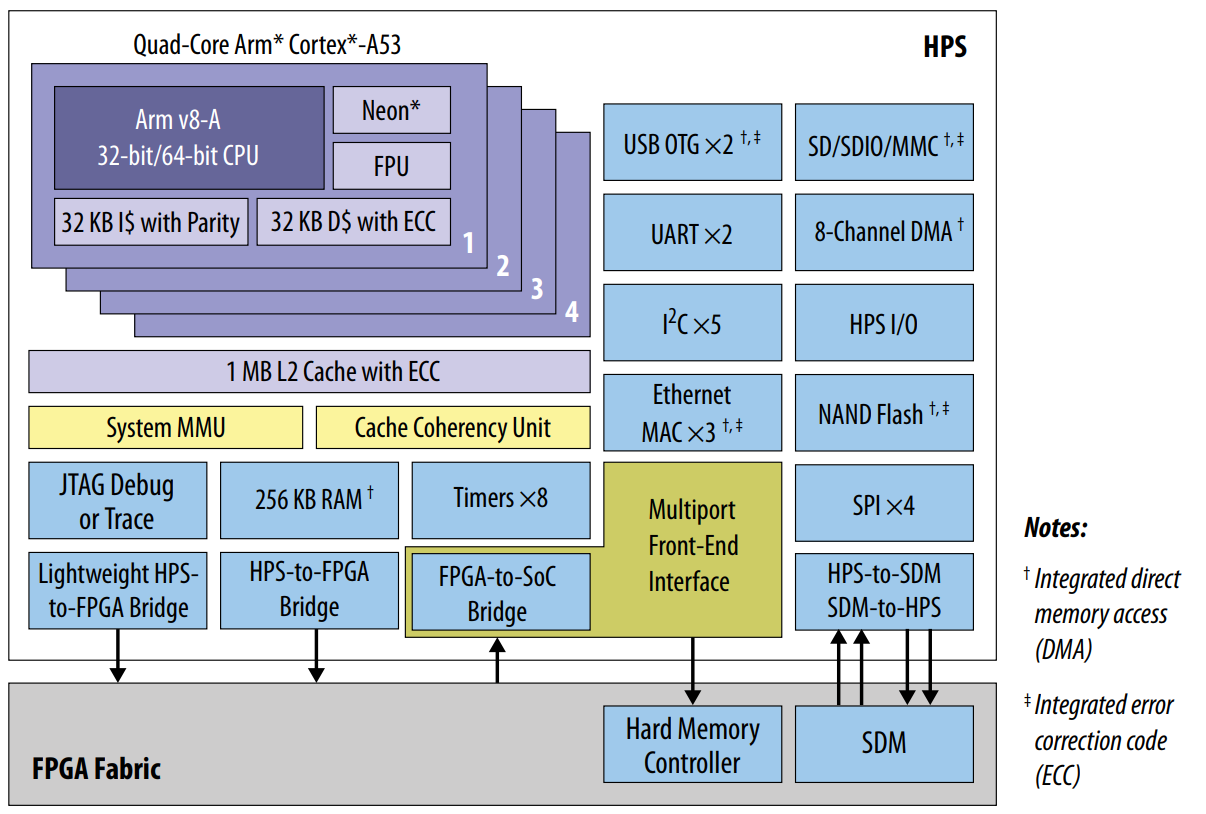

Figura 2.18 - Altera - Agilex 7 SoCs HPS Digrama de Blocos

Fonte: https://static6.arrow.com/aropdfconversion/b568cfe009abfed6a28eff56700189883d7fc179/ag-overview-683458-666707.pdf.

Fonte: https://static6.arrow.com/aropdfconversion/b568cfe009abfed6a28eff56700189883d7fc179/ag-overview-683458-666707.pdf.

- PARA O PRÓXIMO ENCONTRO

-

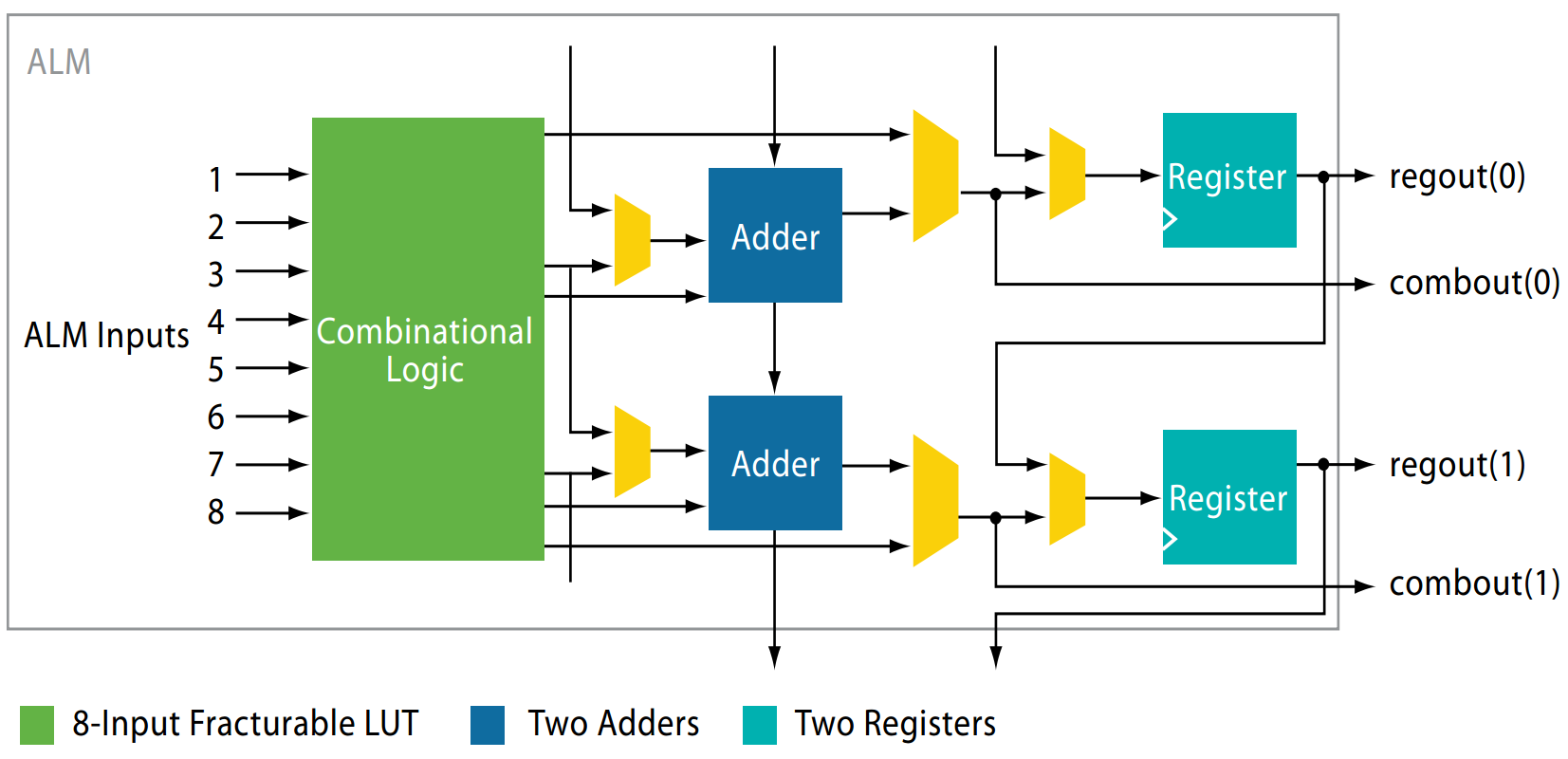

- Fabricantes de DLPs/FPGAs e familias de DLPs atuais.

- ALTERA/INTEL - Stratix, Arria, Cyclone, Max, Agilex

- Xilinx/AMD - Virtex, Kintex, Artix, Zynq (SoC)

- Microchip - Igloo, PolarFire

- Lattice - ECP, iCE, Mach

|

Unidade 3 - Circuitos sequenciais (Implementação com HDL)

| Unidade 3 - Circuitos sequenciais (Implementação com HDL)

|

- Encontro 8 (12 mar)

- Flip-Flop e circuitos sequenciais.

- Diferenças entre código concorrente e sequencial <=> circuitos combinacional e sequencial

- Diferenças entre os objetos SIGNAL e VARIABLE

- Tipos de elementos de memória: Latch x Flip-flop

- Latch D

- Flip-flop tipo D com reset assíncrono e com reset (clear) síncrono

- Seção de código sequencial PROCESS: lista de sensibilidade

[rótulo:] PROCESS [(lista_de_sensibilidade)] [IS]

[parte_declarativa]

BEGIN

afirmação_sequencial;

afirmação_sequencial;

...

END PROCESS [rótulo];

[rótulo:] IF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSIF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSE

afirmação_sequencial;

afirmação_sequencial;

...

END IF [rótulo];

-

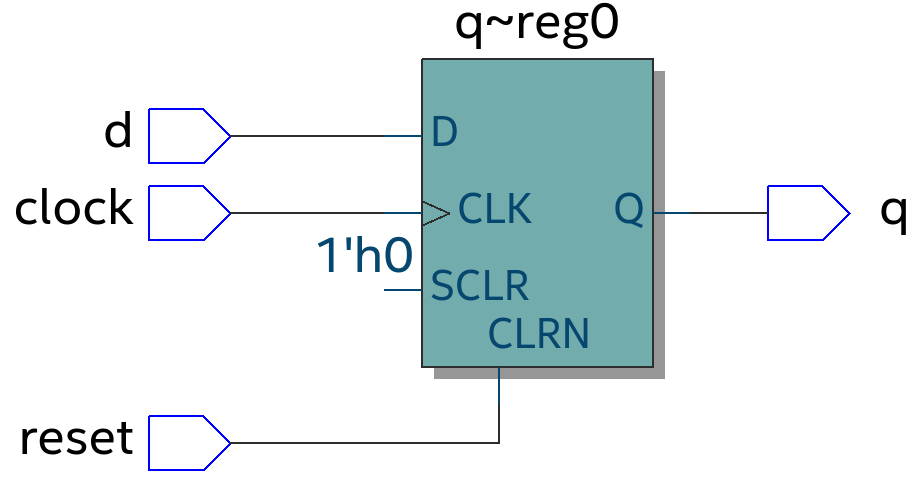

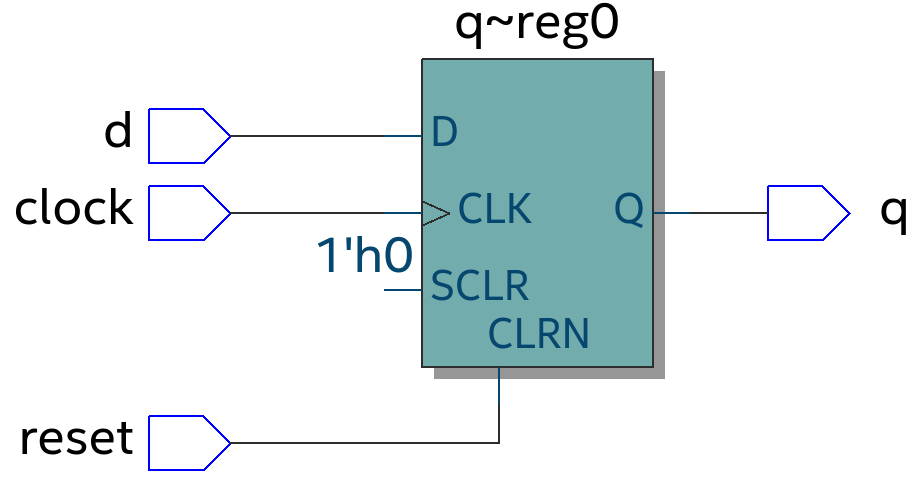

- DFFs com Reset Assincrono e Reset Sincrono, com Enable, com Preset (Variação Ex 6.1).

--Flip Flop tipo D com reset assincrono, sensivel a borda de subida.

process (clock,reset)

begin

if (reset = '1') then

q <= '0';

-- elsif (clock'event and clock = '1') then or

elsif (rising_edge(clock)) then

q <= d;

end if;

end process;

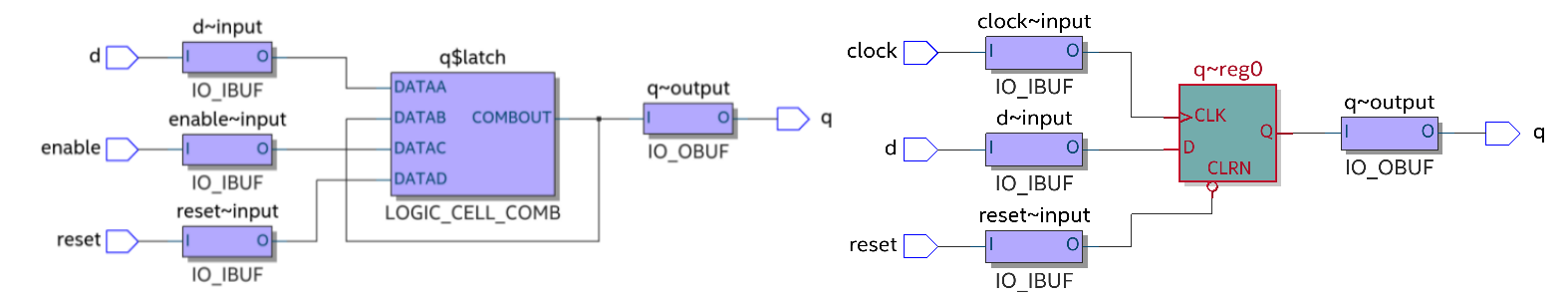

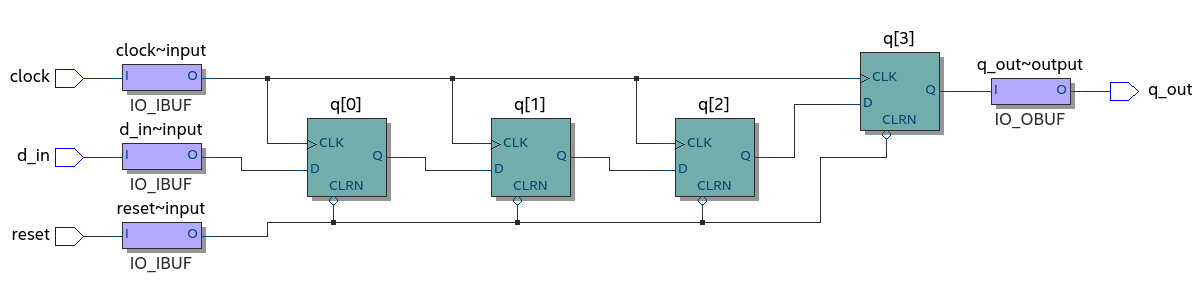

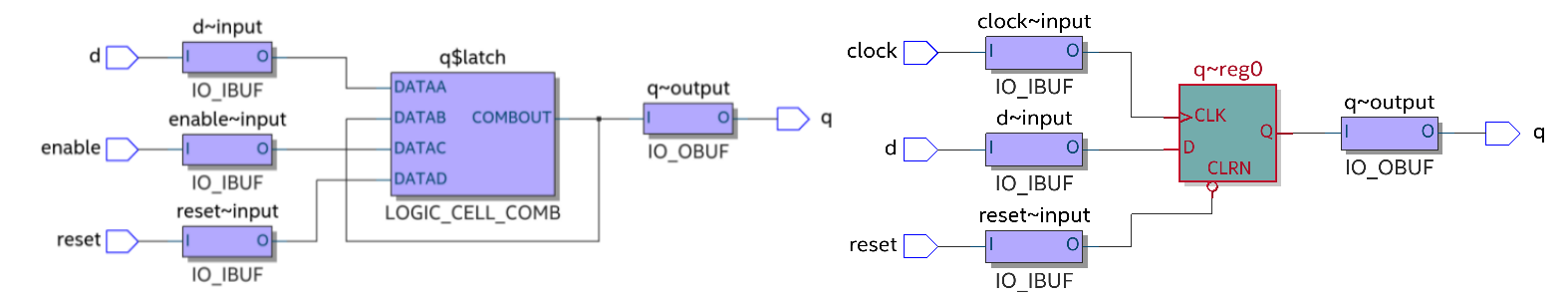

Figura 5.1 - RTL de Flip-flop D de borda de subida, com reset assíncrono

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

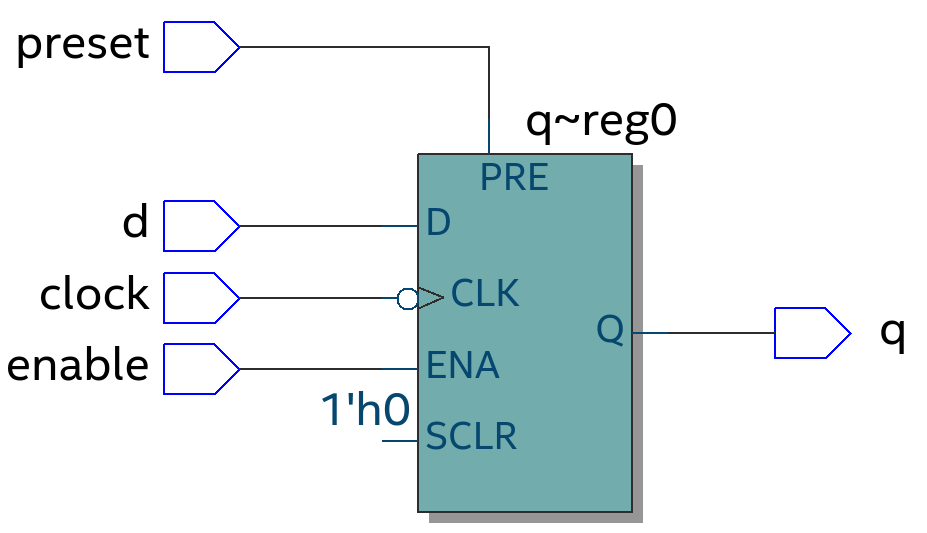

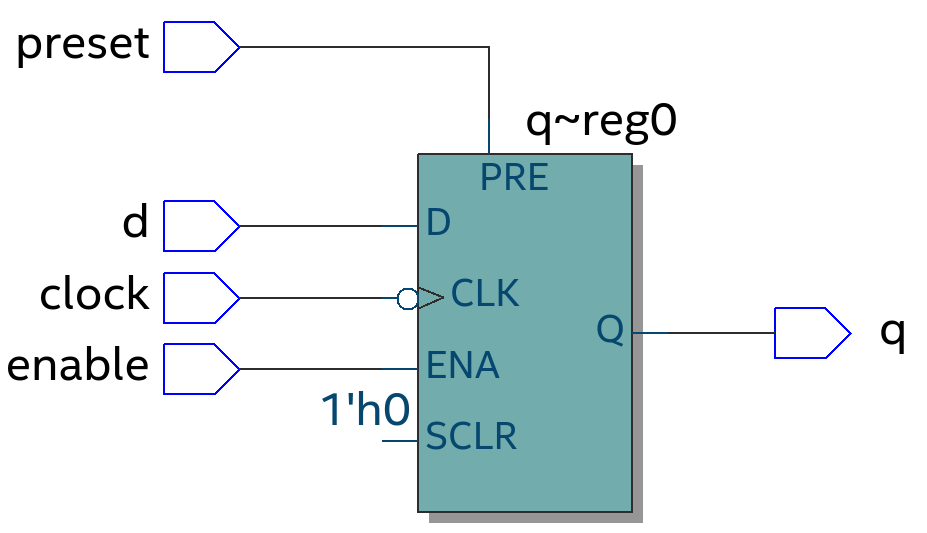

--Flip Flop tipo D com preset assincrono e sinal de enable, sensivel a borda de descida.

process (clock, preset)

begin

if (preset = '1') then

q <= '1';

elsif (falling_edge(clock)) then

if (enable = '1') then

q <= d;

end if;

end if;

end process;

Figura 5.2 - RTL de Flip-flop D de borda de descida, com preset assíncrono e enable

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Encontro 9 (15 mar)

-

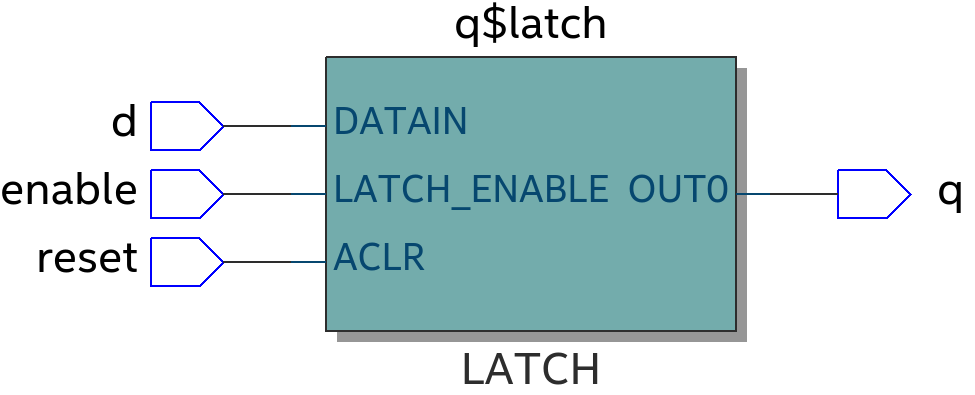

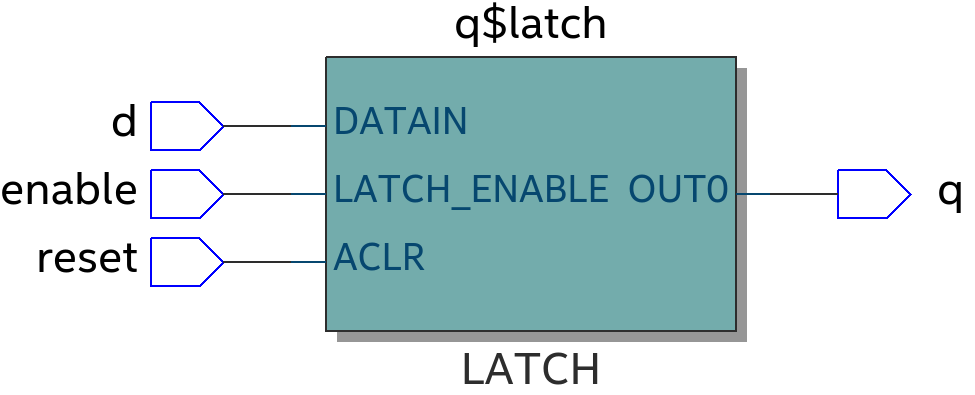

- Comparar com Latch (sem clk'event).

--Latch tipo D com reset assincrono.

process (enable, reset, d)

begin

if (reset = '1') then

q <= '0';

elsif (enable='1')) then

q <= d;

end if;

end process;

Figura 5.3 - RTL de Latch D de com reset assíncrono e enable ativo alto

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Na figura abaixo, note que o Latch é implementado utilizando a LUT do elemento lógico do FPGA, enquanto que o Flip-flop utiliza o componente já disponível neste elemento lógico.

- Evite os latches no projeto

Figura 5.4 - Comparação do Technology Map de um Latch_D (esquerda) com FF_D (direita)

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

-- Flip Flop tipo D com reset síncrono sensível a borda de subida.

-- Modifique a descrição para que o reset_ass seja assíncrono e reset_sinc seja síncrono.

-- Note que a função rising_edge(clock) é equivalente a (clock'event and clock'last_value = '0' and clock = '1'))

process (clock, reset)

begin

if (reset = '1') then

q <= '0';

elsif (clock'event and clock'last_value = '0' and clock = '1')) then

q <= d;

end if;

end process;

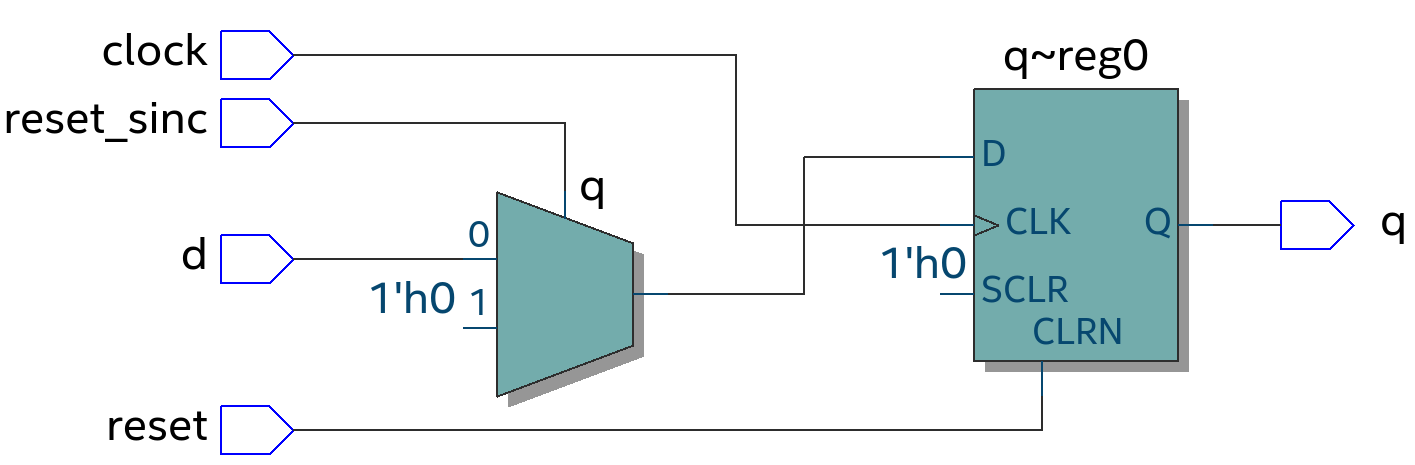

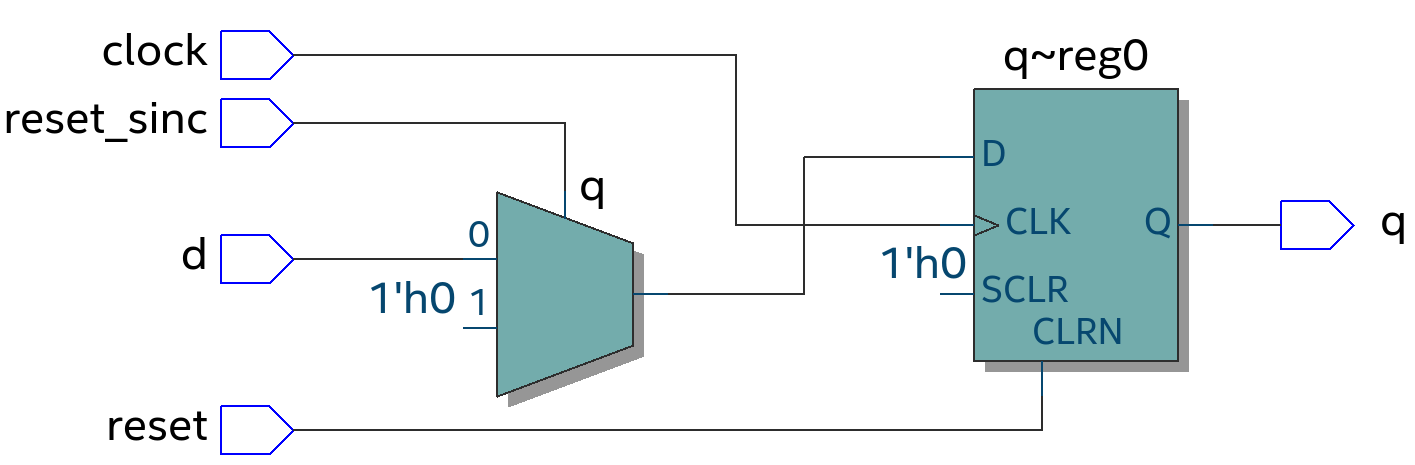

Figura 5.5 - RTL do Flip-flop D com reset assíncrono e reset síncrono

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

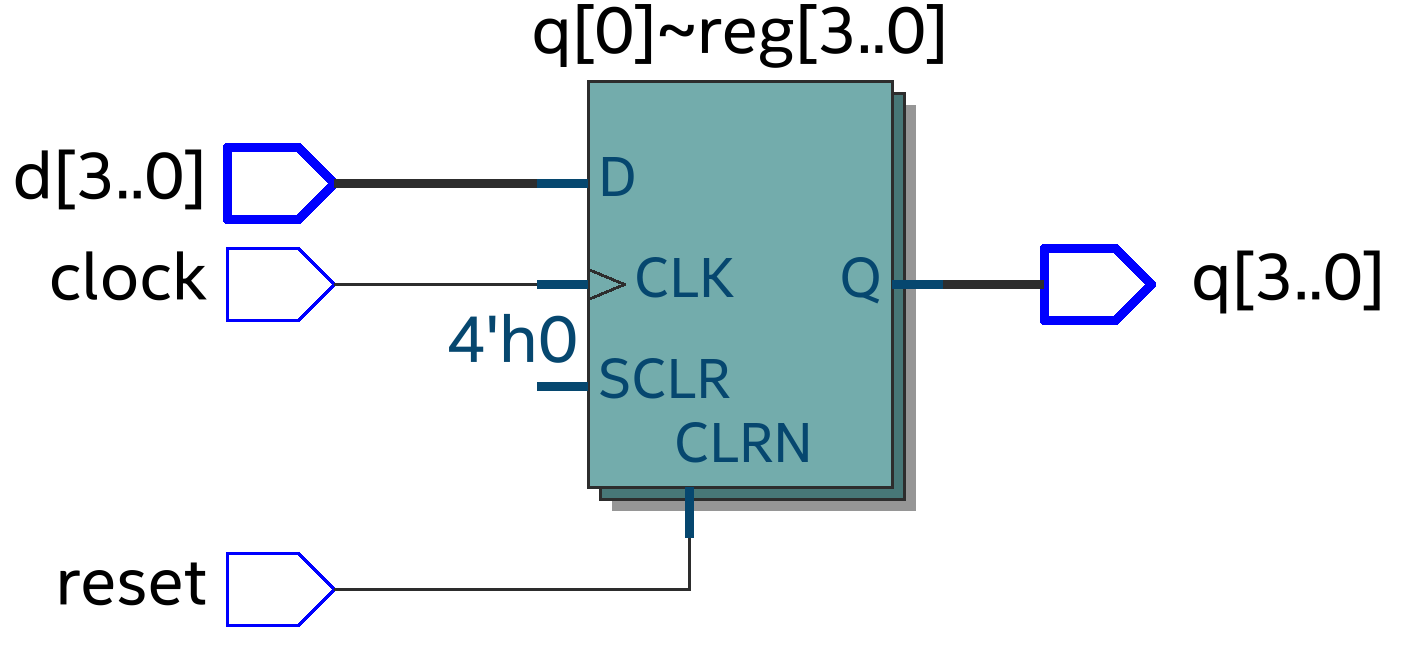

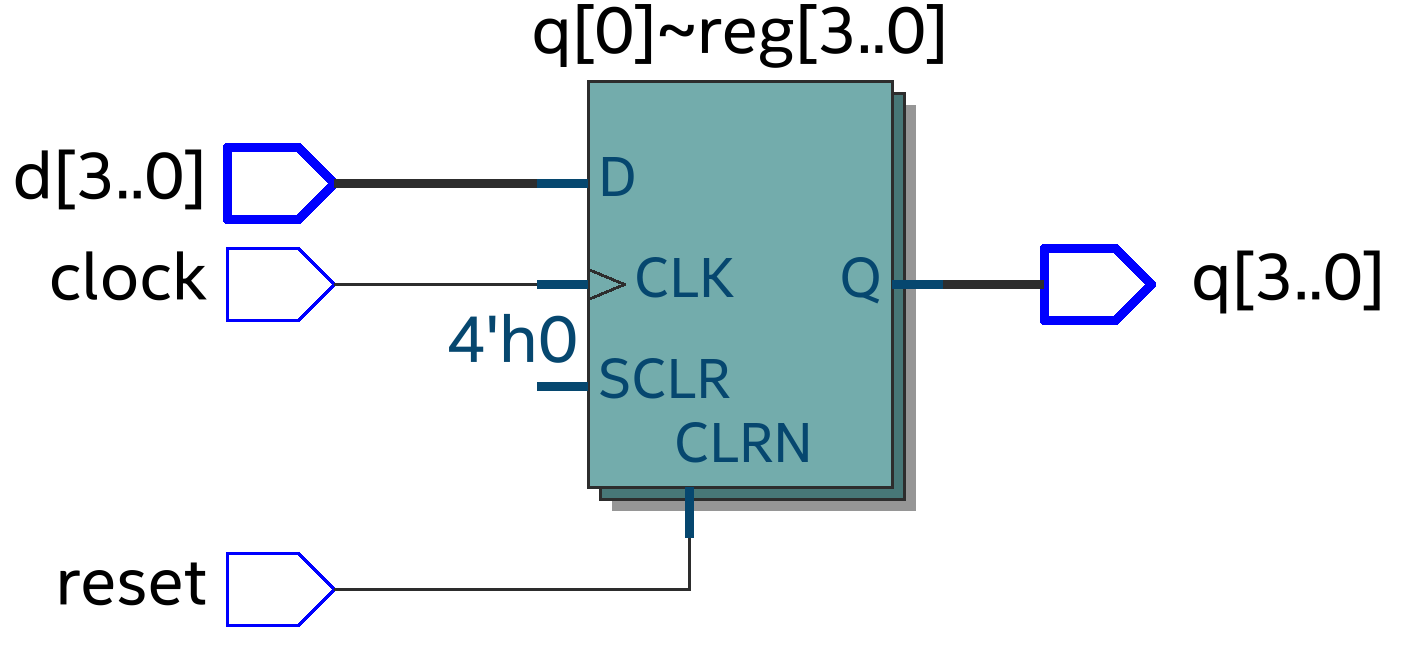

- Exercício: Implemente um registrador com N FF_D no lugar de um único FF_D.

Figura 5.6 - RTL do Registrador (de 4 bits) com reset assíncrono

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

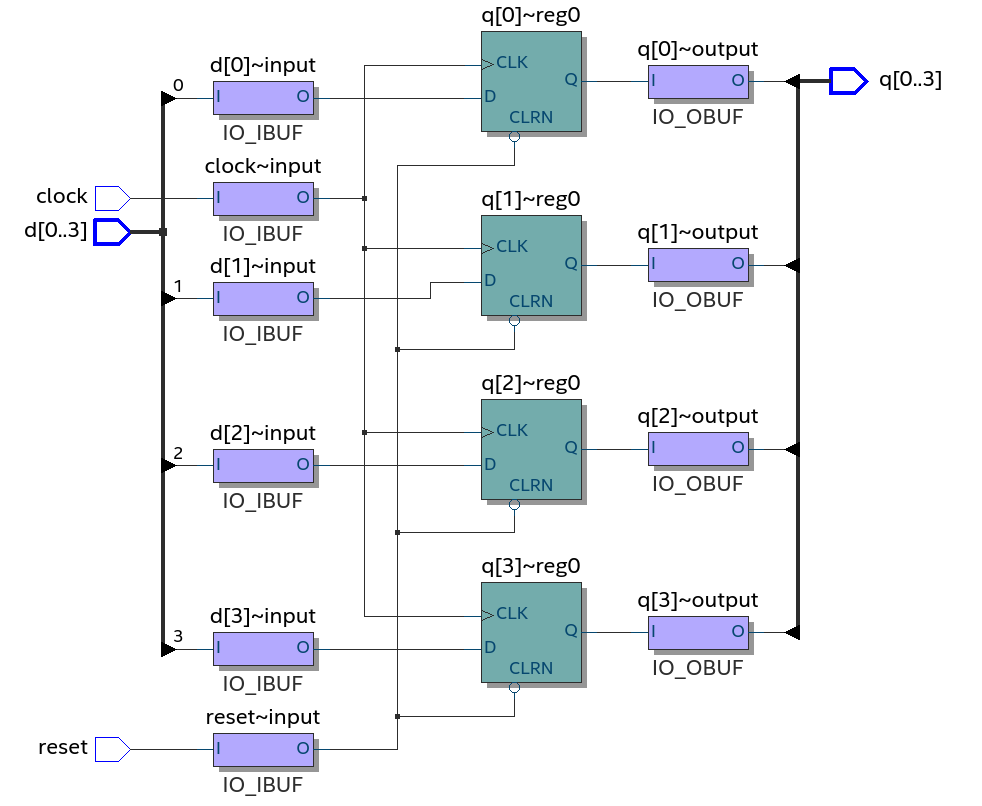

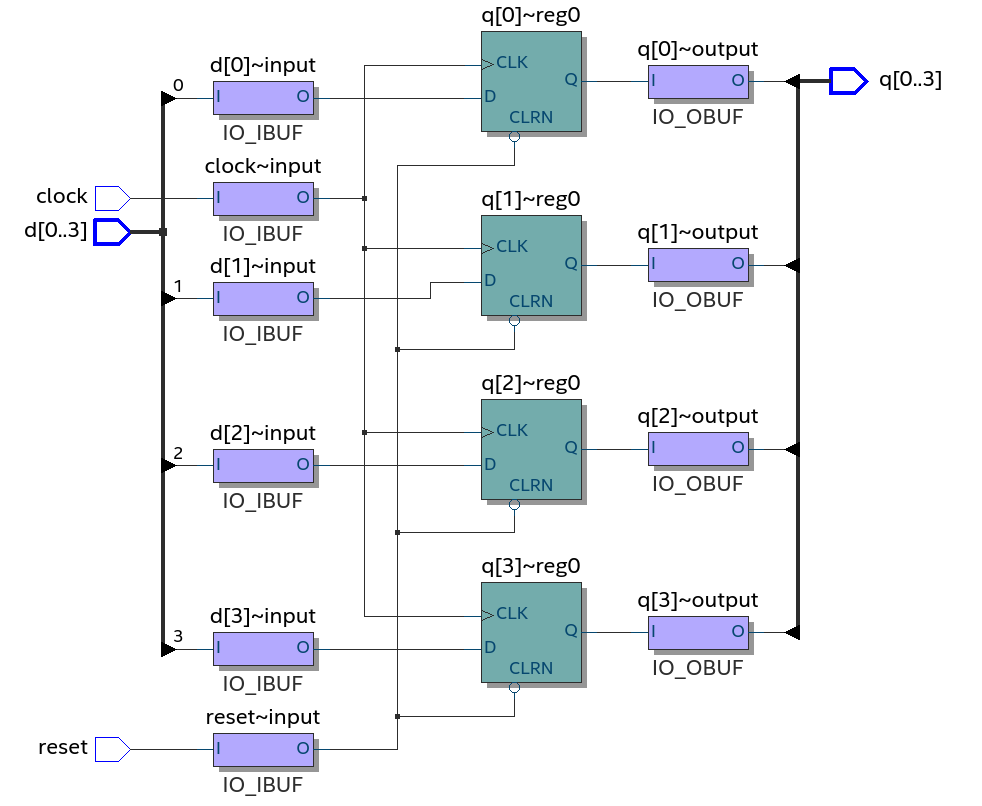

Figura 5.7 - Techonogy Map do Registrador (de 4 bits) com reset assíncrono

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Faça a simulação funcional do DFFs e do Latch

- Encontro 10 (22 mar)

- Implementar um registrador com N FF_D usando a instrução FOR GENERATE.

-- Instrução concorrente FOR GENERATE.

-- Note que neste caso o '''label''' é obrigatório

label: FOR identificador IN faixa GENERATE

[Parte_Declarativa

BEGIN]

Instruções_concorrentes

...

END GENERATE [label];

- Implementar um registrador de deslocamento de N bits.

entity shift_reg is

generic ( N : natural := 4);

port (

clock, reset : in std_LOGIC ;

d_in: in std_LOGIC;

q_out : out std_LOGIC);

end entity;

architecture ifsc_v1 of shift_reg is

signal d: std_logic_vector(N-1 downto 0);

signal q: std_logic_vector(N-1 downto 0);

begin

...

end architecture;

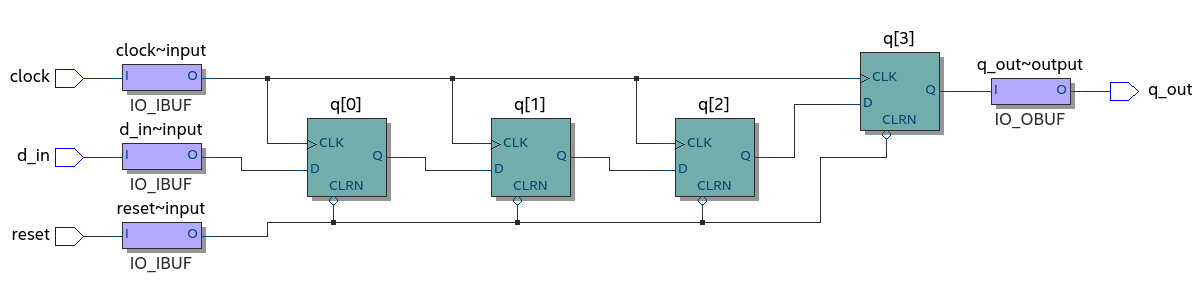

Figura 5.8 - Technology Map de Shift Register

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

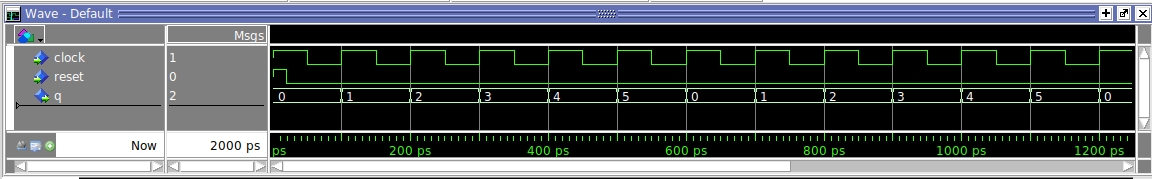

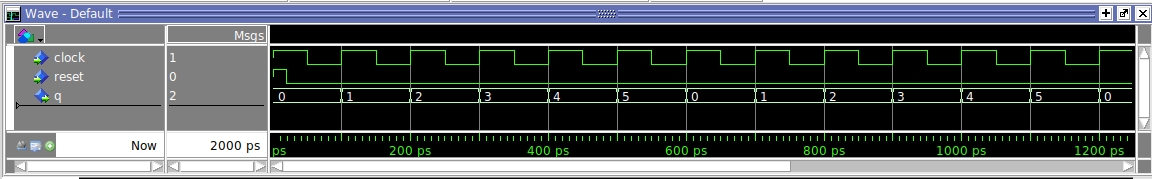

Figura 5.9 - Simulação de Shift Register

800 px

Fonte: Elaborado pelo autor.

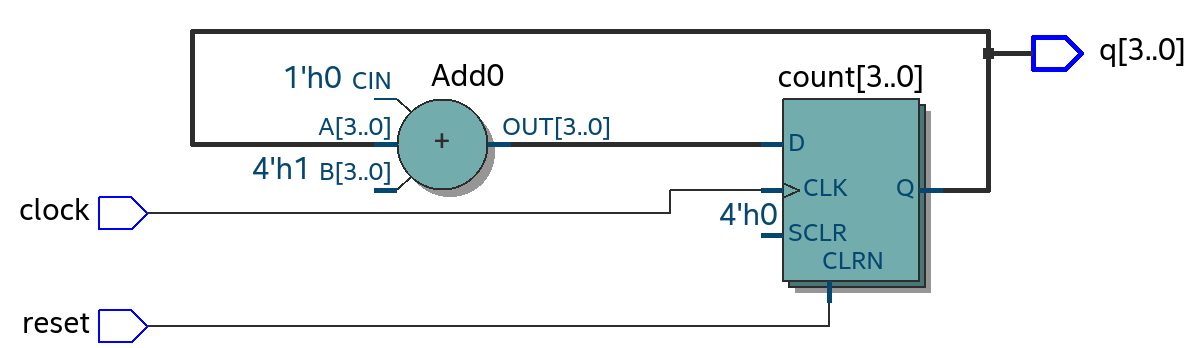

- Implementar um contador crescente 0-N (baseado no Ex.6.2), com N = 2^Mbits-1 (1 3 7 15)

- Com overflow no valor máximo

entity conta_0_N is

generic (MAX : natural := 15);

port (clock, reset: in std_logic; q : out integer range 0 to MAX);

end entity;

architecture ifsc_v1 of conta_0_N is

begin

process (clock,reset)

variable count : integer range 0 to MAX;

begin

if (reset = '1') then

count := 0;

elsif (rising_edge(clock)) then

count := count + 1;

end if;

q <= count;

end process;

end architecture;

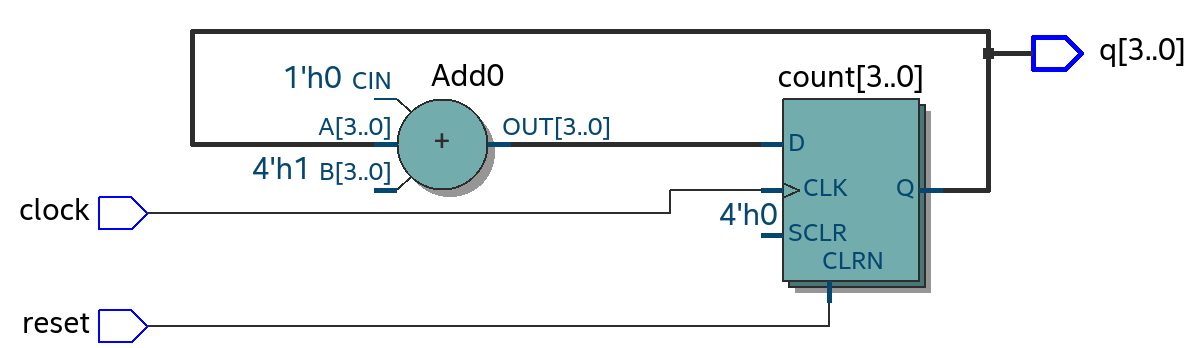

Figura 5.10 - RTL de contador crescente

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

ATUAL

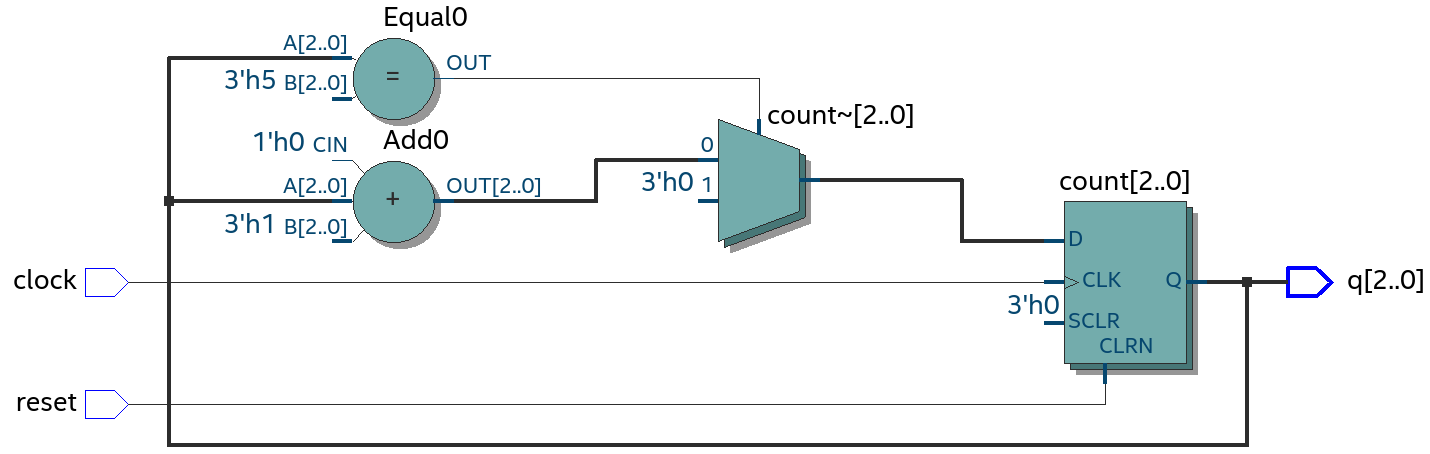

- Encontro 11 (26 mar)

- Implementar um contador crescente 0 até N, com N ≠ 2^Mbits (5, 10)

- Com overflow no valor máximo

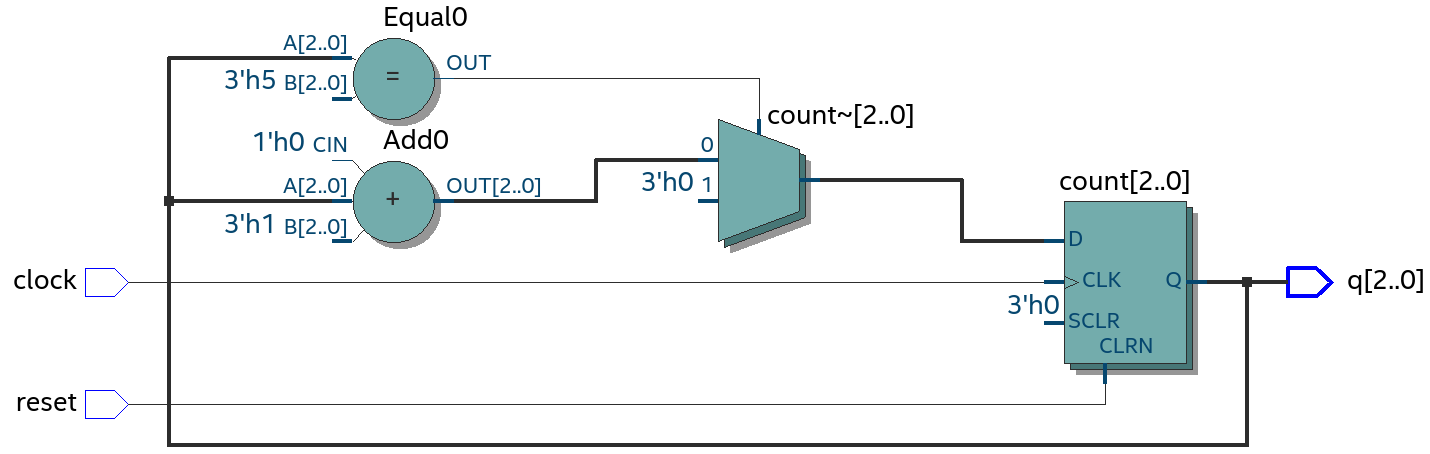

Figura 5.11 - RTL contador crescente 0 a 5

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

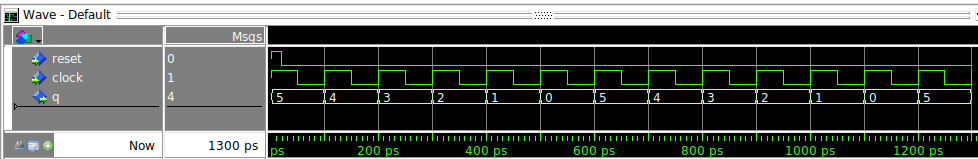

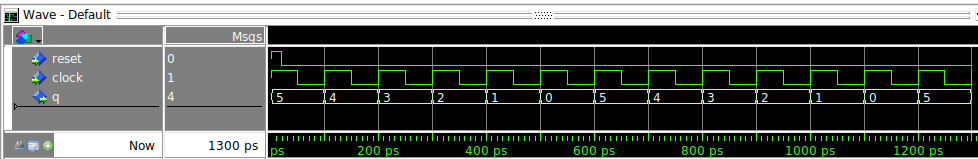

Figura 5.12 - Simulação do contador crescente 0 a 5

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Com parada no valor máximo

- Implementar um contador decrescente N até 0, com N ≠ 2^Mbits (5, 10)

- Com underflow no valor mínimo

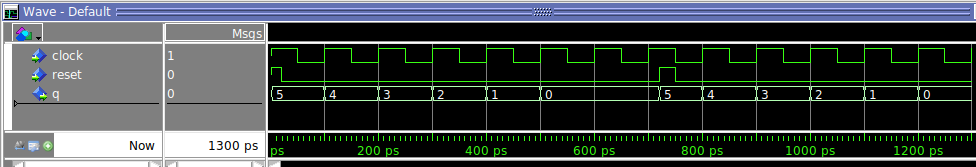

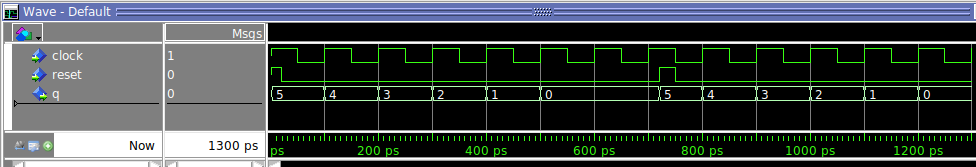

Figura 5.13 - Simulação do contador decrescente 5 a 0

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura 5.14 - Simulação do contador decrescente 5 a 0 com parada

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Com parada no valor mínimo

- DESAFIO

- Implementar um contador bidirecional entre MIN e MAX. Uma entrada DIR indica a direção da contagem. Considere DIR = 0 (crescente) e DIR = 1 (decrescente).

- Versão 1: Com underflow no valor mínimo (MIN) e overflow no máximo (MAX).

- Versão 2: Com parada no valor mínimo (MIN), se decrescente e também no máximo (MAX) se crescente.

|

Avaliações

Durante o semestre serão realizadas 4 avaliações. As avaliações devem ser enviadas pela plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - :

- A2 - :

- A3 - :

- A4 - :

- R - Recuperação de A1 a A4 :

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN.

A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN. Para os BÔNUS só serão considerados projetos entregues no prazo.

AE1 - Conhecendo os dispositivos lógicos programáveis

| AE1 - Conhecendo os dispositivos lógicos programáveis

|

- Objetivos

- Conhecer o Quartus Prime e as características dos dispositivos lógicos programáveis

- Analisar os tempos de propagação em um circuito combinacional

- Alterar configurações do compilador

- Fazer a simulação funcional e temporal de um circuito combinacional.

- Atividades

- Ao escolher a família de FPGAS, escolha inicialmente um dispositivo da família Max II. Anote o código desse dispositivo.

- Capture as telas solicitadas e depois utilize-as no relatório da atividade.

- Anote o tempo utilizado para cada uma das etapas do processo de compilação.

- Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo.

- Anote algum erro (Error) ou alertas (Warnings) que o Quartus II indicar no painel de mensagens [Messages]

- Ao final salve o projeto em um arquivo QAR (sugestão PJ1.QAR)

- Observe as mudanças que ocorrem tanto no tipo de Elemento Lógico disponível, no Chip Planner, no Pin Planner, e no circuito dos pinos de I/O. Note que estes FPGAs também apresenta novos componentes, tais como: Memória, Multiplicadores, DSP, PLL, DLL, etc. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documente aqueles que encontrar.

- Compare os resultados obtidos nos procedimentos do PASSO 1 e PASSO 2.

- Ao escolher a família de FPGAS, escolha um dispositivo FPGA da família Cyclone IV E. Anote o código desse dispositivo.

- Capture as telas mostradas no roteiro e depois utilize-as no relatório da atividade.

- Anote o máximo tempo de propagação entre entrada e saída.

- Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo.

- Experimente modificar as configurações do compilador, conforme mostrado em Configurando o compilador. Se desejar mude a semente inicial trocando o valor de [Seed: 1]

- Experimente inserir diferentes restrições de atraso máximo para o compilador, e analise o resultado obtido.

- Anote algum erro (Error) ou alertas (Warnings) que o Quartus II indicar no painel de mensagens [Messages]

- Ao final salve o projeto em um arquivo QAR (sugestão PJ2.QAR)

- PASSO 4: Realize a simulação funcional de um dos projetos CI74161 ou do cálculo da distância de Hamming

- Capture as telas que mostram o circuito funcionando e depois utilize-as no relatório da atividade.

- Entregas

- Envie um arquivo QAR contendo todos os arquivos necessário para compilar cada um dos projetos.

- Envie um relatório em PDF, incluindo as imagens capturadas (inclua um título para cada figura) e escreva para cada imagem um texto comentando o que representa. O relatório também deve ter a identificação (autor, título, data) uma breve introdução e uma conclusão. A descrição dos procedimentos feita na página wiki não precisa incluída no relatório.

- Use preferencialmente o Overleaf para gerar o relatório. Mas o uso de MS-Word, Libreoffice e Google Docs também é permitida.

- A entrega será feita através do Moodle da disciplina. Observe o prazo de entrega.

|

Referências Bibliográficas:

- ↑ Erro de citação: Marca

<ref> inválida;

não foi fornecido texto para as refs chamadas PEDRONI2010b

Curso de Engenharia de Telecomunicações

|