DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke

Revisão de 22h33min de 25 de julho de 2023 por Moecke (discussão | contribs) (→Unidade 6 - Projeto a nível de Sistema)

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 6 ENCONTROS

| Unidade 1 - Introdução a disciplina | ||

|---|---|---|

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 10 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

- 10 ENCONTROS

| Unidade 3 - Tipos de Dados e Operadores em VHDL |

|---|

Unidade 4 - Código Concorrente

- 4 ENCONTROS

| Unidade 4 - Código Concorrente |

|---|

Unidade 5 - Código Sequencial

- 7 ENCONTROS

| Unidade 5 - Código Sequencial |

|---|

Unidade 6 - Projeto a nível de Sistema

- 3 ENCONTROS

| Unidade 6 - Projeto a nível de Sistema |

|---|

Unidade 7 - Maquinas de Estado Finitas

- 2 AULAS

| Unidade 7 - Maquinas de Estado Finitas | ||

|---|---|---|

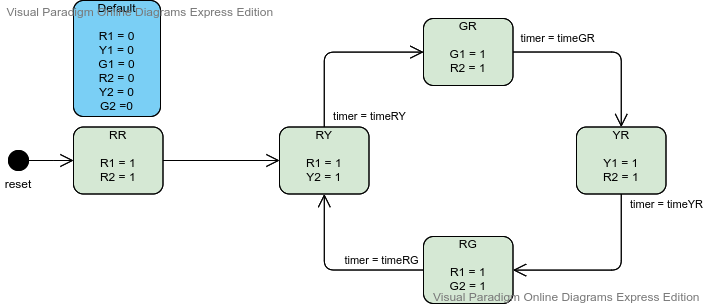

Figura 7.1 - Exemplo de diagrama de estados de uma FSM Fig11.1(a) e implementação em hardware da FSM Fig11.2(a)

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

----------------------------------------------------------

ENTITY < entity_name > IS

PORT (

clk, rst : IN STD_LOGIC;

entradas : IN < data_type > ;

saidas : OUT < data_type >);

END entity;

----------------------------------------------------------

ARCHITECTURE < architecture_name > OF < entity_name > IS

TYPE state IS (A, B, C, ...);

SIGNAL pr_state, nx_state : state;

-- ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute

-- ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential";

-- ATTRIBUTE SYN_ENCODING OF state : TYPE IS "safe";

BEGIN

------Logica Sequencial da FSM:------------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

pr_state <= A;

ELSIF rising_edge(clk) THEN

-- apenas na borda do "clk" ocorre a mudança de estado da FSM

pr_state <= nx_state;

END IF;

END PROCESS;

------Logica Combinacional da FSM:------------

PROCESS (pr_state, entradas)

BEGIN

------Valores default das saidas------------

saidas <= < valor > ;

CASE pr_state IS

WHEN A =>

-- é necessário um WHEN para definir as "saidas" durante cada estado

-- e analisar as "entradas" para definir o próximo estado

saidas <= < valor > ; -- apenas se diferente do valor default

IF (entradas = < valor >) THEN

nx_state <= B;

...

ELSE

nx_state <= A;

END IF;

WHEN B =>

saidas <= < valor > ; -- apenas se diferente do valor default

-- dependendo das "entradas", pode ser que hajam mais de um estados de destino

IF (entradas = < valor >) THEN

nx_state <= C;

ELSIF (entradas = < valor >) THEN

nx_state <= A;

ELSE

nx_state <= B;

END IF;

WHEN C =>

saidas <= < valor > ; -- apenas se diferente do valor default

-- a passagem para outro estado pode não depender de nenhuma "entrada"

nx_state <= C;

WHEN ...

END CASE;

END PROCESS;

------Seção de Saída (opcional):-------

-- Essa seção visa garantir que a saida new_output esteja sincronizada com o clk.

-- Se isso não for importante, ela pode ser suprimida

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

new_output <= < valor > ;

ELSIF rising_edge(clk) THEN --or falling_edge(clk)

new_output <= output;

END IF;

END PROCESS;

END architecture;

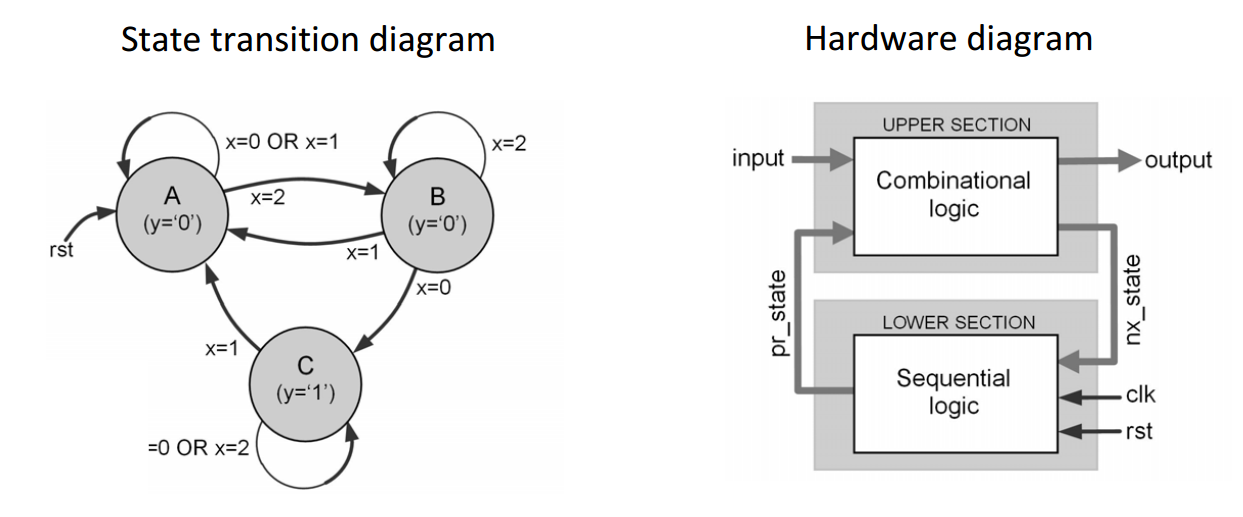

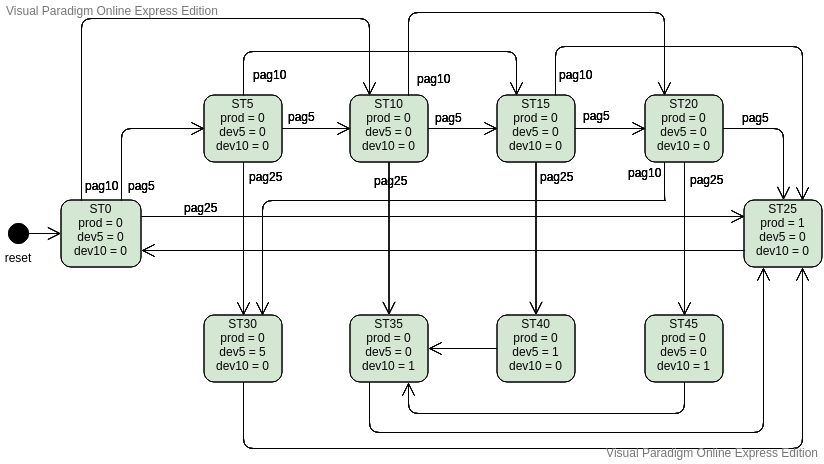

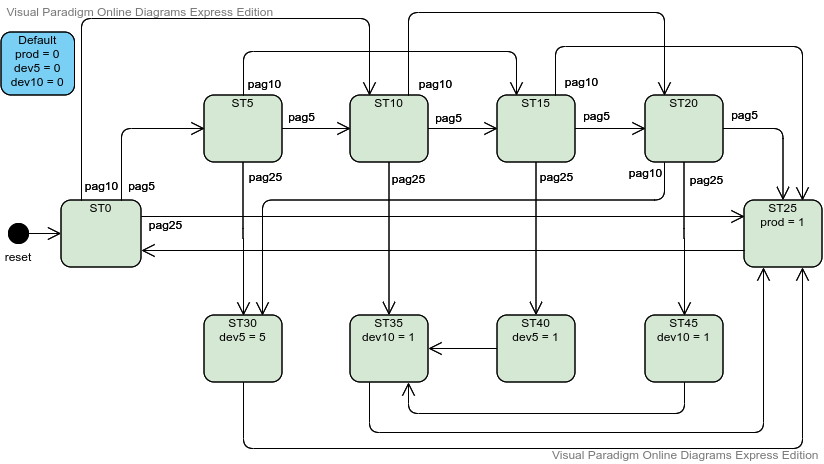

Figura 7.2 - FSM - Máquina de vender doces (diagrama de estados)  Figura 7.3 - FSM - Máquina de vender doces (diagrama de estados com default

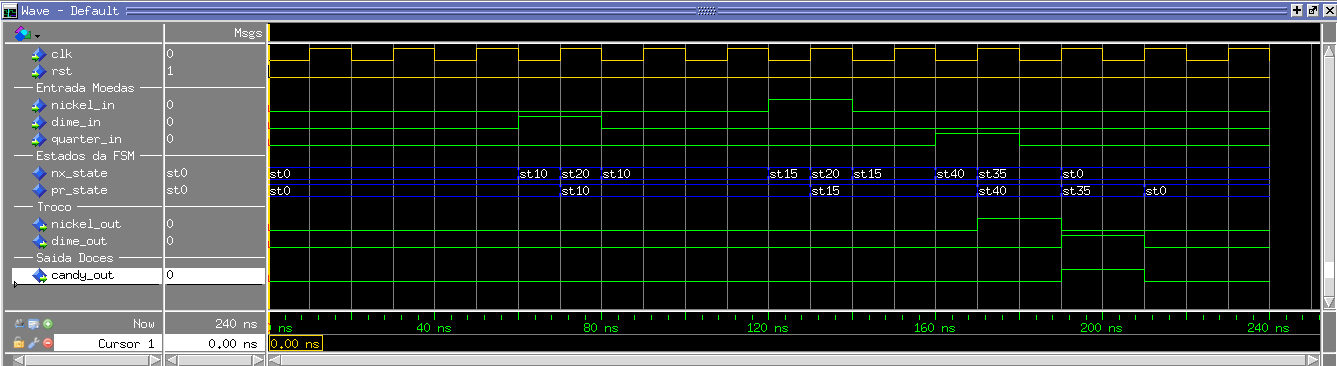

Figura 7.4 - FSM - Máquina de vender doces (simulação)

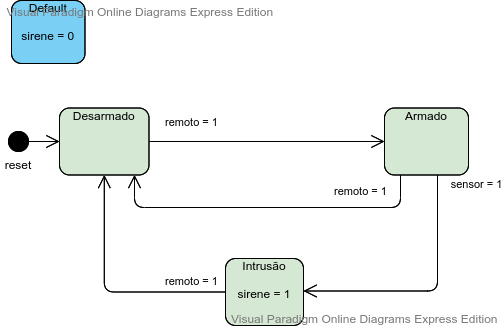

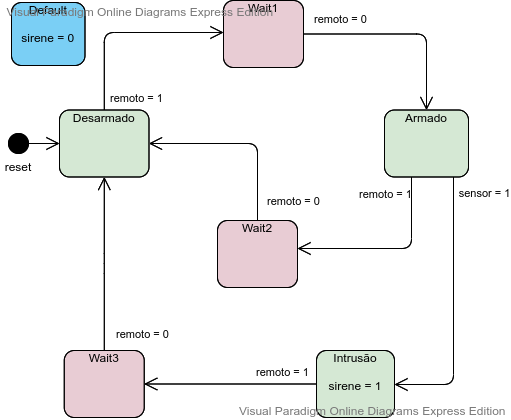

Figura 7.5 - FSM - alarme (oscilando entre os estados quando remoto é 1)

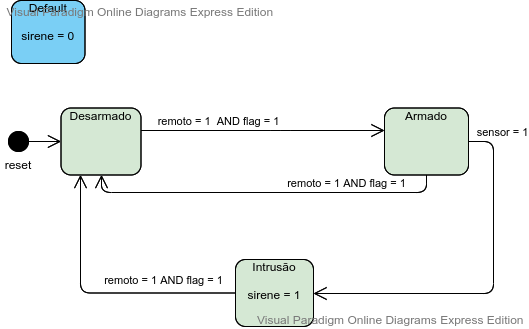

Figura 7.6 - FSM - alarme (solução com flag)

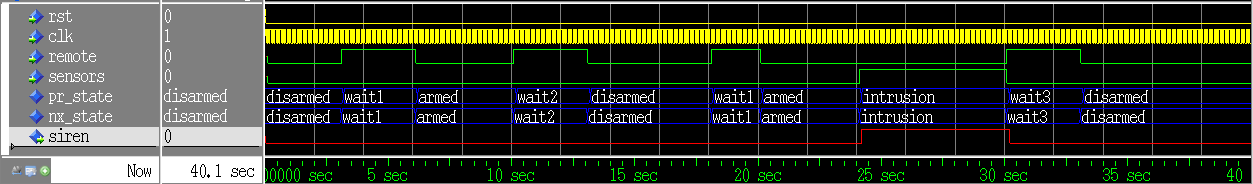

Figura 7.7 - FSM - alarme (solução com estados de WAIT)  Figura 7.8 - Simulação da FSM - alarme (solução com estados de WAIT)

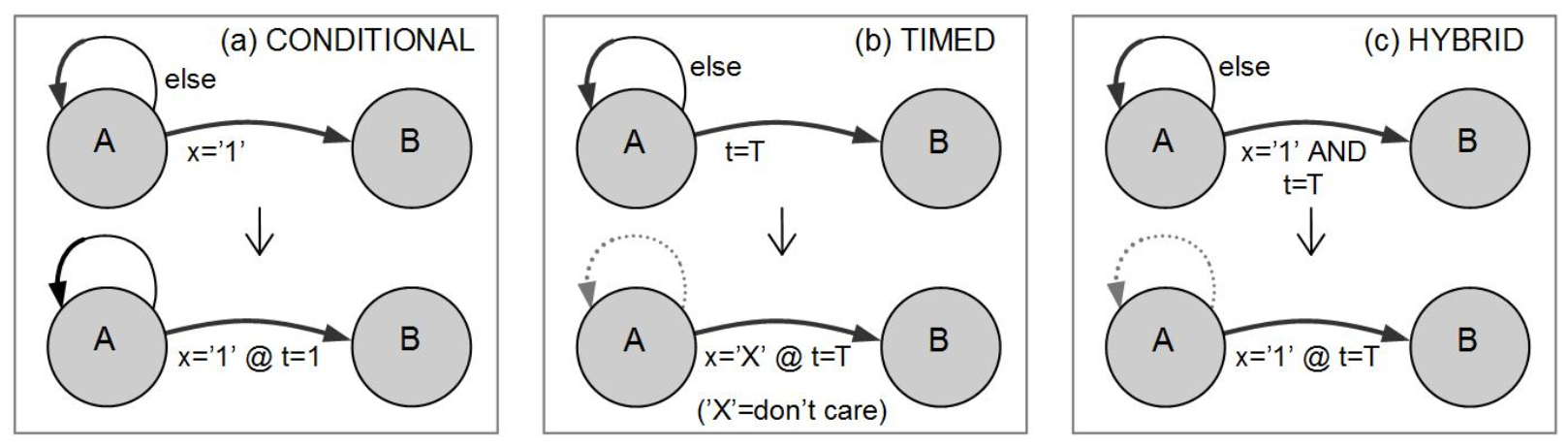

Figura 7.9 - Tipos de FSM (Condicional, Temporizada e Hibrida)

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

----------------------------------------------------------

ENTITY < entity_name > IS

PORT (

clk, rst : IN STD_LOGIC;

input : IN < data_type > ;

output : OUT < data_type >);

END entity;

----------------------------------------------------------

ARCHITECTURE < architecture_name > OF < entity_name > IS

TYPE state IS (A, B, C, ...);

SIGNAL pr_state, nx_state : state;

signal timer: integer range 0 to MAX;

-- ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute

-- ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential";

BEGIN

------Logica Sequencial da FSM:------------

PROCESS (clk, rst)

variable count: integer range o to MAX;

BEGIN

IF (rst = '1') THEN

pr_state <= A;

count := 0;

ELSIF (clk'EVENT AND clk = '1') THEN

count := count + 1;

if (count >= timer) then

pr_state <= nx_state;

count := 0;

end if;

END IF;

END PROCESS;

------Logica Combinacional da FSM:------------

PROCESS (pr_state, input)

BEGIN

------Valores default das saidas------------

output <= < value >;

------Valores default do timer------------

timer <= <value>;

CASE pr_state IS

WHEN A =>

output <= < value > ; -- apenas se diferente do valor default

IF (input =< value >) THEN

timer <= <value>; -- apenas se diferente do valor default

nx_state <= B;

...

ELSE

timer <= <value>; -- apenas se diferente do valor default

nx_state <= A;

END IF;

WHEN B =>

output <= < value > ; -- apenas se diferente do valor default

IF (input =< value >) THEN

timer <= <value>; -- apenas se diferente do valor default

nx_state <= C;

...

ELSE

timer <= <value>; -- apenas se diferente do valor default

nx_state <= B;

END IF;

WHEN ...

END CASE;

END PROCESS;

------Seção de Saída (opcional):-------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

new_output <= < value > ;

ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0'

new_output <= output;

END IF;

END PROCESS;

END architecture;

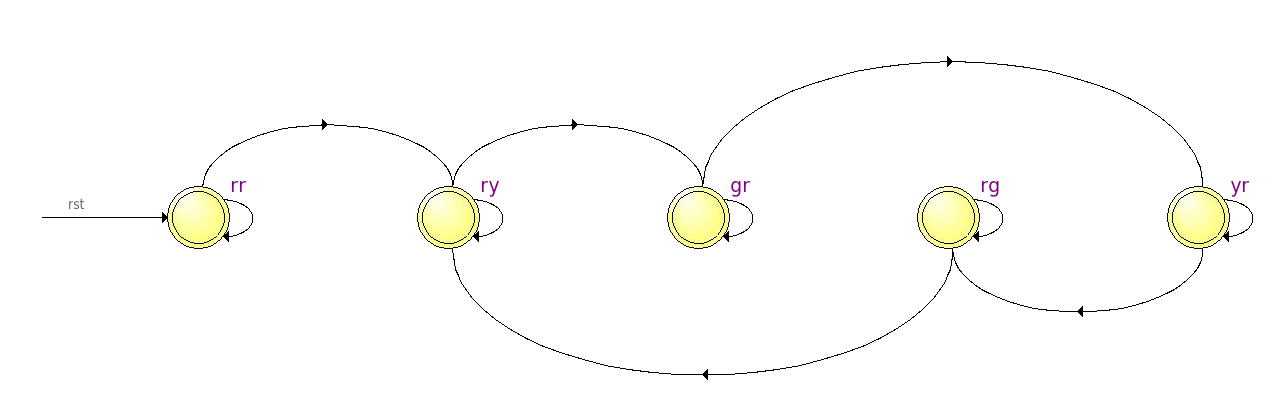

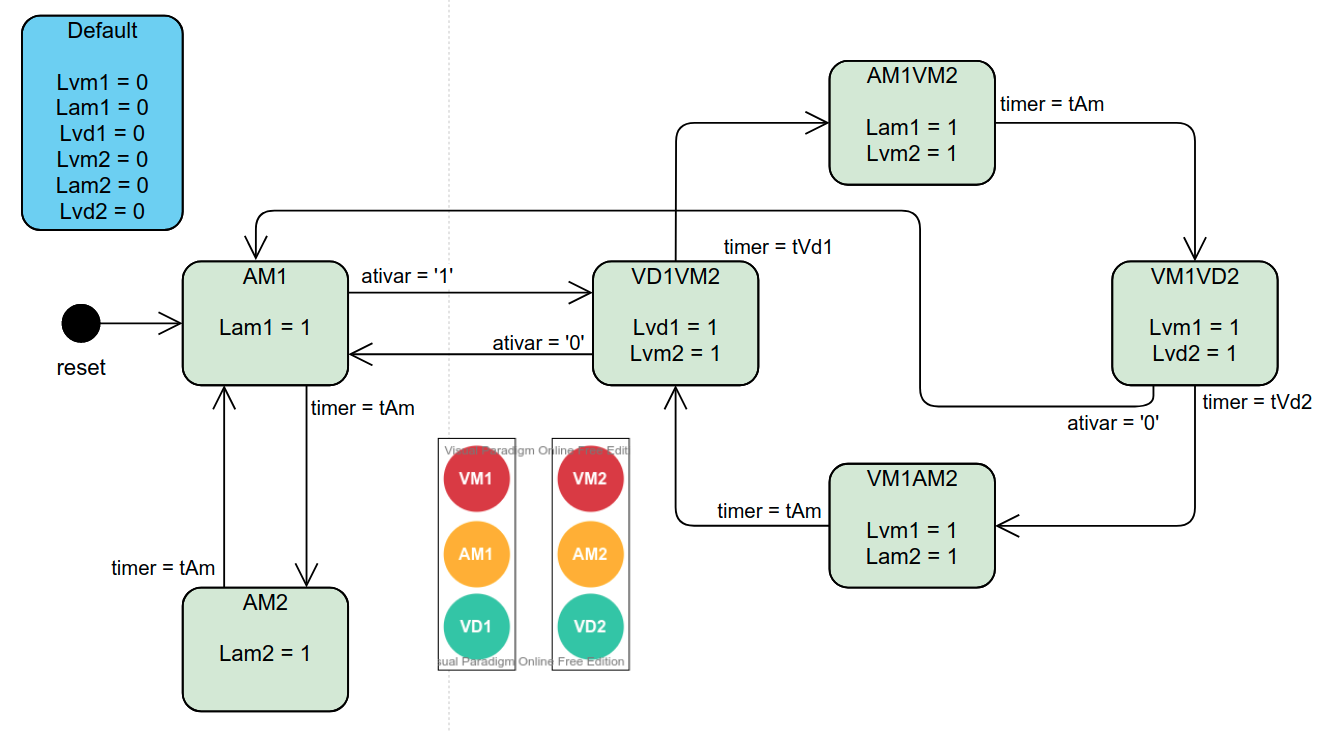

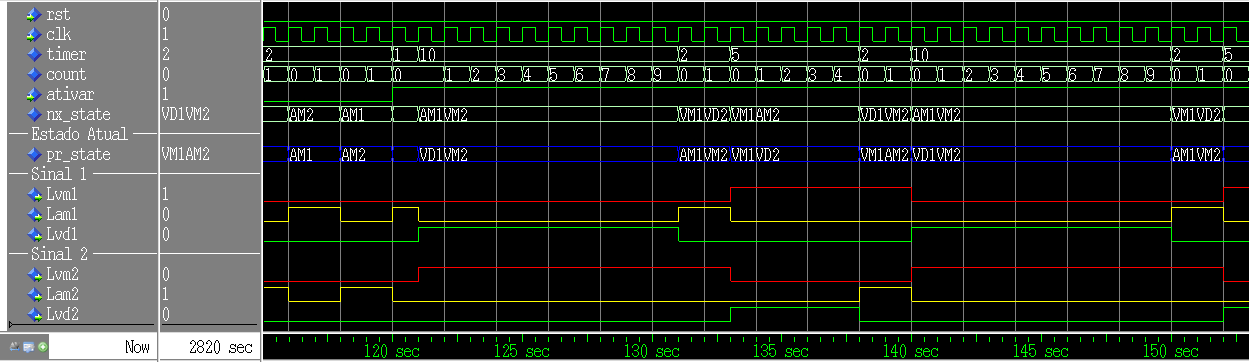

Figura 7.10 - Diagrama de estados do controlador de semáforo  Figura 7.11 - Simulação do controlador de semáforo no Modelsim

|

Unidade 8 - Testbench

- 2 ENCONTROS

| Unidade 8 - Testbench |

|---|

Avaliações

Nas avaliações A1 e A2 vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - Unidade 1 a Unidade 4: dia XX/XX

- A2 - Unidade 5 a Unidade 7: dia XX/XX

- PF - Entrega do projeto final: dia 15/12

- R12 - Recuperação de A1 e A2 : dia 12/12

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. Elas geram BÔNUS que são adicionados aos conceitos das avaliações A1 e A2.

Atividade extra-classe (AE)

A soma das atividades Extra-classe será correspondente a 30% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.