Registro on-line das aulas

Unidade 1 - Introdução a disciplina

| Unidade 1 - Introdução a disciplina

|

- Encontro 1 (18 ago.)

- APRESENTAÇÃO DA DISCIPLINA

- Os materiais, prazos, documentação, histórico de trabalhos anteriores estão publicados nesta wiki.

- A PÁGINA DA DISCIPLINA contem os materiais que não alteram entre semestre.

- Nesta página está o REGISTRO DIÁRIO E AVALIAÇÕES.

- Para a realização e entrega das atividades será utilizada a plataforma Moodle.

- Para a comunicação entre professor-aluno, além dos avisos no SIGAA, utilizaremos o chat institucional. É necessário que forneçam o seu email institucional para serem cadastrados.

- Para participar das aulas é recomendado que o aluno acesse a Nuvem do IFSC ou instale a VM com softwares Quartus II e Modelsim.

- Introdução aos dispositivos lógicos programáveis:

-

- SPLD: PAL, PLA e GAL

- CPLDs

- Encontro 2 (23 ago.)

-

- Fabricantes de DLPs/FPGAs e familias de DLPs atuais.

-

- Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, RAM, DSP, Clock, PLL, I/O

- Ler pag. 413 a 431 de [1] ou pag. 495 a 501 de de [2].

- Encontro 3 e 4 (25 e 30 ago.)

- Leituras complementares para a unidade

- Historia, processo de produção dos chips.

- Curiosidades do mundo digital

- O que é um Schmitt trigger?

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

|

- Encontro 5 (31 ago.)

- Introdução ao VHDL e ambiente EDA - QUARTUS

- Estrutura do código VHDL

- Declaração das bibliotecas e pacotes LIBRARY / PACKAGE

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

- Exemplo - Declaração de uma porta NAND em VHDL

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

- Encontro 6 (1 set.)

Exemplo de descrição de um multiplexador de 4 entradas

entity mux_novo is

port

(

-- Input ports

X: in bit_vector (3 downto 0);

S : in bit_vector (1 downto 0);

-- Output ports

Y : out bit

);

end entity mux_novo;

-- Implementação com lógica pura

architecture v_logica_pura of mux_novo is

begin

Y <= (X(0) and (not S(1)) and (not S(0))) or

(X(1) and (not S(1)) and (S(0))) or

(X(2) and (S(1)) and (not S(0))) or

(X(3) and (S(1)) and (S(0)));

end architecture Logica_pura;

-- Implementação com WHEN ELSE

architecture v_WHEN of mux_novo is

begin

Y <= X(0) when S = "00" else

X(1) when S = "01" else

X(2) when S = "10" else

X(3);

end architecture v_WHEN;

-- Implementação com WITH SELECT

architecture v_WITH_SELECT of mux_novo is

begin

with S select

Y <= X(0) when "00", -- note o uso da ,

X(1) when "01",

X(2) when "10",

X(3) when others; -- note o uso de others, para todos os demais valores.

-- Não pode ser substituido por "11" mesmo que o signal seja bit_vector.

end architecture v_WITH_SELECT;

-- Implementação com IF ELSE

architecture v_IF_ELSE of mux_novo is

begin

-- Uma arquitetura vazia como essa é denominada de STUB,

-- Pode ser utilizada em um projeto durante para conferir as conexões externas.

-- Posteriormente a arquitetura será descrita.

end architecture v_IF_ELSET;

-- Design Unit que associa a architecture com a entity

configuration cfg_ifsc of mux_novo is

-- for v_WITH_SELECT end for;

for v_WHEN end for;

end configuration;

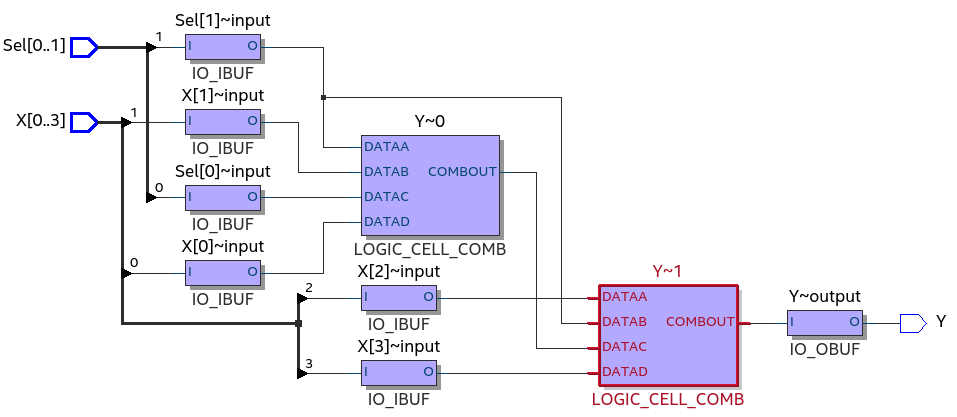

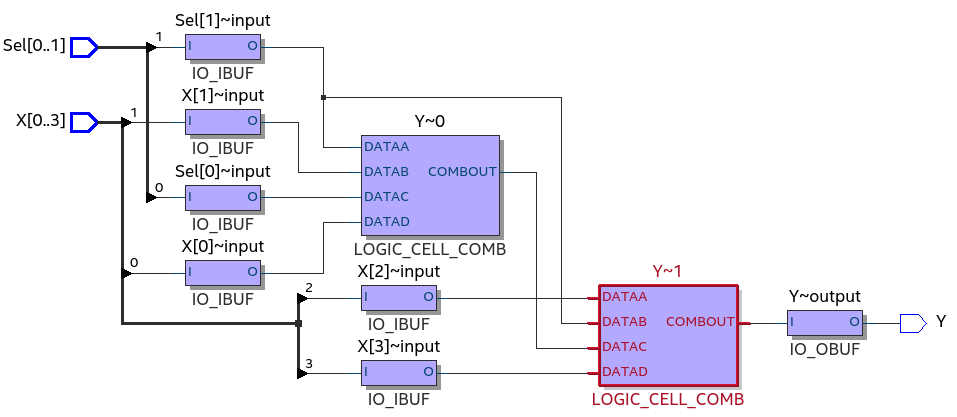

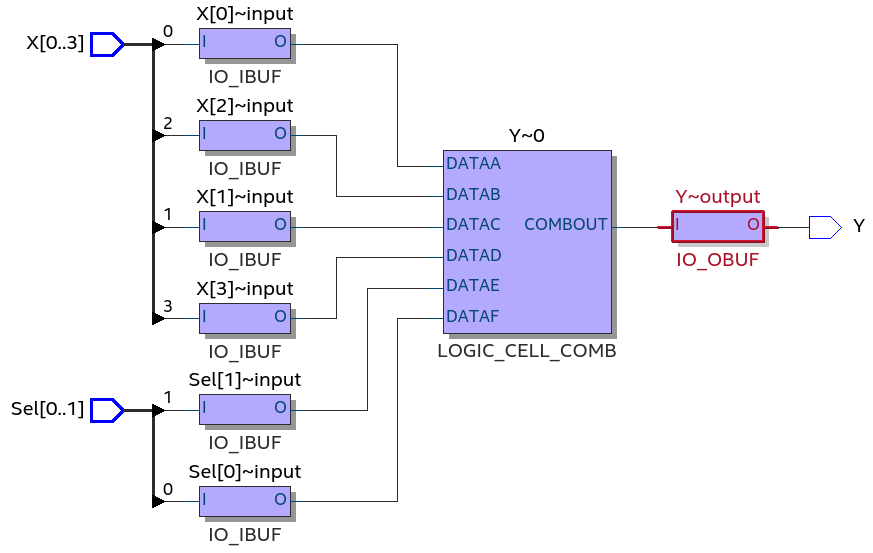

- Faça a análise e sintese do mux_novo, associando a architecture v_logica_pura, depois v_WITH_SELECT, depois v_WHEN e por último v_IF_ELSE.

- Note a diferença entre os RTL Viewer obtidos para cada architecture.

Figura 2.1 - Código RTL do mux 4x1 v_logica_pura

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura 2.2 - Código RTL do mux 4x1 v_WHEN

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura 2.3 - Código RTL do mux 4x1 v_WITH_SELECT

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- OBS: Register Transfer-Level (RTL) é uma abstração na qual o circuito é descrito em termos de fluxo de sinais entre os registradores presentes no hardware e as operações combinacionais realizadas com esses dados.

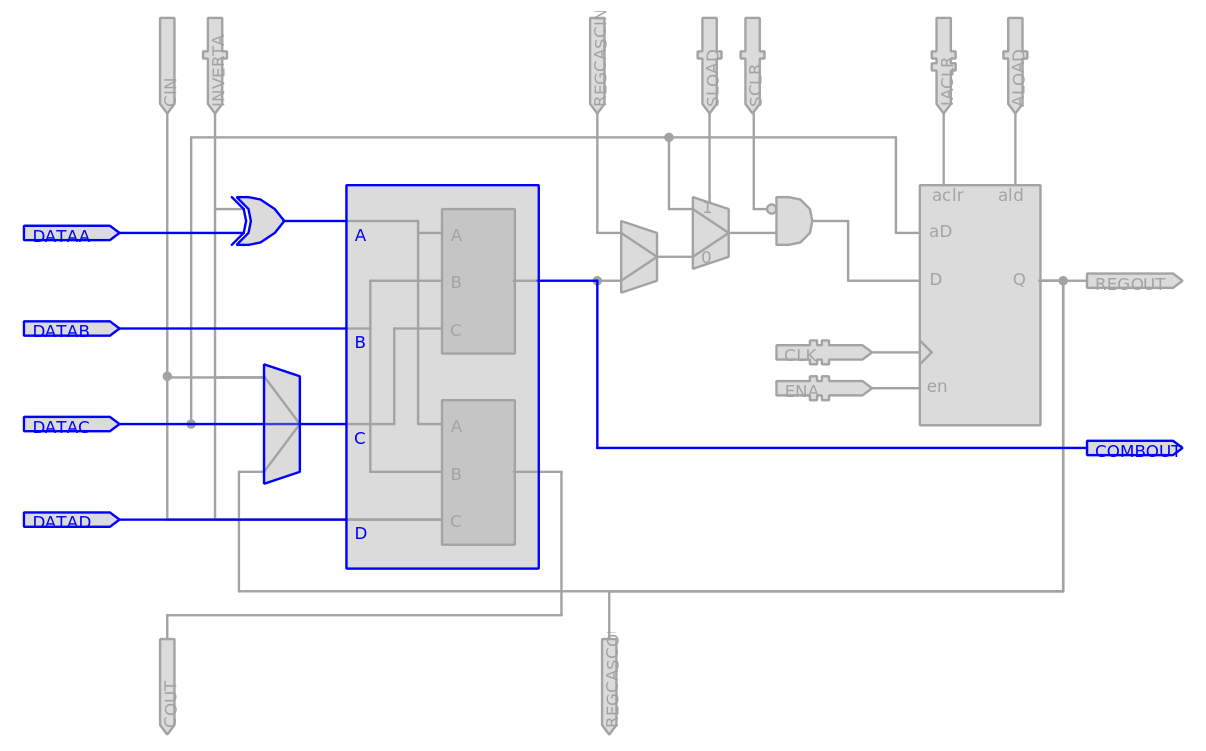

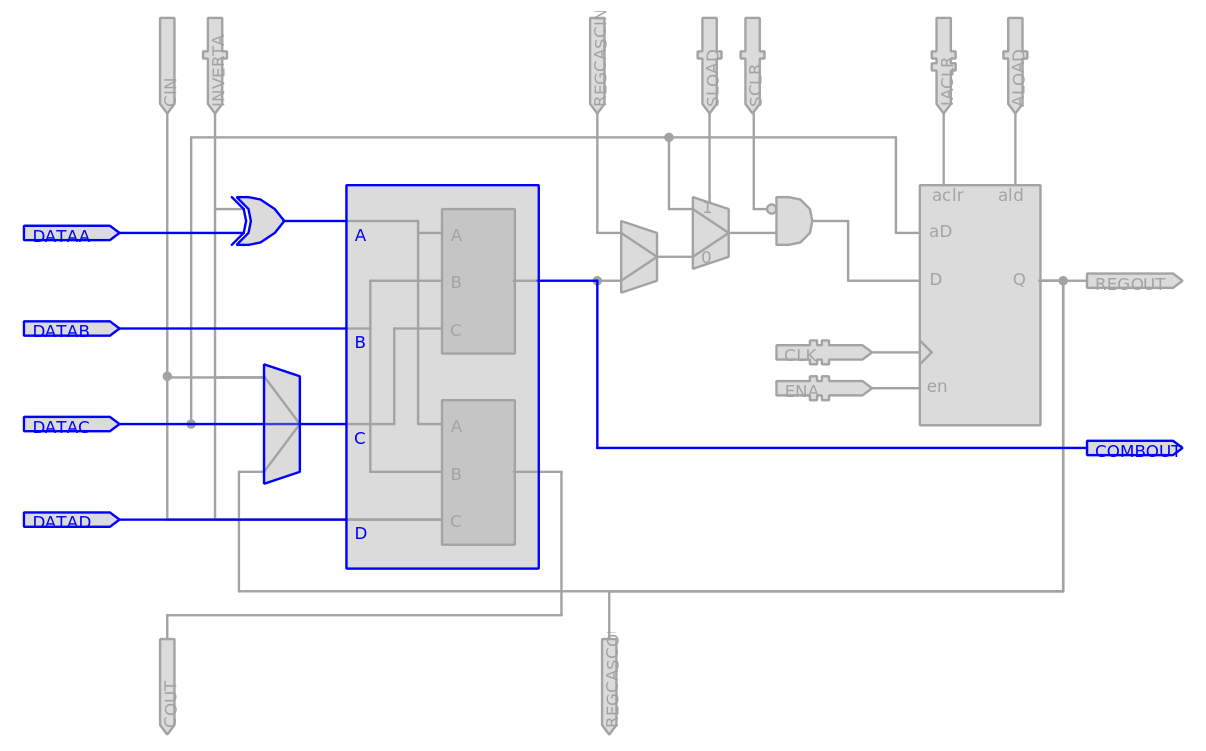

- Note a que ao verificar o Technology Map Viewer, nos 3 primeiros casos serão usados os mesmos elementos lógicos.

Figura 2.4 - Technology Map do mux 4x1 para a família Cyclone

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Note que o elemento lógico acima possui uma LUT (LookUp Table) que basicamente implementa o circuito combinacional através de uma tabela de consulta (Tabela Verdade), a qual pode ser visualizada clicando com o botão Direito do Mouse e selecionando Properties, juntamente com Mapa de Karnaugh e seu Circuito Lógico representado por portas. Todas as representações são equivalentes.

Figura 2.5 - Elemento Lógico usado no mux 4x1 para a família Cyclone (node properties)

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Dependendo da família de FPGA que se estiver usando, o compilador implementar o circuito descrito com um número diferente de elementos lógicos (LEs). No caso da família Cyclone, na qual a LUT tem 4 entradas, são necessários 2 LEs para mapear uma lógica combinacional com 6 entradas e 1 saída (Mux4x1).

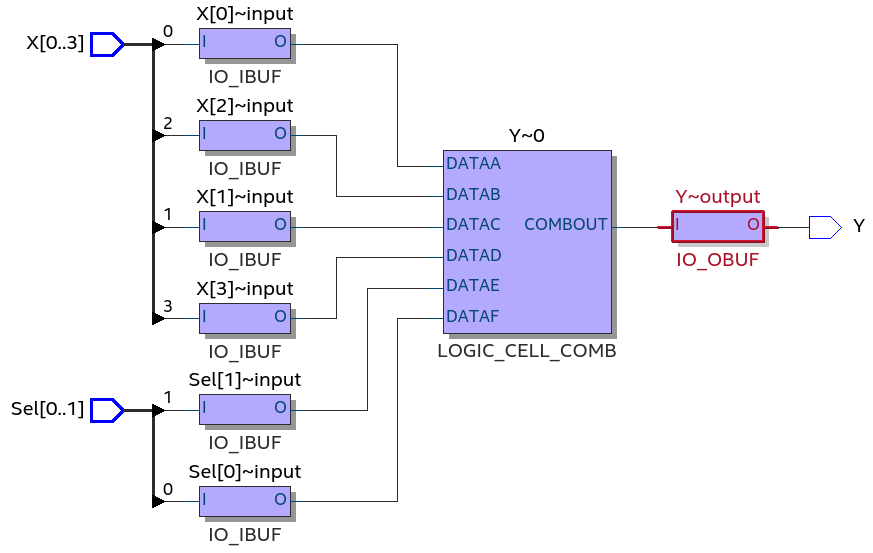

No entanto se utilizarmos um dispositivo FPGA da família Stratix III, que tem LUT tem 6 entradas, será necessário apenas 1 LE, conforme ilustrado a seguir.

Figura 2.5 - Technology Map do mux 4x1 para a família Stratix III

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Encontro 9 (6 set.)

- Exemplo 2.2 (VHDL) - programação de um flip-flop

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

Figura 2.2 - Código RTL do Exemplo 2.2

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Use o Technology Map Viewer para ver a como o circuito foi mapeado para os elementos lógicos disponíveis no dispositivo FPGA selecionado (EP1C3T100A8)

Figura 2.3 - Technology Map do Exemplo 2.2

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura 2.4 - Chip Planner do Exemplo 2.2

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Modifique o circuito do flip-flop para que ele passe a ter 4 flip-flops

Figura 2.5 - RTL 4 FF

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Uso de alguns sites auxiliares para a programação em VHDL:

|

Unidade 3 - Tipos de Dados e Operadores em VHDL

|}

Unidade 4 - Código Concorrente

|}

Unidade 5 - Código Sequencial

|}

Unidade 6 - Projeto a nível de Sistema

|}

Unidade 7 - Maquinas de Estado Finitas

|}

Avaliações

Nas avaliações A1 e A2 serão realizadas de forma presencial e vocês poderão consultar apenas as folhas entregues:

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

A soma das atividades Extra-classe será correspondente a 20% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle da disciplinas, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

AE1 - Palavras-cruzadas INTRODUÇÃO

| AE1 - Palavras-cruzadas INTRODUÇÃO

|

|

|

AE2 - Conhecendo os dispositivos lógicos programáveis

| AE2 - Conhecendo os dispositivos lógicos programáveis

|

- Objetivos

- Conhecer o Quartus II e as características dos dispositivos lógicos programáveis

- Analisar os tempos de propagação em um circuito combinacional

- Alterar configurações do compilador

- Fazer a simulação funcional e temporal de um circuito combinacional.

- Atividade

- Ao escolher a família de FPGAS, escolha inicialmente um dispositivo da família Cyclone II, ou Max II. Anote o código desse dispositivo.

- Capture as telas solicitadas e depois utilize-as no relatório da atividade.

- Anote o tempo utilizado para cada uma das etapas do processo de compilação.

- Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo.

- Anote algum erro (Error) ou alertas (Warnings) que o Quartus II indicar no painel de mensagens [Messages]

- Ao final salve o projeto em um arquivo QAR (sugestão PJ1.QAR)

- PASSO 2: Repita a atividade descrita em Conhecendo os dispositivos lógicos programáveis, trocando a família e dispositivo a ser usado na implementação. Escolha nesta vez um dispositivos da família Cyclone IV E ou Stratix II GX. Anote o código desse dispositivo.

- Observe as mudanças que ocorrem tanto no tipo de Elemento Lógico disponível, no Chip Planner, no Pin Planner, e no circuito dos pinos de I/O. Note que estes FPGAs também apresenta novos componentes, tais como: Memória, Multiplicadores, DSP, PLL, DLL, etc. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documente aqueles que encontrar.

- Compare os resultados obtidos nos procedimentos do PASSO 1 e PASSO 2.

- Ao escolher a família de FPGAS, escolha um dispositivo FPGA da família Cyclone IV E. Anote o código desse dispositivo.

- Capture as telas mostradas no roteiro e depois utilize-as no relatório da atividade.

- Anote o máximo tempo de propagação entre entrada e saída.

- Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo.

- Experimente modificar as configurações do compilador, conforme mostrado em Configurando o compilador. Se desejar mude a semente inicial trocando o valor de [Seed: 1]

- Experimente inserir diferentes restrições de atraso máximo para o compilador, e analise o resultado obtido.

- Anote algum erro (Error) ou alertas (Warnings) que o Quartus II indicar no painel de mensagens [Messages]

- Ao final salve o projeto em um arquivo QAR (sugestão PJ2.QAR)

- PASSO 4: Realize a simulação funcional e também a temporal de um dos projetos CI74161 ou do cálculo da distância de Hamming

- Capture as telas que mostram o circuito funcionando e depois utilize-as no relatório da atividade.

- Entregas

- Envie um arquivo QAR contendo todos os arquivos necessário para compilar cada um dos projetos.

- Envie um relatório em PDF, incluindo as imagens capturadas (inclua um título para cada figura) e escreva para cada imagem um texto comentando o que representa. O relatório também deve ter a identificação (autor, título, data) uma breve introdução e uma conclusão. A descrição dos procedimentos feita na página wiki não precisa incluída no relatório.

- Use preferencialmente o Overleaf para gerar o relatório. Mas o uso de MS-Word, Libreoffice e Google Docs também é permitida.

- A entrega será feita através do Moodle da disciplina. Observe o prazo de entrega.

|

|}

- ↑ 1,0 1,1 1,2 1,3 1,4 PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335