DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 6 ENCONTROS

| Unidade 1 - Introdução a disciplina | ||||

|---|---|---|---|---|

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 10 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

- 10 ENCONTROS

| Unidade 3 - Tipos de Dados e Operadores em VHDL |

|---|

Unidade 4 - Código Concorrente

- 3 Encontros

| Unidade 4 - Código Concorrente | ||

|---|---|---|

<optional_label>: <target> <=

<value> when <condition> else

<value> when <condition> else

<value> when <condition> else

...

<value>;

Warning (13012): Latch ... has unsafe behavior

<optional_label>: with <expression> select

<target> <=

<value> when <choices>,

<value> when <choices>,

<value> when <choices>,

...

<value> when others;

Error (10313): VHDL Case Statement error ...: Case Statement choices must cover all possible values of expression

configuration which_mux of mux4x1 is

-- for operators_only end for;

-- for operators_only_alias end for;

for with_WHEN end for;

-- for with_SELECT end for;

end configuration;

label: FOR identificador IN faixa GENERATE

[Parte_Declarativa

BEGIN]

Instruções_concorrentes

...

END GENERATE [label];

---------------------

-- FILE my_pkg.vhd --

---------------------

library ieee;

use ieee.std_logic_1164.all;

package my_pkg is

type a_slv is array(natural range <>) of std_logic_vector (3 downto 0);

end package;

---------------------------

-- FILE vector_adder.vhd --

---------------------------

library ieee work;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use work.my_pkg.all;

entity vector_adder is

generic (N : natural := 4);

port (

a : in a_slv (0 to N-1);

soma : out std_logic_vector (3 downto 0));

end entity;

-- Versão que realiza a soma diretamente, mas que precisa modificar o código de acordo com o número de entradas.

architecture ifsc_v1 of vector_adder is

signal soma_sig : signed(3 downto 0);

begin

soma_sig <= signed(a(0)) + signed(a(1)) + signed(a(2)) + signed(a(3));

soma <= std_logic_vector(soma_sig);

end architecture;

-- Versão que realiza a soma usando um FOR GENERATE

architecture ifsc_v2 of vector_adder is

begin

end architecture;

---------------------------

-- FILE vector_adder.vhd --

---------------------------

configuration ifsc_cfg of vector_adder is

-- for ifsc_v1 end for;

for ifsc_v2 end for;

end configuration;

-------------------------

-- File: bin2gray.vhd --

-------------------------

entity bin2gray is

generic (N : natural := 4 )

port

(

g : out std_logic_vector(____)

b : in std_logic_vector(____)

)

end entity

architecture ifsc_v1 of ____ is

begin

end architecture

architecture ifsc_v2 of ____ is

begin

end architecture

-------------------------

-- File: gray2bin.vhd --

-------------------------

entity gray2bin is

generic (N : natural := 4 )

port

(

g : in std_logic_vector(____)

b : out std_logic_vector(____)

)

end entity

architecture ifsc_v1 of ____ is

begin

end architecture

architecture ifsc_v2 of ____ is

begin

end architecture

Outros exemplos a serem estudados:

----------------------

-- File: alu.vhd --

----------------------

entity ua is

generic (N : natural := 4);

port

(

a, b : in std_logic(? downto 0);

cin : in std_logic;

opcode : in std_logic(? downto 0);

y : out std_logic(? downto 0)

);

end entity;

architecture alu of alu is

begin

end architecture;

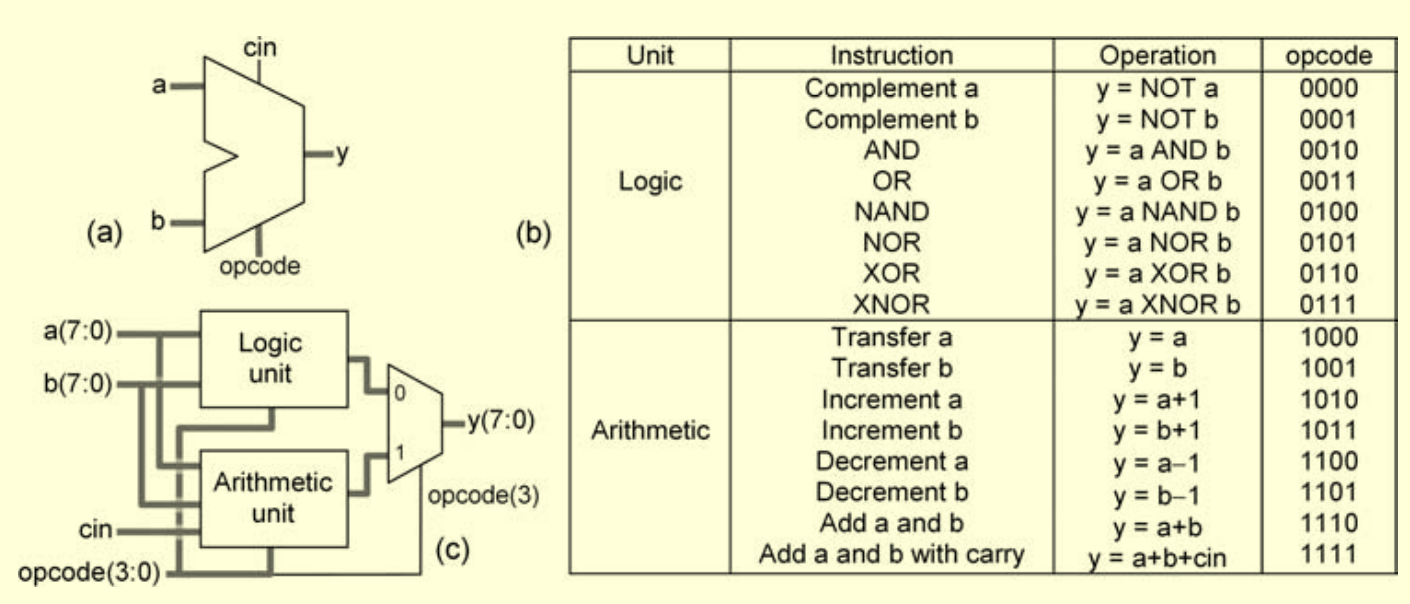

Figura 3.9 - Unidade de Lógica e Aritmética

|

Unidade 5 - Código Sequencial

- 5 ENCONTROS

| Unidade 5 - Código Sequencial |

|---|

[rótulo:] PROCESS [(lista_de_sensibilidade)] [IS]

[parte_declarativa]

BEGIN

afirmação_sequencial;

afirmação_sequencial;

...

END PROCESS [rótulo];

[rótulo:] IF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSIF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSE

afirmação_sequencial;

afirmação_sequencial;

...

END IF [rótulo];

--Flip Flop tipo D com reset assincrono, sensivel a borda de subida.

process (clock,reset)

begin

if (reset = '1') then

q <= '0';

-- elsif (clock'event and clock = '1') then or

elsif (rising_edge(clock)) then

q <= d;

end if;

end process;

--Flip Flop tipo D com preset assincrono e sinal de enable, sensivel a borda de descida.

process (clock, preset)

begin

if (preset = '1') then

q <= '1';

elsif (falling_edge(clock)) then

if (enable = '1') then

q <= d;

end if;

end if;

end process;

--Latch tipo D com reset assincrono.

process (enable, reset, d)

begin

if (reset = '1') then

q <= '0';

elsif (enable='1')) then

q <= d;

end if;

end process;

-- Flip Flop tipo D com reset síncrono sensível a borda de subida.

-- Modifique a descrição para que o reset_ass seja assíncrono e reset_sinc seja síncrono.

-- Note que a função rising_edge(clock) é equivalente a (clock'event and clock'last_value = '0' and clock = '1'))

process (clock, reset)

begin

if (reset = '1') then

q <= '0';

elsif (clock'event and clock'last_value = '0' and clock = '1')) then

q <= d;

end if;

end process;

Instruções do tipo LOOP: LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT

[rótulo:] LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] FOR identificador IN faixa LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] WHILE condição LOOP -- Executa as "afirmações enquanto a "condição" for verdadeira

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

EXIT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, termina o "LOOP"

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

NEXT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, não executa as linhas até a linha "END LOOP"

-- e incrementa o "identificador".

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] CASE expressão IS

WHEN valor => atribuições; -- valor único

...

WHEN valor1 | valor2 | ... | valorN => atribuições; -- lista de valores

...

WHEN valor1 TO valor2 => atribuições; -- faixa de valores

...

END CASE;

entity leading_zeros is

generic (N : natural := 8);

port

( ________ : in std_logic_vector(0 to N-1);

count : out integer range 0 to N

);

end entity;

architecture ____ of leading_zeros is

begin

process (data)

variable count : integer ____ 0 to N

begin

count := 0;

for i ___ data'range ____

case data(i) is

when '0' => count := count + 1;

when _____ => exit;

end ___

end ____

zeros <= count;

end process;

end _______;

entity carry_ripple_adder is

generic (N : integer := 4);

port (

a, b : std_logic_vector (N-1 downto 0);

cin : std_logic

s : out std_logic_vector (N downto 0);

cout : out std_logic;

);

end entity;

architecture estrutural of carry_ripple_adder

begin

-- Uso de um codigo sequencial para geracao de um circuito combinacional

process (a, b, cin)

variable c : std_logic_vector(N downto);

begin

c(0) := cin;

for i in 0 to N - 1 loop

-- Codigo de um full adder

-- soma de dois bits e carry_in do full adder anterior

s(i) <= a(i) xor b(i) xor c(i);

-- geraao do carry_out para o proximo full adder

c(i + 1) := (a(i) and b(i)) or (a(i) and c(i)) or (b(i) and c(i));

end loop;

cout <= c(N);

end process;

end architecture;

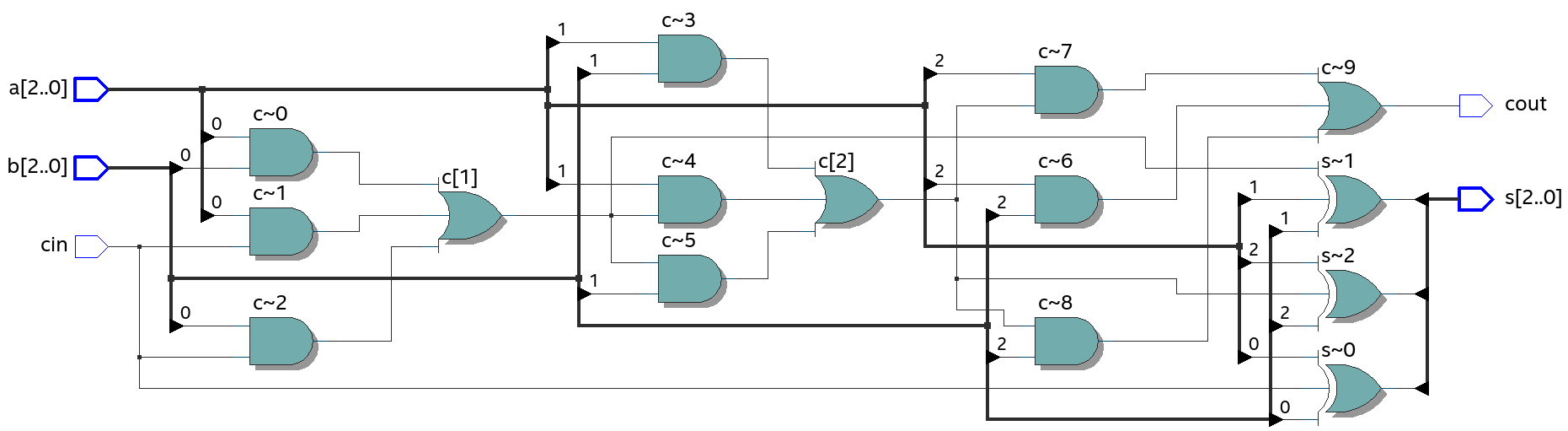

Figura 5.1 - RTL do carry_ripple_adder de 3 bits

[rótulo:] WAIT UNTIL <condition>;

[rótulo:] WAIT ON sensitivity_list;

[rótulo:] WAIT FOR time_expression;

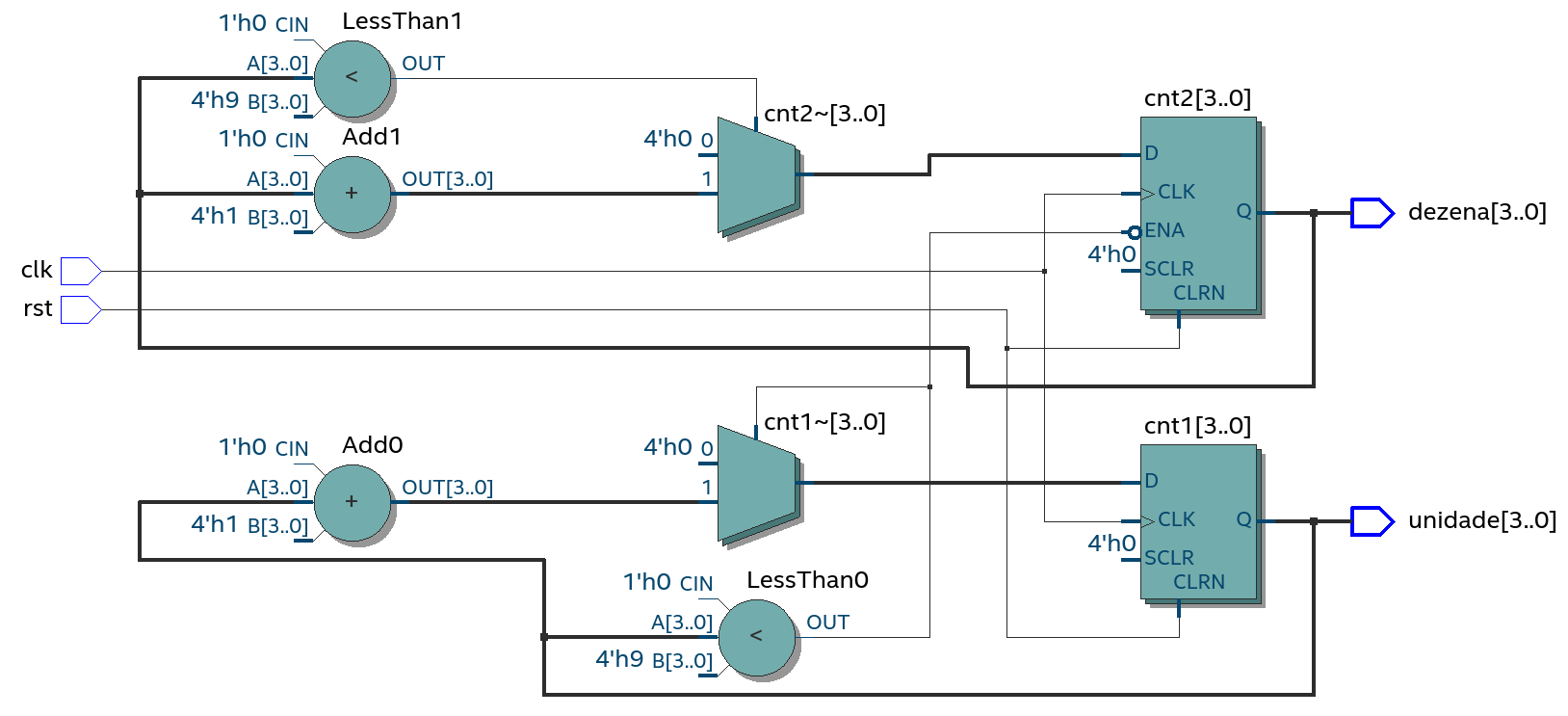

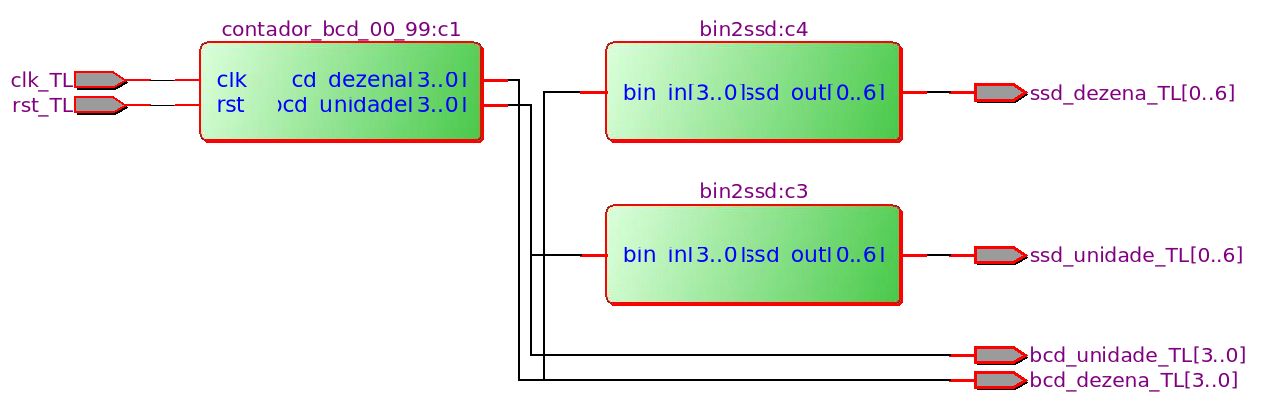

Figura 5.2 - RTL do contador BCD 00 a 99  Figura 5.3 - Simulação do contador BCD 00 a 99

Figura 5.4 - RTL do contador bidirecional BCD 00 a 99 Figura 5.5 - Simulação do contador bidirecional BCD 00 a 99

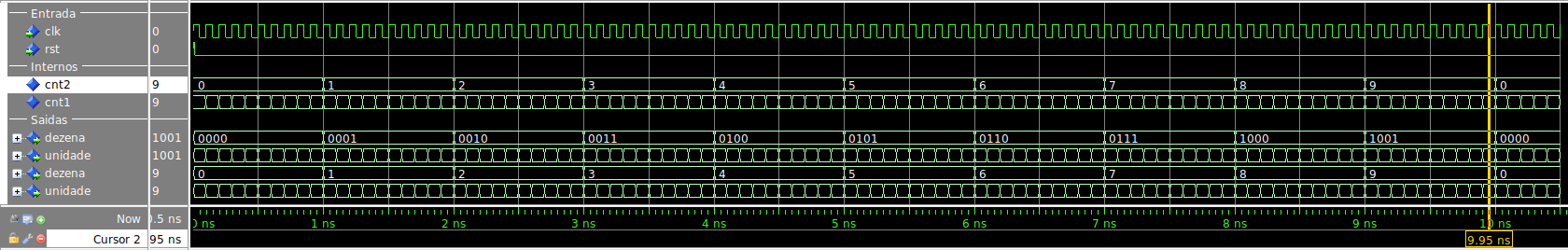

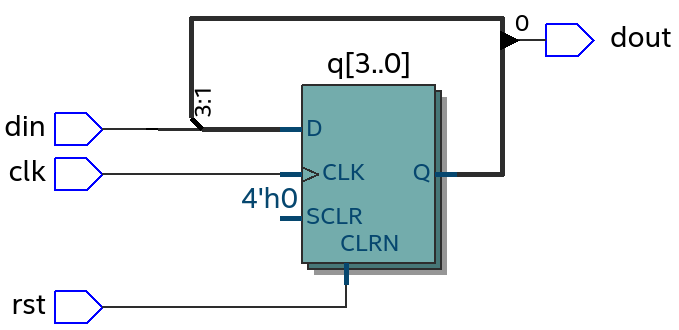

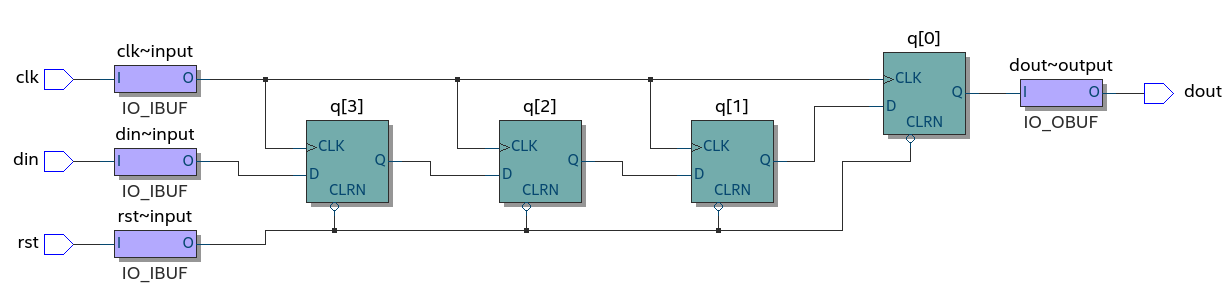

Figura 5.6 - RTL do registrador de deslocamento (Ex.6.3)  Figura 5.7 - Technology Map do registrador de deslocamento (Ex.6.3)

entity shift_reg4_right is

port

(

din, clk, rst : in std_logic;

dout : out std_logic

);

end entity;

architecture ifsc of shift_reg4_right is

begin

end architecture;

entity shift_reg_right is

generic (N : integer := 4);

port

(

din, clk, rst : in std_logic;

dout : out std_logic

);

end entity;

architecture ifsc of shift_reg_right is

begin

end architecture;

entity shift_reg_right is

generic (N : integer := 4);

port

(

din, clk, rst : in std_logic;

dout : out std_logic

);

end entity;

architecture ifsc of shift_reg_right is

begin

process (clk, rst)

variable q : std_logic_vector (N-1 downto 0);

begin

if (rst = '1') then

q := (others => '0');

elsif (clk'EVENT and clk = '1') then

q := din & q (N-1 downto 1);

end if;

dout <= q(0);

end process;

end architecture;

|

Unidade 6 - Projeto a nível de Sistema

- 5 Encontros

| Unidade 6 - Projeto a nível de Sistema |

|---|

Assim a entity contador_bcd_00_99 entity contador_bcd_00_99 is

generic (max_dezena : natural := 5; max_unidade : natural := 9);

port (

clk, rst : in std_logic;

bcd_dezena, bcd_unidade : out std_logic_vector(3 downto 0)

);

end entity;

Será declarada como um COMPONENT component contador_bcd_00_99 is

generic (max_dezena : natural := 5; max_unidade : natural := 9);

port (

clk, rst : in std_logic;

bcd_dezena, bcd_unidade : out std_logic_vector(3 downto 0)

);

end component;

comp1 : contador_bcd_00_99

GENERIC MAP (2, 3)

PORT MAP (clk,rst, bcd_dezena, bcd_unidade);

comp1 : contador_bcd_00_99

GENERIC MAP ( max_dezena => 2, max_unidade => 3)

PORT MAP ( clk => clk,

rst => rst,

bcd_dezena => bcd_dezena,

bcd_unidade => bcd_unidade);

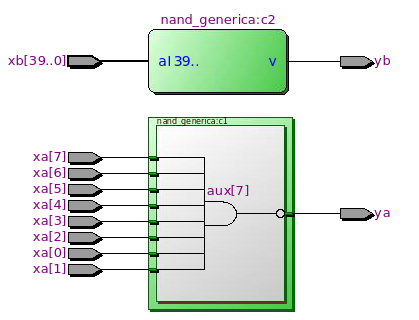

Figura 5.1 - RTL portas NAND genéricas

Figura 5.2 - RTL do contador_ssd_00_99 usando componentes

gen: for i in 0 to 7 generate

comp: flip_flop port map (clk, rst, d(i), q(i));

end generate;

A instrução ASSERT é útil para verificar as entradas de um subprograma. Seu propósito não é criar circuito, mas assegurar que certos requisitos são atendidos durante a síntese e/ou simulação. Pode ser condicional ou incondicional (condição_booleana = FALSE). A sintaxe da instrução é: [rótulo:] assert condição_booleana

[report mensagem]

[severity nivel_severidade];

A mensagem pode ser criada usando STRINGs que podem ser concatenadas. O nível de severidade pode ser NOTE (para passar informação para o compilador/simulator), WARNING (para informar que algo não usual ocorreu), ERROR (para informar que alguma condição não usual "sério" ocorreu), ou FAILURE (para informar que uma condição não aceitável ocorreu). Normalmente o compilador para quando ocorre um ERROR ou FAILURE. ERROR é o valor "default" [3].

function nome_funçao (lista_parametros_entrada) return tipo_saida is

declarações

begin

afirmações sequenciais

return value;

end function;

procedure nome_procedimento (lista_parâmetros_entrada, lista_parâmetros_saída) is

declarações

begin

afirmações sequenciais

end procedure;

function log2c (n : integer) return integer is

variable m , p : integer;

begin

m := 0;

p : = 1;

while p < n loop

m : = m + 1;

p := p * 2;

end loop;

return m;

end log2c;

-- FILE: comparator.vhd

-- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010.

library ieee;

use ieee.numeric_std.all;

use work.my_package.all;

entity organizer is

generic (size : natural := 3);

port

(

x : in UNSIGNED(2 to 5);

y : out UNSIGNED(size - 1 downto 0)

);

end entity;

architecture organizer of organizer is

begin

y <= order_and_fill(x, size);

end architecture;

-- FILE: my_pkg.vhd

-- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335

library ieee;

use ieee.numeric_std.all;

package my_package is

function order_and_fill (input : UNSIGNED; bits : natural) return UNSIGNED;

end package;

package body my_package is

function order_and_fill (input : UNSIGNED; bits : natural) return UNSIGNED is

variable a : UNSIGNED(input'LENGTH - 1 downto 0);

variable result : UNSIGNED(bits - 1 downto 0);

begin

assert (input'LENGTH <= bits)

report "Improper input size!"

severity FAILURE;

if (input'LEFT > input'RIGHT) then

a := input;

else

for i in a'range loop

a(i) := input(input'LEFT + i);

end loop;

end if;

if (a'LENGTH < bits) then

result(bits - 1 downto a'LENGTH) := (others => '0');

result(a'LENGTH - 1 downto 0) := a;

else

result := a;

end if;

return result;

end function;

end package body;

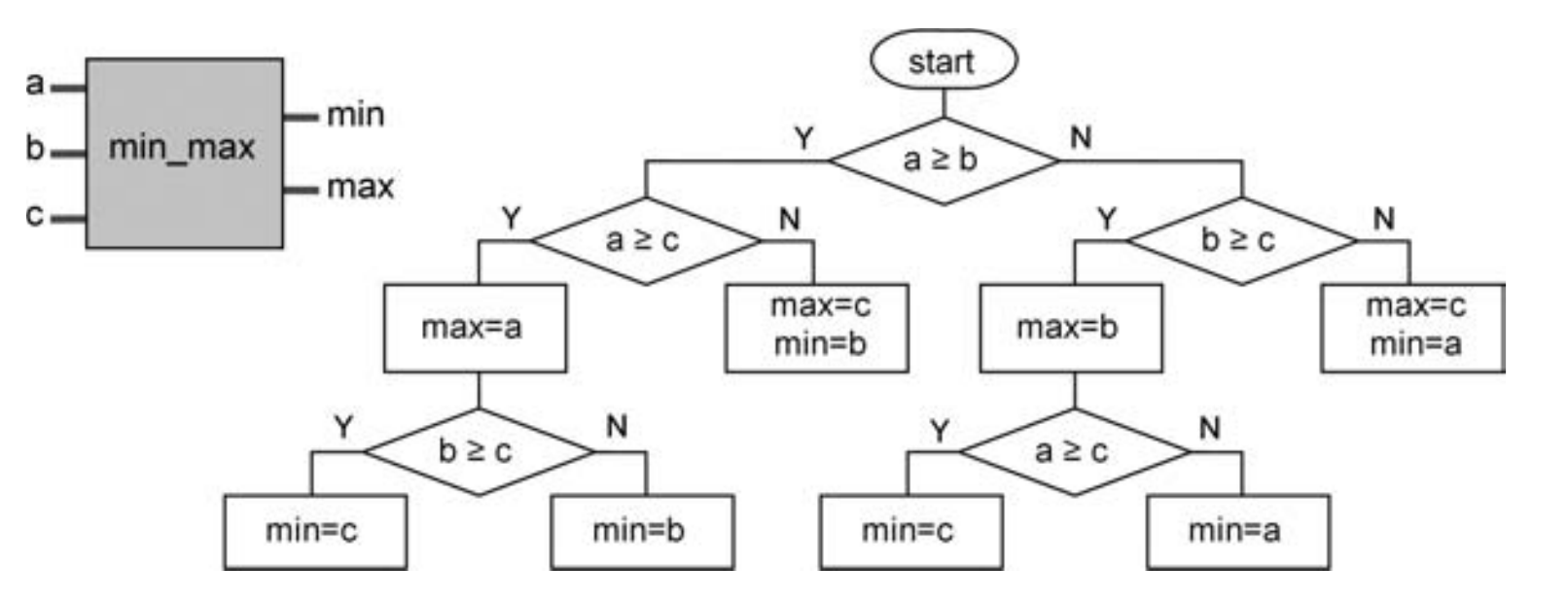

Figura 6.1 - Fluxograma da PROCEDURE min_max  -- FILE: comparator.vhd

-- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010.

use work.my_package.all;

entity comparator is

port

(

a, b, c : in integer range 0 to 255;

min, max : out integer range 0 to 255

);

end entity;

architecture comparator of comparator is

begin

min_max(a, b, c, min, max);

end architecture;

-- FILE: my_pkg.vhd

-- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010.

package my_package is

procedure min_max (

signal a, b, c : in integer;

signal min, max : out integer

);

end package;

package body my_package is

procedure min_max (

signal a, b, c : in integer range 0 to 255;

signal min, max : out integer range 0 to 255) is

begin

if (a >= b) then

if (a >= c) then

max <= a;

if (b >= c) then

min <= c;

else

min <= b;

end if;

else

max <= c;

min <= b;

end if;

else

if (b >= c) then

max <= b;

if (a >= c) then

min <= c;

else min <= a;

end if;

else

max <= c;

min <= a;

end if;

end if;

end procedure;

end package body;

|

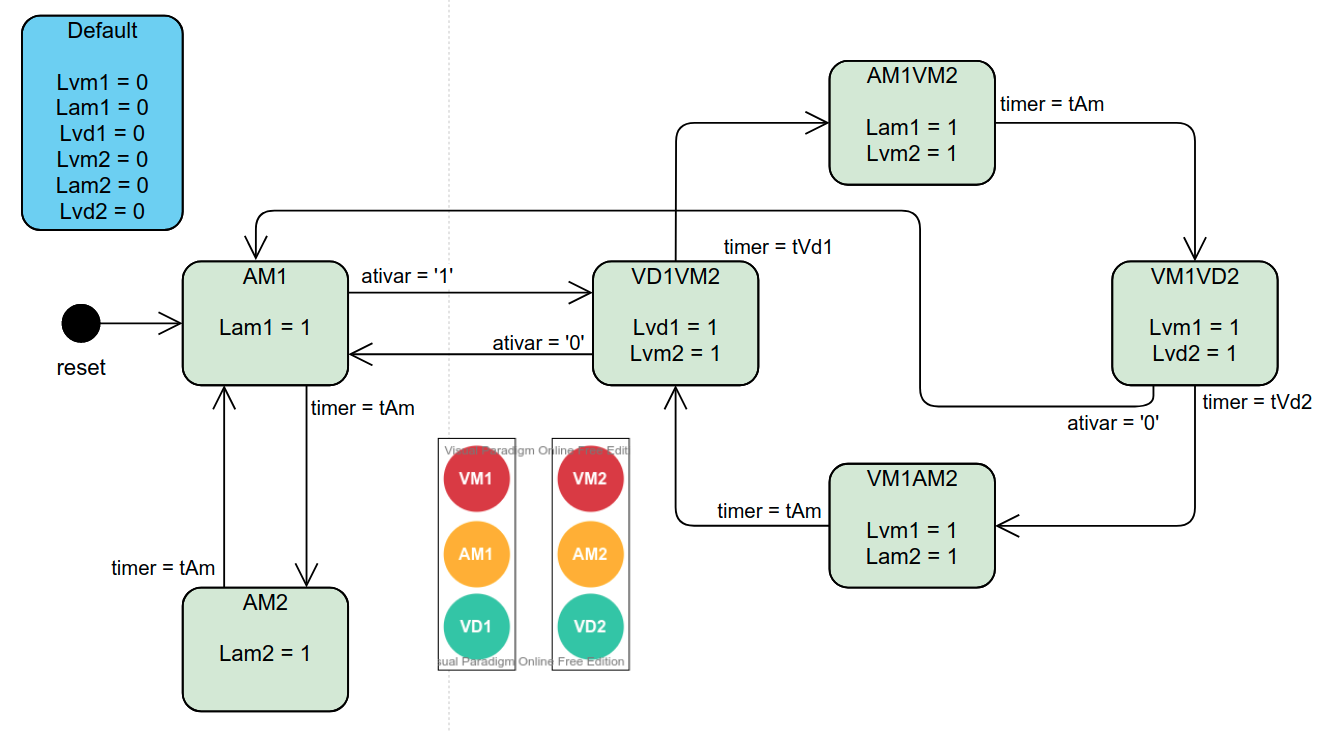

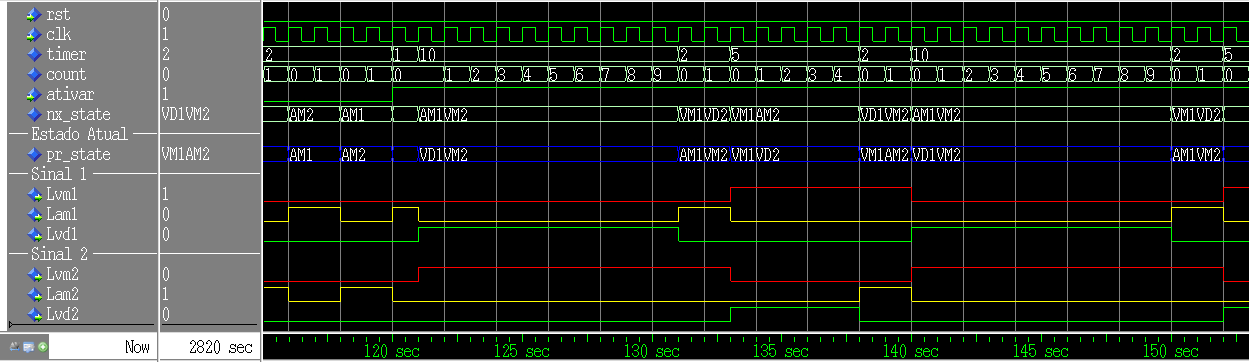

Unidade 7 - Maquinas de Estado Finitas

- 2 AULAS

| Unidade 7 - Maquinas de Estado Finitas | ||

|---|---|---|

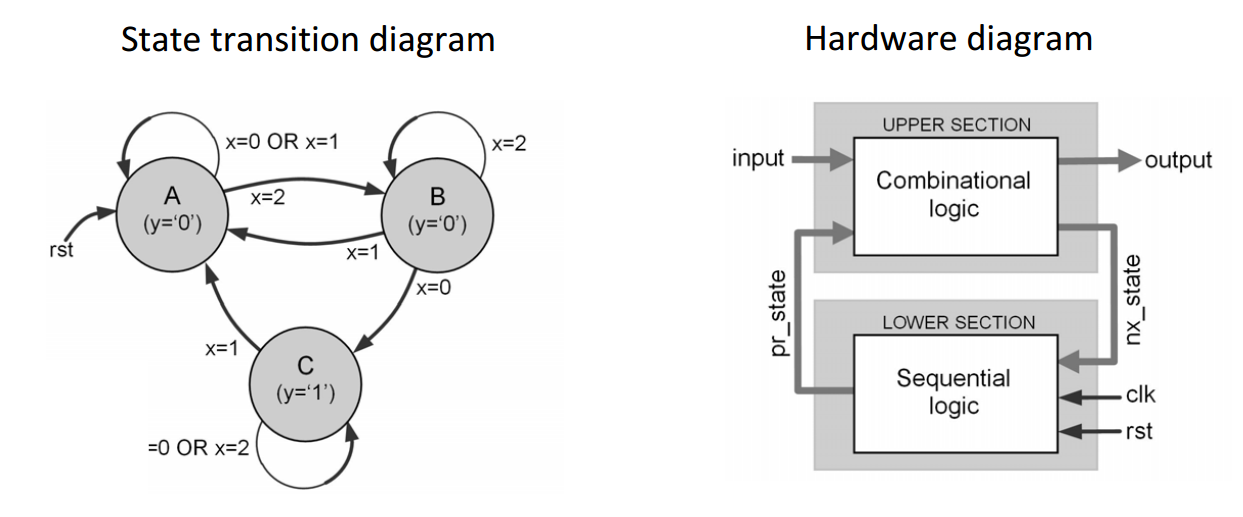

Figura 7.1 - Exemplo de diagrama de estados de uma FSM Fig11.1(a) e implementação em hardware da FSM Fig11.2(a)

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

----------------------------------------------------------

ENTITY < entity_name > IS

PORT (

clk, rst : IN STD_LOGIC;

entradas : IN < data_type > ;

saidas : OUT < data_type >);

END entity;

----------------------------------------------------------

ARCHITECTURE < architecture_name > OF < entity_name > IS

TYPE state IS (A, B, C, ...);

SIGNAL pr_state, nx_state : state;

-- ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute

-- ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential";

-- ATTRIBUTE SYN_ENCODING OF state : TYPE IS "safe";

BEGIN

------Logica Sequencial da FSM:------------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

pr_state <= A;

ELSIF rising_edge(clk) THEN

-- apenas na borda do "clk" ocorre a mudança de estado da FSM

pr_state <= nx_state;

END IF;

END PROCESS;

------Logica Combinacional da FSM:------------

PROCESS (pr_state, entradas)

BEGIN

------Valores default das saidas------------

saidas <= < valor > ;

CASE pr_state IS

WHEN A =>

-- é necessário um WHEN para definir as "saidas" durante cada estado

-- e analisar as "entradas" para definir o próximo estado

saidas <= < valor > ; -- apenas se diferente do valor default

IF (entradas = < valor >) THEN

nx_state <= B;

...

ELSE

nx_state <= A;

END IF;

WHEN B =>

saidas <= < valor > ; -- apenas se diferente do valor default

-- dependendo das "entradas", pode ser que hajam mais de um estados de destino

IF (entradas = < valor >) THEN

nx_state <= C;

ELSIF (entradas = < valor >) THEN

nx_state <= A;

ELSE

nx_state <= B;

END IF;

WHEN C =>

saidas <= < valor > ; -- apenas se diferente do valor default

-- a passagem para outro estado pode não depender de nenhuma "entrada"

nx_state <= C;

WHEN ...

END CASE;

END PROCESS;

------Seção de Saída (opcional):-------

-- Essa seção visa garantir que a saida new_output esteja sincronizada com o clk.

-- Se isso não for importante, ela pode ser suprimida

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

new_output <= < valor > ;

ELSIF rising_edge(clk) THEN --or falling_edge(clk)

new_output <= output;

END IF;

END PROCESS;

END architecture;

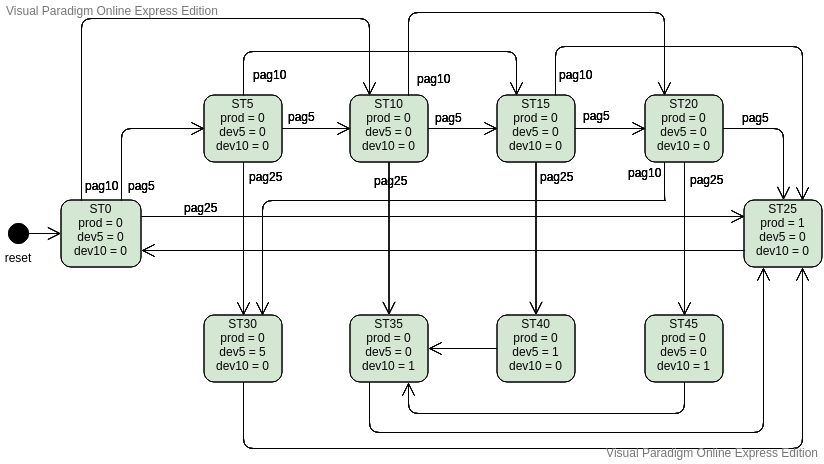

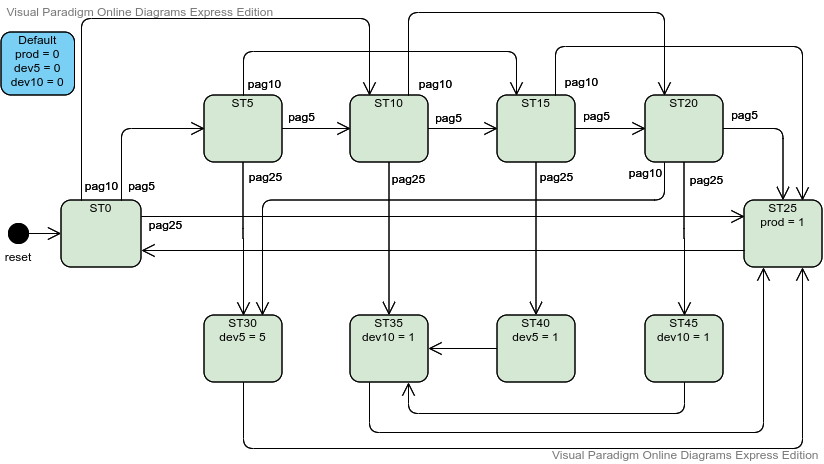

Figura 7.2 - FSM - Máquina de vender doces (diagrama de estados)  Figura 7.3 - FSM - Máquina de vender doces (diagrama de estados com default

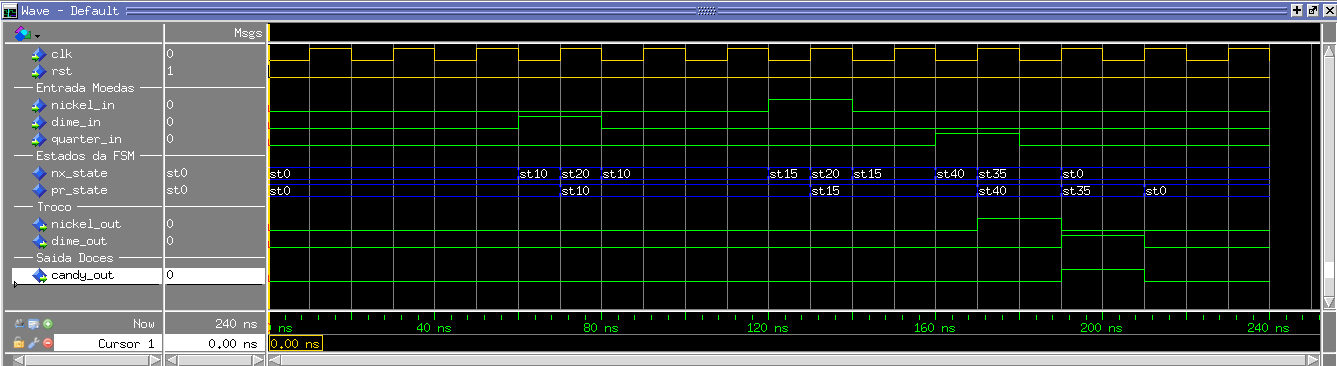

Figura 7.4 - FSM - Máquina de vender doces (simulação)

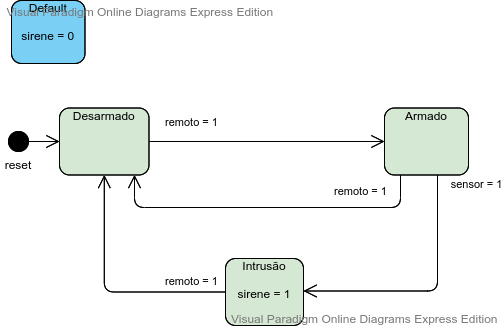

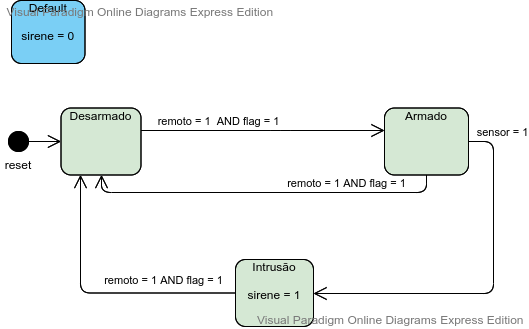

Figura 7.5 - FSM - alarme (oscilando entre os estados quando remoto é 1)

Figura 7.6 - FSM - alarme (solução com flag)

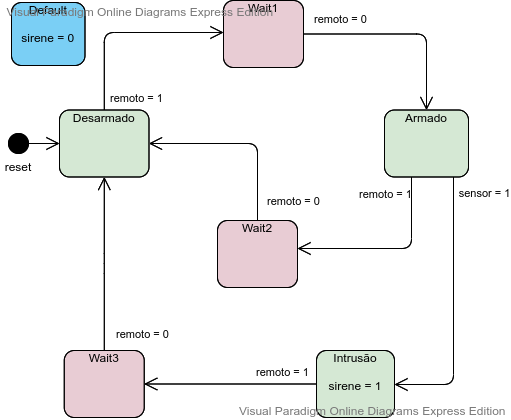

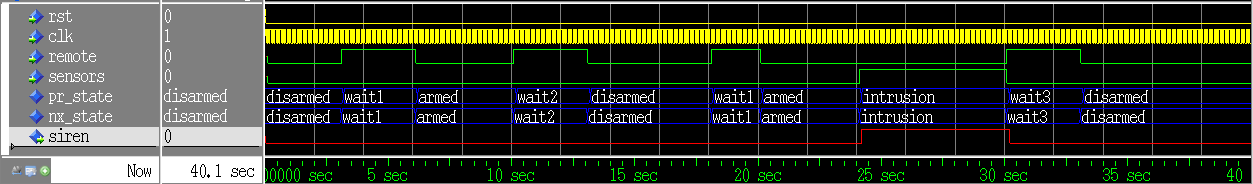

Figura 7.7 - FSM - alarme (solução com estados de WAIT)  Figura 7.8 - Simulação da FSM - alarme (solução com estados de WAIT)

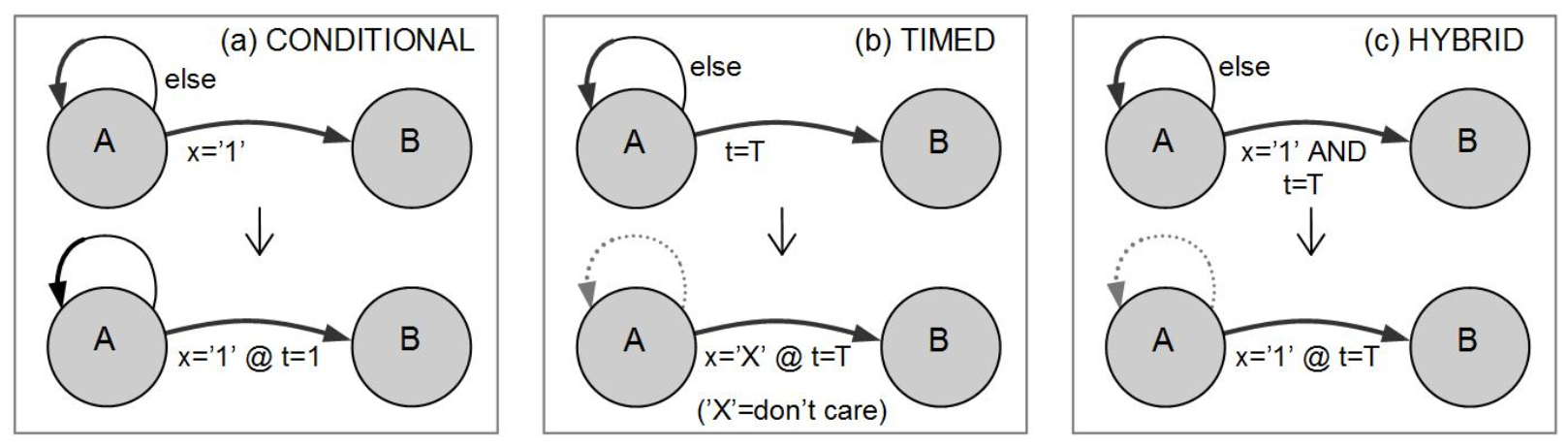

Figura 7.9 - Tipos de FSM (Condicional, Temporizada e Hibrida)

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

----------------------------------------------------------

ENTITY < entity_name > IS

PORT (

clk, rst : IN STD_LOGIC;

input : IN < data_type > ;

output : OUT < data_type >);

END entity;

----------------------------------------------------------

ARCHITECTURE < architecture_name > OF < entity_name > IS

TYPE state IS (A, B, C, ...);

SIGNAL pr_state, nx_state : state;

signal timer: integer range 0 to MAX;

-- ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute

-- ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential";

BEGIN

------Logica Sequencial da FSM:------------

PROCESS (clk, rst)

variable count: integer range o to MAX;

BEGIN

IF (rst = '1') THEN

pr_state <= A;

count := 0;

ELSIF (clk'EVENT AND clk = '1') THEN

count := count + 1;

if (count >= timer) then

pr_state <= nx_state;

count := 0;

end if;

END IF;

END PROCESS;

------Logica Combinacional da FSM:------------

PROCESS (pr_state, input)

BEGIN

------Valores default das saidas------------

output <= < value >;

------Valores default do timer------------

timer <= <value>;

CASE pr_state IS

WHEN A =>

output <= < value > ; -- apenas se diferente do valor default

IF (input =< value >) THEN

timer <= <value>; -- apenas se diferente do valor default

nx_state <= B;

...

ELSE

timer <= <value>; -- apenas se diferente do valor default

nx_state <= A;

END IF;

WHEN B =>

output <= < value > ; -- apenas se diferente do valor default

IF (input =< value >) THEN

timer <= <value>; -- apenas se diferente do valor default

nx_state <= C;

...

ELSE

timer <= <value>; -- apenas se diferente do valor default

nx_state <= B;

END IF;

WHEN ...

END CASE;

END PROCESS;

------Seção de Saída (opcional):-------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

new_output <= < value > ;

ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0'

new_output <= output;

END IF;

END PROCESS;

END architecture;

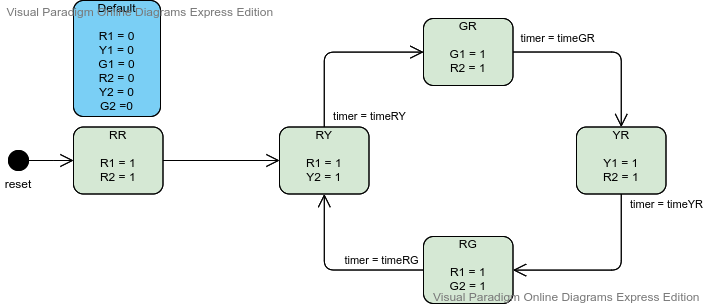

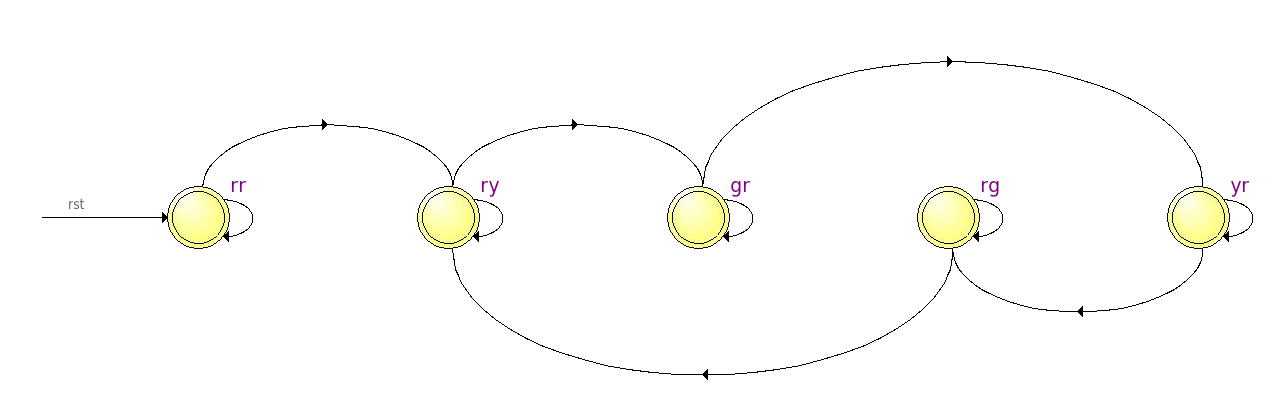

Figura 7.10 - Diagrama de estados do controlador de semáforo  Figura 7.11 - Simulação do controlador de semáforo no Modelsim

|

Unidade 8 - Testbench

- 2 ENCONTROS

| Unidade 8 - Testbench |

|---|

Avaliações

Nas avaliações A1 e A2 vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - Unidade 1 a Unidade 4: dia XX/XX

- A2 - Unidade 5 a Unidade 7: dia XX/XX

- PF - Entrega do projeto final: dia 15/12

- R12 - Recuperação de A1 e A2 : dia 12/12

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. Elas geram BÔNUS que são adicionados aos conceitos das avaliações A1 e A2.

Atividade extra-classe (AE)

A soma das atividades Extra-classe será correspondente a 30% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

- ↑ 1,0 1,1 1,2 1,3 1,4 PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,00 2,01 2,02 2,03 2,04 2,05 2,06 2,07 2,08 2,09 2,10 2,11 2,12 2,13 2,14 2,15 2,16 2,17 2,18 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335