DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke

Revisão de 07h39min de 23 de agosto de 2022 por Moecke (discussão | contribs) (→Unidade 6 - Projeto a nível de Sistema)

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 4 ENCONTROS

| Unidade 1 - Introdução a disciplina | ||||

|---|---|---|---|---|

|

|}

Unidade 3 - Tipos de Dados e Operadores em VHDL

|}

Unidade 4 - Código Concorrente

|}

Unidade 5 - Código Sequencial

|}

Unidade 6 - Projeto a nível de Sistema

|}

Unidade 7 - Maquinas de Estado Finitas

|}

Avaliações

Nas avaliações A1 e A2 serão realizadas de forma presencial e vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

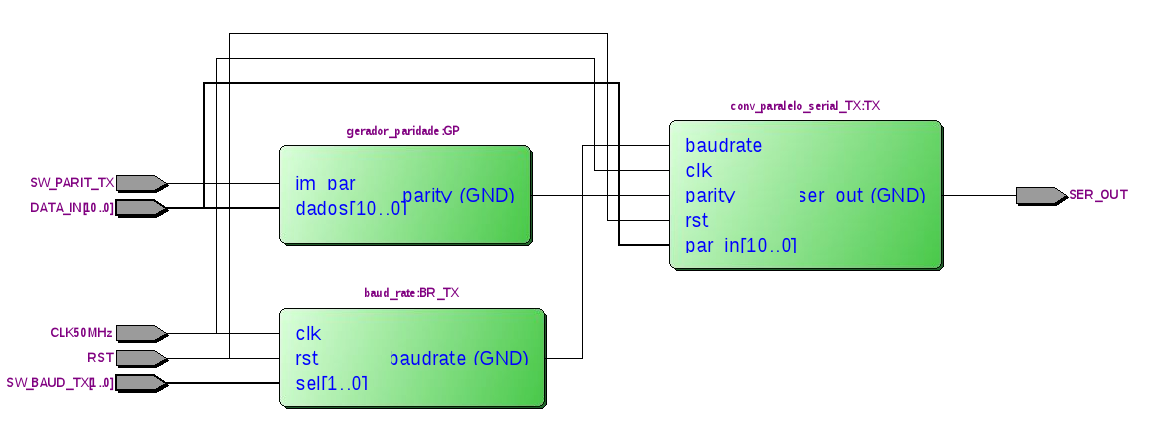

Figura 1 - Interface transmissora serial

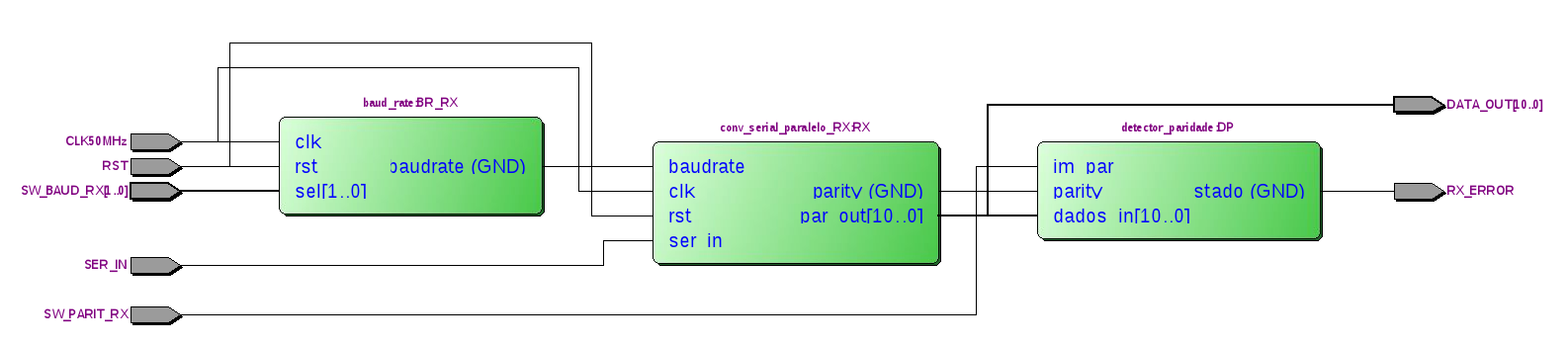

Figura 2 - Interface receptora serial

- A entrada DATA_IN deve ter apenas 8 bits e usar as chaves do kit como entrada de dados, e o valor deve ser mostrado em dois displays de sete segmentos em hexadecimal (0 a F)

- A saída DATA_OUT deve ter apenas 8 bits usar os leds como saída de dados, e o valor também deve ser mostrado em dois displays de sete segmentos em hexadecimal (0 a F)

- As taxa de transmissão deverão ser geradas a partir do clock principal CLK50MHz do kit a ser utilizado.

- A seleção da taxa de transmissão será feita através das chaves SW_BAUD_TX[1..0] para o transmissor e das SW_BAUD_RX[1..0] para o receptor.

- Por exemplo:

- 00 => 0.1 bps, 01 => 10 bps, 10 => 9600 bps, 11 => 100 kbps.

- Na transmissão deverá ser enviado um bit paridade (par ou impar) de acordo com a chave seletora SW_PARITY.

- 0 => paridade par, 1 => paridade impar.

- No receptor a saída RX_ERROR deve ser usada para indicar que houve erro na recepção do dado.

- O sistema no seu TOP LEVEL deverá ser constituído de um Conversor Paralelo Serial, um Conversor Serial Paralelo, dois Geradores de Baud Rate, um Gerador de Paridade, um Detector de Paridade, um Circuito de Entrada de Dados, e um Circuito de Saída de Dados.

- O projeto deve ser desenvolvido integrando estes componentes no TOP LEVEL, de modo que neste nível existam apenas conexões entre estes componentes. Recomenda-se utilizar também componentes para a criação dos circuitos no segundo nível. O reuso de componentes já desenvolvidos nas aulas é fortemente encorajado.

- Durante a fase das simulações recomenda-se alterar o valor da frequência do CLK50MHz para um clock menor de modo a viabilizar uma simulação mais rápida. As simulações de cada componente do TOP LEVEL e da integração de todos componentes no TOP LEVEL devem ser feitas no MODELSIM.

- O sistema deverá ser implementado, testado e demonstrado no kit de hardware FPGA DE2-115 usando as chaves e leds disponíveis e os pinos da GPIO para acionar circuitos externos. (opcional)

- O arquivo QAR do projeto, e os arquivos .do do MODELSIM devem ser enviados antecipadamente para o professor para conferencia antes da implementação no kit de hardware.

- Escreva um relatório técnico contendo os resultados em no máximo 10 paginas A4. O relatório além das tabelas com os dados de frequência máxima, número de componente, número de pinos, deverá conter a figura dos circuitos RTL da ENTITY top level com uma explicação do seu funcionamento. Também devem ser apresentadas as simulações funcionais e uma análise textual dos resultados obtidos. A descrição da função dos pinos no Kit DE2-115 também deve ser feita.

- Para entender o sistema de transmissão recomenda-se consulte materiais complementares sobre Comunicação serial assíncrona, bit de paridade, UART, Taxa de bits.

- Para o teste da transmissão serial pode ser utilizada a interface DB9 disponível nos computadores, em conjunto com o software minicom.

|}

ATIVIDADE EXTRA-CLASSE (AE)

A soma das atividades Extra-classe será correspondente a 20% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle da disciplinas, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

|}