Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

| Linha 2 366: | Linha 2 366: | ||

* 5 Encontros | * 5 Encontros | ||

{{collapse top| expand=true | Unidade 6 - Projeto a nível de Sistema}} | {{collapse top| expand=true | Unidade 6 - Projeto a nível de Sistema}} | ||

| − | + | <!-- | |

;Encontro 37 (17 nov.): | ;Encontro 37 (17 nov.): | ||

*Projeto a nível de Sistema. | *Projeto a nível de Sistema. | ||

| Linha 2 628: | Linha 2 628: | ||

:* Ver pag. 201 a 213 de <ref name="PEDRONI2010b"/> | :* Ver pag. 201 a 213 de <ref name="PEDRONI2010b"/> | ||

| − | |||

; Encontro 41 e 42 (16 jul. Sábado): | ; Encontro 41 e 42 (16 jul. Sábado): | ||

*[https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE7_-_Laborat.C3.B3rio_de_programa.C3.A7.C3.A3o_de_FPGA_-_Timer_000_a_999_.28vers.C3.A3o_2.29 AE7 - Laboratório de programação de FPGA - Timer 000 a 999 (versão 2) ] | *[https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE7_-_Laborat.C3.B3rio_de_programa.C3.A7.C3.A3o_de_FPGA_-_Timer_000_a_999_.28vers.C3.A3o_2.29 AE7 - Laboratório de programação de FPGA - Timer 000 a 999 (versão 2) ] | ||

| − | |||

::* Exercícios: 9.1 a 9.4, 9.6 a 9.9 | ::* Exercícios: 9.1 a 9.4, 9.6 a 9.9 | ||

:* Ver pag. 213 a 239 de <ref name="PEDRONI2010b"/>) | :* Ver pag. 213 a 239 de <ref name="PEDRONI2010b"/>) | ||

Edição das 12h56min de 25 de fevereiro de 2023

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 4 ENCONTROS

| Unidade 1 - Introdução a disciplina | ||||

|---|---|---|---|---|

|

|}

Unidade 3 - Tipos de Dados e Operadores em VHDL

- 8 Encontros

| Unidade 3 - Tipos de Dados e Operadores em VHDL |

|---|

|

Unidade 4 - Código Concorrente

- 3 Encontros

| Unidade 4 - Código Concorrente |

|---|

Unidade 5 - Código Sequencial

- 5 ENCONTROS

| Unidade 5 - Código Sequencial |

|---|

Unidade 6 - Projeto a nível de Sistema

- 5 Encontros

| Unidade 6 - Projeto a nível de Sistema |

|---|

Unidade 7 - Maquinas de Estado Finitas

| Unidade 7 - Maquinas de Estado Finitas | ||

|---|---|---|

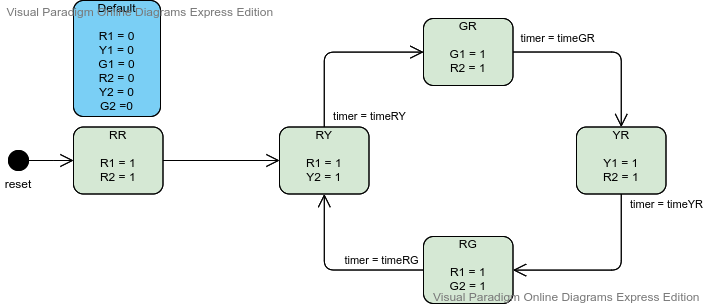

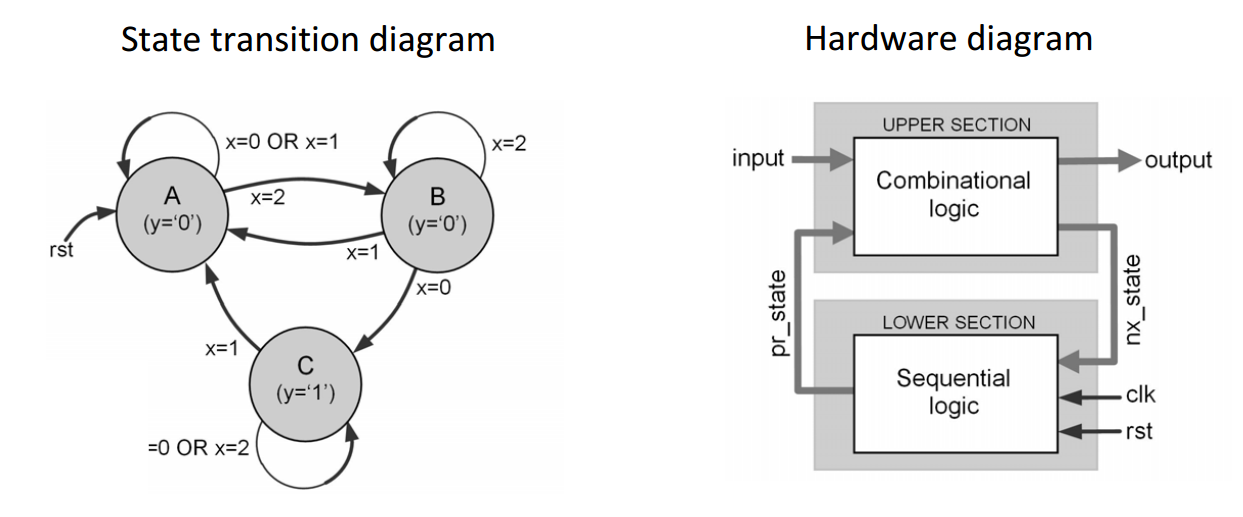

Figura 7.1 - Exemplo de diagrama de estados de uma FSM Fig11.1(a) e implementação em hardware da FSM Fig11.2(a)

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

----------------------------------------------------------

ENTITY < entity_name > IS

PORT (

clk, rst : IN STD_LOGIC;

input : IN < data_type > ;

output : OUT < data_type >);

END entity;

----------------------------------------------------------

ARCHITECTURE < architecture_name > OF < entity_name > IS

TYPE state IS (A, B, C, ...);

SIGNAL pr_state, nx_state : state;

-- ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute

-- ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential";

-- ATTRIBUTE SYN_ENCODING OF state : TYPE IS "safe";

BEGIN

------Logica Sequencial da FSM:------------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

pr_state <= A;

ELSIF (clk'EVENT AND clk = '1') THEN

pr_state <= nx_state;

END IF;

END PROCESS;

------Logica Combinacional da FSM:------------

PROCESS (pr_state, input)

BEGIN

------Valores default das saidas------------

output <= < value > ;

CASE pr_state IS

WHEN A =>

output <= < value > ; -- apenas se diferente do valor default

IF (input =< value >) THEN

nx_state <= B;

...

ELSE

nx_state <= A;

END IF;

WHEN B =>

output <= < value > ; -- apenas se diferente do valor default

IF (input =< value >) THEN

nx_state <= C;

...

ELSE

nx_state <= B;

END IF;

WHEN ...

END CASE;

END PROCESS;

------Seção de Saída (opcional):-------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

new_output <= < value > ;

ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0'

new_output <= output;

END IF;

END PROCESS;

END architecture;

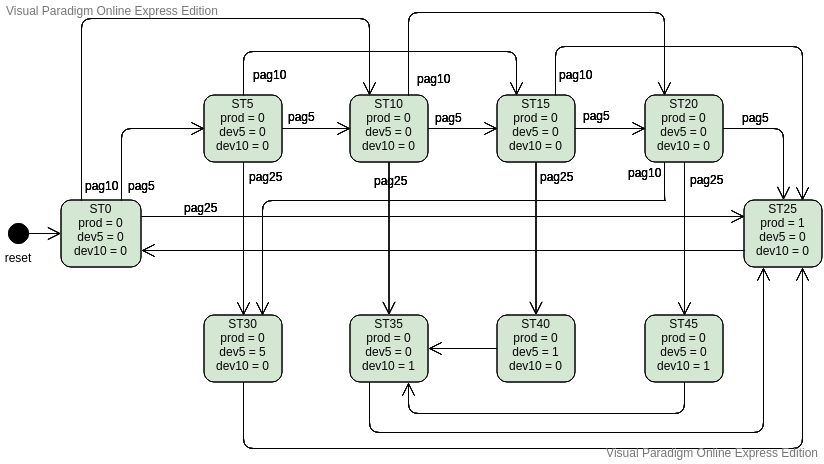

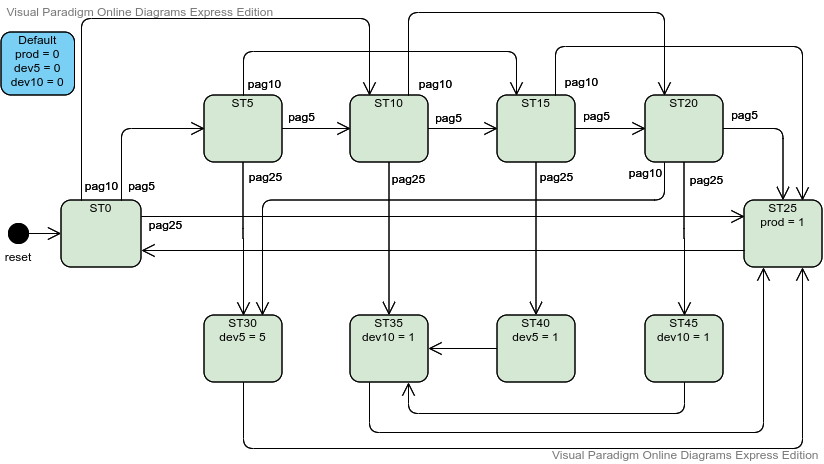

Figura 7.2 - FSM - Máquina de vender doces (diagrama de estados)  Figura 7.3 - FSM - Máquina de vender doces (diagrama de estados com default

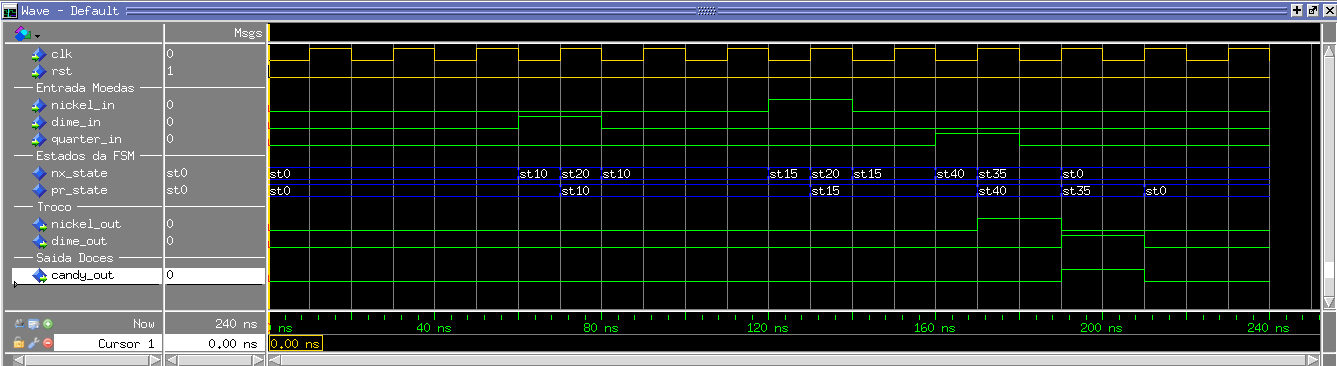

Figura 7.4 - FSM - Máquina de vender doces (simulação)

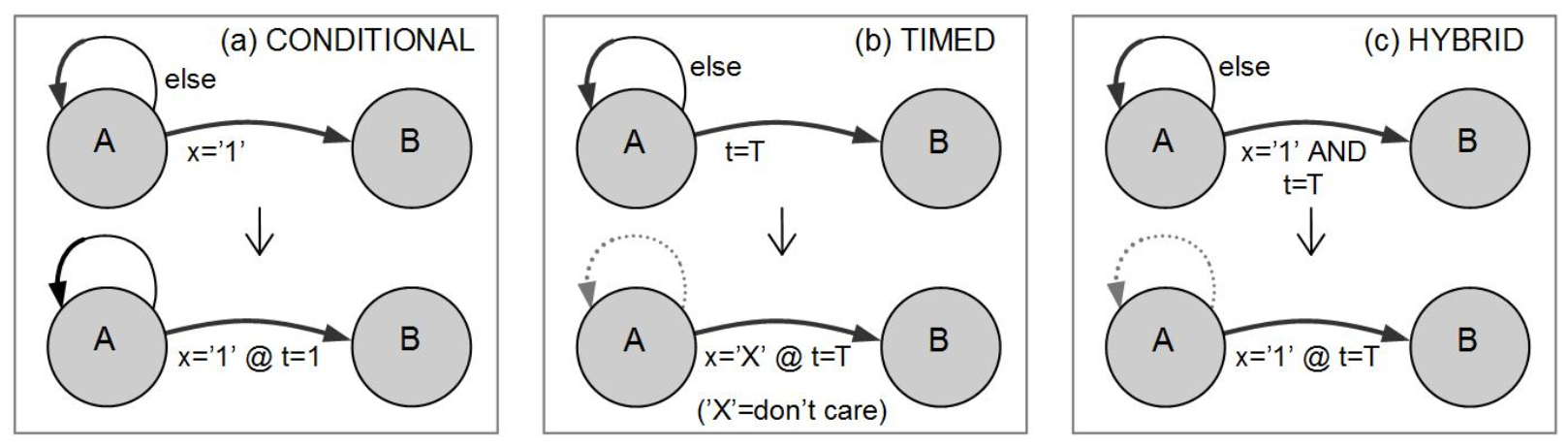

Figura 7.9 - Tipos de FSM (Condicional, Temporizada e Hibrida)

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

----------------------------------------------------------

ENTITY < entity_name > IS

PORT (

clk, rst : IN STD_LOGIC;

input : IN < data_type > ;

output : OUT < data_type >);

END entity;

----------------------------------------------------------

ARCHITECTURE < architecture_name > OF < entity_name > IS

TYPE state IS (A, B, C, ...);

SIGNAL pr_state, nx_state : state;

signal timer: integer range 0 to MAX;

-- ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute

-- ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential";

BEGIN

------Logica Sequencial da FSM:------------

PROCESS (clk, rst)

variable count: integer range o to MAX;

BEGIN

IF (rst = '1') THEN

pr_state <= A;

count := 0;

ELSIF (clk'EVENT AND clk = '1') THEN

count := count + 1;

if (count >= timer) then

pr_state <= nx_state;

count := 0;

end if;

END IF;

END PROCESS;

------Logica Combinacional da FSM:------------

PROCESS (pr_state, input)

BEGIN

------Valores default das saidas------------

output <= < value >;

------Valores default do timer------------

timer <= <value>;

CASE pr_state IS

WHEN A =>

output <= < value > ; -- apenas se diferente do valor default

IF (input =< value >) THEN

timer <= <value>; -- apenas se diferente do valor default

nx_state <= B;

...

ELSE

timer <= <value>; -- apenas se diferente do valor default

nx_state <= A;

END IF;

WHEN B =>

output <= < value > ; -- apenas se diferente do valor default

IF (input =< value >) THEN

timer <= <value>; -- apenas se diferente do valor default

nx_state <= C;

...

ELSE

timer <= <value>; -- apenas se diferente do valor default

nx_state <= B;

END IF;

WHEN ...

END CASE;

END PROCESS;

------Seção de Saída (opcional):-------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

new_output <= < value > ;

ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0'

new_output <= output;

END IF;

END PROCESS;

END architecture;

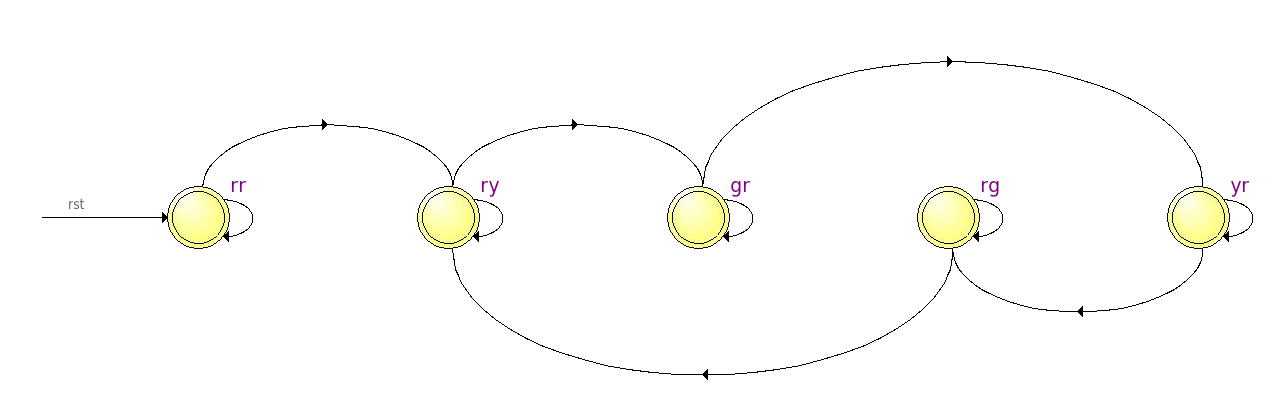

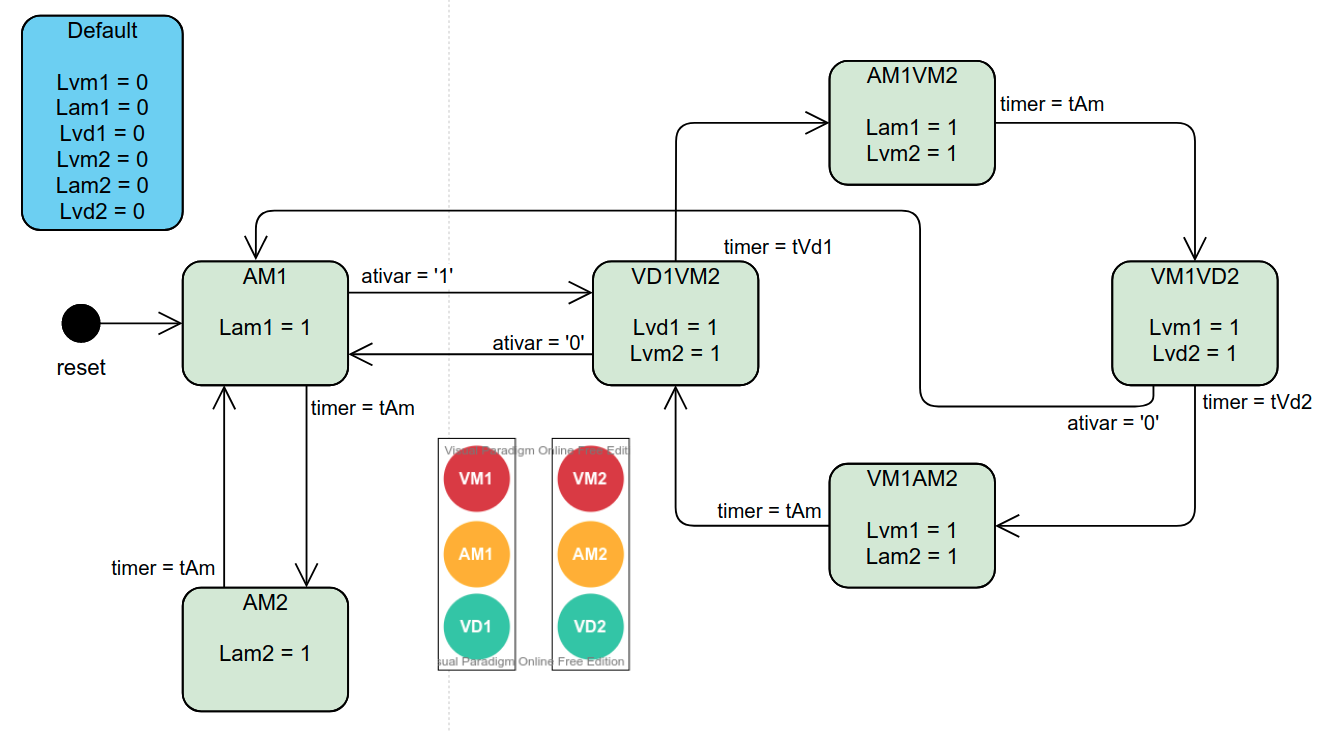

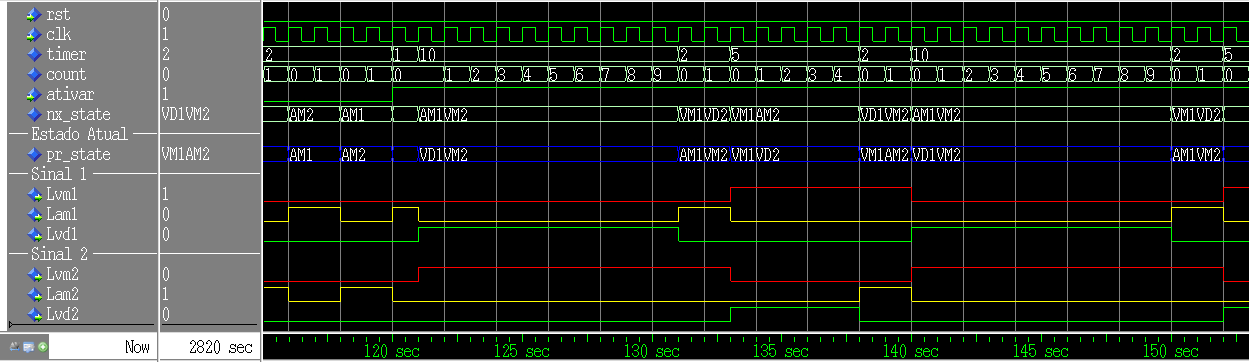

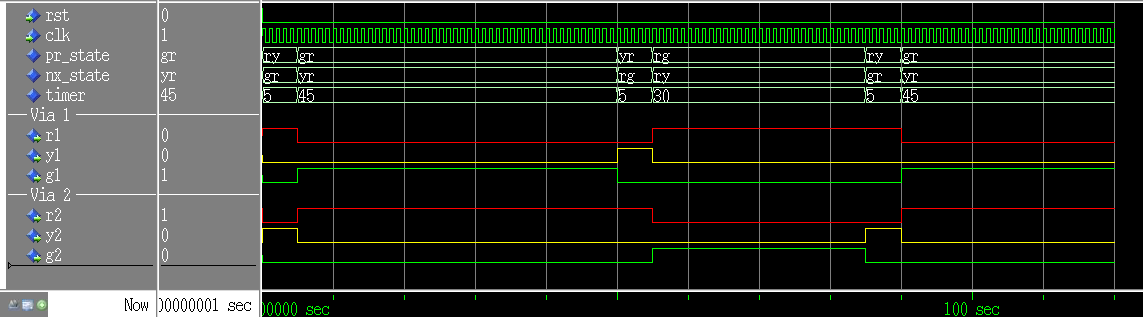

Figura 7.10 - Diagrama de estados do controlador de semáforo  Figura 7.11 - Simulação do controlador de semáforo no Modelsim

Figura 7.14 - Simulação do controlador de semáforo no Modelsim  |

Unidade 8 - Testbench

| Unidade 8 - Testbench |

|---|

/opt/intelFPGA/20.1/modelsim_ae/linuxaloem/vsim

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY semaforo_vhd_tst IS

END semaforo_vhd_tst;

ARCHITECTURE semaforo_arch OF semaforo_vhd_tst IS

-- constants

-- signals

SIGNAL ativar : STD_LOGIC;

SIGNAL clk : STD_LOGIC;

SIGNAL lam1 : STD_LOGIC;

SIGNAL lam2 : STD_LOGIC;

SIGNAL lvd1 : STD_LOGIC;

SIGNAL lvd2 : STD_LOGIC;

SIGNAL lvm1 : STD_LOGIC;

SIGNAL lvm2 : STD_LOGIC;

SIGNAL rst : STD_LOGIC;

COMPONENT semaforo

PORT (

ativar : IN STD_LOGIC;

clk : IN STD_LOGIC;

lam1 : OUT STD_LOGIC;

lam2 : OUT STD_LOGIC;

lvd1 : OUT STD_LOGIC;

lvd2 : OUT STD_LOGIC;

lvm1 : OUT STD_LOGIC;

lvm2 : OUT STD_LOGIC;

rst : IN STD_LOGIC

);

END COMPONENT;

BEGIN

i1 : semaforo

PORT MAP (

-- list connections between master ports and signals

ativar => ativar,

clk => clk,

lam1 => lam1,

lam2 => lam2,

lvd1 => lvd1,

lvd2 => lvd2,

lvm1 => lvm1,

lvm2 => lvm2,

rst => rst

);

init : PROCESS

-- variable declarations

BEGIN

-- code that executes only once

WAIT;

END PROCESS init;

always : PROCESS

-- optional sensitivity list

-- ( )

-- variable declarations

BEGIN

-- code executes for every event on sensitivity list

WAIT;

END PROCESS always;

END semaforo_arch;

vcom -93 -work work {../../semaforo.vhd}

vsim work.semaforo

do wave_curto.do

force -freeze sim:/semaforo/rst 1 0, 0 10

force -freeze sim:/semaforo/clk 1 0, 0 {0.5sec} -r 1sec

force -freeze sim:/semaforo/ativar 0 0, 1 10.3sec, 0 55.5sec, 1 70sec, 0 106.22sec, 1 120sec

run 150sec

-- DECLARAR

constant tclk: time := 1 ns;

signal clk : std_logic := '0';

-- CLOCK COM PERIODO DE 2*tclk (COM CÓDIGO CONCORRENTE)

clk <= not clk after tclk;

-- CLOCK COM PERIODO DE 2*tclk (COM CÓDIGO SEQUENCIAL)

PROCESS

BEGIN

clk <= '1';

wait for tclk;

clk <= '0';

wait for tclk;

END PROCESS;

-- DECLARAR

constant treset: time := 100 ps;

signal reset : std_logic;

-- RESET COM DURAÇÃO DE treset (COM CÓDIGO CONCORRENTE)

reset <= '1', '0' after treset;

-- RESET COM DURAÇÃO DE treset (COM CÓDIGO SEQUENCIAL)

PROCESS

BEGIN

reset <= '1';

wait for treset;

reset <= '0';

wait;

END PROCESS;

-- DECLARAR

constant t_a: time := 100 ps;

constant Nbits: natural := 8;

signal a : std_logic_vector(Nbits-1 downto 0);

-- GERAÇÂO DO SINAL a = [0 1 2 3 4 ...] COM DURAÇÃO DE t_a em cada valor (COM CÓDIGO SEQUENCIAL)

PROCESS

BEGIN

for i in 0 to 2**Nbits-1 loop

a <= std_logic_vector(to_unsigned(i,Nbits));

wait for t_a;

end loop;

END PROCESS;

No exemplo abaixo é utilizado um tipo de Linear-feedback shift register -- DECLARAR

constant t_a: time := 100 ps;

constant Nbits: natural := 8;

signal a : std_logic_vector(Nbits-1 downto 0) := (0 => '1', 3 => '1', others => '0');

-- GERAÇÂO DO SINAL a COM DURAÇÃO DE t_a em cada valor (COM CÓDIGO SEQUENCIAL)

-- USANDO UM CONTADOR LFSR

PROCESS

BEGIN

for i in 0 to 2**Nbits-1 loop

a <= (a(0) xor a(2) xor a(3) xor a(4)) & a(Nbits-1 downto 1); -- para 8 bits

wait for t_a;

end loop;

END PROCESS;

|

-->

Avaliações

Nas avaliações A1 e A2 serão realizadas de forma presencial e vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - Unidade 1 a Unidade 4: dia 1/11

- A2 - Unidade 5 a Unidade 7: dia XX/12

- PF - Projeto Final: dia 13/12

- R12 - Recuperação A1 e A2 : dia 15/12

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. Elas geram BÔNUS que são adicionados aos conceitos das avaliações A1 e A2.

Atividade extra-classe (AE)

A soma das atividades Extra-classe será correspondente a 20% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

AE1 - Palavras-cruzadas INTRODUÇÃO

| AE1 - Palavras-cruzadas INTRODUÇÃO |

|---|

AE2 - Conhecendo os dispositivos lógicos programáveis

| AE2 - Conhecendo os dispositivos lógicos programáveis |

|---|

ATENÇÃO: Se está com problemas com a simulação funcional, veja esta página Quartus Prime QSIM problems

|

- ↑ 1,0 1,1 1,2 1,3 1,4 PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,0 2,1 2,2 2,3 2,4 2,5 2,6 2,7 2,8 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335