|

|

| Linha 276: |

Linha 276: |

| | {{fig|2.5|RTL 4 FF| RTL_4FF.png| 400 px |}} | | {{fig|2.5|RTL 4 FF| RTL_4FF.png| 400 px |}} |

| | | | |

| − | <!--

| + | ;Aula 6 (21 out): |

| − | ;Aula 6 e 7 (24 e 25 mai): | + | *Realização da atividade AE2 no laboratório. |

| | + | *Primeira aula presencial depois da longa Pandemia |

| | + | |

| | + | ===ATUAL=== |

| | + | ;Aula 7 (26 out): |

| | * Uso de alguns sites auxiliares para a programação em VHDL: | | * Uso de alguns sites auxiliares para a programação em VHDL: |

| | :*[[Preparando para gravar o circuito lógico no FPGA]] | | :*[[Preparando para gravar o circuito lógico no FPGA]] |

| Linha 309: |

Linha 313: |

| | <big> Video motivational para apreender FPGA, VHDL [https://youtu.be/ecyyZ6zTLic Microsoft's Bing* Intelligent Search with Intel® FPGAs] </big> | | <big> Video motivational para apreender FPGA, VHDL [https://youtu.be/ecyyZ6zTLic Microsoft's Bing* Intelligent Search with Intel® FPGAs] </big> |

| | | | |

| | + | <!-- |

| | ;Aula 8 (27 mai): | | ;Aula 8 (27 mai): |

| | * Uso das bibliotecas no VHDL. | | * Uso das bibliotecas no VHDL. |

Edição das 09h41min de 26 de outubro de 2021

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

| Unidade 1 - Introdução a disciplina

|

- Aula 1 (6 Out)

- APRESENTAÇÃO DA DISCIPLINA

- Os materiais, prazos, documentação, histórico de trabalhos anteriores estão publicados nesta wiki.

- A PÁGINA DA DISCIPLINA contem os materiais que não alteram entre semestre.

- Nesta página está o REGISTRO DIÁRIO E AVALIAÇÕES.

- Para a realização e entrega das atividades será utilizada a PLATAFORMA MOODLE. Chave para auto inscrição (engtelecom_aluno)

- Durante a pandemia do COVID19 os encontros síncronos serão realizados através da plataforma Google Meet. Os encontros (havendo a concordância de todos) serão gravados, e ocorrerão nos horários normais das aulas. As aulas terão duração de 1h15 minutos com possibilidade de ainda acrescer 15 minutos previstos para esclarecimento de dúvidas. As gravações ficarão disponíveis por 30 dias no Drive do aluno, mas não poderão ser baixadas por limitação do sistema.

- Além dos horários de aula síncrona, serão agendados horários de ATENDIMENTO EXTRACLASSE para que os alunos possam tirar dúvidas da disciplina ou das ferramentas de ensino.

- Para a comunicação entre professor-aluno, além dos avisos do Sistema Acadêmimco (SIGAA), utilizaremos a plataforma SLACK. Sugere-se que os alunos também a utilizem para comunicação entre eles, principalmente nos trabalhos em equipe.

- Aula 2 (7 Out)

- Introdução aos dispositivos lógicos programáveis:

-

- SPLD: PAL, PLA e GAL

- CPLDs

-

- Fabricantes de DLPs/FPGAs e familias de DLPs atuais.

-

- Aula 3 (14 out)

- Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, RAM, DSP, Clock, PLL, I/O

- Leituras complementares para a unidade

- Historia, processo de produção dos chips.

- Curiosidades do mundo digital

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

|

- Aula 4 (19 out)

- Introdução ao VHDL e ambiente EDA - QUARTUS

- Estrutura do código VHDL

- Declaração das bibliotecas e pacotes LIBRARY / PACKAGE

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

- Exemplo - Declaração de uma porta NAND em VHDL

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

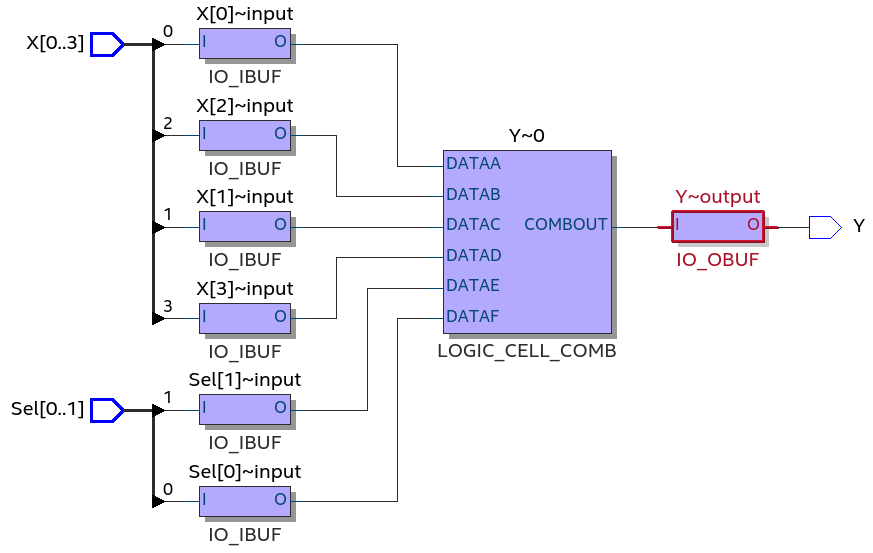

Exemplo de descrição de um multiplexador de 4 entradas

entity mux_novo is

port

(

-- Input ports

X: in bit_vector (3 downto 0);

S : in bit_vector (1 downto 0);

-- Output ports

Y : out bit

);

end entity mux_novo;

-- Implementação com lógica pura

architecture v_logica_pura of mux_novo is

begin

Y <= (X(0) and (not S(1)) and (not S(0))) or

(X(1) and (not S(1)) and (S(0))) or

(X(2) and (S(1)) and (not S(0))) or

(X(3) and (S(1)) and (S(0)));

end architecture Logica_pura;

-- Implementação com WHEN ELSE

architecture v_WHEN of mux_novo is

begin

Y <= X(0) when S = "00" else

X(1) when S = "01" else

X(2) when S = "10" else

X(3);

end architecture v_WHEN;

-- Implementação com WITH SELECT

architecture v_WITH_SELECT of mux_novo is

begin

with S select

Y <= X(0) when "00", -- note o uso da ,

X(1) when "01",

X(2) when "10",

X(3) when others; -- note o uso de others, para todos os demais valores.

-- Não pode ser substituido por "11" mesmo que o signal seja bit_vector.

end architecture v_WITH_SELECT;

-- Implementação com IF ELSE

architecture v_IF_ELSE of mux_novo is

begin

-- Uma arquitetura vazia como essa é denominada de STUB,

-- Pode ser utilizada em um projeto durante para conferir as conexões externas.

-- Posteriormente a arquitetura será descrita.

end architecture v_IF_ELSET;

-- Design Unit que associa a architecture com a entity

configuration cfg_ifsc of mux_novo is

-- for v_WITH_SELECT end for;

for v_WHEN end for;

end configuration;

- Aula 5 (20 out)

- Faça a análise e sintese do mux_novo, associando a architecture v_logica_pura, depois v_WITH_SELECT, depois v_WHEN e por último v_IF_ELSE.

- Note a diferença entre os RTL Viewer obtidos para cada architecture.

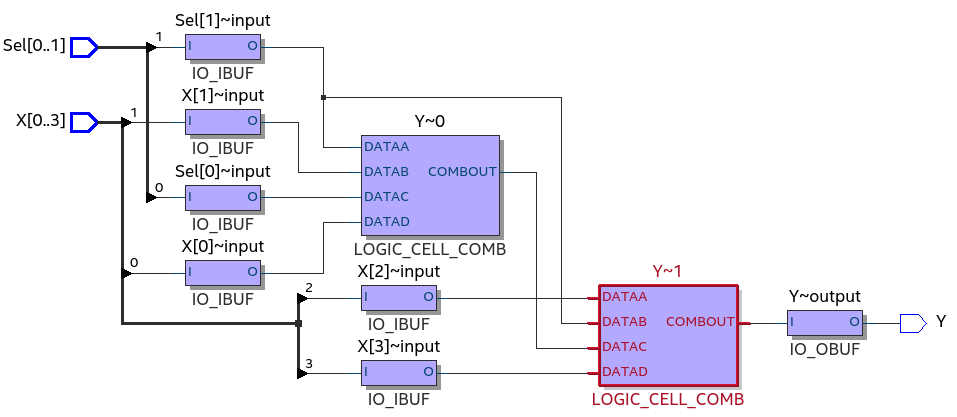

Figura 2.1 - Código RTL do mux 4x1 v_logica_pura

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

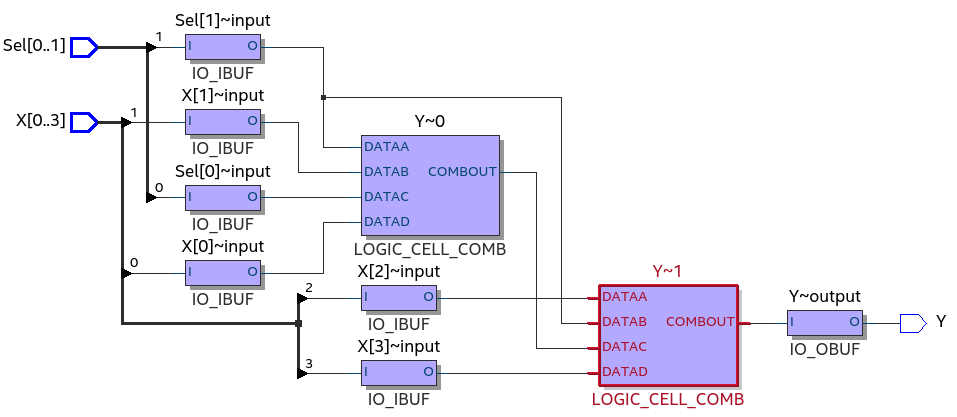

Figura 2.2 - Código RTL do mux 4x1 v_WHEN

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura 2.3 - Código RTL do mux 4x1 v_WITH_SELECT

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- OBS: Register Transfer-Level (RTL) é uma abstração na qual o circuito é descrito em termos de fluxo de sinais entre os registradores presentes no hardware e as operações combinacionais realizadas com esses dados.

- Note a que ao verificar o Technology Map Viewer, nos 3 primeiros casos serão usados os mesmos elementos lógicos.

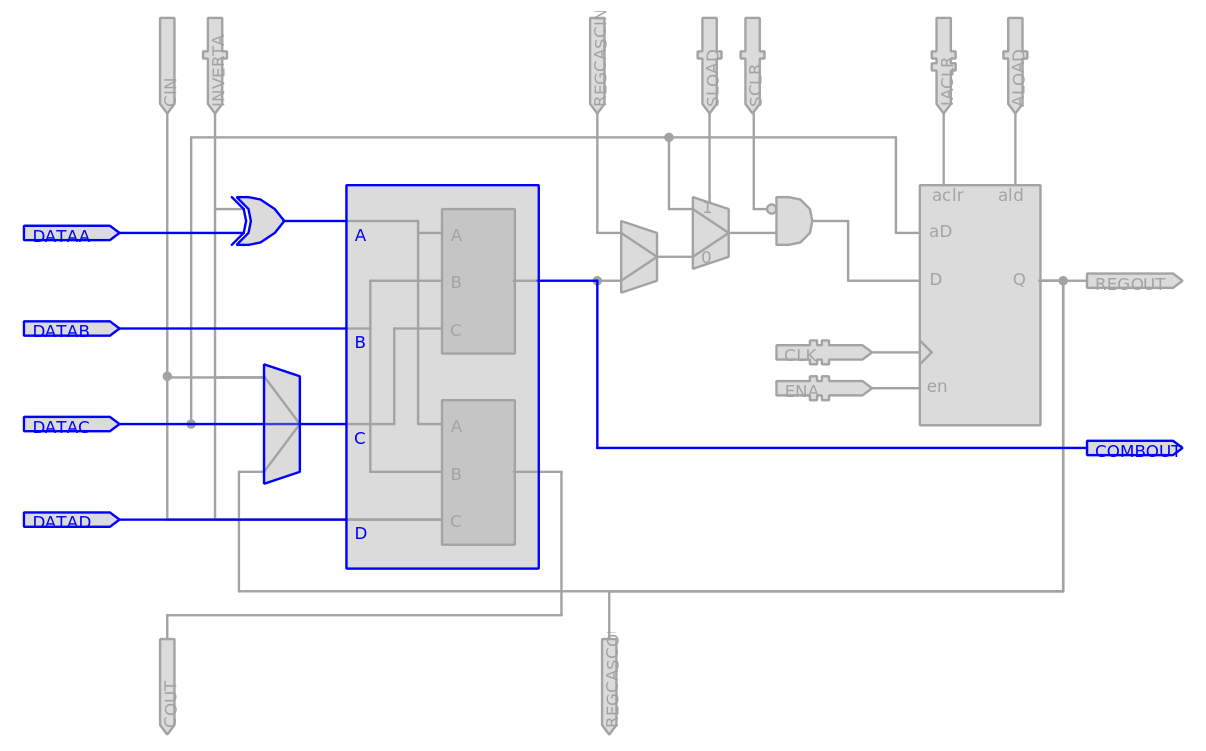

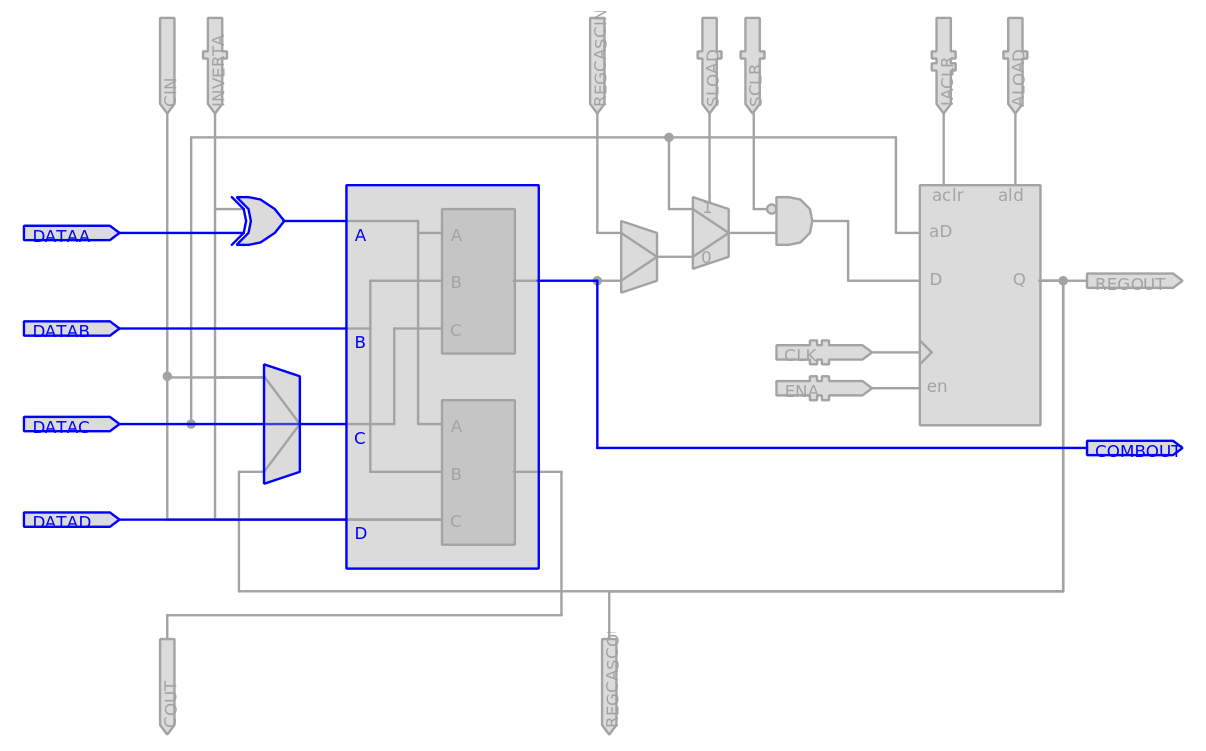

Figura 2.4 - Technology Map do mux 4x1 para a família Cyclone

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Note que o elemento lógico acima possui uma LUT (LookUp Table) que basicamente implementa o circuito combinacional através de uma tabela de consulta (Tabela Verdade), a qual pode ser visualizada clicando com o botão Direito do Mouse e selecionando Properties, juntamente com Mapa de Karnaugh e seu Circuito Lógico representado por portas. Todas as representações são equivalentes.

Figura 2.5 - Elemento Lógico usado no mux 4x1 para a família Cyclone (node properties)

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Dependendo da família de FPGA que se estiver usando, o compilador implementar o circuito descrito com um número diferente de elementos lógicos (LEs). No caso da família Cyclone, na qual a LUT tem 4 entradas, são necessários 2 LEs para mapear uma lógica combinacional com 6 entradas e 1 saída (Mux4x1).

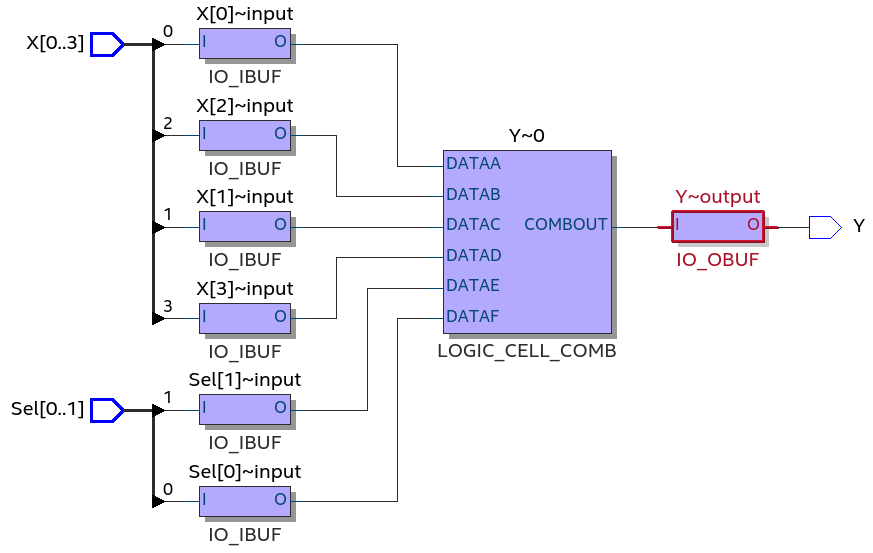

No entanto se utilizarmos um dispositivo FPGA da família Stratix III, que tem LUT tem 6 entradas, será necessário apenas 1 LE, conforme ilustrado a seguir.

Figura 2.5 - Technology Map do mux 4x1 para a família Stratix III

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Exemplo 2.2 (VHDL) - programação de um flip-flop

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

Figura 2.2 - Código RTL do Exemplo 2.2

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Use o Technology Map Viewer para ver a como o circuito foi mapeado para os elementos lógicos disponíveis no dispositivo FPGA selecionado (EP1C3T100A8)

Figura 2.3 - Technology Map do Exemplo 2.2

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura 2.4 - Chip Planner do Exemplo 2.2

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Modifique o circuito do flip-flop para que ele passe a ter 4 flip-flops

Figura 2.5 - RTL 4 FF

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Aula 6 (21 out)

- Realização da atividade AE2 no laboratório.

- Primeira aula presencial depois da longa Pandemia

ATUAL

- Aula 7 (26 out)

- Uso de alguns sites auxiliares para a programação em VHDL:

- Exemplo de um contador em VHDL. COUNTER na página de VHDL da Wikipedia.

- Objetivos: Copiar e colar o código no Quartus; diferença entre analise e síntese e compilação; observar o RTL (usar UNGROUP); simulação funcional e simulação temporal; observar os atrasos de propagação na simulação temporal.

- Revisitando o Básico de simulação funcional e temporal com o QSIM.

- Realize as simulações funcional e temporal do circuito Flip-Flop4 ou Counter usando o QSIM.

Figura 2.6 - Simulação Funcional de 4 FF 100ns

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura 2.7 - Simulação Temporal de 4 FF 100ns

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças.

IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possível verificar se o circuito atende as restrições de tempo.

- Para definir as restrições de tempo do clock por exemplo, pode ser adicionado um arquivo .sdc ao projeto definindo a frequência do clock esperada através da seguinte linha:

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

Video motivational para apreender FPGA, VHDL Microsoft's Bing* Intelligent Search with Intel® FPGAs

|

Avaliações

Nas avaliações A1 e A2 serão realizadas de forma presencial e vocês poderão consultar apenas as folhas entregues:

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

A soma das atividades Extra-classe será correspondente a 25% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle da disciplinas, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

| AE1 - Palavras-cruzadas INTRODUÇÃO

|

AE1 - Palavras-cruzadas INTRODUÇÃO

- BÔNUS

- 0,3 pontos na avaliação A1 -

- 0,2 pontos na avaliação A1 -

- 0,1 pontos na avaliação A1 -

|

| AE2 - Conhecendo os dispositivos lógicos programáveis

|

AE2 - Conhecendo os dispositivos lógicos programáveis

- Atividade

- Ao escolher a família de FPGAS, escolha inicialmente um dispositivo da família Cyclone II.

- Capture as telas solicitadas e depois utilize-as em um relatório da atividade.

- Anote o tempo utilizado para cada uma das etapas do processo de compilação

- Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo.

- Anote algum erro (Error) ou alertas (Warnings) que o Quartus II indicar no painel de mensagens [Messages]

- Ao final salve o projeto em um arquivo QAR (sugestão PJ1.QAR)

- Em seguida escolha um dos seguintes dispositivos e repita todo o procedimento:

- Modifique a família para Cyclone IV E e use um dispositivo para EP4CE****, e observe as mudanças que ocorre tanto no tipo de Elemento Lógico, no Chip Planner, e no Pin Planner, e no circuito dos pinos de I/O. Note que este FPGA também apresenta novos componentes, tais como: Memória, Multiplicadores, PLLs. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documento o que encontrar.

- Modifique a família para Stratix II GX e use o dispositivo para EP2SGX****, e observe as mudanças que ocorre tanto no tipo de Elemento Lógico, no Chip Planner, e no Pin Planner, e no circuito dos pinos de I/O. Note que este FPGA também apresenta novos componentes, tais como: Memória, Elementos DSP, PLL, DLL. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documento o que encontrar.

- Procure comparar os resultados obtidos nos dois procedimentos.

- Entregas

- Envie dois arquivos QAR contendo todos os arquivos necessário para compilar os dois projetos.

- Envie um relatório em PDF, incluindo as imagens capturadas (inclua legenda em cada figura) e escreva para cada imagem um texto comentando o que representa. O relatório também deve ter a identificação (autor, título, data) uma breve introdução e uma conclusão. A descrição dos procedimentos feita na página wiki não precisa incluída no relatório.

- Use preferencialmente o Overleaf para gerar o relatório. Mas o uso de MS-Word, Libreoffice e Google Docs também é permitida.

- A entrega será feita através do Moodle da disciplina. Observe o prazo de entrega.

|

- ↑ 1,0 1,1 1,2 1,3 1,4 PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,0 2,1 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335