Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

(→ATUAL) |

(→ATUAL) |

||

| Linha 64: | Linha 64: | ||

;PARA O PRÓXIMO ENCONTRO: | ;PARA O PRÓXIMO ENCONTRO: | ||

| − | * | + | * Leia a assista a alguns dos vídeos sobre a historia e processo de produção dos chips. |

:*[https://www.semiwiki.com/forum/content/1535-brief-history-fabless-semiconductor-industry.html A Brief History of the Fabless Semiconductor Industry] | :*[https://www.semiwiki.com/forum/content/1535-brief-history-fabless-semiconductor-industry.html A Brief History of the Fabless Semiconductor Industry] | ||

:*[http://www.semiwiki.com/forum/content/1539-brief-history-tsmc.html Taiwan Semiconductor Manufacturing Corporation (TSMC)], [http://www.globalfoundries.com/ GLOBALFOUNDRIES] | :*[http://www.semiwiki.com/forum/content/1539-brief-history-tsmc.html Taiwan Semiconductor Manufacturing Corporation (TSMC)], [http://www.globalfoundries.com/ GLOBALFOUNDRIES] | ||

:*[https://www.linkedin.com/pulse/free-copy-fabless-transformation-semiconductor-industry-daniel-nenni-1 Fabless: The Transformation of the Semiconductor Industry, 2014] - Download free | :*[https://www.linkedin.com/pulse/free-copy-fabless-transformation-semiconductor-industry-daniel-nenni-1 Fabless: The Transformation of the Semiconductor Industry, 2014] - Download free | ||

| − | |||

:*[https://www.youtube.com/watch?v=W3rfVpkNquA Produção do FinFET], [https://www.youtube.com/watch?v=d9SWNLZvA8g] | :*[https://www.youtube.com/watch?v=W3rfVpkNquA Produção do FinFET], [https://www.youtube.com/watch?v=d9SWNLZvA8g] | ||

:*[https://en.wikipedia.org/wiki/3_nm_process 3 nm process], [https://en.wikipedia.org/wiki/Multigate_device multi-gate MOSFET] | :*[https://en.wikipedia.org/wiki/3_nm_process 3 nm process], [https://en.wikipedia.org/wiki/Multigate_device multi-gate MOSFET] | ||

Edição das 23h16min de 31 de julho de 2023

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 6 ENCONTROS

| Unidade 1 - Introdução a disciplina |

|---|

ATUAL

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 10 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

- 10 ENCONTROS

| Unidade 3 - Tipos de Dados e Operadores em VHDL |

|---|

Unidade 4 - Código Concorrente

- 4 ENCONTROS

| Unidade 4 - Código Concorrente |

|---|

Unidade 5 - Código Sequencial

- 7 ENCONTROS

| Unidade 5 - Código Sequencial |

|---|

Unidade 6 - Projeto a nível de Sistema

- 3 ENCONTROS

| Unidade 6 - Projeto a nível de Sistema |

|---|

Unidade 7 - Maquinas de Estado Finitas

- 3 ENCONTROS

| Unidade 7 - Maquinas de Estado Finitas |

|---|

Unidade 8 - Testbench

- 2 ENCONTROS

| Unidade 8 - Testbench |

|---|

Avaliações

Nas avaliações A1 e A2 vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - Unidade 1 a Unidade 4: dia XX/XX

- A2 - Unidade 5 a Unidade 7: dia XX/XX

- PF - Entrega do projeto final: dia 15/12

- R12 - Recuperação de A1 e A2 : dia 12/12

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN.

Atividade extra-classe (AE)

A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

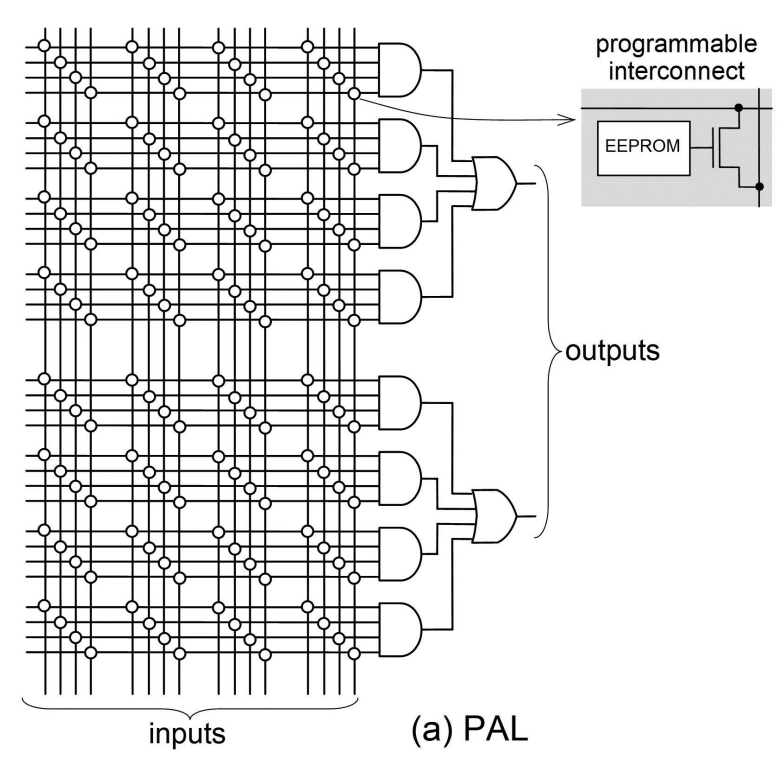

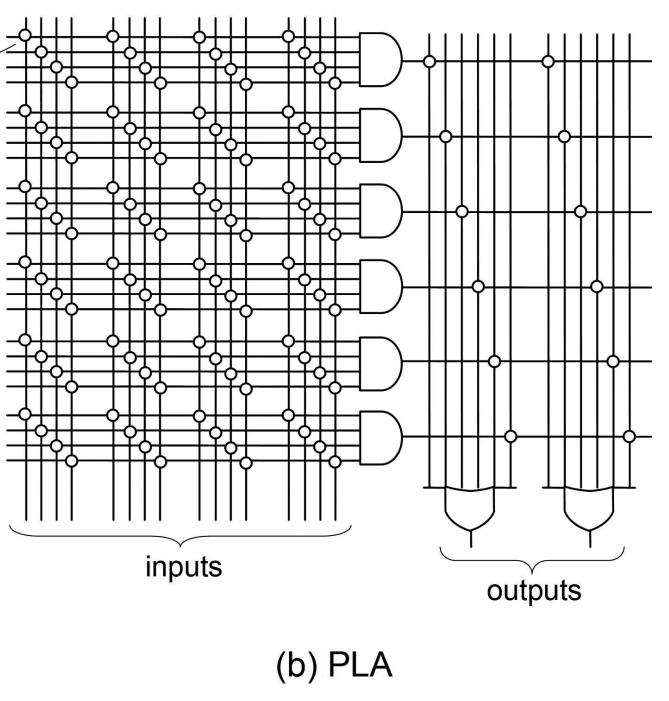

AE2 - Conhecendo os dispositivos lógicos programáveis

| AE2 - Conhecendo os dispositivos lógicos programáveis |

|---|

|