Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

(→ATUAL) |

|||

| Linha 15: | Linha 15: | ||

*Seção 2.1 Dispositivos lógicos programáveis do TCC [[Integração de ramais analógicos com FPGA utilizando processador softcore]], Renan Rodolfo da Silva. | *Seção 2.1 Dispositivos lógicos programáveis do TCC [[Integração de ramais analógicos com FPGA utilizando processador softcore]], Renan Rodolfo da Silva. | ||

| − | |||

;Encontro 2 (28 jul): | ;Encontro 2 (28 jul): | ||

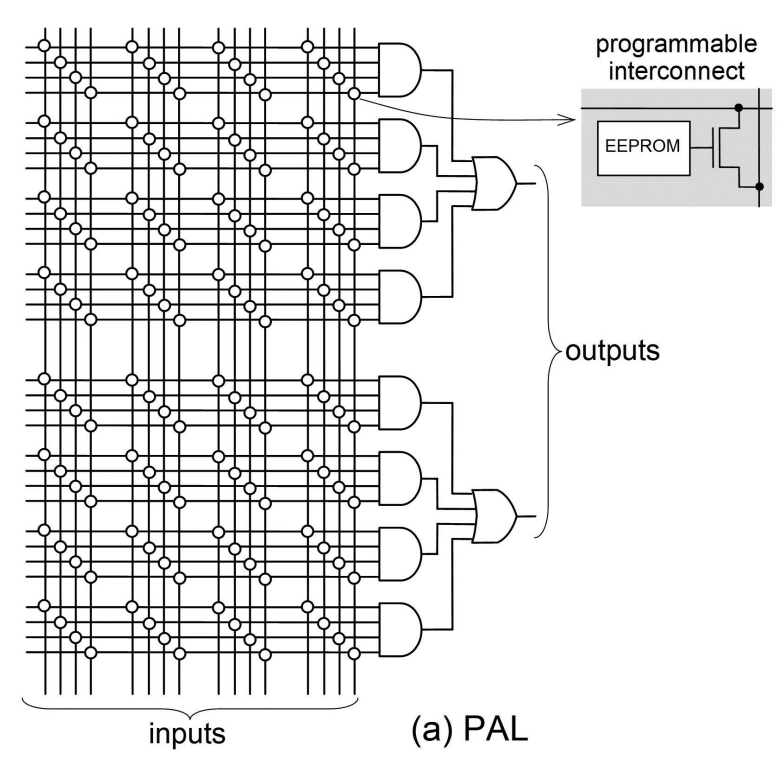

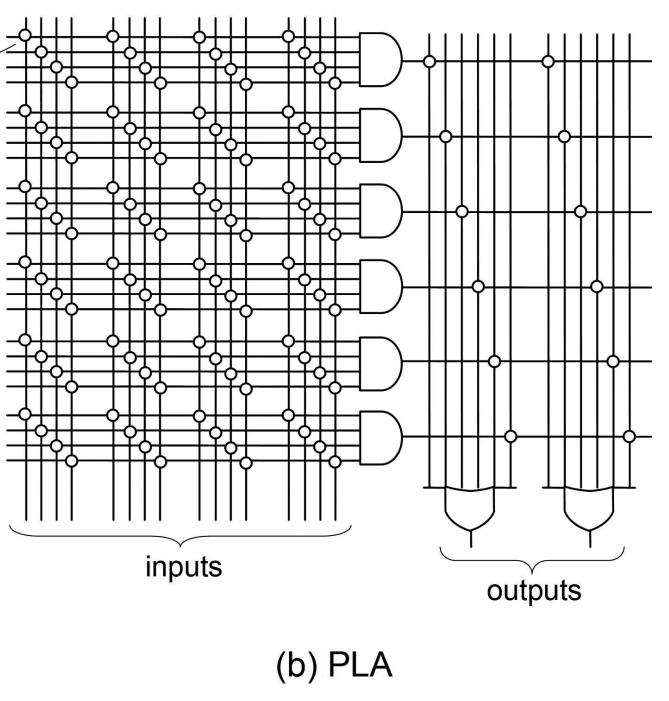

*Introdução aos dispositivos lógicos programáveis: | *Introdução aos dispositivos lógicos programáveis: | ||

| Linha 57: | Linha 56: | ||

*[https://www.intel.com/content/www/us/en/products/details/fpga/platforms.html See why Microsoft chose Intel FPGAs to accelerate their next generation cloud infrastructure] | *[https://www.intel.com/content/www/us/en/products/details/fpga/platforms.html See why Microsoft chose Intel FPGAs to accelerate their next generation cloud infrastructure] | ||

*[https://www.youtube.com/watch?v=ecyyZ6zTLic Microsoft's Bing* Intelligent Search with Intel® FPGAs] | *[https://www.youtube.com/watch?v=ecyyZ6zTLic Microsoft's Bing* Intelligent Search with Intel® FPGAs] | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | ; | + | ====ATUAL==== |

| + | ;Encontro 3 (1 ago): | ||

| + | * [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 1 e 2 | ||

| + | * [[Níveis lógicos]] | ||

| + | ;PARA O PRÓXIMO ENCONTRO: | ||

* Historia, processo de produção dos chips. | * Historia, processo de produção dos chips. | ||

:*[https://www.semiwiki.com/forum/content/1535-brief-history-fabless-semiconductor-industry.html A Brief History of the Fabless Semiconductor Industry] | :*[https://www.semiwiki.com/forum/content/1535-brief-history-fabless-semiconductor-industry.html A Brief History of the Fabless Semiconductor Industry] | ||

| Linha 77: | Linha 72: | ||

:*[https://www.youtube.com/watch?v=UvluuAIiA50 GLOBALFOUNDRIES Sand to Silicon], [https://www.youtube.com/watch?v=F2KcZGwntgg How Microchips are made] - Processo de fabricação de um chip | :*[https://www.youtube.com/watch?v=UvluuAIiA50 GLOBALFOUNDRIES Sand to Silicon], [https://www.youtube.com/watch?v=F2KcZGwntgg How Microchips are made] - Processo de fabricação de um chip | ||

:*[https://en.wikipedia.org/wiki/Foundry_model Foundries], [https://en.wikipedia.org/wiki/List_of_semiconductor_fabrication_plants List of semiconductor fabrication plants] | :*[https://en.wikipedia.org/wiki/Foundry_model Foundries], [https://en.wikipedia.org/wiki/List_of_semiconductor_fabrication_plants List of semiconductor fabrication plants] | ||

| − | + | <!-- | |

*[https://www.sciencedirect.com/topics/computer-science/one-time-programmable One-Time Programmable] Science Direct | *[https://www.sciencedirect.com/topics/computer-science/one-time-programmable One-Time Programmable] Science Direct | ||

*http://www.dcc.ufrj.br/~gabriel/circlog/DispLogPro.pdf | *http://www.dcc.ufrj.br/~gabriel/circlog/DispLogPro.pdf | ||

| Linha 83: | Linha 78: | ||

;Curiosidades do mundo digital: | ;Curiosidades do mundo digital: | ||

*[https://www.computerhistory.org/siliconengine/timeline/ The Silicon Engine Timeline] | *[https://www.computerhistory.org/siliconengine/timeline/ The Silicon Engine Timeline] | ||

| − | |||

| − | |||

| − | |||

;Encontro 5 (23 fev.): | ;Encontro 5 (23 fev.): | ||

| Linha 109: | Linha 101: | ||

* Ler pag. 413 a 431 de <ref name="PEDRONI2010a"> PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657 </ref> ou pag. 495 a 501 de de <ref name="PEDRONI2010b"> PEDRONI, Volnei A. '''Circuit Design and Simulation with VHDL'''; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 </ref>. | * Ler pag. 413 a 431 de <ref name="PEDRONI2010a"> PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657 </ref> ou pag. 495 a 501 de de <ref name="PEDRONI2010b"> PEDRONI, Volnei A. '''Circuit Design and Simulation with VHDL'''; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 </ref>. | ||

| + | ::* [https://en.wikipedia.org/wiki/Field-programmable_gate_array#History FPGA History] | ||

| + | ::* [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Design_and_programming FPGA Design and programming] | ||

| + | ::* [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Basic_process_technology_types FPGA Basic process technology types] | ||

| + | ::* [https://en.wikipedia.org/wiki/Field-programmable_gate_array#Major_manufacturers FPGA Major manufacturers] | ||

* Assistir [https://www.coursera.org/lecture/intro-fpga-design-embedded-systems/1-many-types-of-fpgas-EWo0n Many types of FPGAs] Coursera | * Assistir [https://www.coursera.org/lecture/intro-fpga-design-embedded-systems/1-many-types-of-fpgas-EWo0n Many types of FPGAs] Coursera | ||

Edição das 22h47min de 31 de julho de 2023

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 6 ENCONTROS

| Unidade 1 - Introdução a disciplina |

|---|

ATUAL

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 10 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

- 10 ENCONTROS

| Unidade 3 - Tipos de Dados e Operadores em VHDL |

|---|

Unidade 4 - Código Concorrente

- 4 ENCONTROS

| Unidade 4 - Código Concorrente |

|---|

Unidade 5 - Código Sequencial

- 7 ENCONTROS

| Unidade 5 - Código Sequencial |

|---|

Unidade 6 - Projeto a nível de Sistema

- 3 ENCONTROS

| Unidade 6 - Projeto a nível de Sistema |

|---|

Unidade 7 - Maquinas de Estado Finitas

- 3 ENCONTROS

| Unidade 7 - Maquinas de Estado Finitas |

|---|

Unidade 8 - Testbench

- 2 ENCONTROS

| Unidade 8 - Testbench |

|---|

Avaliações

Nas avaliações A1 e A2 vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - Unidade 1 a Unidade 4: dia XX/XX

- A2 - Unidade 5 a Unidade 7: dia XX/XX

- PF - Entrega do projeto final: dia 15/12

- R12 - Recuperação de A1 e A2 : dia 12/12

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN.

Atividade extra-classe (AE)

A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

AE2 - Conhecendo os dispositivos lógicos programáveis

| AE2 - Conhecendo os dispositivos lógicos programáveis |

|---|

|