Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

| Linha 3 257: | Linha 3 257: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| + | --> | ||

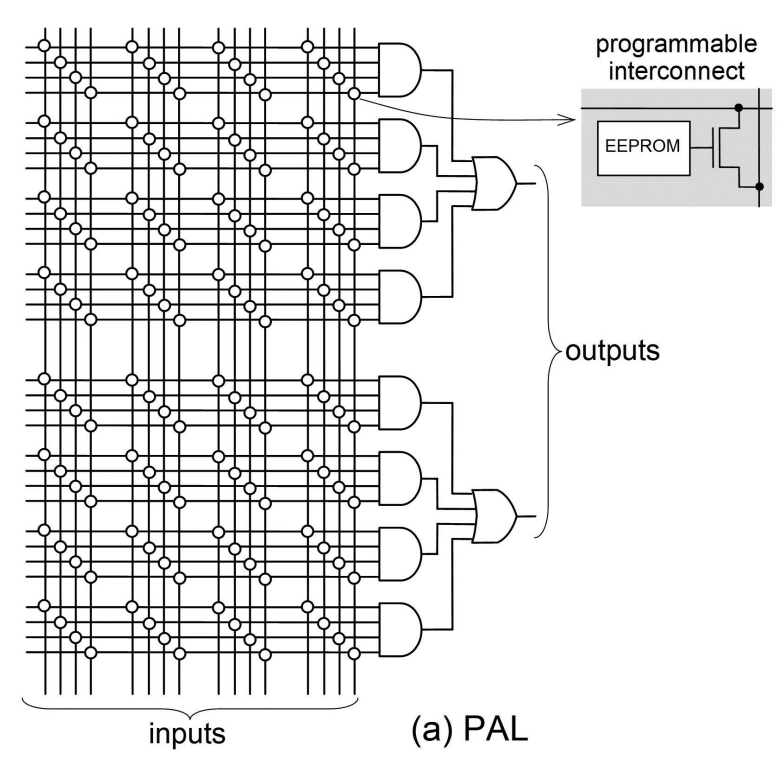

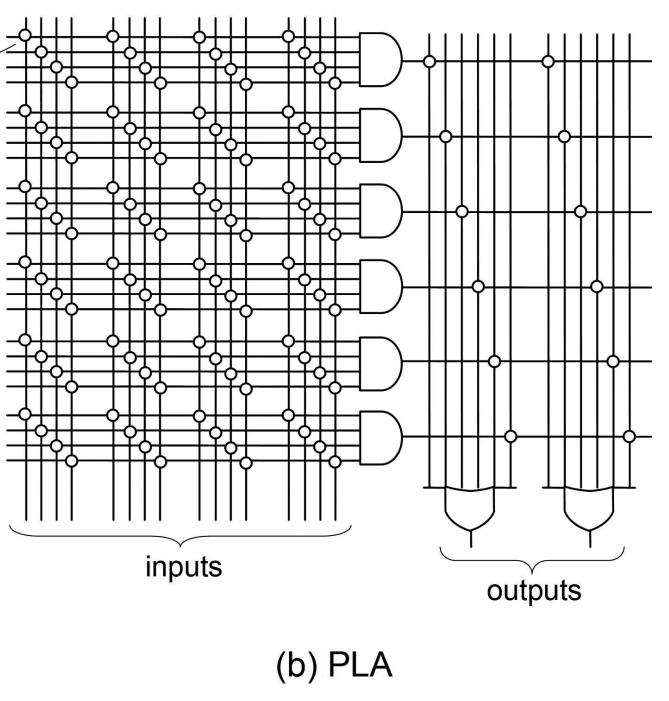

===AE2 - Conhecendo os dispositivos lógicos programáveis=== | ===AE2 - Conhecendo os dispositivos lógicos programáveis=== | ||

| − | {{collapse top |bg=lightyellow | AE2 - Conhecendo os dispositivos lógicos programáveis}} | + | {{collapse top |expand=true| bg=lightyellow | AE2 - Conhecendo os dispositivos lógicos programáveis}} |

;Objetivos: | ;Objetivos: | ||

| − | *Conhecer o Quartus | + | *Conhecer o Quartus Prime e as características dos dispositivos lógicos programáveis |

*Analisar os tempos de propagação em um circuito combinacional | *Analisar os tempos de propagação em um circuito combinacional | ||

*Alterar configurações do compilador | *Alterar configurações do compilador | ||

*Fazer a simulação funcional e temporal de um circuito combinacional. | *Fazer a simulação funcional e temporal de um circuito combinacional. | ||

| − | ; | + | ;Atividades: |

| − | *'''PASSO 1:''' Realize a atividade descrita em [[Conhecendo os dispositivos lógicos programáveis]] | + | *'''PASSO 1:''' Realize a atividade descrita em [[Conhecendo os dispositivos lógicos programáveis - QUARTUS PRIME]] |

:*Ao escolher a família de FPGAS, escolha inicialmente um dispositivo da família '''Cyclone II''', ou '''Max II'''. Anote o código desse dispositivo. | :*Ao escolher a família de FPGAS, escolha inicialmente um dispositivo da família '''Cyclone II''', ou '''Max II'''. Anote o código desse dispositivo. | ||

:*Capture as telas solicitadas e depois utilize-as no relatório da atividade. | :*Capture as telas solicitadas e depois utilize-as no relatório da atividade. | ||

| Linha 3 275: | Linha 3 276: | ||

:*Ao final salve o projeto em um arquivo QAR (sugestão PJ1.QAR) | :*Ao final salve o projeto em um arquivo QAR (sugestão PJ1.QAR) | ||

| − | *'''PASSO 2''': Repita a atividade descrita em [[Conhecendo os dispositivos lógicos programáveis]], trocando a família e dispositivo a ser usado na implementação. Escolha nesta vez um dispositivos da família '''Cyclone IV E''' ou '''Stratix II GX'''. Anote o código desse dispositivo. | + | *'''PASSO 2''': Repita a atividade descrita em [[Conhecendo os dispositivos lógicos programáveis - QUARTUS PRIME]], trocando a família e dispositivo a ser usado na implementação. Escolha nesta vez um dispositivos da família '''Cyclone IV E''' ou '''Stratix II GX'''. Anote o código desse dispositivo. |

:*Observe as mudanças que ocorrem tanto no tipo de Elemento Lógico disponível, no Chip Planner, no Pin Planner, e no circuito dos pinos de I/O. Note que estes FPGAs também apresenta novos componentes, tais como: Memória, Multiplicadores, DSP, PLL, DLL, etc. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documente aqueles que encontrar. | :*Observe as mudanças que ocorrem tanto no tipo de Elemento Lógico disponível, no Chip Planner, no Pin Planner, e no circuito dos pinos de I/O. Note que estes FPGAs também apresenta novos componentes, tais como: Memória, Multiplicadores, DSP, PLL, DLL, etc. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documente aqueles que encontrar. | ||

:*Compare os resultados obtidos nos procedimentos do PASSO 1 e PASSO 2. | :*Compare os resultados obtidos nos procedimentos do PASSO 1 e PASSO 2. | ||

| + | <!-- | ||

*'''PASSO 3''': Realize o procedimento descrito em [[Medição de tempos de propagação em circuitos combinacionais]] | *'''PASSO 3''': Realize o procedimento descrito em [[Medição de tempos de propagação em circuitos combinacionais]] | ||

Edição das 22h38min de 31 de julho de 2023

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 6 ENCONTROS

| Unidade 1 - Introdução a disciplina |

|---|

ATUAL

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 10 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

- 10 ENCONTROS

| Unidade 3 - Tipos de Dados e Operadores em VHDL |

|---|

Unidade 4 - Código Concorrente

- 4 ENCONTROS

| Unidade 4 - Código Concorrente |

|---|

Unidade 5 - Código Sequencial

- 7 ENCONTROS

| Unidade 5 - Código Sequencial |

|---|

Unidade 6 - Projeto a nível de Sistema

- 3 ENCONTROS

| Unidade 6 - Projeto a nível de Sistema |

|---|

Unidade 7 - Maquinas de Estado Finitas

- 3 ENCONTROS

| Unidade 7 - Maquinas de Estado Finitas |

|---|

Unidade 8 - Testbench

- 2 ENCONTROS

| Unidade 8 - Testbench |

|---|

Avaliações

Nas avaliações A1 e A2 vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - Unidade 1 a Unidade 4: dia XX/XX

- A2 - Unidade 5 a Unidade 7: dia XX/XX

- PF - Entrega do projeto final: dia 15/12

- R12 - Recuperação de A1 e A2 : dia 12/12

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN.

Atividade extra-classe (AE)

A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

AE2 - Conhecendo os dispositivos lógicos programáveis

| AE2 - Conhecendo os dispositivos lógicos programáveis |

|---|

|