Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

(→ATUAL) |

(→ATUAL) |

||

| Linha 19: | Linha 19: | ||

*Introdução aos dispositivos lógicos programáveis: | *Introdução aos dispositivos lógicos programáveis: | ||

:* Conceito, tipos de PLDs | :* Conceito, tipos de PLDs | ||

| − | + | :* SPLD: | |

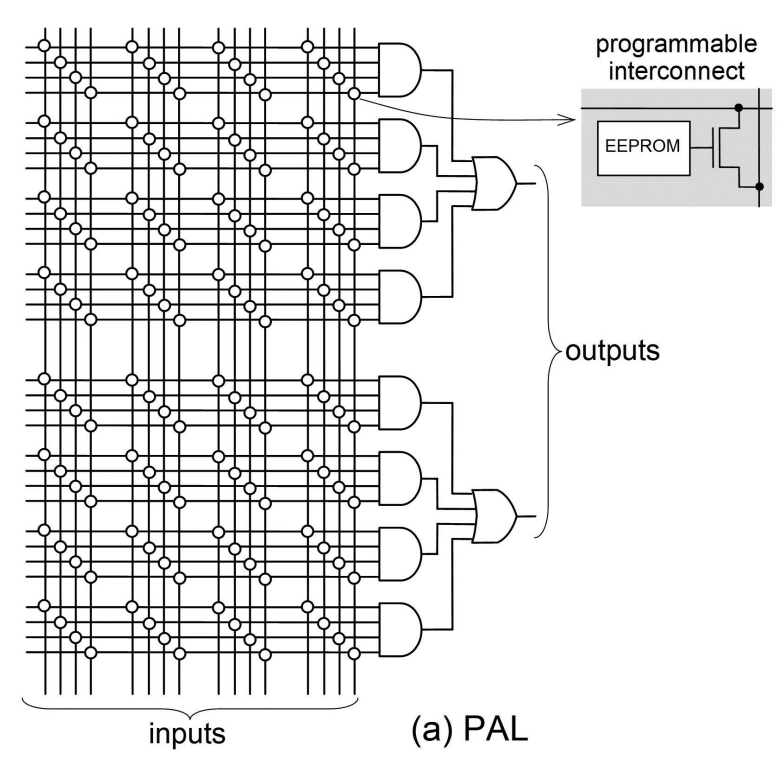

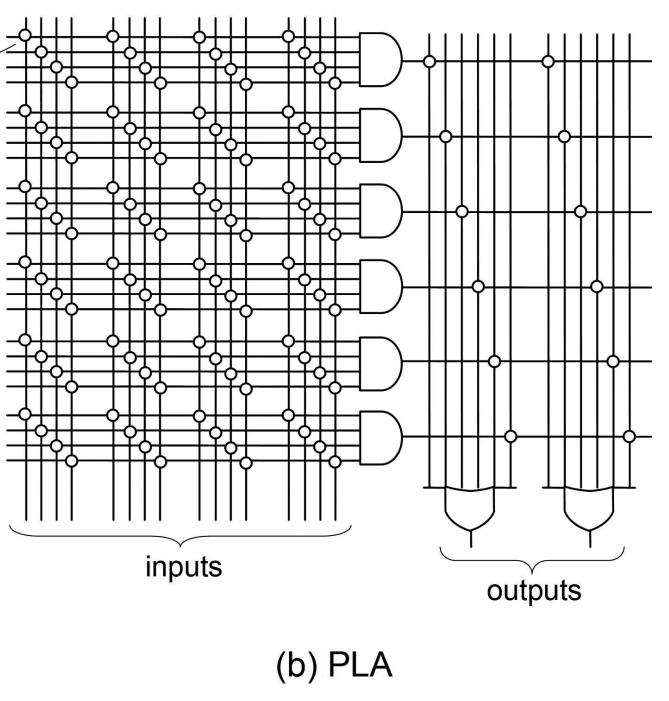

| − | + | ::*PAL (e.g. [[Media: PAL16.pdf| PAL16 da Texas Instruments (1984)]]) | |

| + | ::*PLA (e.g. [[Media: PLS100.pdf| PLS100 da Philips Semiconductors (1993)]]) | ||

| + | ::*GAL (e.g. [[Media: GAL16V8.pdf| GAL16V8 da Lattice (2004)]]) | ||

| + | :* CPLDs (e.g. [[Media: ATF2500C.pdf| ATF2500C da Atmel (2008)]], [https://br.mouser.com/c/ds/semiconductors/programmable-logic-ics/cpld-complex-programmable-logic-devices/ Complex Programmable Logic Devices Datasheets - Mouser]) | ||

{{collapse top | expand=true| Exemplos de PLDs}} | {{collapse top | expand=true| Exemplos de PLDs}} | ||

Edição das 15h03min de 26 de julho de 2023

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 6 ENCONTROS

| Unidade 1 - Introdução a disciplina |

|---|

ATUAL

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 10 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

- 10 ENCONTROS

| Unidade 3 - Tipos de Dados e Operadores em VHDL |

|---|

Unidade 4 - Código Concorrente

- 4 ENCONTROS

| Unidade 4 - Código Concorrente |

|---|

Unidade 5 - Código Sequencial

- 7 ENCONTROS

| Unidade 5 - Código Sequencial |

|---|

Unidade 6 - Projeto a nível de Sistema

- 3 ENCONTROS

| Unidade 6 - Projeto a nível de Sistema |

|---|

Unidade 7 - Maquinas de Estado Finitas

- 3 ENCONTROS

| Unidade 7 - Maquinas de Estado Finitas |

|---|

Unidade 8 - Testbench

- 2 ENCONTROS

| Unidade 8 - Testbench |

|---|

Avaliações

Nas avaliações A1 e A2 vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - Unidade 1 a Unidade 4: dia XX/XX

- A2 - Unidade 5 a Unidade 7: dia XX/XX

- PF - Entrega do projeto final: dia 15/12

- R12 - Recuperação de A1 e A2 : dia 12/12

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. Elas geram BÔNUS que são adicionados aos conceitos das avaliações A1 e A2.

Atividade extra-classe (AE)

A soma das atividades Extra-classe será correspondente a 25% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.